SfoiV

г

(Л

4 У1

1

140

зование входного двоичного кода в рабочий код осуществляется параллельным методом, что повышает быстродействие устройства. Устройство при помопщ основного и вспомогательного цифроана- логовьк преобразователей 1 и 2, регистров 5, 6, 11, 13, блока памяти 10, блока сравнения 3, арифметико-логического устройства 12, блока управления 4 и цифровых коммутаторов 7, 8,

17

9 проводит определение кодов реальных весов разрядов основного цифроанало- гового преобразователя 1. Введение цифровых коммутаторов 14 и 15. позволяет на основании полученных кодов произвести формирование массива кодов, размещаемых в блоке памяти 10, и формировать рабочий код из входного двоичного за один такт суммирования. 2 з.п. ф-лы, 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1984 |

|

SU1216827A1 |

| Устройство для цифроаналогового преобразования | 1984 |

|

SU1248072A1 |

| Многоканальное устройство для ввода-вывода аналоговой информации | 1988 |

|

SU1564606A1 |

| Устройство аналого-цифрового преобразования | 1985 |

|

SU1288914A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1667249A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1257848A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1750060A1 |

| Микропроцессор | 1983 |

|

SU1195364A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

Изобретение относится к вычислительной и цифровой измерительной технике и может быть использовано для преобразования цифровых величин в аналоговые.

Цель изобретения - повышение быстродействия .

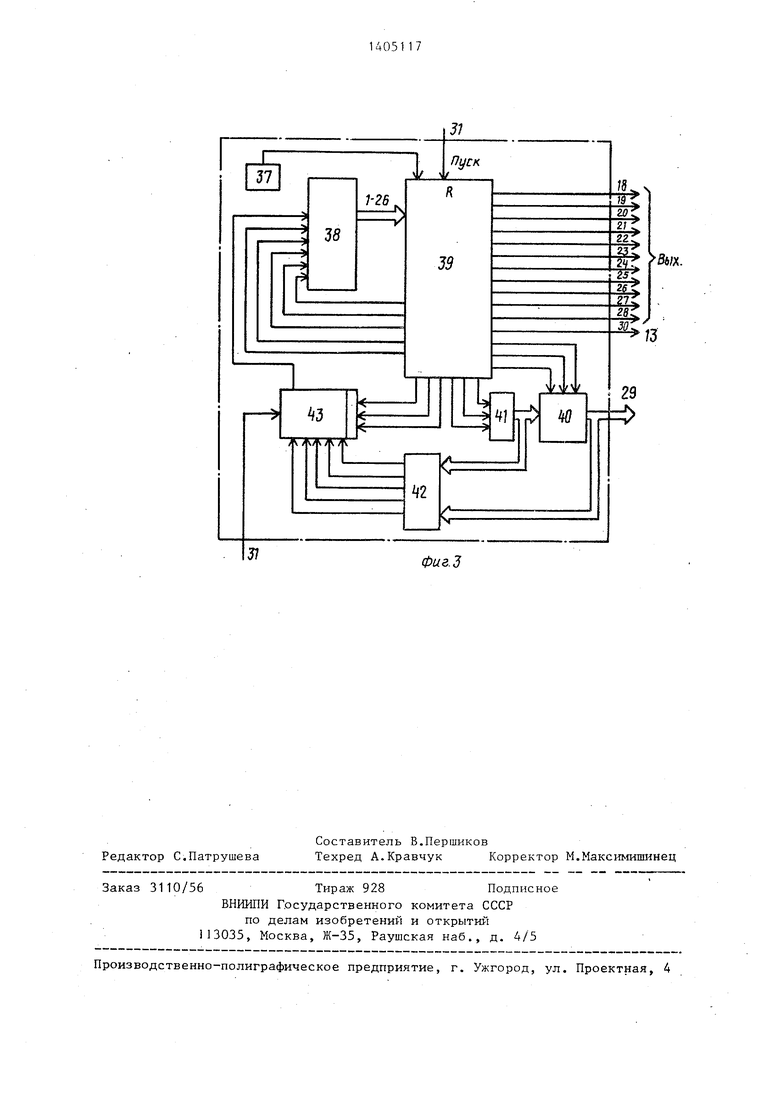

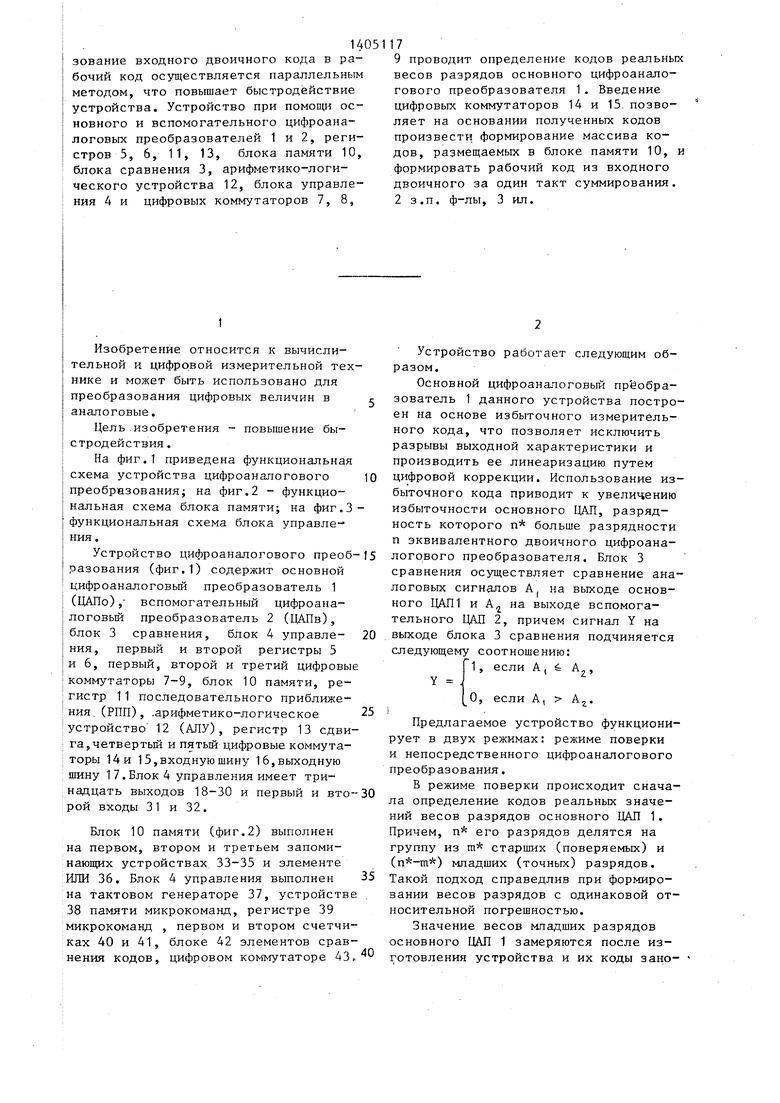

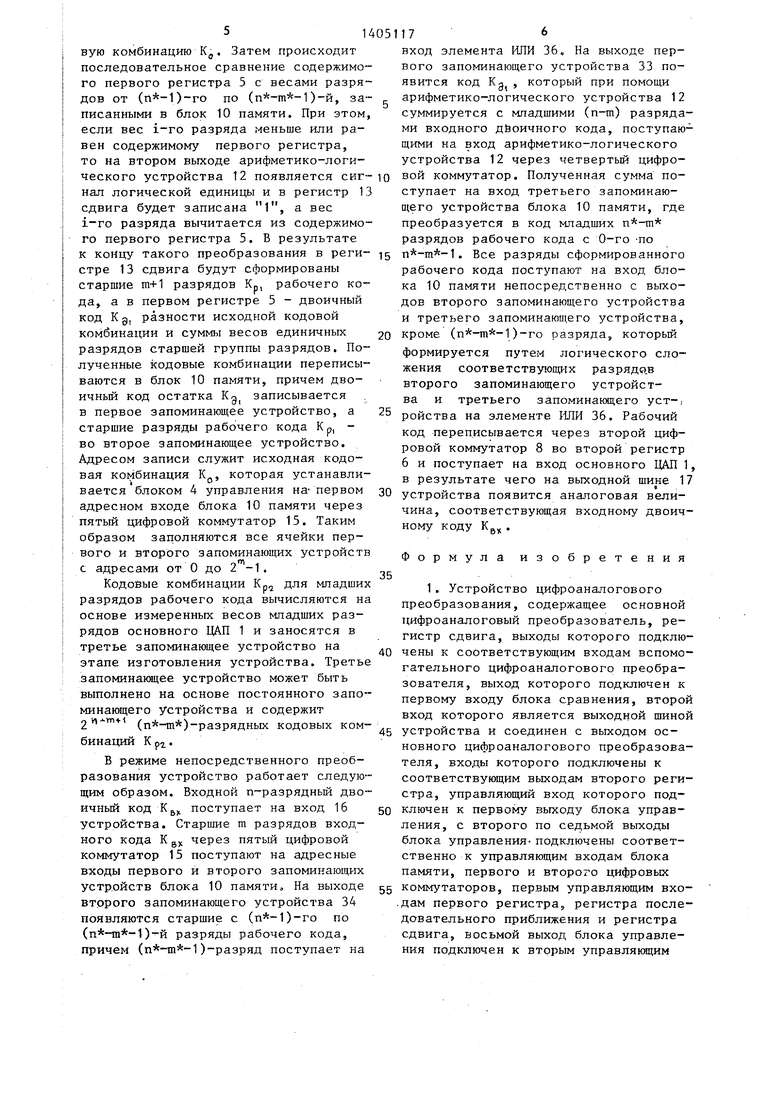

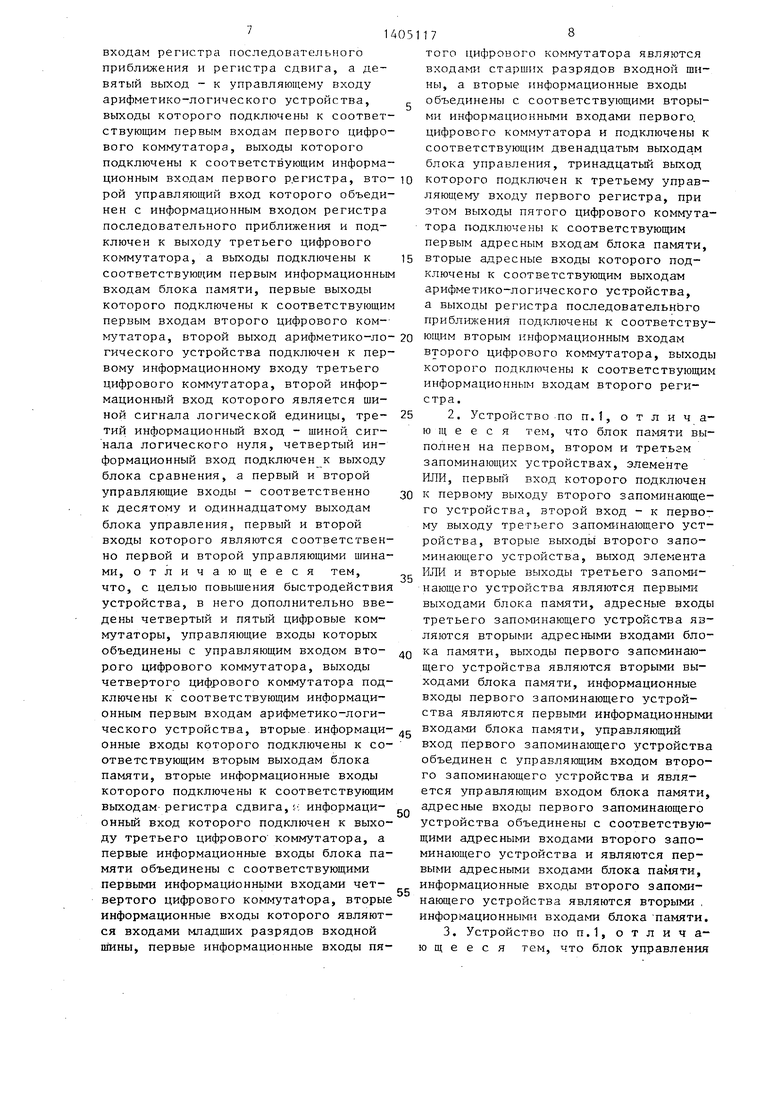

На фиг.1 приведена функциональная схема устройства цифроаналогового преобразования; на фиг.2 - функциональная схема блока памяти; на фиг.З функциональная схема блока управления.

Устройство цифроаналогового npeo6разования (фиг.1) содержит основной цифроаналоговый преобразователь 1 (ЦАПо) , вспомогательный цифроана- логовьш преобразователь 2 (ЦАПв), блок 3 сравнения, блок 4 управле- ния, первый и второй регистры 5 и 6, первый, второй и третий цифровые I коммутаторы 7-9, блок 10 памяти, ре- Iгистр 11 последовательного приближения. (РПП), .арифметико-логическое устройство 12 (АЛУ), регистр 13 сдви- i га,четвертьш и пятый цифровые коммута- ; торы 14 и 15,входную шину 16, выходную шину 1 7. Блок 4 управления имеет тринадцать выходов 18-30 и первый и второй входы 31 и 32.

Блок 10 памяти (фиг.2) выполнен на первом, втором и третьем запоминающих устройствах 33-35 и элементе ИЛИ 36. Блок 4 управления выполнен на тактовом генераторе 37, устройстве 38 памяти микрокоманд, регистре 39 микрокоманд , первом и втором счетчиках 40 и 41, блоке 42 элементов сравнения кодов, цифровом коммутаторе 43,

Устройство работает следующим образом.

Основной цифроаналоговый преобразователь 1 данного устройства построен на основе избыточного измерительного кода, что позволяет исключить разрывы выходной характеристики и производить ее линеаризацию путем цифровой коррекции. Использование избыточного кода приводит к увеличению избыточности основного ЦАП, разрядность которого п больше разрядности п эквивалентного двоичного цифроаналогового преобразователя. Блок 3 сравнения осуществляет сравнение аналоговых сигналов А| на выходе основного ЦАП1 и А на выходе вспомогательного ЦАП 2, причем сигнал Y на выходе блока 3 сравнения подчиняется следующему соотношению:

Y

1, если А, и: А, О, если А, А,

Предлагаемое устройство функционирует в двух режимах: режиме поверки и непосредственного цифроаналогового преобразования.

В режиме поверки происходит сначала определение кодов реальных значений весов разрядов основного ЦАП 1. Причем, п его разрядов делятся на группу из т старших (поверяемых) и () младших (точных) разрядов. Такой подход справедлив при формировании весов разрядов с одинаковой относительной погрешностью.

Значение весов мпадших разрядов основного ЦАП 1 замеряются после изготовления устройства и их коды зано31

сятся в область памяти первого загсо- минающего устройства блока 10 памяти в ячейки с номерами от А до -т Определение кодов К- реальных значе- НИИ весов разрядов производится только из т старших разрядов.

Определение кодов старших разрядов происходит при формировании вспомо- I гательным ЦАП 2 ступенчато нарастаю- щей аналоговой величины А . , каждая ступень которой соответствует весу 1-го поверяемого разряда. Каждый аналоговый сигнал дважды уравновешивается по методу поразрядного кодиро- вания компенсирующим сигналом А, основного ЦАП 1 - один раз с запретом включения поверяемого разряда, второй раз - без запрета. По результатам двух кодирований определяется код реального веса поверяемого разряда.

Определение реальных весов осуществляется следующим образом. По сигналам блока 4 управления происходит обнуление первого регистра 5, обнуление участка первого запоминающего устройства блока 10 управления с адресами до А, , запись исходного кода в регистр 13 сдвига, установка начального состояния регистра 11 последовательного приближения, подключение выходов арифметико-логического устройства 12 через первый цифровой коммутатор 7 к входам первого регистра 5. Сигнал на выходе 21 блока 4 управления коммутирует выходы первого регистра 5 на входы арифметико-логического устройства 12, выходы регистра 11 последовательного приближения на входы второго регистра 6 и выходы 29 блока 4 управления - на первые адресные входы блока 10 памяти. На выходе вспомогательного ЦАП 2 появится аналоговый сигнал А,2. т)

Значение вспомогательного аналогового

сигнала должно быть таким, чтобы при поразрядном уравновешивании его компенсирующим сигналом основного ЦАП 1 произошло включение поверяемого ()-го разряда, т.е. должен превышать реальный вес поверяемого разряда на 5-20%. Далее при помощи блоков 1-6, 9, 11 производится аналого-цифровое преобразование сигнала А , ,, ,1 . Результат первого преобразования К, которое осуществляется с запретом включения ()-го разряда, формируется в регистре 11 последовательного приближе-

1174

ния при помопр блока 4 управления и третьего цифрового коммутатора 9. Одновременно с этим в первом регистре 5 формируется двоичный код, код первого преобразования К,, при. помощи блоков 4, 5, 10, 9, 12 по формуле

К

1 ()

i.

1 0

5 0

5 О 0

5

где а; ,11 - разрядные коэффициенты первого кодирования

Результат вт.орого кодирования

кже формируется в регистре 11 последовательного приближения, а соответствующий ему двоичный код 1( первом регистре 5 по

формуле «-1

.11

,1 2(. /-j

где ,lj - разрядные коэффициенты второго кодирования К,.

Так как в вьфажении (1) коды К; равны нулю при , то код равен коду реального веса (пЛ-т)-го разряда, т.е. К ( ° сигналу блока 4 управления этот код переписывается в первое запоминающее устройство блока 10 памяти по адресу А (.

Далее производится сдвиг регистра 13 сдвига, в результате чего на выходе вспомогательного ЦАП 2 появится аналоговый сигнал для определения реального веса следующего поверяемого разряда.

Этот процесс аналогичен для всех последующих разрядов и заканчивается после определения кодов реальных весов всех старших разрядов. Вычисленные коды записывают в область первого запоминающего устройства с адресами от до А„, .

Затем происходит формирование кодовых комбинаций старших т разрядов рабочего кода, соответствующих старшей т-разрядной группе входного кода. Формирование рабочих кодовых комбинаций происходит последовательно для всех 2 комбинаций старших разрядов входного двоичного кода от О до 2 -1, при этом его младшие n-m разрядов полагаются равными нулю.

Блок 4 управления через первый цифровой коммутатор 7 записывает в первый регистр 5 преобразуемую кодо51

вую комбинацию Kg. Затем происходит последовательное сравнение содержимого первого регистра 5 с весами разрядов от ()-го по ()-й, за- писанными в блок 10 памяти. При этом, если вес i-ro разряда меньше или равен содержимому первого регистра, то на втором выходе арифметико-логического устройства 12 появляется сиг- нал логической единицы и в регистр 13 сдвига будет записана 1, а вес i-го разряда вычитается из содержимого первого регистра 5. В результате к концу такого преобразования в реги- стре 13 сдвига будут сформированы старшие т+1 разрядов К, рабочего кода, а в первом регистре 5 - двоичный код Kg, разности исходной кодовой комбинации и суммы весов единичных разрядов старшей группы разрядов. Полученные кодовые комбинации переписываются в блок 10 памяти, причем двоичный код остатка Кд записывается в первое запоминающее устройство, а старшие разряды рабочего кода Кр, - во второе запоминающее устройство. Адресом записи служит исходная кодовая комбинация Кр, которая устанавливается блоком 4 управления на- первом адресном входе блока 10 памяти через пятый цифровой коммутатор 15. Таким образом заполняются все ячейки первого и второго запоминающих устройств с адресами от О до 2 -1.

Кодовые комбинации Кр, для младших

разрядов рабочего кода вычисляются на основе измеренных весов младших разрядов основного ЦАП 1 и заносятся в третье запоминающее устройство на этапе изготовления устройства. Третье запоминаняцее устройство может быть выполнено на основе постоянного запоминающего устройства и содержит 2H- Wi-n ()-разрядных кодовых комбинаций К PI .

В режиме непосредственного преобразования устройство работает следующим образом. Входной п-разрядньш двоичный код Kg, поступает на вход 16 устройства. Старшие m разрядов входного кода К ц через пятый цифровой коммутатор 15 поступают на адресные входы первого и второго запоминающих устройств блока 10 памяти. На выходе второго запоминающего устройства 34 появляются старшие с ()-го по () разряды рабочего кода, причем ()-разряд поступает на

- 5 0 5 о

5

5

„

0 g

176

вход элемента ИЛИ 36. На выходе первого запоминающего устройства 33 появится код Kg , который при помощи арифметико-логического устройства 12 суммируется с мпадшими (n-m) разрядами входного двоичного кода, поступающими на вход арифметико-логического устройства 12 через четвертый цифровой коммутатор. Полученная сумма поступает на вход третьего запоминающего устройства блока 10 памяти, где преобразуется в код младших разрядов рабочего кода с 0-го -по . Все разряды сформированного рабочего кода поступают на вход, блока 10 памяти непосредственно с выходов второго запоминающего устройства и третьего запоминающего устройства, кроме ()-го разряда, который

формируется путем логического сложения соответствующих разрядов второго запоминающего устройства и третьего запоминающего уст-j ройства на элементе ИЛИ 36. Рабочий код переписывается через второй цифровой коммутатор 8 во второй регистр 6 и поступает на вход основного ЦАП 1, в результате чего на выходной шине 17 устройства появится аналоговая величина, соответствующая входному двоичному коду Кц, .

Формула изобретения

входам регистра последовательного приближения и регистра сдвига, а девятый выход - к управляющему входу арифметико-логического устройства, выходы которого подключены к соответствующим первым входам первого цифрового коммутатора, выходы которого подключены к соответствующим информационным входам первого регистра, второй управляющий вход которого объединен с информационным входом регистра последовательного приближения и подключен к выходу третьего цифрового коммутатора, а выходы подключены к соответствуюп(им первым информационным входам блока памяти, первые выходы которого подключены к соответствующим первым входам второго цифрового ком-- мутатора, второй выход арифметико-логического устройства подключен к первому информационному входу третьего цифрового коммутатора, второй информационный вход которого является шиной сигнала логической единицы, третий информационный вход - шиной сигнала логического нуля, четвертый информационный вход подключен к выходу блока сравнения, а первый и второй управляющие входы - соответственно к десятому и одиннадцатому выходам блока управления, первый и второй входы которого являются соответственно первой и второй управляющими шинами, отличающееся тем, что, с целью повышения быстродействия устройства, в него дополнительно введены четвертый и пятый цифровые коммутаторы, управляющие входы которых объединены с управляющим входом второго цифрового коммутатора, выходы четвертого цифрового коммутатора подключены к соответствующим информационным первым входам арифметико-логического устройства, вторые, информационные входы которого подключены к соответствующим вторым выходам блока памяти, вторые информационные входы которого подключены к соответствующим выходам- регистра сдвига, .: информационный вход которого подключен к выходу третьего цифрового коммутатора, а первые информационные входы блока памяти объединены с соответствующими первыми информационными входами четвертого цифрового KOMMyTatopa, вторые информационные входы которого являются входами младших разрядов входной пшны, первые информационные входы пя51178

того цифрового коммутатора являются входаьш старших разрядов входной шины, а вторые информационные входы J- объединены с соответствующими вторыми информационными входами первого, цифрового коммутатора и подключены к cooтвeтcтвyюцц м двенадцатым выходам блока управления, тринадцатый выход

0 которого подключен к третьему управляющему входу первого регистра, при этом выходы пятого цифрового кoм fyтa- тора подключены к соответствующим первым адресным входам блока памяти,

5 вторые адресные входы которого подключены к соответствующим выходам арифметико-логического устройства, а выходы регистра последовательного пpиблi жeния подключены к соответству0 ющим вторым информационным входам

второго цифрового коммутатора, выходы которого подключены к соответствующим информационным входам второго регистра.

5 2. Устройство по п.1, отличающееся тем, что блок памяти выполнен на первом, втором и третьем запоминающих устройствах, элементе ИЛИ, первый вход которого подключен

0 к первому выходу второго запоминающего устройства, второй вход - к перво- Nry выходу третьего запоминающего устройства, вторые выходы второго запоминающего устройства, выход элемента ИЛИ и вторые выходы третьего запоминающего устройства являются первымг- выходами блока памяти, адресные входы третьего запоминающего устройства являются вторыми адресными входами бло0 ка памяти, выходы первого запоминающего устройства являются вторыми выходами блока памяти, информационные входы первого запоминающего устройства являются первыми информационными

g входами блока памяти, управляющий

вход первого запоминающего устройства объединен с управляющим входом второго запоминающего устройства и является управляющим входом блока памяти.

5

адресные входы первого запоминающего устройства объединены с соответствующими адресными входами второго запоминающего устройства и являются первыми адресными входами блока памяти, информационные входы второго 3anoMJi- нающего устройства являются вторыми , информационными входами блока памяти, 3, Устройство по П.1, отличающееся тем, что блок управления

914

выполнен на устройстве памяти микрокоманд, регистре микрокоманд, первом н втором счетчиках, блоке элементов равнения кодов, цифровом коммутато- ре, тактрвом генераторе, выход которого подключен к входу записи регистра микрокоманд, информационные входы с первого по двадцать шестой которого подключены к соответствующим выхо- дам устройства памяти микрокоманд, вход обнуления является вторым входом блока управления, выходы с первого по одиннадцатый - соответствующими выходами блока управления, двенадцатый выход - тринадцатым выходом блока управления, выходы с тринадцатого по пятнадцатый подключены соответственно к первому, второму и третьему управляющим входам первого счетчика, выхо- ды которого являются двенадцатыми выходами блока управления и подключены к соответствующим первым входам блока элементов сравнения кодов, вто1710

рые входы которого объединены с соответствующими информационными входами первого счетчика и подключены к соответствующим выходам второго счетчика, первый, второй и третий управляющие входы которого подключены соответственно к выходам регистра микрокоманд с щестнсщцатого по восемнадцатый, выходы с девятнадцатого по двадцать первый которого подключены соответственно к адресным входам цифрового коммутатора с первого по третий, информационные входы с первого по пятый которого подключены к соответствующим выходам блока элементов сравнения кодов, шестой информационньй вход является первым входом блока управления,, выход подключен к первому адресному входу устройства памяти микрокоманд, адресные входы с второго по шестой которого подключены соответственно к выходам регистра микрокоманд с двадцать второго по двадцать шестой.

Фиг. 2

5

фиг.З

| Декодирующее устройство | 1979 |

|

SU864543A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-06-23—Публикация

1986-06-16—Подача