Изобретение относится к электро- радионзмерениям и может быть нсполь- зовано для поверки фазометров; низкочастотного и инфранизкочастотного диапазонов«

Целью изобретения является упрощение устройства и обеспечение возможности програ много управления.

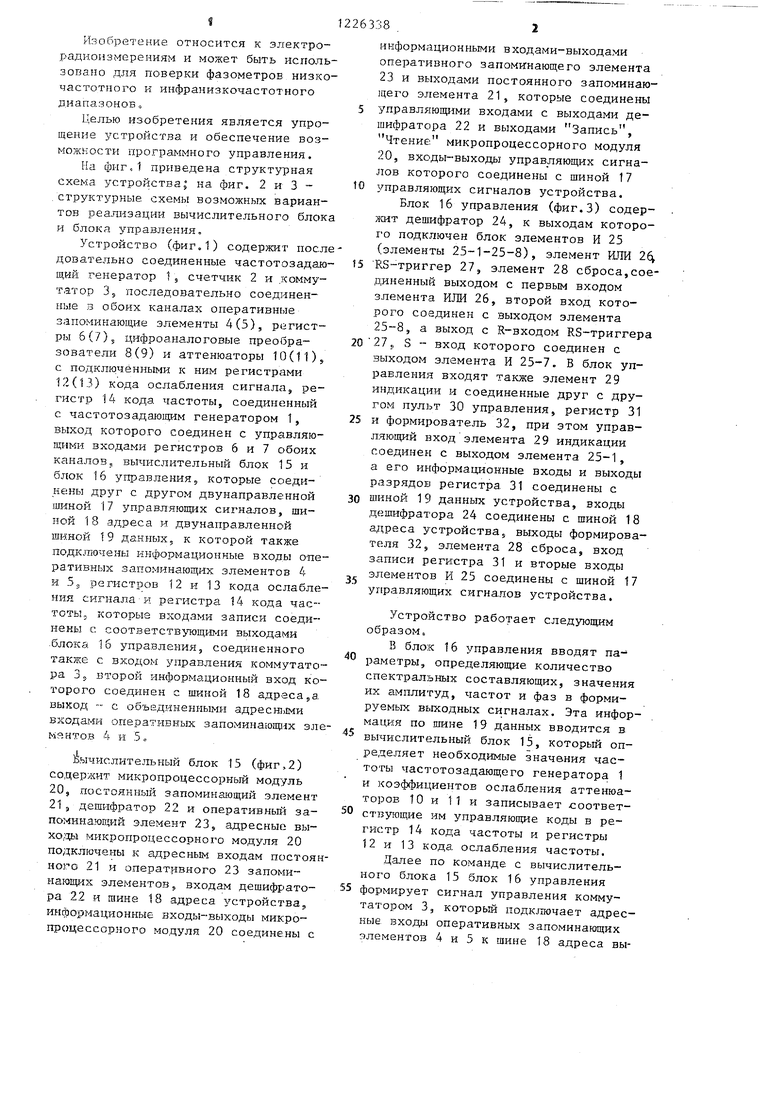

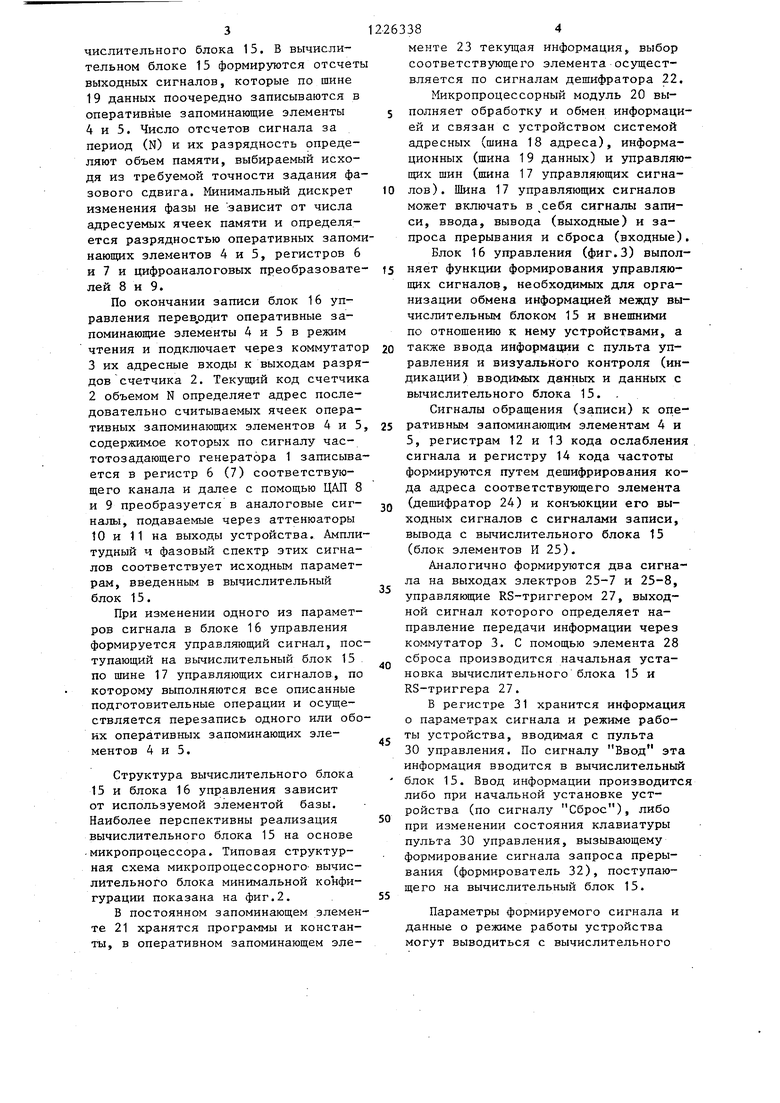

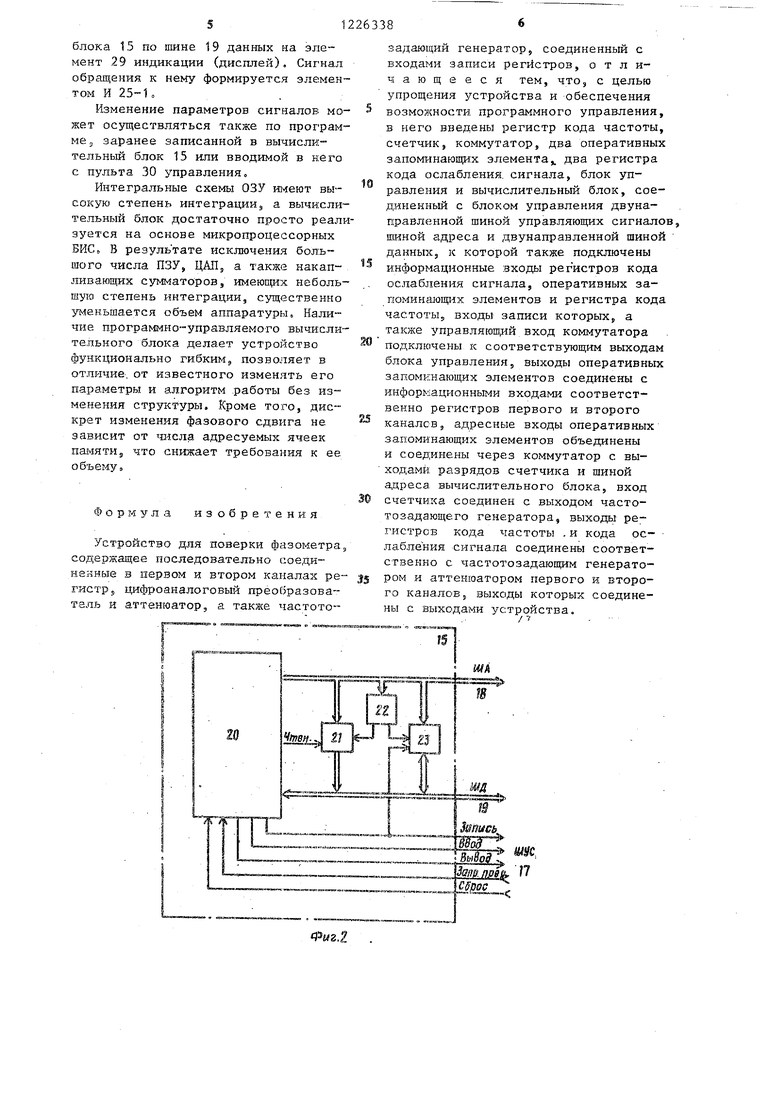

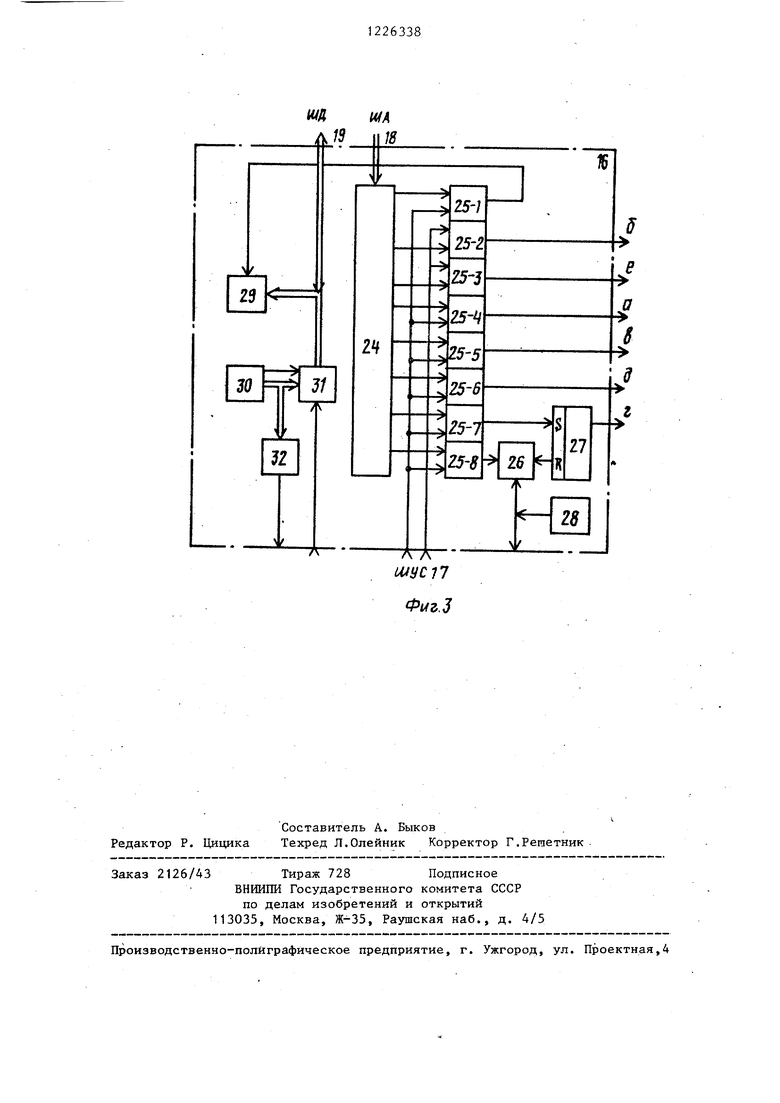

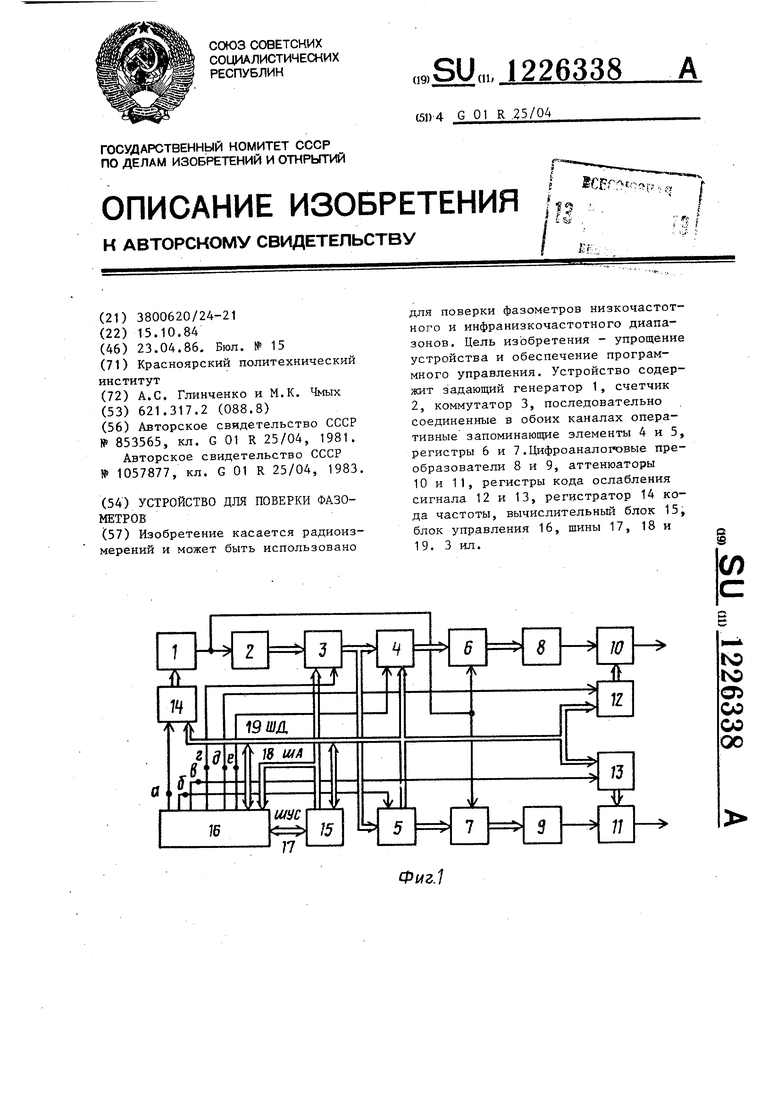

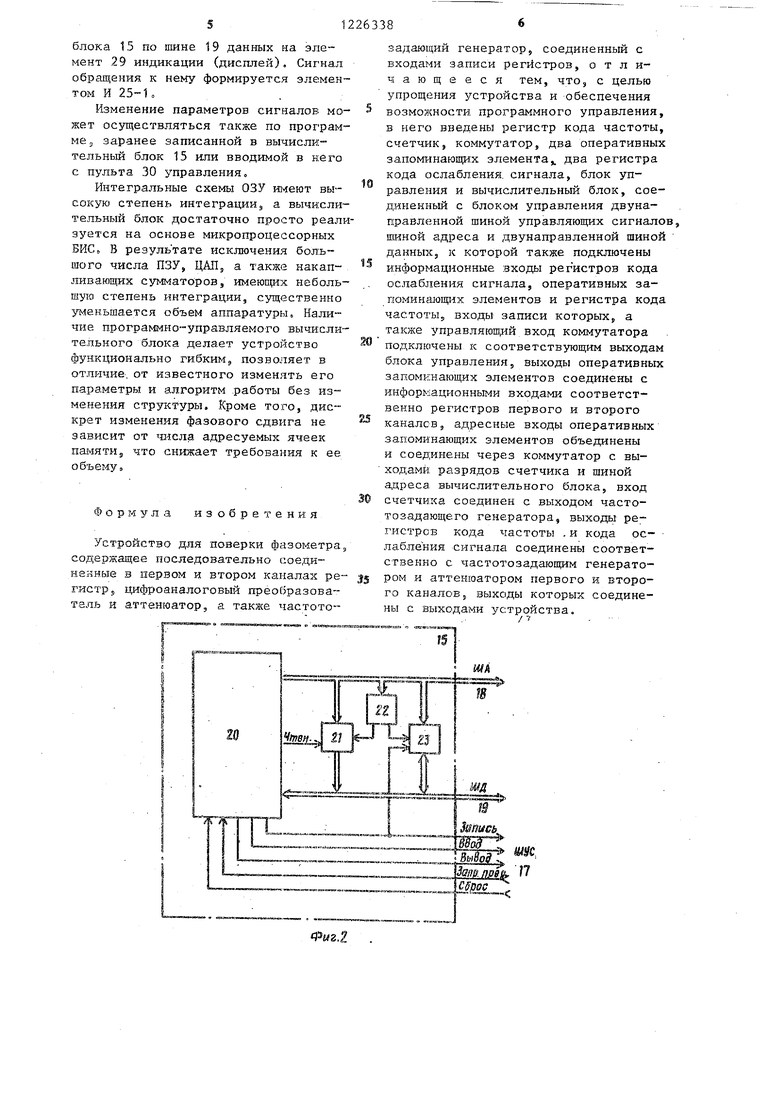

На фнг.1 приведена структурная схема устройства; на фиг. 2 и 3 - .структурные схемы возможных вариантов реализации вычислительного блока и блока управления.

Устройство (фиг.1) содержит после довательно соединенные частотозадаю- 1ДИЙ генератор 1 , счетчик 2 и .коммутатор 3, последовательно соединенные 3 обоих каналах оперативные запоминающие элементы 4(5), регистры 6(7), цифроаналоговые преобра- зователи 8(9) и аттенюаторы 10(11), с подключёнными к ним регистрами 12(1.3) ко.да ослабления сигнала, регистр 14 кода частоты, соединенный с частотозадающим генератором 1, выход которого соединен с управляющими входами регистров 6 и 7 обоих каналов, вычислительный блок 15 и блок 16 управления 5 которые соединены друг с другом двунаправленной шиной 17 управляющих сигналов, шиной 18 адреса и двунаправленной шиной 19 данных, к которой также подключеньз информационные входы оперативных запоминающих элементов 4 и 5,, регистров 12 и 13 кода ослабления сигнала и регистра 14 кода частоты,, которые входами записи соединены с соответствутащими выходами блока 16 управления, соединенного также с входо.м управления коммутатора 3 второй информационный вход которого соединен с шиной 18 адресара выход - с объединенными адресш ми входами оперативных запоминаЕощ1;1х эл маатов 4 и 5.

Вычислительный блок 15 (фиг,2) содержит микропроцессорный модуль

20,постоянный запоминающий элемент

21,дешифратор 22 и оперативньй за- поминающий элемент 23, адресные выхода микропроцессорного модуля 20 подключены к адресным входам постояного 21 и оперативного 23 запоминающих элементов 5 входам дешифрато- ра 22 .и шине 18 адреса устройства информационные входы-выходы микро- прс)цессор.ного мо.дуля 20 соединены с

информационными входами-выходами оперативного запоминающего элемента 23 и выходами постоянного запоминающего элемента 21, которые соединены уп.равляющими входами с выходами дешифратора 22 и выходами Запись, Чтение микропроцессорного модуля 20, входы-выходы управляющих сигналов которого соединены с шиной 17 Заправляющих сигналов устройства.

Блок 16 управления (фиг.З) содер- лсит дешифратор 24, к выходам которого подключен блок элементов И 25 (элементы 25-1-25-8), элемент ИЛИ 2 FlS-TpHrrep 27, элемент 28 сброса,соединенный выходом с первым входом элемента ИЛИ 26, второй вход которого соединен с выходом элемента 25-8, а выход с R-входом RS-триггера 27,, S - вход которого соединен с выходом элемента И 25-7, В блок управления входят также элемент 29 индикации и соединенные друг с другом пульт 30 управления, регистр 31 и формирователь 32, при этом управляющий вход элемента 29 индикации соединен с выходом элемента 25-1, а его информационные входы и выходы разрядов регистра 31 соединены с шиной 19 данных устройства, входы дешифратора 24 соединены с шиной 18 адреса устройства., выходы формирователя 32, элемента 28 сброса, вход записи регистра 31 и вторые входы элементов И 25 соединены с шиной 17 управляющих: сигналов устройства.

Устройство работает следующим образом.

В блох 16 управления вводят па раметры, определяющие количество спектральных составляющих, значения их амплитуд, частот и фаз в формируемых выходных сигналах. Эта информация по шине 19 данных вводится в вычислительный блок 15, которьй определяет необходимые значения частоты частотозадающего генератора 1 и коэффициентов ослабления аттенюаторов 10 и 11 и записывает соответ- ст}зующие им управляющие коды в регистр 14 кода частоты и регистры 12 и 13 кода ослабления частоты.

Далее по команде с вычислительного блока 15 блок 16 управления формирует сигнал управления коммутатором 3, который подключает адресные входы оперативных запоминающих элементов 4 и 5 к шине 18 адреса вы3

числительного блока 15. В вычислительном блоке 15 формируются отсчеты выходных сигналов, которые по шине 19 данных поочередно записываются в оперативные запоминающие элементы 4 и 5. Число отсчетов сигнала за период (N) и их разрядность определяют объем памяти, выбираемый исходя из требуемой точности задания фазового сдвига. Минимальный дискрет изменения фазы не зависит от числа адресуемых ячеек памяти и определяется разрядностью оперативных запоминающих элементов 4 и 5, регистров 6 и 7 и цифроаналоговых преобразователей 8 и 9.

По окончании записи блок 16 управления переводит оперативные запоминающие элементы 4 и 5 в режим чтения и подключает через коммутатор 3 их адресные входы к выходам разрядов счетчика 2. Текущий код счетчика 2 объемом N определяет адрес последовательно считываемых ячеек оперативных запоминающих элементов 4 и 5, содержикое которых по сигналу час- тотозадающего генератора 1 записывается в регистр 6 (7) соответствующего канала и далее с помощью ЦАП 8 и 9 преобразуется в аналоговые сигналы, подаваемые через аттенюаторы 10 и 11 на выходы устройства. Амплитудный ч фазовый спектр этих сигналов соответствует исходным параметрам, введенным в вычислительный блок 15.

При изменении одного из параметров сигнала в блоке 16 управления формируется управляющий сигнал, поступающий на вычислительный блок 15 по шине 17 управляющих сигналов, по которому выполняются все описанные подготовительные операции и осуществляется перезапись одного или обоих оперативных запоминающих элементов 4 и 5.

Структура вычислительного блока 15 и блока 16 управления зависит от используемой элементой базы. Наиболее перспективны реализация вычислительного блока 15 на основе микропроцессора. Типовая структурная схема микропроцессорного- вычислительного блока минимальной конфигурации показана на фиг.2.

В постоянном запоминающем элементе 21 хранятся программы и константы, в оперативном запоминающем эле-263384

менте 23 текущая информация, выбор соответствующего элемента осуществляется по сигналам дешифратора 22. Микропроцессорный модуль 20 вы- 5 полняет обработку и обмен информацией и связан с устройством системой адресных (шина 18 адреса), информационных (шина 19 данных) и управляющих шин (шина 17 управляющих сигна- 10 лов). Шина 17 управляющих сигналов может включать в себя сигналы записи, ввода, вывода (выходные) и запроса прерывания и сброса (входные). Блок 16 управления (фиг.З) выпол- t5 няет функции формирования управляющих сигналов, необходимых для организации обмена информацией между вычислительным блоком 15 и внешними по отношению к нему устройствами, а 0 также ввода информации с пульта управления и визуального контроля (индикации) вводимых данных и данных с вычислительного блока 15. .

Сигналы обращения (записи) к опе- 5 ративным запоминающим элементам 4 и 5, регистрам 12 и 13 кода ослабления сигнала и регистру 14 кода частоты формируются путем дешифрирования кода адреса соответствующего элемента д (дешифратор 24) и конъюкции его выходных сигналов с сигналами записи, вывода с вьтислительного блока 15 (блок элементов И 25).

Аналогично формируются два сигнала на выходах электров 25-7 и 25-8, управляющие RS-триггером 27, выходной сигнал которого определяет направление передачи информации через коммутатор 3. С помощью элемента 28 сброса производится начальная установка вычислительного блока 15 и RS-триггера 27.

В регистре 31 хранится информация о параметрах сигнала и режиме рабо- ты устройства, вводимая с пульта 30 управления. По сигналу Ввод эта информация вводится в вычислительный блок 15. Ввод информации производится либо при начальной установке устройства (по сигналу Сброс), либо при изменении состояния клавиатуры пульта 30 управления, вызывающему формирование сигнала запроса прерывания (формирователь 32), поступающего на вычислительный блок 15.

5

0

Параметры формируемого сигнала и данные о режиме работы устройства могут выводиться с вычислительного

блока 15 по шине 19 данных на элемент 29 индикации (дисплей). Сигнал обращения к нему формируется элементом И 25-Ь

Изменение параметров сигналов может осзпдествляться также по программе g заранее записанной в вычислительный блок 15 или вводимой в него с пульта 30 управления.

Интегральные схемы ОЗУ HivjeroT высокую степень интеграции, а вычи:сли- тельный блок достаточно просто реализуется на основе микропроцессорных БИС, В результате исключения большого числа ПЗУ, ЦАП, а также накапливающих сумматоров, имеюпщх неболь- myvj степень интеграции, существенно уменьшается объем аппаратуры Наличие программно--управляемого вычислительного блока делает устройство функционально гибким, позволяет в отличие, от известного изменять его параметры и алгоритм .работы без изменения структуры. Кроме того, дискрет изменения фазового сдвига не зависит от числа адресуемых ячеек пш«1ятИд что снижает требования к ее объему.

Формула изобретения

Устройстзо для поверки фазометра содержащее последовательно соединенные в первом и втором каналах ре- гистр цифроаналоговый преобразователь и аттенюатор, а также частоте

5

задающий генератор, соединенный с входами записи регистров, отличающееся тем, что, с целью упрощения устройства и обеспечения возможности, программного управления, в него введены регистр кода частоты, счетчик, коммутатор, два оперативных запом: -шающих элемента,, два регистра кода ослабления, сигнала, блок управления и вычислительный блок, соединенный с блоком управления двунаправленной шиной управляющих сигналов, кнной адреса и двунаправленной шиной данных, к которой также подключены информационные входы рег истров кода ослабления сигнала, оперативных за- помингиощих элементов и регистра кода частоты5 входы записи которых, а также управляющими вход коммутатора подключены к соответствующим выходам блока управления, выходы оперативных запоминающих элементов соединены с информационными входами соответственно регистров первого и второго каналов, адресные входы оперативных запоминающих элементов объединены и соединены через коммутатор с вы- ходами разрядов счетчика и шиной а,цреса вычислительного блока, вход счетчика соединен с выходом часто- тозадающего генератора, выходы регистров кода частоты .и кода ос- лабления сигнала соединены соответственно с частотозадаюш;им генератором и аттенюатором первого и второго каналов, выходы которых соединены с выходами устройства.

/-

ШС

ШЛ

ш

л л МУСТ7

.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Калибратор фазы | 1988 |

|

SU1647449A1 |

| Устройство для задания фазового сдвига | 1990 |

|

SU1721537A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1615803A1 |

| ЭХОЭНЦЕФАЛОСКОП | 1992 |

|

RU2031626C1 |

| Мультимикропроцессорная система | 1980 |

|

SU907551A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1741137A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

Изобретение касается радиоизмерений и может быть использовано для поверки фазометров низкочастотного и инфранизкочастотного диапазонов. Цель изобретения - упрощение устройства и обеспечение программного управления. Устройство содержит задающий генератор 1, счетчик 2, коммутатор 3, последовательно соединенные в обоих каналах оперативные запоминающие элементы 4 и 5, регистры 6 и 7.Цифроаналохювые преобразователи 8 и 9, аттенюаторы 10 и 11, регистры кода ослабления сигнала 12 и 13, регистратор 14 кода частоты, вычислительный блок 15, блок управления 16, шины 17, 18 и 19. 3 ил. ю to О5 00 СО оо Фиг,1

| Цифровое устройство для воспроизведе-Ния фАзОВыХ СдВигОВ | 1979 |

|

SU853565A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для поверки фазометров | 1982 |

|

SU1057877A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-04-23—Публикация

1984-10-15—Подача