1

Изобретение относится к автоматике и вычислительной технике, может быть использовано в системах автоматического управления объектами и является усовершенствованием устрой ства по авт. св. № 697975.

Цель изобретения - расширение диагностических возможностей по разделению неисправностей между блоками устройства.

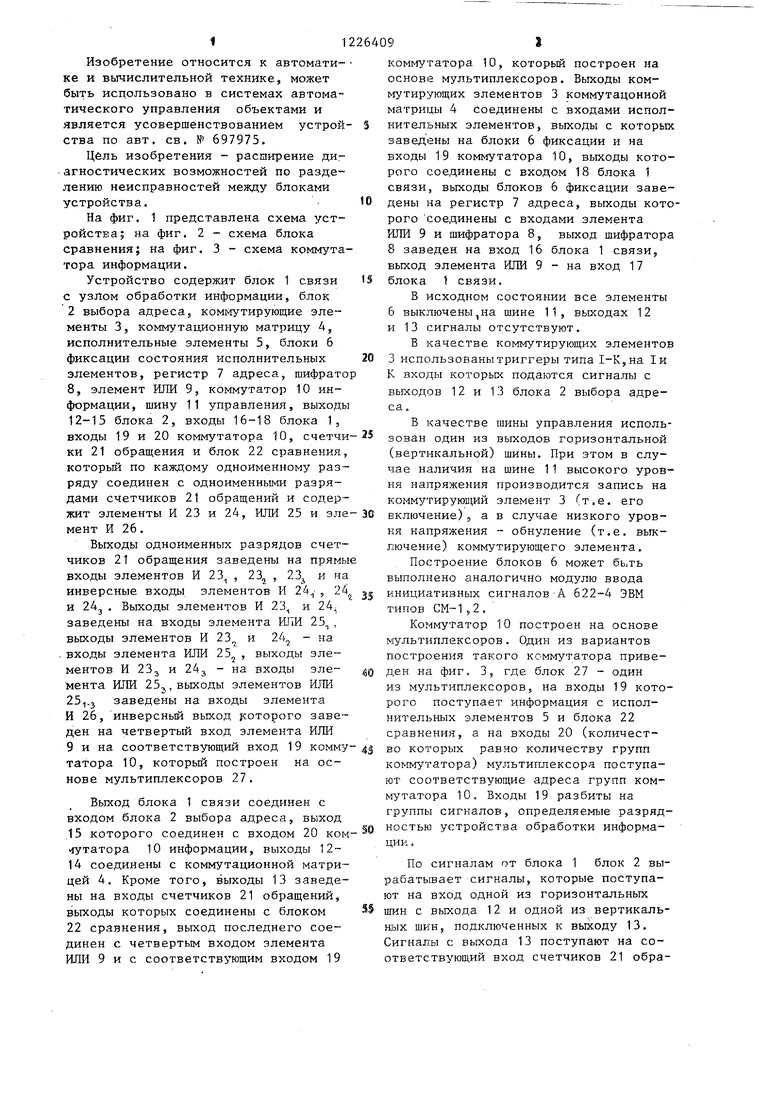

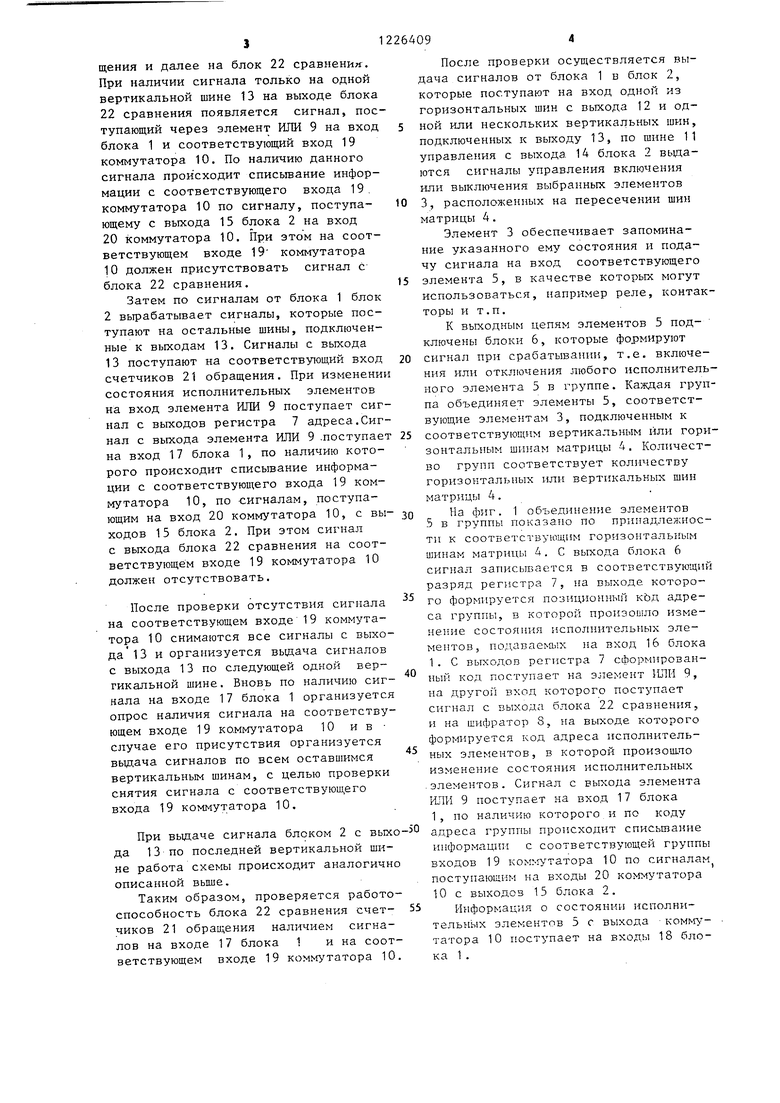

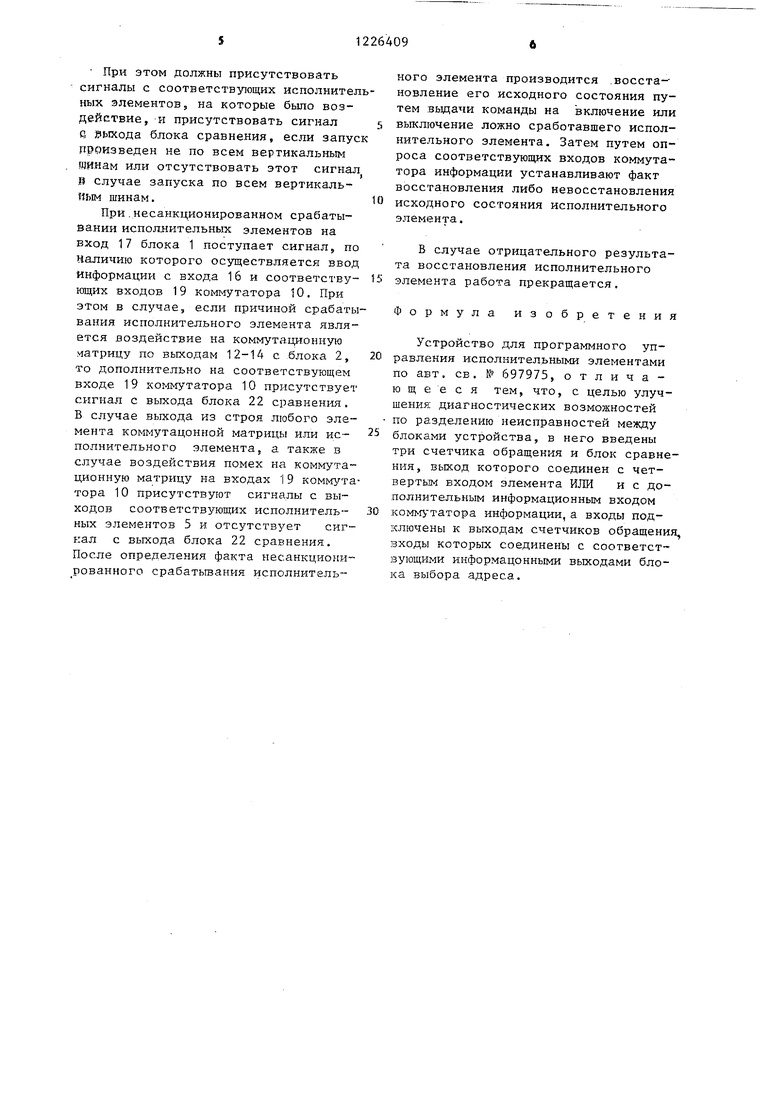

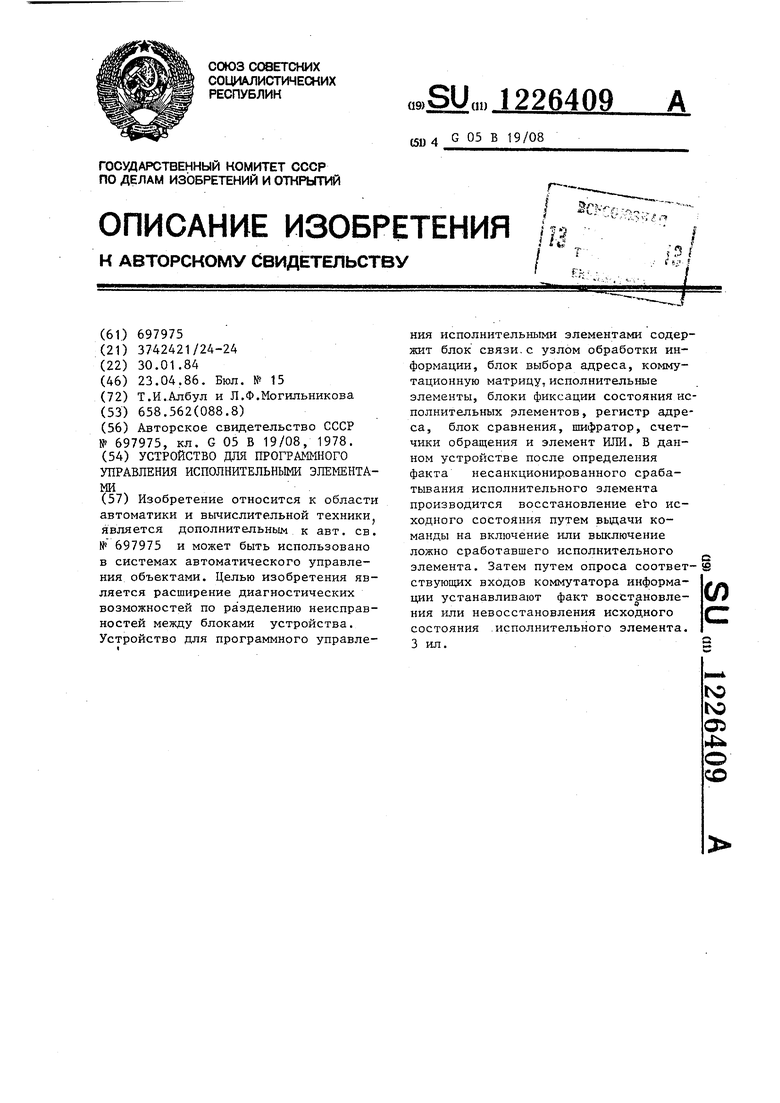

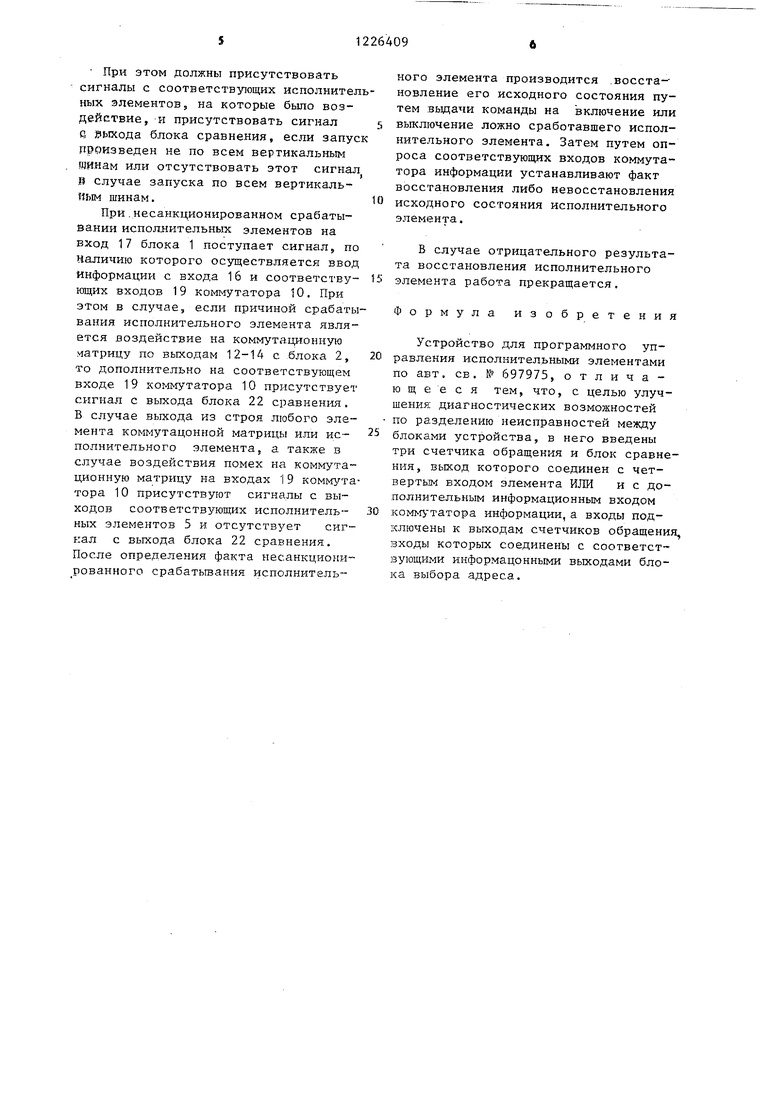

На фиг. 1 представлена схема устройства; на фиг. 2 - схема блока сравнения; на фиг. 3 - схема коммутатора информации.

Устройство содержит блок 1 связи с узлом обработки информации, блок 2 выбора адреса, коммутирующие элементы 3, коммутационную матрицу 4, исполнительные элементы 5, блоки б фиксации состояния исполнительных элементов, регистр 7 адреса, шифрат 8, элемент ИЛИ 9, коммутатор 10 информации, шину 11 управления, выход 12-15 блока 2, входы 16-18 блока 1,

В качестве шины управления испольвходы 19 и 20 коммутатора 10, счетчи-2S зован один из выходов горизонтальной ки 21 обращения и блок 22 сравнения, который по каждому одноименному разряду соединен с одноименными разрядами счетчиков 21 обращений и содержит элементы И 23 и 24, ИЛИ 25 и эле-30 мент И 26.

Выходы одноименных разрядов счетчиков 21 обращения заведены на прямые

(вертикальной) шины. При этом в случае наличия на шине 11 высокого уровня напряжения производится запись на коммутирующий элемент 3 (т.е. его включение) ,, а в случае низкого уровня напряжения - обнуление (т.е. выключение) коммутирующего элемента.

Построение блоков 6 может быть выполнено аналогично модулю ввода 35 инициативных сигналов А 622-4 ЭВМ типов СМ-1 ,, 2 .

входы элементов И 23 , 23, , 23 и на инверсные входы элементов И , 24 и 24,j . Выходы элементов И 23 и 24 заведены на входы элемента ШШ 25 , выходы элементов И 23 и 24 - на входы элемента ИЛИ 25, , выходы элементов И 23j и 24з - на входы эле- Q мента ИЛИ 25, выходы элементов ИЛИ 25,.J заведены на входы элемента И 26, инверсный выход которого заведен на четвертый вход элемента ИЛИ 9 и на соответствующий вход 19 комму-43 татора 10, который построен на основе мультиплексоров 27.

35

40

§0

Выход блока 1 связи соединен с входом блока 2 выбора адреса, выход .15 которого соединен с входом 20 ком чутатора 10 информации, выходы 12- 14 соединены с коммутационной матрицей 4. Кроме того, выходы 13 заведены на входы счетчиков 21 обращений, выходы которых соединены с блоком 22 сравнения, выход последнего соединен с четвертым входом элемента ИЛИ 9 и с соответствующим входом 19

коммутатора 10, который построен на основе мультиплексоров. Выходы коммутирующих элементов 3 коммутацонной матрицы 4 соединены с входами исполнительных элементов, выходы с которых заведены на блоки 6 фиксации и на входы 19 коммутатора 10, выходы которого соединены с входом 18 блока 1 связи, вьпсоды блоков 6 фиксации заведены на регистр 7 адреса, выходы которого соединены с входами элемента ИЛИ 9 и шифратора 8,, выход шифратора 8 заведен на вход 16 блока 1 связи, выход элемента ИЛИ 9 - на вход 17 блока 1 связи,

В исходном состоянии все элементы 6 выключены,на шине 11, выходах 12 и 13 сигналы отсутствуют.

В качестве коммутирующих элементов 3 использованы триггеры типа 1-К,на 1и К входы которых подаются сигналы с выходов 12 и 13 блока 2 выбора адреса,

В качестве шины управления использован один из выходов горизонтальной

2S зован один из выходов горизонтальной 30

Q 43

(вертикальной) шины. При этом в случае наличия на шине 11 высокого уровня напряжения производится запись на коммутирующий элемент 3 (т.е. его включение) ,, а в случае низкого уровня напряжения - обнуление (т.е. выключение) коммутирующего элемента.

Построение блоков 6 может быть выполнено аналогично модулю ввода 35 инициативных сигналов А 622-4 ЭВМ типов СМ-1 ,, 2 .

Коммутатор 10 построен на основе мультиплексоров. Один из вариантов построения такого коммутатора приве- 40 дев на фиг. 3, где блок 27 - один

из мультиплексоров, на входы 19 которого поступает информация с исполнительных элементов 5 и блока 22 сравнения, а на входы 20 (количество которых равно количеству групп коммутатора) мультиплексора поступают соответствующие адреса групп коммутатора 10, Входы 19 разбиты на группы сигналов, определяемые разряд- §0 ностью устройства обработки информации.

По сигналам от блока 1 блок 2 вырабатывает сигналы, которые поступают на вход одной из горизонтальных шин с вькода 12 и одной из вертикальных шин, подключенных к выходу 13. Сигналы с выхода 13 поступают на соответствующий вход счетчиков 21 обращения и далее на блок 22 сравнение. При наличии сигнала только на одной вертикальной шине 13 на выходе блока 22 сравнения появляется сигнал, поступающий через элемент ИЛИ 9 на вход блока 1 и соответствующий вход 19 коммутатора 10. По наличию данного сигнала происходит списьгеание информации с соответствующего входа 19. коммутатора 10 по сигналу, поступающему с выхода 15 блока 2 на вход 20 коммутатора 10. При этом на соответствующем входе 19 коммутатора 10 должен присутствовать сигнал с блока 22 сравнения.

Затем по сигналам от блока 1 блок 2 вьфабатывает сигналы, которые поступают на остальные шины, подключенные к выходам 13. Сигналы с выхода 13 поступают на соответствующий вход счетчиков 21 обращения. При изменении состояния исполнительных элементов на вход элемента ИЛИ 9 поступает сигнал с выходов регистра 7 адреса.Сигнал с выхода элемента ИЛИ 9 .поступает 25 соответствующим вертикальным или гори

на вход 17 блока 1, по наличию которого происходит списывание информации с соответствующего входа 19 коммутатора 10, по сигналам, поступающим на вход 20 коммутатора 10, с вы- ходов 15 блока 2. При этом сигнал с выхода блока 22 сравнения на соответствующем входе 19 коммутатора 10 должен отсутствовать.

После проверки отсутствия сигнала на соответствующем входе 19 коммутатора 10 снимаются все сигналы с выхода 13 и организуется выдача сигналов с выхода 13 по следующей одной вертикальной шине. Вновь по наличию сигнала на входе 17 блока 1 организуется опрос наличия сигнала на соответствующем входе 19 коммутатора 10 и в случае его присутствия организуется выдача сигналов по всем оставшимся вертикальным шинам, с целью проверки снятия сигнала с соответствуюш,его входа 19 коммутатора 10.

При вьщаче сигнала блоком 2 с выхо да 13 по последней вертикальной шине работа схемы происходит аналогично описанной вьш1е.

Таким образом, проверяется работоспособность блока 22 сравнения счет- чиков 21 обращения наличием сигналов на входе 17 блока 1 и на соответствующем входе 19 коммутатора 10

После проверки осуществляется выдача сигналов от блока 1 в блок 2, которые поступают на вход одной из горизонтальных шин с выхода 12 и одной или нескольких вертикальных шин, подключенных к выходу 13, по шине 11 управления с выхода 14 блока 2 в1еда- ются сигналы управления включения или выключения выбранных элементов

3, расположенных на пересечении шин матриды 4.

Элемент 3 обеспечивает запоминание указанного ему состояния и подачу сигнала на вход соответствующего

элемента 5, в качестве которых могут использоваться, например реле, контакторы и т.п.

К выходным цепям элементов 5 подключены блоки 6, которые формируют

сигнал при срабатывании, т.е. включения или отключения любого исполнительного элемента 5 в группе. Каждая группа объединяет элементы 5, соответствующие элементам 3, подключенным к

зонтальным шинам матрицы 4. Количество групп соответствует количеству горизонтальных или вертикальных шин матрицы 4.

На фиг. 1 объединение элементов 5 в группы показано по принадлежности к соответствукидим горизонтальным и1инам матрицы 4. С выхода блока 6 сигнал записывается в соответствующий разряд регистра 7, на выходе которого формируется позиционный кЬд адреса группы, в которой произо1лло изменение состояния исполнительных элементов, подаваеьалх на вход 16 блока 1. С выходов регистра 7 сформированный код поступает на элемент ИЛИ 9, на Apyroii вход которого поступает сигнал с выхода блока 22 сравнения, и на шифратор 8, на выходе которого формируется код адреса исполнительных элементов, в которой произошло изменение состояния исполнительных элементов. Сигнал с выхода элемента ИЛИ 9 поступает на вход 17 блока 1, по наличию которого и по коду адреса группы про15сходит списьшание информации с соответствующей группы входов 19 комг. утатора 10 по сигналам поступающим на входы 20 коммутатора 10 с выходов 15 блока 2.

Информация о состоянии исполнительных элементов 5 о выхода KOMNrs - татора 10 поступает на входы 18 блока 1 .

При этом должны присутствовать сигналы с соответствующих исполнителных элементов, на которые было воздействие, -и присутствовать сигнал С выхода блока сравнения, если запус .рроизведен не по всем вертикальным шинам или отсутствовать этот сигнал В Случае запуска по всем вертикальным шинам.

При.несанкционированном срабатывании исполнительных элементов на вход 17 блока 1 поступает сигнал, по Наличию которого осуществляется ввод Информации с входа 16 и соответству- ющих входов 19 коммутатора 10. При этом в случае, если причиной срабатывания исполнительного элемента является воздействие на коммутационную матрицу по выходам 12-14 с блока 2, то дополнительно на соответствующем входе 19 коммутатора 10 присутствует сигнал с выхода блока 22 сравнения, В случае выхода из строя любого элемента коммутацонной матрицы или ис- полнительного элемента, а также в случае воздействия помех на коммутационную матрицу на входах 19 коммутатора 10 присутствуют сигналы с выходов соответствующих исполнитель-- ных элементов 5 и отсутствует сиг- кал с выхода блока 22 сравнения. После определения факта несанкционированного срабатывания исполнительного элемента производится .восста- новление его исходного состояния путем выдачи команды на включение или выключение ложно сработавшего исполнительного элемента. Затем путем опроса соответствующих входов коммутатора информации устанавливают факт восстановления либо невосстановления исходного состояния исполнительного элемента.

В случае отрицательного результата восстановления исполнительного элемента работа прекращается.

Формула изобретени

Устройство для программного уп- равлешия исполнительными элементами по авт. св. № 697975, отличающееся тем, что, с целью улучшения диагностических возможностей по разделению неисправностей между блоками устройства, в него введены три счетчика обращения и блок сравнения, выход которого соединен с чет- вертьм входом элемента ИЛИ и с дополнительным информационным входом коммутатора информации, а входы подключены к выходам счетчиков обращени входы которых соединены с соответствующими информацонными выходами блока выбора адреса.

иг.1

S/JOH с/)

-F/

Г-10

201

Щ

2A

/J

2

rs

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для контроля сложных релейных распределителей | 1985 |

|

SU1252780A1 |

| Устройство ввода-вывода матричной вычислительной системы | 1987 |

|

SU1529234A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для передачи и приема команд телеуправления | 1988 |

|

SU1667135A1 |

| Система доступа к памяти | 1983 |

|

SU1151974A1 |

| Программное устройство управления | 1986 |

|

SU1339558A1 |

| Система для контроля сложных релейных распределителей | 1987 |

|

SU1522209A2 |

| Программное устройство управления | 1983 |

|

SU1173414A1 |

| Устройство для программного управления исполнительными элементами | 1978 |

|

SU697975A1 |

Изобретение относится к области автоматики и вычислительной техники является дополнит ел ьньш к авт. св. № 697975 и может быть использовано в системах автоматического управления объектами. Целью изобретения является расширение диагностических возможностей по разделению неисправностей между блоками устройства. Устройство для программного управления исполнительными элементами содержит блок связи.с узлом обработки информации, блок выбора адреса, коммутационную матрицу,исполнительные элементы, блоки фиксации состояния исполнительных элементов, регистр адре- са, блок сравнения, шифратор, счетчики обращения и элемент ИЛИ. В данном устройстве после определения факта несанкционированного срабатывания исполнительного элемента производится восстановление исходного состояния путем вьдачи команды на включение или выключение ложно сработавшего исполнительного элемента. Затем путем опроса соответ- S ствующих входов коммутатора информации устанавливают факт восстановления или невосстановления исходного состояния исполнительного элемента. 3 ил. (Л to ю о: 4 О СО

2J,

2f

20i

20f

rs

27

fS

5

1 Щ

Риг. 2

Редактор Е.Папп

Составитель И,Швец

Техред И,Попович Корректор Т,Кол(

Заказ 2131/46 Тираж 836 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открыт1-1й 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

20f

7S

27

fS

20

PasJ

.(

| Устройство для программного управления исполнительными элементами | 1978 |

|

SU697975A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-04-23—Публикация

1984-01-30—Подача