группе адресных входов соответствующего мультиплексора данных, группа выходов приоритетности запросов блок обработки запросов подключена к соответствующим группам управляющих входов мультиплексора, адреса, мультиплексора записываемых данных и группе входов очередности выполнения запросов блока индивидуального управления, выход граничного адреса каждого блока памяти подключен к входу адреса соответствующедо блока обработки запросов, причем блок индивидуального управления содержит ждущий генератор импульсов, элемент ИЛИ, счетчик, дешифратор, триггер, коммутатор, группу из М элементов И, причем вход запуска ждущего генератора подключен к выходу элемента ИЛИ, входы которого подключены к вхо дам приема запросов блока, выход генератора импульсов подключен к счетному входу счетчика, выход которого подключен к входу дешифратора, выход которого подключен к испол нительному выходу блока, первым входам элементов И группы, входу сброса счетчика, входу установки триггера, выход которого подключен к объединен ным вторым входам элементов И группы входу запрета запуска ждущего генератора импульсов, входу разрешения сброса счетчика, выходы элементов И группы подключены к выходам записи блока, третьи входы элементов И группы подключены к входам очередности выполнения запросов блока, первая группа информационных входов коммутатора подключена к входам очередности выполнения запросов блока, вторая группа информационных входов . коммутатора подключена к входам занятости блока, выход коммутатора подключен к управляющему входу триггера . 2. Система по п. 1, отличающаяся тем, что блок обработки запросов содержит регистр, узел приоритета и М схем сравнения, причем первые входы схем сравнения подключены к входам запросов блока, вторые входы схем сравнения подключены к входам адреса блока, выходы схем сравнения подключены к информационным входам регистра, а также к группе информационных выходов блока, управляющий вход регистра подключен к управляющему входу блока, выходы регистра подключены к входам узла приоритета, выходы которого являются выходами приоритетности блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией между абонентами | 1986 |

|

SU1383376A1 |

| Оперативное запоминающее устройство | 1982 |

|

SU1088066A1 |

| Измеритель аналоговых сигналов | 1988 |

|

SU1599869A1 |

| Буферное запоминающее устройство | 1981 |

|

SU1022221A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Устройство для сопряжения телеграфных линий связи с ЦВМ | 1988 |

|

SU1603392A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Устройство отладки микропрограммных блоков | 1988 |

|

SU1541617A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

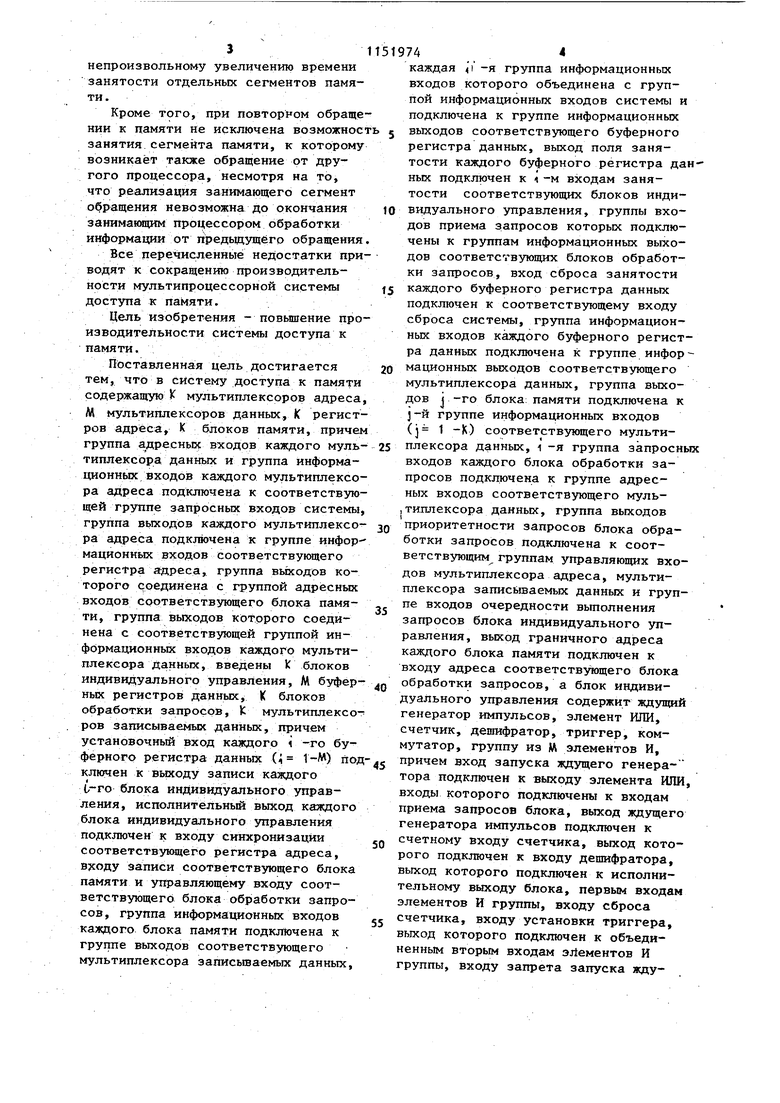

1. СИСТЕМА ДОСТУПА К ПАМЯТИ, содержащая К мультиплексоров адреса, М мультиплексоров данных, К регистров адреса, К блоков памяти, причем группа адресных входов каждого мультиплексора данных и группа информационных входов каждого мультиплексора адреса подключена к соответствующей группе запросных входов системы, группа выходов каждого мультиплексора адреса подключена к группе информационных входов соответствующего регистра адреса, группа выходов которого соединена с группой адресных входов соответствующего блока памяти, группа выходов которого соединена с соответствующей группой информационных входов КЕ1ЖДОГО мультиплексора данных, отличающаяся тем, что, с целью повышения производительности, в нее введены К блоков индивидуального управления, М буферных регистров данных, К блоков обработки запросов, 1( мультиплексоров записываемых данных, причем установочный вход каждого i -го буферного регистра данных ( 1 ) подключен к выходу записи каждого -го блока индивидуального управления, исполнительный выход каждого блока индивидуального управления подключен к входу синхронизации соответствующего регистра адреса, входу записи соответствующего блока памяти и управляющему входу соответствующего блока обработки запросов, группа информационных входов каждого блока памяти подключена к группе выходов соответствующего мультиплексо ра записываемых данных, каждая ( -я группа информационных входов которого объединена с группой информационных входов системы и подключена к группе информационных (Л выходов соответствующего буферного с: регистра данных, выход поля занятости каждого буферного регистра данных подключен к -м входам занятости соответствующих блоков индивидуального управления, группы входов приема запросов которых подСП ключены к группам информационных выходов, соответствующих блоков обрасо ботки запросов, вход сброса занятости каждого буферного регистра данных подключен к соответствующему входу сброса системы, группа информационных входов каждого буферного регистра данных подключена к группе информационных выходов соответствующего мультиплексора данных, группа выходов J -го блока памяти подключена к j -и группе информационных входов ( 3 ) соответствующего мультиплексора данных, i -я группа запросных входов каждого блока обработки запросов подключена к

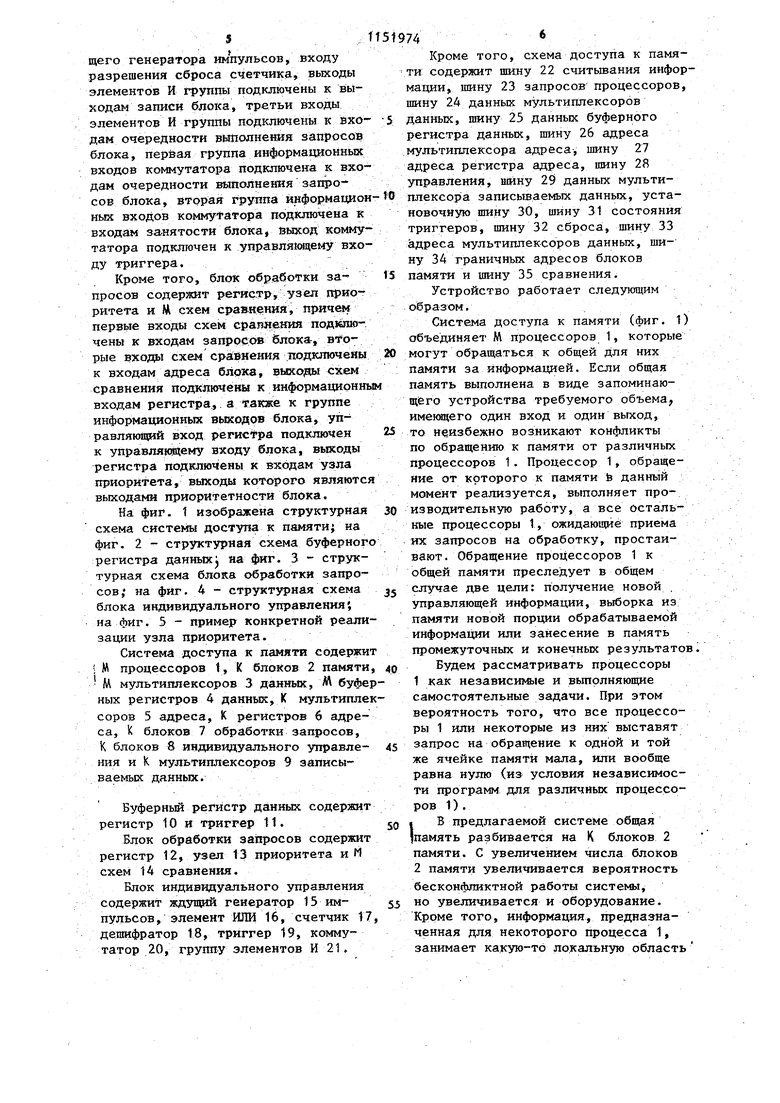

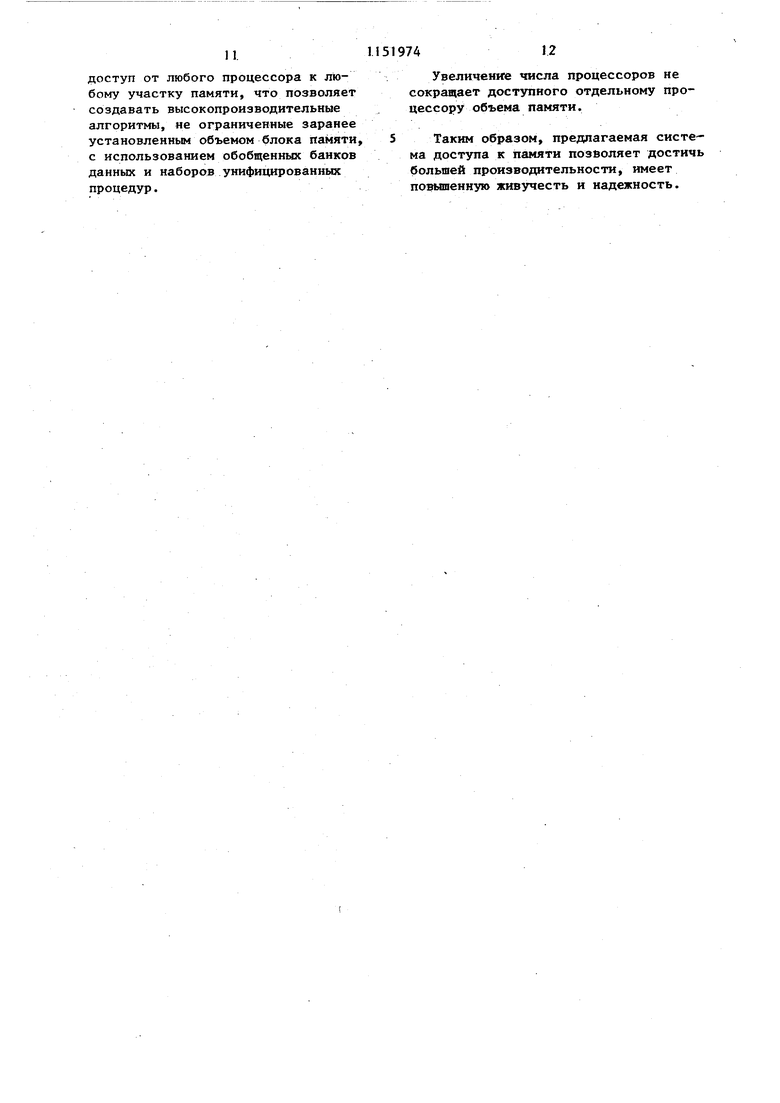

Изобретение относится к вычислительной технике и может быть использовано для построения мультипроцессо ных систем и высокопроизводительных вычислительных средств. Известны системы, допускающие одновременный доступ к памяти двух и более процессоров, содержащие сег ментированную память и процессоры, один из которых имеет доступ к всем сегментам, а остальные - к отдельным сегментам памяти lj . Недостатками такой системы являются ограничения на доступные объемы памяти для всех, кроме одного, проце соров и центрапизация управления доступом в одном процессоре, что приводит к сложной технической реали зации при использовании в системе более двух процессоров и снижению жизнеспособности системы. Наиболее близкой по технической сущности к изобретению является мультипроцессорная система доступа к памяти, содержащая процессоры, мультиплексоры данных, устройства запоминания адреса, мультиплексоры адреса и сегменты памяти 2j. Недостатками этой системы доступа к памяти являются доступность всего объема памяти только для одного из процессоров, низкое быстро действие по обработке запросов, вследствие их синхронной обработки, отсутствие приоритета по времени поступления запросов, отсутствие буферизации поступакицей и считываемой информации, что приводит к непроизвольному увеличению времени занятости отдельных сегментов памяти. Кроме того, при повторном обраще нии к памяти не исключена возможнос занятия сегмента памяти, к которому возникает также обращение от другого процессора, несмотря на то, что реализация занимающего сегмент обращения невозможна до окончания занимающим процессором обработки информации от прецыкущёго обращения Все перечисленные недостатки при водят к сокращению производительности мультипроцессорной системы доступа к памяти. Цель изобретения - повышение про изводительности системы доступа к памяти. Поставленная цель достигается тем, что в систему доступа к памяти содержащую К мультиплексоров адреса М мультиплексоров данных, К регистров адреса, К блоков памяти, причем группа адресньк входов каждого мультиплексора данных и группа информационных входов каждого мультиплексора адреса подключена к соответствующей группе запросных входов системы группа вькодов каждого мультиплексора адреса подключена к группе информационных входов соответствующего регистра адреса, группа вькодов которого соединена с группой адресных входов соответствующего блока памяти, группа выходов которого соединена с соответствующей группой информационных входов каждого мультиплексора данных, введены К блоков индивидуального управления, М буферных регистров данных, К блоков обработки запросов, )С мультиплексоров записываемых данных, причем установочный вход каждого i -го буферного регистра данных (i, 1-W) под ключен к выходу записи каждого Ь-го блока индивидуального управления, исполнительный выход каждого блока индивидуального управления подключен к входу синхронизации соответствующего регистра адреса, ВХОДУ записи соответствующего блока памяти и управляющему входу соответствующего блока обработки запросов , группа информационных входов каждого блока памяти подключена к группе выходов соответствующего мультиплексора записьшаемых данных. каждая i -я группа информационных входов которого объединена с группой информационных входов системы и подключена к группе информационных выходов соответствующего буферного регистра данных, выход поля занятости каждого буферного регистра данных подключен к i -м входам занятости соответствующих блоков индивидуального управления, группы входов приема запросов которых подключены к группам информационных вьгходов соответствующих блоков обработки запросов, вход сброса занятости каждого буферного регистра данных подключен к соответствующему входу сброса системы, группа информационных входов каждого буферного регистра данных подключена к группе информационных выходов соответствующего мультиплексора данных, группа выходов j -го блока: памяти подключена к J-и группе информационных входов (i 1 -К) соответствующего мульти-t 1 плексора данных, i -я группа запросных входов каждого блока обработки запросов подключена к группе адресных входов соответствующего мультиплексора данных, группа выходов приоритетности запросов блока обработки запросов подключена к соответствующим группам управляющих входов мультиплексора адреса, мультиплексора записьшаемых данных и группе входов очередности вьтолнения запросов блока индивидуального управления, выход граничного адреса каждого блока памяти подключен к входу адреса соответствующего блока обработки запросов, а блок индивидуального управления содержит ждущий генератор импульсов, элемент ИЛИ, счетчик, дещифратор, триггер, коммутатор, группу из М элементов И, причем вход запуска ждущего генера- тора подключен к выходу элемента ИЛИ, входы которого подключены к входам приема запросов блока, выход лсдущего генератора импульсов подключен к счетному входу счетчика, выход которого подключен к входу дещифратора, выход которого подключен к исполнительному выходу блока, первым входам элементов И группы, входу сброса счетчика, входу установки триггера, выход которого подключен к объединенным вторым входам элементов И группы, входу запрета запуска ждущего генератора импульсов, входу разрешения сброса счетчика, выходы элементов И группы подключены к выкодам записи блока, третьи входы элементов И группы подключены к вхо дам очередности вдаолнения запросов блока, первая группа информационных входов коммутатора подключена к вхо дам очередности выполнения запросов блока, вторая группа ИНформацио ных входов коммутатора подключена к входам за нятости блока, выход комму татора подключен к управляющему вхо ду триггера. Кроме того, блок обработки запросов содержит регистр узел приоритета и N1 схем сравнения;, причем первые входы схем срапнения подкнючены к входам запросов блока, вторые входы схем срайнения подключены к входам адреса блока, выходы схем сравнения подключены к информационн входам регистра, а также к группе информационных выходов блока, управляюй(ий вход регис-гра подключен к управля( входу блока, выходы регистра подключены к входам узла приоритета, выходы которого являютс выходами приоритетности блока. На: фиг. 1 изображена структурная схема системы доступа к памяти; на фиг. 2 - структурная схема буферног регистра данныхj на фиг. 3 - структурная схема блока обработки запросов; на фиг. 4 - структурная схема блока индивидуального управления , на фиг. 5 - пример конкретной реали зации узла приоритета. Система доступа к памяти содержи 1 М процессоров t, К блоков 2 памяти М мультиплексоров 3 данных, Л буфе ных регистров 4 данных, К мультипле соров 5 адреса, К регистров 6 адреса, К блоков 7 обработки запросов, К блоков 8 индивидуального управления и К. мультиплексоров 9 записываемых данных. Буферный регистр данньлх содержит регистр 10 и триггер 11. Блок обработки запросов содержит регистр 12, узел 13 приоритета иМ схем 14 сравнения. Блок индивидуального управления содержит ждущий генератор 15 импульсов, элемент ИЛИ 16, счетчик 17 дешифратор 18, триггер 19, коммутатор 20, группу элементов И 21. 74 Кроме того, схема доступа к памяти содержит шину 22 считьтания информации, шину 23 запросов процессоров, шину 24 данных мультиплексоров данных, шину 25 данных буферного регистра данных, шину 26 адреса мультиплексора адреса, шину 27 адреса регистра адреса, шину 28 управления, шину 29 данных мультиплексор а записываемых данных, установочную ШИНУ 30, шину 31 состояния триггеров, шину 32 сброса, шину 33 адреса мультиплексоров данных, шину 34 граничных адресов блоков памяти и шину 35 сравнения. Устройство работает следующим образом. Система доступа к памяти (фиг. 1) объединяет М процессоров 1, которые могут обращаться к общей для них памяти за информацией. Если общая память выполнена в виде запоминающ его устройства требуемого объема, имекицего один вход и один выход, то неизбежно возникают конфликты по обращению к памяти от различных процессоров 1. Процессор 1, обращение от которого к памяти b данный момент реализуется, выполняет производительную работу, а все остальные процессоры 1, ожидающие приема их запросов на обработку, простаивают. Обращение процессоров 1 к общей памяти преследует в общем случае две цели: получение новой управляющей информации, выборка из памяти новой порции обрабатываемой информации или занесение в память промежуточных и конечных результатов. Будем рассматривать процессоры 1как независи1 |е и вьтрлняющие самостоятельные задачи. При этом вероятность того, что все процессоры 1 или некоторые из них выставят запрос на обращение к одной и той же ячейке памяти мала, или вообще равна нулю (из условия независимости программ для различных процессоров 1). В предлагаемой системе общая щамять разбивается на К блоков 2 памяти. С увеличением числа блоков 2памяти увеличивается вероятность бесконфликтной работы систе, но увеличивается и оборудование. Кроме того, информация, предназначенная для некоторого процесса 1, занимает какую-то локальную область памяти и пересечение этих областей для различных процессоров незначительно (обычно это пересечение происходит на общесистемных организующих участках программы). Если объем блока 2 памяти выбран меньшим или. равньм минимальному объему информации, требуемому для какого-либо процессора 1, а процессоры 1 характеризуются примерно оди наковым быстродействием, то большая часть (или все) обращений от раэлич ньк процессоров 1 осуществляется к различньгм блокам 2 памяти. Это объясняется тем, что в блоках пере сечения, т.е. в блоках, содержащих .окончание задачи для одного процессора Г и начало для другого, обычно размещаются, информация; для обработк промежуточные результаты одного про цессора 1 и управляющая информация для другого. Кроме того, необходима учитывать конкретные особенности алгоритмов различных задач. Информация считывается из j -го блока 2 памяти (шины 22) по запросу от i -го процессора Т (шины 23) через -и мультиплексор 3 данных (шины 24) и t -и буферный регистр 4 данных (шины 25) в « -и процессор В системе имеется W мультиплексоро 3 данных и буферных регистров 4 дан ных в соответствии с числом процессоров 1. Адрес считываемых или записываем данных через -и мультиплексор 5 а реса заносится по шине 26 на регист 6 адреса, выход 27 которого соедине с адресными входами блока 2 памяти. Включение j-го блока 2 памяти в работу осущест&ляетёя после прием обращенного к нему запроса в j -и блок 7 обработки запросов и управляется сигналами, формируемыми j -м устройством 8 индивидуального управ лёния (шины 28)., Информация, записываемая из -г процессора 1 в i -и блок 2 памяти, по шинам 23 заносится через i -и мультиплексор 3 данных (вюны 24) на -и буферный регистр 4 данных и с выходных пшн 25 буферного регистра 4 данных через j -и мультиплексор 9 записываемых данных по ши нам 29 поступает на информационный вход j -го блока 2 памяти. На фиг. 2 приведена структурная схема буферного регистра 4 д1анньгх. .который содержит регистр 10, разрядность которого С определяется требуемым форматом перемещаемой .между процессорами 1 и блоками 2 памяти информацией, и триггер И. Последний устанавливается в единичное состояние по установочным входам импульсов, поступающим по шинам 30 из блоков 8 индивидуального управления. Этим же импульсом производится прием инфо1змации с шин 24 на регистр 10. Выход триггера 11 (шина 3t) сигнализирует о наличии в регистре 10 запрашиваемой информации. Установка в единичное состояние триггера 11 запрещает прием (с занятием какого-либо блока 2 памяти) запроса от процессора 1, которому соответствует установленный триггер 11. Это позволяет обеспечить прием на обработку запроса от другого процессора 1 имеющего более низкий приоритет, в то время, когда более приоритетный процессор 1 занят на приеме ранее подготовленной информации и не готов к приему новой. Сброс триггера 11 осуществляется сигналом, поступающим по шйне 32 от соответствующего процессора 1, по окончании в нем операций по приему информа1щи с буферного регистра и данных, т.е. когда дальнейшее хранение информации в буферном регистре 4 данных не требуется. Количество регистров 4 данных и мультиплексоров 3 данных в системе равно числу процессоров Т и между ними установлено взаимооднозначное соответствие. Мультиплексор 9 записываемых данных, число которых в системе равно числу блоков 2 памяти, представляет собой М - входовых мультиплексоров с общей адресной частью, на которую по шинам 33 подается из соответствуют|вго блока 7 обработки запросов адресная комбинация выбирающая источник записываемых данных. I . . Мультиплексоры 3 данных представляют собой совокупность из К входовых мультиплексоров с общими адресными входами. Мультиплексоры 5 адреса представляют собой совокупность М -входовых мультиплексоров с общими адресными входами, число которых соответствует числу разрядов в адресной информации для блока 2 памяти.

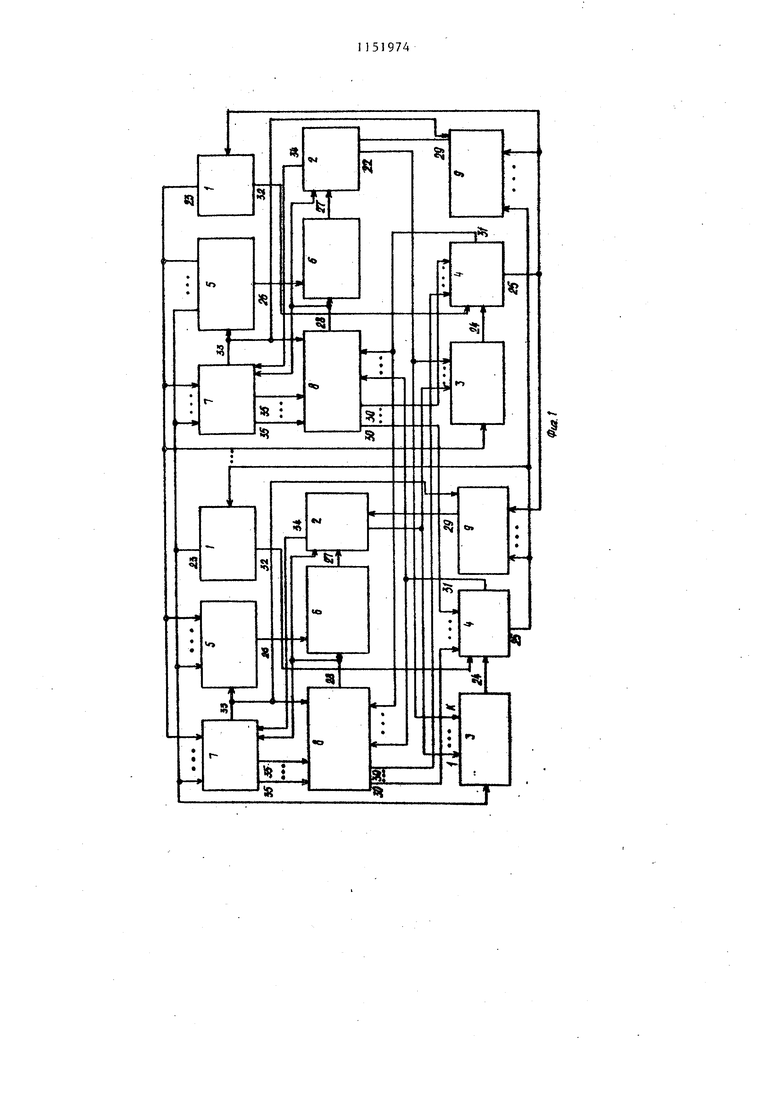

Регистр 10 является и разрядным регистром с Ц дизъюнктивно соединенными входами синхронизации, на которые по шинам 30 поступают исполнительные импульсы от того из К блоков 8 индивидуального управления, который обрабатьтает запрос, соответствующий рассматриваемому регистру 4 данных. Эти же импульсы поступают одновременно на дизъюнктивно соединенные входы установки в единицу (5) триггера It, являющегося S -триггером, на вход R поступает импульс сброса от подключенного к шинам внешней связи (которыми являются шины 23j 25 и 32) процессора 1.

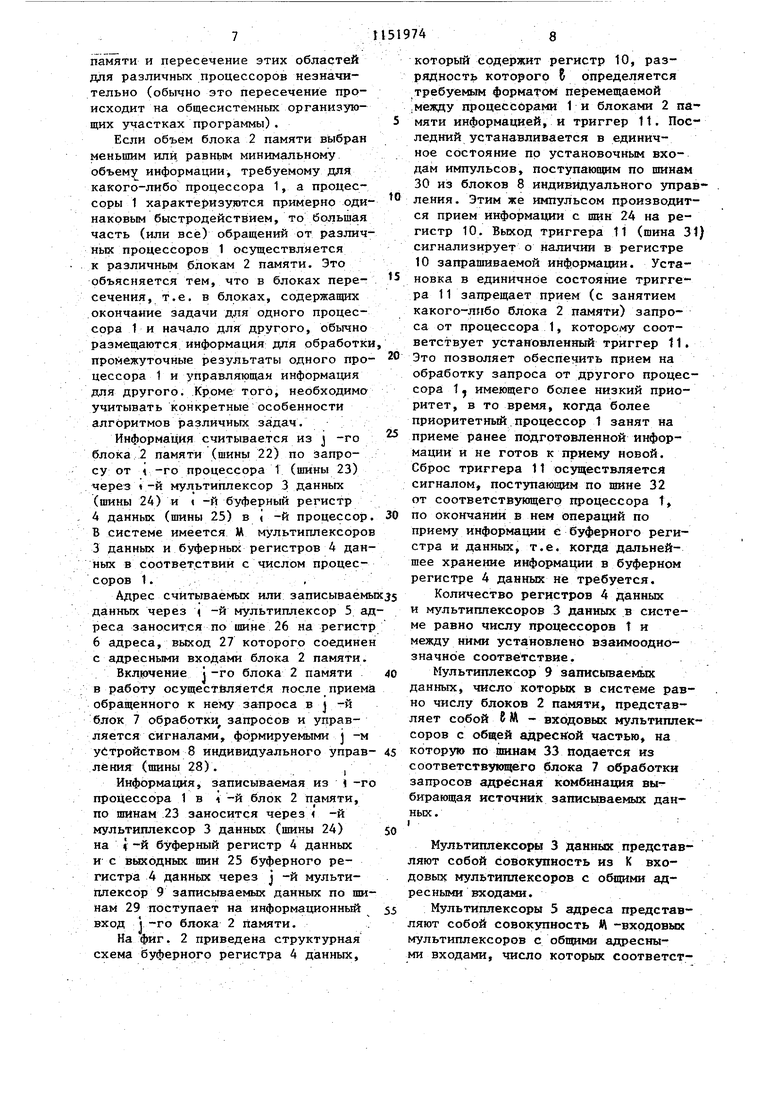

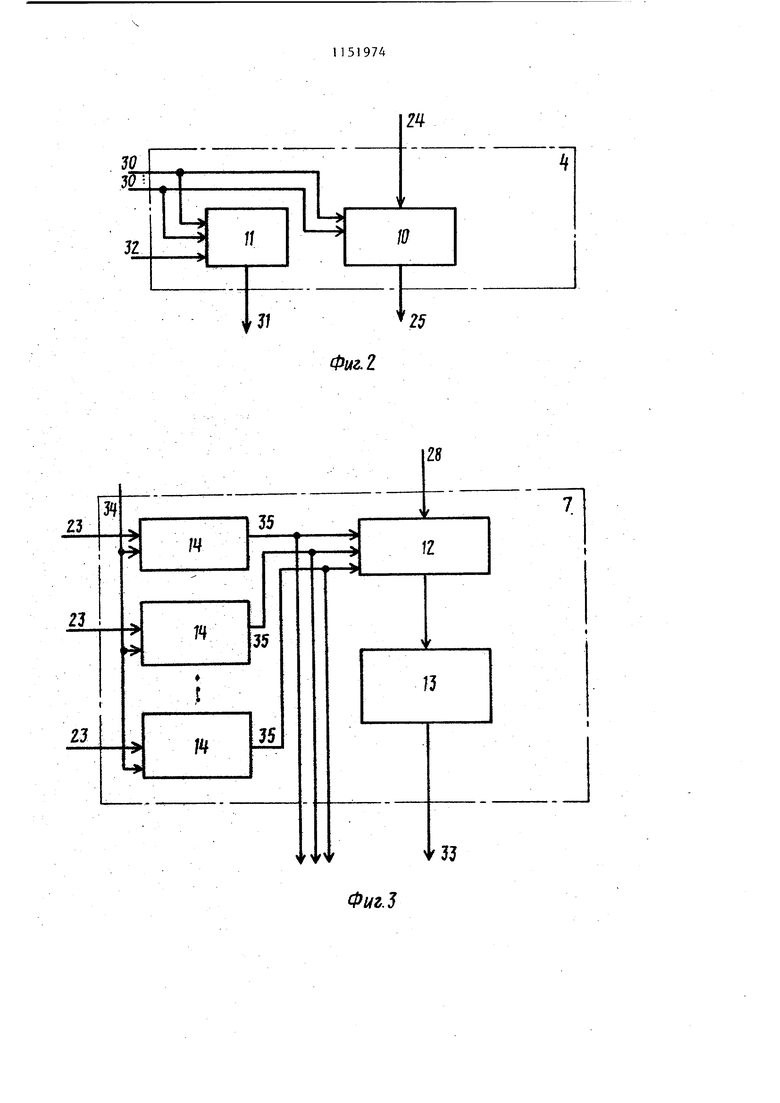

Блок 7 обработки запросов (фиг. 3 содержит регистр 12, на который по шинам 23 от процессоров 1 помещаются соответствутощие данному блоку 2 пймяти запросы. Записью запросов в регистр 12 управляет блок 8 индивидуального управления по шинам 28. Запросы проверяются на соответствие данному блоку 2 памяти на схемах 14 сравнения сравнением с граничными адресами, индивидуальными для каждого блока 2 памяти (шины 34). Выходные шины 35 схем 14 сравнения соединены с информационными входами регистра 12, а также с входами блока 8 индивидуального управления для запуска временной диаграммы обработки запросов.

Запросы, записанные в регистр 12, поступают на узел 13 приоритета, где определяется очередность выполнения запросов , и по шине 33 наиболее приоритетный из имеющихся запросов поступает на соответствующие входы мультиплексора 5 адреса, мультиплексора 9 записьгоаемых данных и блока 8 индивидуального управления. По окончании обработки запроса производится новый прием в регистр 12.

Таким образом, при одновременном поступлении нескольких обращений к одному блоку 2 памяти все запросы принимаются на р егистр 12, но через узел 13 приоритета проходит только один из них (наиболее приоритетный) . После окончания обработки процессору 1 по айне 25 сообщается об этом и обработанный запрос снимается с шины 23. Осуществляется повторный прием на регистр 12 ожидавших обработки и вновь поступивших к этому моменту запросов, после чего процесс повторяется.

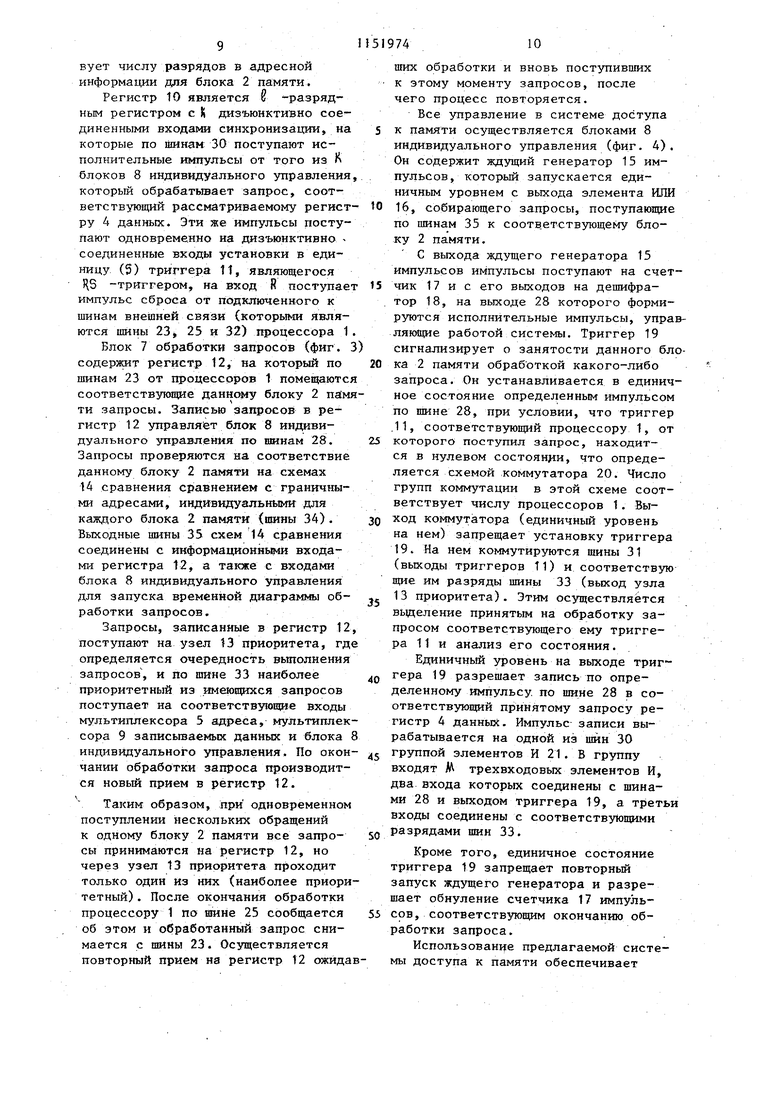

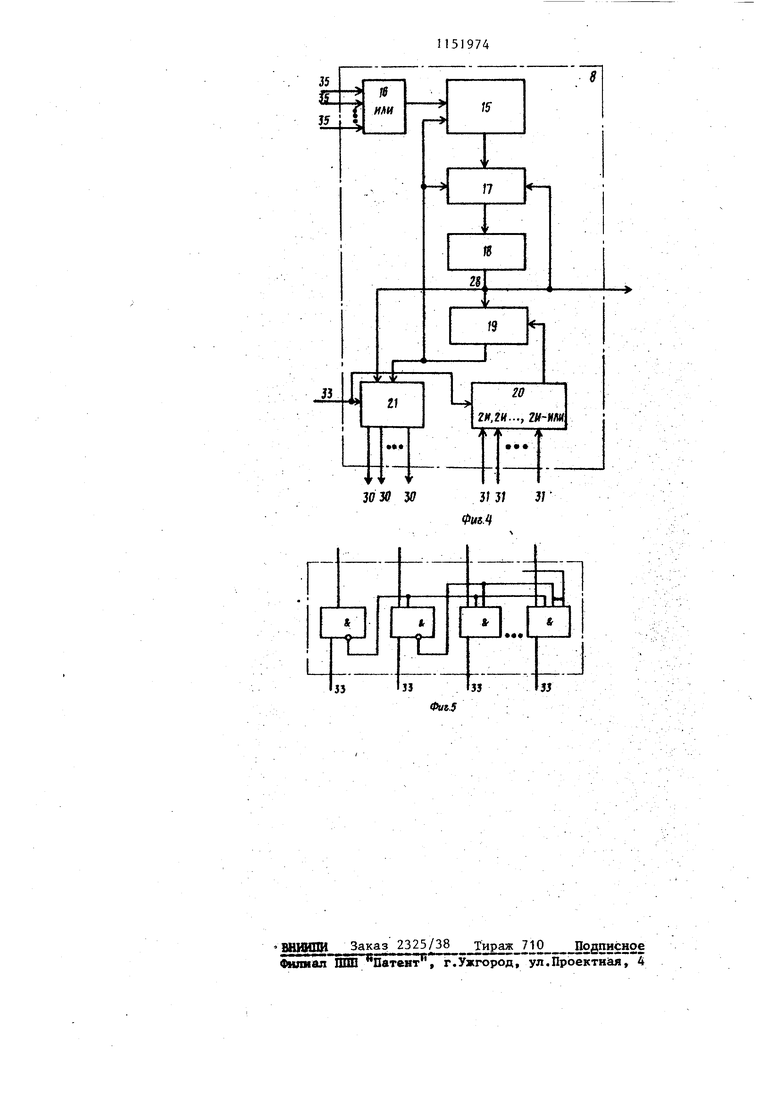

Все управление в системе доступа к памяти осуществляется блоками 8 индивидуального управления (фиг. 4). Он содержит ждущий генератор 15 импульсов, который запускается единичным уровнем с выхода элемента ИЛИ

16, собирающего запросы, поступающие по шинам 35 к соотв.етствующему блоку 2 памяти.

С выхода ждущего генератора 15 импульсов импульсы поступают на счетчик 17 и с его выходов на дешифратор 18, на выходе 28 которого формируются исполнительные импульсы, управляющие работой системы. Триггер 19 сигнализирует о занятости да;нного блока 2 памяти обработкой какого-либо запроса. Он устанавливается в единичное состояние определенным импульсом по шине 28, при условии, что триггер .11, соответствзпощий процессору 1, от

которого поступил запрос, находится в нулевом состоянии, что определяется схемой коммутатора 20. Число групп коммутации в этой схеме соответствует числу процессоров 1. Выход коммутатора (единичный уровень на нем) запрещает установку триггера 19. На нем коммутируются шины 31 (выходы триггеров 11) и соответствую щие им разряды шины 33 (выход узла

13 приоритета). Этим осуществляется вьщеление принятым на обработку запросом соответствующего ему триггера 1 1 и анализ его состояния.

Единичный уровень на выходе триггера 19 разрешает запись по определенному импульсу, по шине 28 в соответствующий принятому запросу регистр 4 данных. Импульс записи вырабатывается на одной из шин 30

группой элементов И 21. В группу входят М трехвходовых элементов И, два входа которых соединены с шинами 28 и выходом триггера 19, а третьи входы соединены с соответствующими

разрядами шин 33.

Кроме того, единичное состояние триггера 19 запрещает повторный запуск ждущего генератора и разрешает обнуление счетчика 17 импульсов, соответствующим окончанию обработки запроса.

Использование предлагаемой системы доступа к памяти обеспечивает

доступ от любого процессора к любому участку памяти, что позволяет создавать высокопроизводительные алгоритмы, не ограниченные заранее установленным объемом блока памяти с использованием обобщенных банков данных и наборов унифицированных процедур.

Увеличение числа процессоров не сокращает доступного отдельному процессору объема памяти.

Таким образом, предлагаемая система доступа к памяти позволяет достичь большей производительности, имеет повышенную живучесть и надежность.

Фиг, 2

Фиг.З

tu

33

зоУ зг

Фт.

tu

.J

J3

3}

3J

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 4325116, кл | |||

| Способ получения мыла | 1920 |

|

SU364A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент CUIA № 4282572, кл | |||

| Способ получения и применения продуктов конденсации фенола или его гомологов с альдегидами | 1920 |

|

SU362A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

Авторы

Даты

1985-04-23—Публикация

1983-12-19—Подача