1

Изобретение относится к вычислительной технике.

Цель изобретения - сокращение; оборудования.

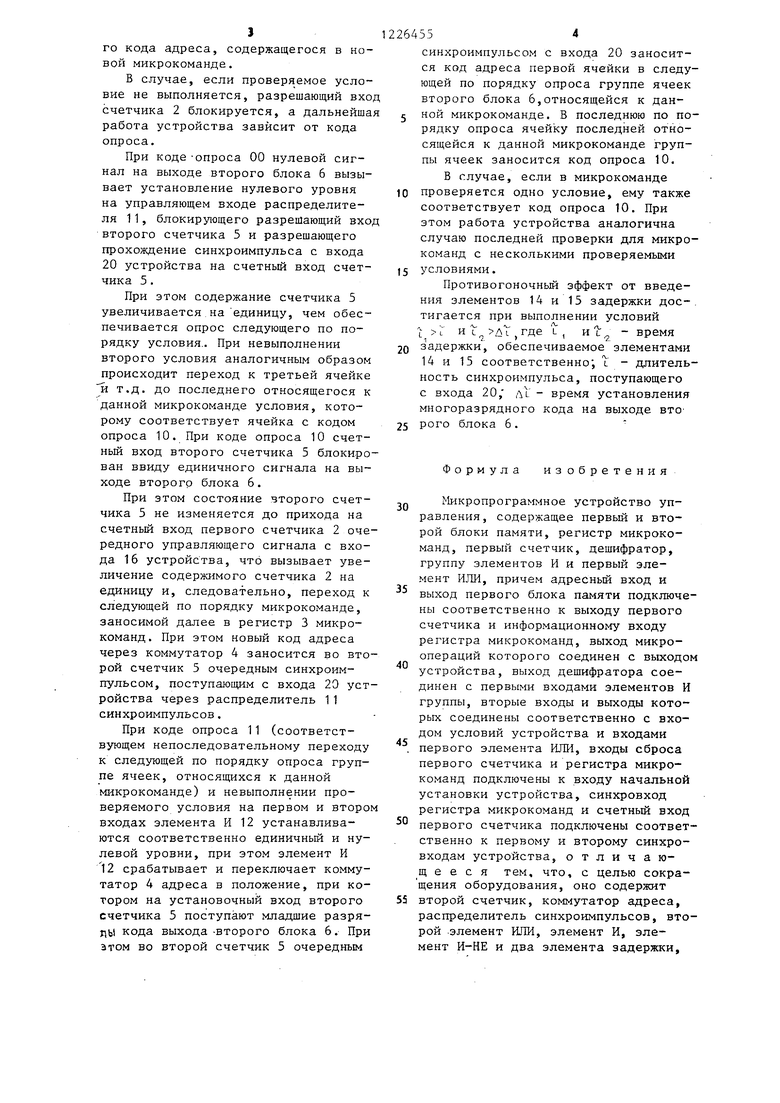

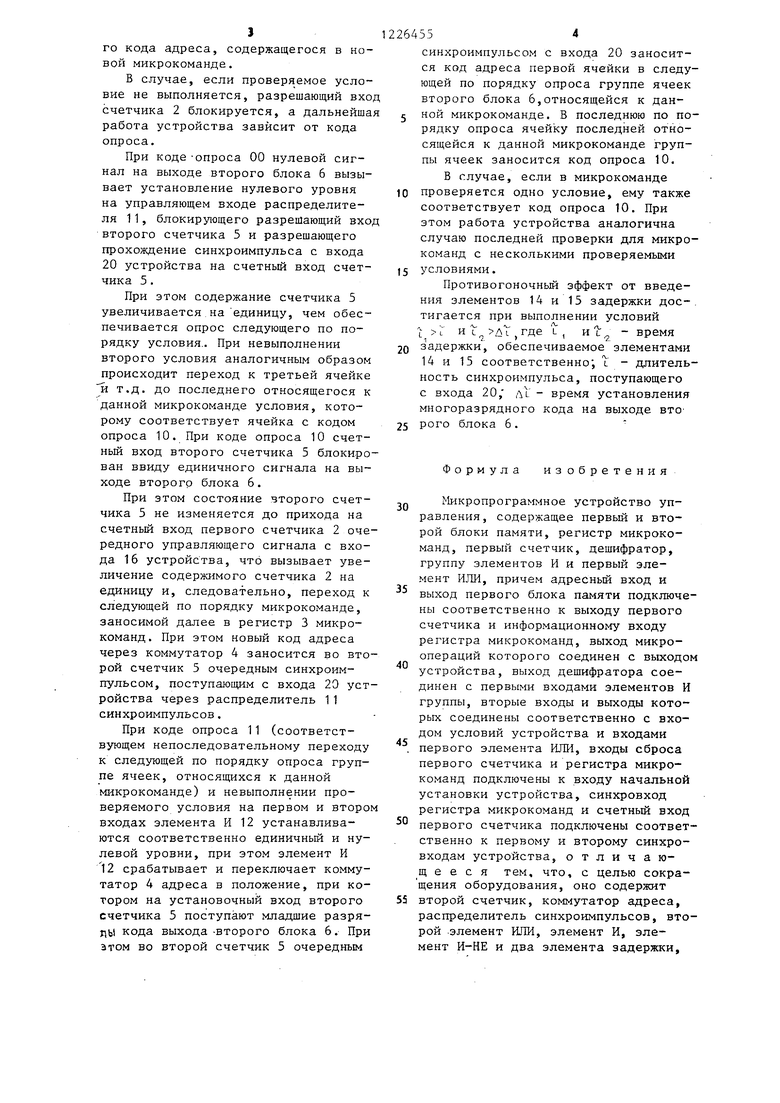

На фиг . 1 приведена функциональна схема предлагаемого микропрограммного устройства управления} на фиг.2 .фрагмент структуры второго блока па фиг.З - функциональная схема распределителя синхроимпульсов.

Микропрограммное устройство управления (фиг.1) содержит первый блок 1 памяти, первый счетчик 2, регистр 3 микрокоманд, коммутатор 4 адреса, второй счетчик 5, второй блок 6 памяти, дешифратор 7,, группу 8 элементов И, первый и второй элементы ИЛИ 9 и 10, распределитель 11 синхроимпульсов, элемент И 12, элемент И-НЕ 13, первый и второй элементы ft и 15 задержки, синхро- вход 16 устройства, вход 17 начальной установки устройства, вход 18 условий устройства, синхровходы 19 и 20, выход 21 устройства.

На фиг,2 обозначены адрес А ячейки блока 6, а также код В условия, код С адреса перехода и код Д опроса, причем индекс i обозначает принадлежность к i микрокоманде, а индекс ij - к j-му по исходному порядку опроса условию в i-и микрокоманде .

Фрагмент а соответствует микрокоманде с тремя проверяемыми условиями, а фрагмент 6 - той же микрокоманде после перепрограммирования с целью увеличения числа проверяе- ней условий до четьфех,причем вводимая дополнительно проверка с кодами В и С является второй по порядку опроса, а i-n - относительный адрес перехода в резервную зону памяти.

Распределитель 11 синхрош 1пуль- сов (фиг.З) содержит элемент И-НЕ 2 к элемент И 23.

Устройство работает следующим образом.

В исходном состоянии счетчики

2и 5 и регистр 3 обнулены сигналов с входа 17 начальной установки устройства . Сигналом с входа 19 из первого блока 1 считывается в регистр

3первая микрокоманда, соответствующая нулевому состоянию счетчика 2. При этом код микрооперации с выхода регистра 3 микрокоманд поступает

на выход 21 устройства, а код адре10

15

20

25

264552

са ячейки с выхода регистра 3 - на первый информационный вход коммутатора 4 адреса.

По нулевому содержанию второго 5 счетчика 5 определяется исходная ячейка второго блока 6, в которую, в частности, занесен код опроса .10. При указанном коде опроса единичный сигнал с выхода второго блока 6 через второй элемент ИЛИ 10 и элемент 14 задержки, предназначенный для устранения гонок, поступает на управляющий вход распределителя 11 синхроимпульсов, разрецйя прохождение очередного синхросигнала с входа 20 устройства на разрешающий вход .второго счетчика 5, а нулевой сигнап с выхода второго блока 6 через элемент И 12 поступает на управляющий вход коммутатора 4 адреса, разрешая прохождение кода адреса ячейки с второго выхода регистра 3 микрокоманд на установочный вход второго счетчика 5. Таким образом обеспечи.вается занесение во второй счетчик 5 кода адреса первой ячейки, соответствующей первой микрокоманде. По этому адресу с выхода второго блока 6 считывается код первого проверяемого условия. Согласно этому коду дешифратор 7 подает единичный сигнал на первый вход соответствующего элемента И группы 8.

В случае выполнения соответствующего условия сигнал с входа 18 условий вызывает срабатывание элемента И группы 8 и образование единичного сигнала на выходе первого элемента ИЛИ 9, разрешающего прохождение синхроимпульса с входа 28 через введенный с целью устранения гонок элемент 15 задержки и элемент И-НЕ 13 на разрешающий вход первого счетчика 2. При этом код адреса перехода с выхода второго блока 6 заносится в первый счетчик 2, чем обеспечивается условный переход устройства в заданное состояние.

Одновременно единичный сигнал с выхода первого элемента ИЛИ 9, во- первых, подается на вход элемента И 12, обеспечивая тем самым нулевой уровень на управляющем входе коммутатора 4 адреса и, во-вторых, поступает через второй элемент ИЛИ 10 и 55 элементJ4 задержки на управляющий вход распределителя 11 синхроимпульсов . Благодаря этому обеспечивается занесение во второй счетчик 5 ново30

35

40

45

50

Э

го кода адреса, содержащегося в новой микрокоманде.

В случае, если проверяемое условие не выполняется, разрешающий вхо счетчика 2 блокируется, а дальнейша работа устройства зависит от кода опроса.

При коде -опроса 00 нулевой сигнал на выходе второго блока 6 вызывает установление нулевого уровня на управляющем входе распределителя 11, блокирующего разрешающий вхо второго счетчика 5 и разрешающего прохождение синхроимпульса с входа 20 устройства на счетный вход счетчика 5.

При этом содержание счетчика 5 увеличивается на единицу, чем обеспечивается опрос следующего по порядку условия.. При невыполнении второго условия аналогичным образом происходит переход к третьей ячейке и т.д. до последнего относящегося к данной микрокоманде условия, которому соответствует ячейка с кодом опроса 10. При коде опроса 10 счетный вход второго счетчика 5 блокирован ввиду единичного сигнала на выходе второго блока 6.

При этом состояние второго счетчика 5 не изменяется до прихода на счетньш вход первого счетчика 2 очередного управляющего сигнала с входа 16 устройства, что вызывает увеличение содержимого счетчика 2 на единицу и, следовательно, переход к следующей по порядку микрокоманде, заносимой далее в регистр 3 микрокоманд. При этом новый код адреса через коммутатор 4 заносится во второй счетчик 5 очередным синхроимпульсом, поступающим с входа 20 устройства через распределитель 11 синхроимпульсов.

При коде опроса 11 (соответствующем непоследовательному переходу к следующей по порядку опроса группе ячеек, относящихся к данной микрокоманде) и невыполнении проверяемого условия на первом и второ входах элемента И 12 устанавливаются соответственно единичный и нулевой уровни, при этом элемент И 12 срабатывает и переключает коммутатор 4 адреса в положение, при котором на установочный вход второго счетчика 5 поступают младшие разряду кода выхода-второго блока 6. При этом во второй счетчик 5 очередным

264554

синхроимпульсом с входа 20 заносится код адреса первой ячейки в следующей по порядку опроса группе ячеек второго блока 6,относящейся к дан5 ной микрокоманде. В последнюю по порядку опроса ячейку последней относящейся к данной микрокоманде группы ячеек заносится код опроса 10. В случае, если в микрокоманде

10 проверяется одно условие, ему также соответствует код опроса 10. При этом работа устройства аналогична случаю последней проверки для микрокоманд с несколькими проверяемыми

)5 условиями.

Противогоночньй эффект от введения элементов 14 и 15 задержки дос-. тигается при выполнении условий I 1 и t -лТ ,где L , - время

2Q задержки, обеспечиваемое элементами 14 и 15 соответственно; 1 - длительность синхроимпульса, поступающего с входа 20, д1 - время установления многоразрядного кода на выходе вто

25 рого блока 6.

Формула изобретения

Микропрограммное устройство управления, содержащее первый и второй блоки памяти, регистр микрокоманд, первый счетчик, дешифратор, группу элементов И и первый элемент ИЛИ, причем адресный вход и

выход первого блока памяти подключены соответственно к выходу первого счетчика и информационному входу регистра микрокоманд, выход микроопераций которого соединен с выходом устройства, выход дешифратора соединен с первыми входами элементов И группы, вторые входы и выходы которых соединены соответственно с входом условий устройства и входами первого элемента ИЛИ, входы сброса первого счетчика и регистра микрокоманд подключены к входу начальной установки устройства, синхровход регистра микрокоманд и счетный вход

первого счетчика подключены соответственно к первому и второму синхро- входам устройства, о т л и ч а ю- щ е е с я тем, что, с целью сокращения оборудования, оно содержит

второй счетчик, коммутатор адреса, распределитель синхроимпульсов, второй -элемент ИЛИ, элемент И, элемент И-НЕ и два элемента задержки.

причем первый и второй информационные входы, управляющий вход и выход коммутатора подключены соо тветст- венно к адресным выходам, регистра микрокоманд и второго блока памяти, выходу элемента И и установочным входам второго счетчика, вход сброса, счетный и разрешающий входы и выход которого соединены соответственно с входом начальной установки устройства, первым и вторым выходами распределителя синхроимпульсов и адресным входом второго блока памяти, выходы кода условий, первый и второй выходы опроса которого соединены соответственно с входом дieши,фpaтopa,

первым входом второго элемента ИЛИ и прямым входом элемента И,-инверсный вход которого соединен с выходом первого элемента ИЛИ, с первым входом элемента И-НЕ и вторым входом второго элемента ИЛИ, выход которого через первый элемент задержки соединен с первым входом распределителя синхроимпульсов, второй вход которого соединен с третьим синхровходом устройства и через второй элемент задержки с вторым входом элемента И-НЕ, выход которого соединен с разрешающим входом первого счетчика, установочный вход которого соединен с адресным выходом второго блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сортировки информации | 1986 |

|

SU1365075A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1242946A1 |

| Устройство для обмена данными в распределенной вычислительной системе | 1988 |

|

SU1580382A1 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1164706A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1211724A1 |

Изобретение относится квЭчис- лительной технике. Цель изобретения - сокращение объема оборудования. Это достигается за счет введения в устройство счетчика, коммутатора адреса, распределителя синхроимпульсов, элемента ИЛИ, элемента И, элемента И-НЕ и двух элементов задержки с соответствующими функциональными связями между ними и известными блоками устройства. Вновь введенные блоки позволяют достигнуть противогоночного эффекта. 3 ил. ю О) ( ел сд

Ф«г.2 Редактор Т. Кугрышева

Составитель Логачева

Техред В.Кадар Корректор И. Эрдейи

2134/48 Тираж 671 Подписное ВНИНПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35,. Раушская наб., д, 4/5

7роизводственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

| Майоров С.А., Новиков Т.Н | |||

| Принципы организации цифровых машин | |||

| Л.: Машиностроение, 1974, с | |||

| Кузнечный горн | 1921 |

|

SU215A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1005050A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-04-23—Публикация

1984-10-19—Подача