Изобретение относится к технике накопления информации и полупроводниковой технике и может быть использовано в устройствах вычислительной техники и автоматики.

Целью изобретения является повышение быстродействия и расширение области применения формирователя за счет формирования трех логических уровней сигнала.

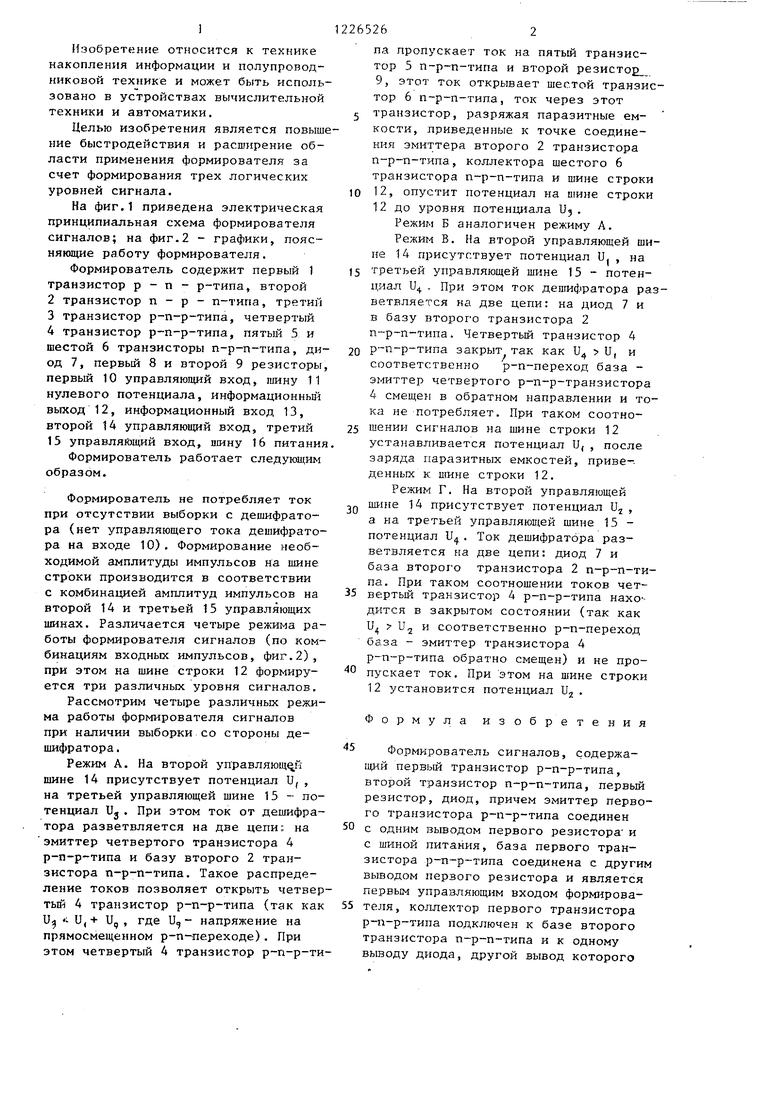

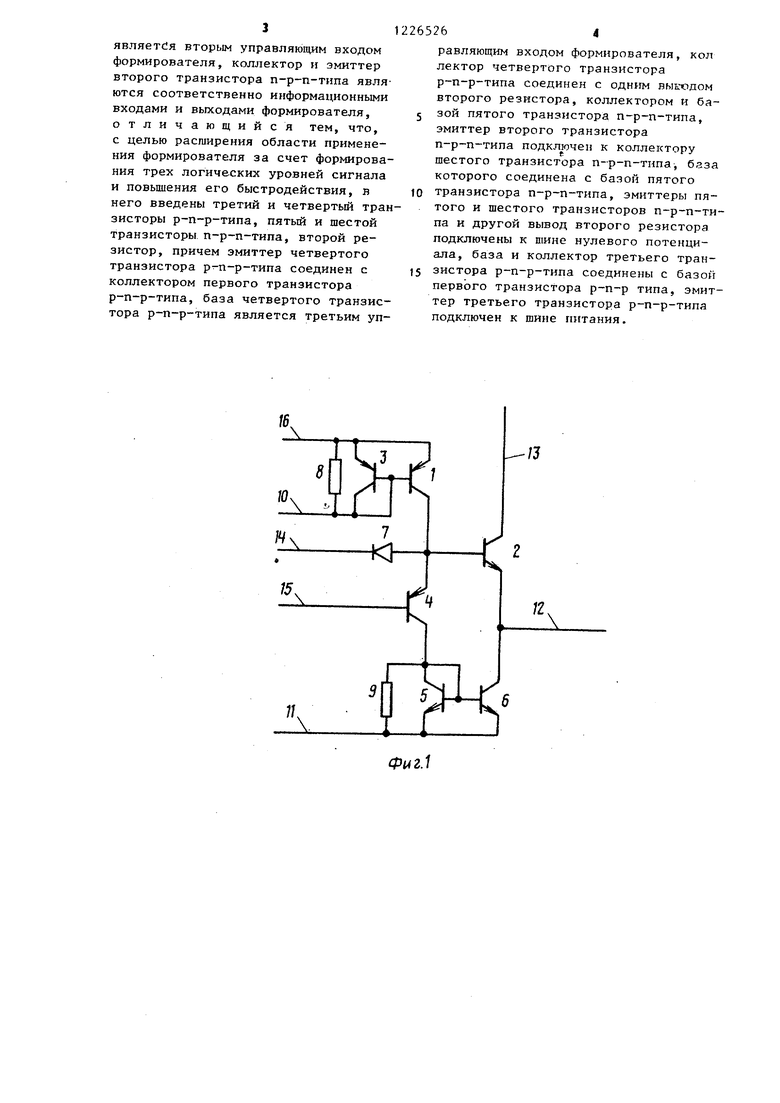

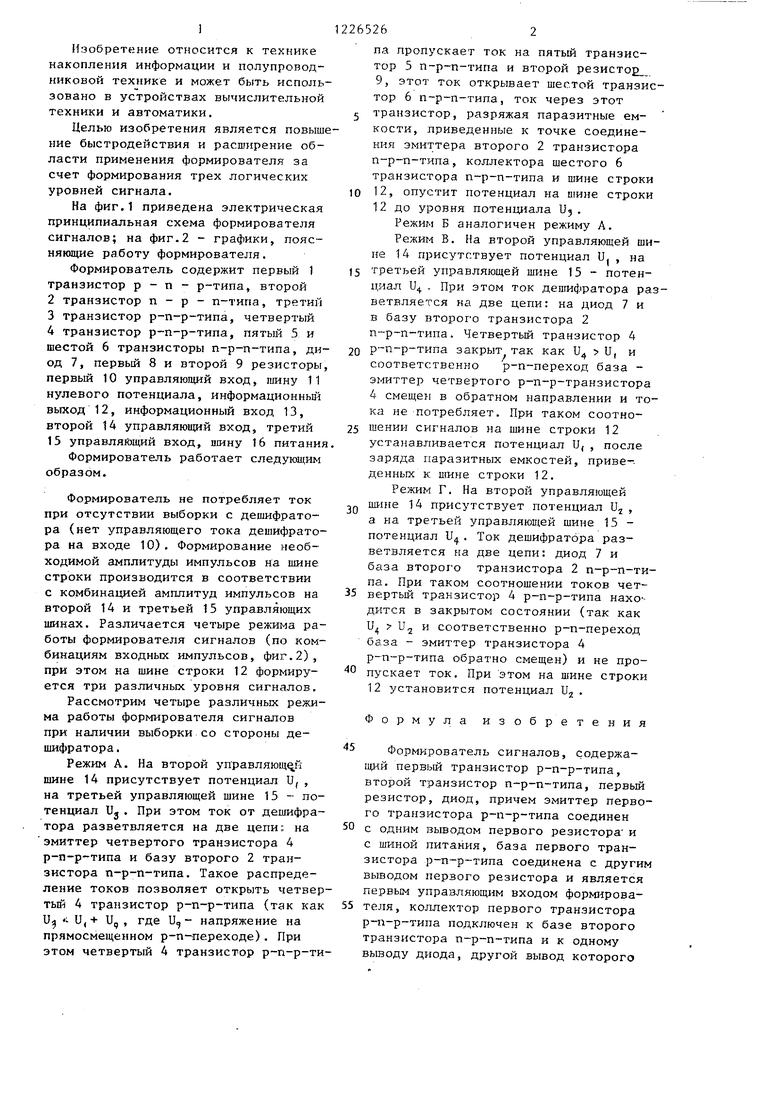

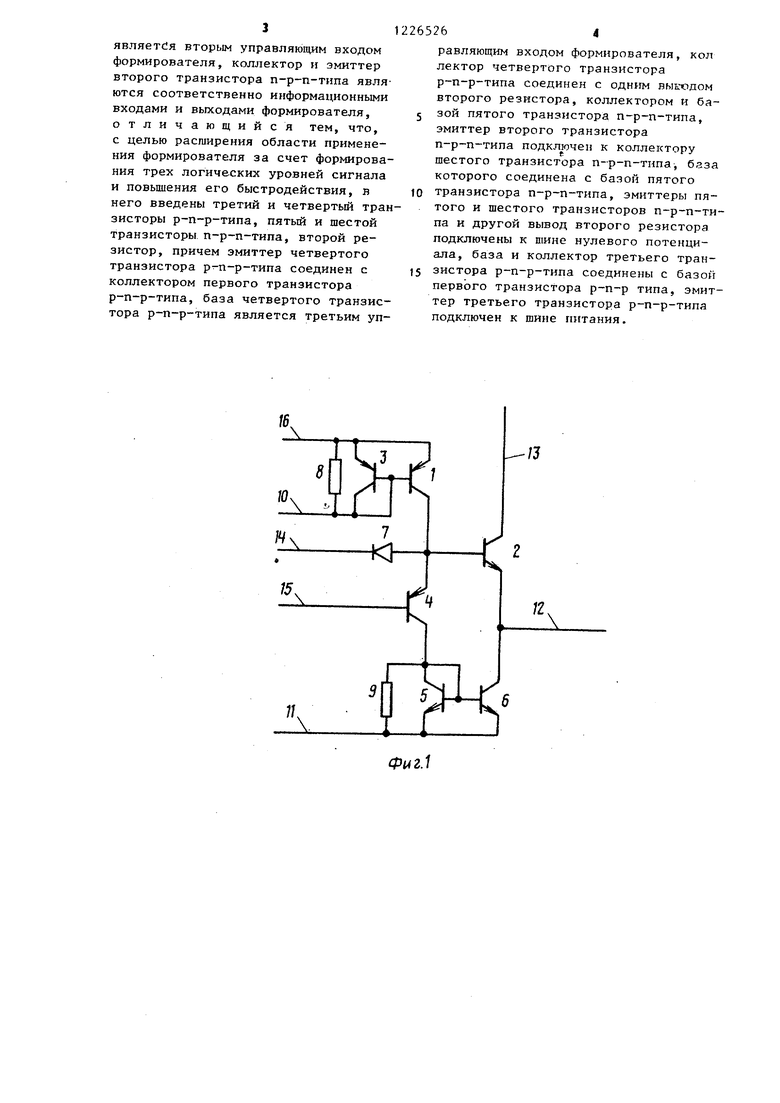

На фиг.1 приведена электрическая принципиальная схема формирователя сигналов; на фиг.2 - графики, поясняющие работу формирователя.

Формирователь содержит первый 1 транзистор р - п - р-типа, второй

2транзистор п - р - п-типа, третий

3транзистор р-п-р-типа, четвертый

4транзистор р-п-р-типа, пятьш 5 и шестой 6 транзисторы п-р-п-типа, диод 7, первый 8 и второй 9 резисторы первый 10 управляющий вход, пшну 11 нулевого потенциала, информационньш выход 12, информационный вход 13, второй 14 управляющий вход, третий

15 управляющий вход, шину 16 питания

Формирователь работает следующим образом.

Формирователь не потребляет ток при отсутствии выборки с дешифратора (нет управляющего тока дешифратора на входе 10). Формирование необходимой амплитуды импульсов на шине строки производится в соответствии с комбинацией амплитуд импульсов на второй 14 и третьей 15 управляющих шинах. Различается четыре режима работы формирователя сигналов (по комбинациям входных импульсов, фиг.2), при этом на шине строки 12 формируется три различных уровня сигналов,

Рассмотрим четыре различных режима работы формирователя сигналов при наличии выборки со стороны дешифратора.

Режим А. На второй управляющф шине 14 присутствует потенциал U,, на третьей управляющей шине 15 - потенциал и,. При этом так от дешифратора разветвляется на две цепи: на эмиттер четвертого транзистора 4 р-п-р-типа и базу второго 2 транзистора п-р-п-типа. Такое распределение токов позволяет открыть четвер тьтй 4 транзистор р-п-р-типа (так как U- - и, -ь и, , где и, - напряжение на прямосмещенном р-п-переходе). При этом четвертый 4 транзистор р-п-р-типа пропускает ток на пятый транзистор 5 п-р п-типа и второй резисто2.. 9, этот ток открывает шестой транзистор 6 п-р-п-типа, ток через этот

транзистор, разряжая паразитные емкости, приведенные к точке соединения эмиттера второго 2 транзистора П р-п-типа, коллектора шестого 6 транзистора п-р-п-типа и шине строки

12, опустит потенциал на шине строки 12 до уровня потенциала Uj,

Режим Б аналогичен режиму А. Режим В, На второй управляющей шине 14 присутствует потенциал U. , на

третьей управляющей шине 15 - потенциал 1)4. . При этом ток дешифратора разветвляется на две цепи: на диод 7 и в базу второго транзистора 2 п-р-п-типа. Четвертый транзистор 4

р--п-р-типа закрыт так как U U, и соответственно р-п-переход база - эмиттер четвертого р-п-р-транзистора 4 смещен в обратном направлении и тока не потребляет. При таком соотношении сигналов на шине строки 12 устанавливается потенциал U,, после заряда паразитных емкостей, приве-. денных к шине строки 12,

Режим Г. На второй управляющей

шине 14 присутствует потенциал U , а на треть Й управляющей шине 15 - потенциал U. Ток дешифратора разветвляется на две цепи: диод 7 и база второго транзистора 2 п-р-п-типа. При таком соотношении токов четвертый транзистор 4 р-п-р-типа нахо-- дится в закрытом состоянии (так как и и и соответственно р-п-переход база - эмиттер транзистора 4 р-п-р-типа обратно смещен) и не пропускает ток. При этом на шине строки 12 установится потенциал U .

Формула изобретения

Формирователь сигналов, содержащий первый транзистор р-п-р-типа, второй транзистор п-р-п-типа, первый резистор, диод, причем эмиттер первого транзистора р-п-р-типа соединен

с одним выводом первого резистора и

с шиной питания, база первого транзистора р-п-р-типа соединена с другим выводом первого резистора и является первым управляющим входом формирова- 55 теля, коллектор первого транзистора р-п-р-типа подключен к базе второго транзистора п-р-п-типа и к одному выводу диода, другой вывод которого

3

являетйя вторым управляющим входом формирователя, коллектор и эмиттер второго транзистора п-р-п-типа являются соответственно информационными входами и выходами формирователя, отличающийся тем, что, с целью расширения области применения формирователя за счет формирования трех логических уровней сигнала и повышения его быстродействия, в него введены третий и четвертый транзисторы р-п-р-типа, пятый и шестой транзисторы п-р-п-типа, второй резистор, причем эмиттер четвертого транзистора р-п-р-типа соединен с коллектором первого транзистора р-п-р-типа, база четвертого транзистора р-п-р-типа является третьим уп265264

равляющим входом формирователя, кол лектор четвертого транзистора р-п-р-типа соединен с одним выкодом второго резистора, коллектором и ба5 ЗОЙ пятого транзистора п-р-п-типа, эмиттер второго транзистора п-р-п-типа подключен к коллектору шестого транзистора п-р-п-типа, база которого соединена с базой пятого

10 транзистора п-р-п-типа, эмиттеры пятого и шестого транзисторов п-р-п-типа и другой вывод второго резистора подключены к шине нулевого потенциала, база и коллектор третьего тран)5 зистора р-п-р-типа соединены с базой первого транзистора р-п-р типа, эмиттер третьего транзистора р-п-р-типа подключен к шине питания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь сигналов записи и считывания | 1983 |

|

SU1113852A1 |

| Оперативное запоминающее устройство | 1982 |

|

SU1111204A1 |

| Устройство для предварительной проверки транзисторов | 1982 |

|

SU1101762A1 |

| Запоминающее устройство | 1985 |

|

SU1305774A2 |

| Устройство формирования эталонных цифровых сигналов | 1983 |

|

SU1176443A1 |

| Формирователь импульсов управления | 1985 |

|

SU1290501A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Десятичное счетно-индикаторное устройство | 1982 |

|

SU1078628A1 |

| Устройство для отображения графической информации на газоразрядном матричном индикаторе | 1987 |

|

SU1495846A1 |

| Коммутатор аналоговых сигналов | 1981 |

|

SU978345A1 |

Изобретение относится к области вычислительной техники и автоматики. Цель изобретения состоит в повышении быстродействия и расширении области применения.формирователя сигналов за счет формирования трех логических уровней сигнала. Формирователь сигналов содержит транзисторы |п-р-пир-п- р-типа, диод, резисторы. Формирователь работает в четырех различных режимах при наличии сигналов выборки со стороны дешифратора, 2 ил. сл

/5

11

С

12

ЗП 5

tX

Г п

Фиг.1

Фi,iг.2

Редактор А.Шандор

Состав.11тель О.Кулаков

Техред И.Попович Корректор С.Шекмар .

Заказ 2140/52 Тираж 543 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035,.. Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

| Валиев К.А | |||

| и Орликовский А,А | |||

| Полупроводниковые интегральные схемы памяти на биполярных транзисторньк структурах.- М.: Советское радио, 1979, с.210, Электроника, 1974, № 9, с.59-65 | |||

| Валиев К.А | |||

| и Орликовский А.А | |||

| Полупроводниковые интегральные схемы памяти на биполярных транзисторных структурах | |||

| М.: Советское радио, 1979, с | |||

| Крутильный аппарат | 1922 |

|

SU234A1 |

Авторы

Даты

1986-04-23—Публикация

1984-09-21—Подача