источников 43 и 44 тока с соответствующими связями. Параметры элементов йсточн1иса второго опорного напряжения идентичны соответствующим параметрам элементов накопителя, что уменьшает

1

Изобретение относится к микроэлектронике, может найти применение в интегральных запоминающих устройствах (ЗУ) для вычислительной техники и является усовершенствованием известного устройства по авт. сн. № 1256097.

Целью изобретения является повышение быстродействия устройства.

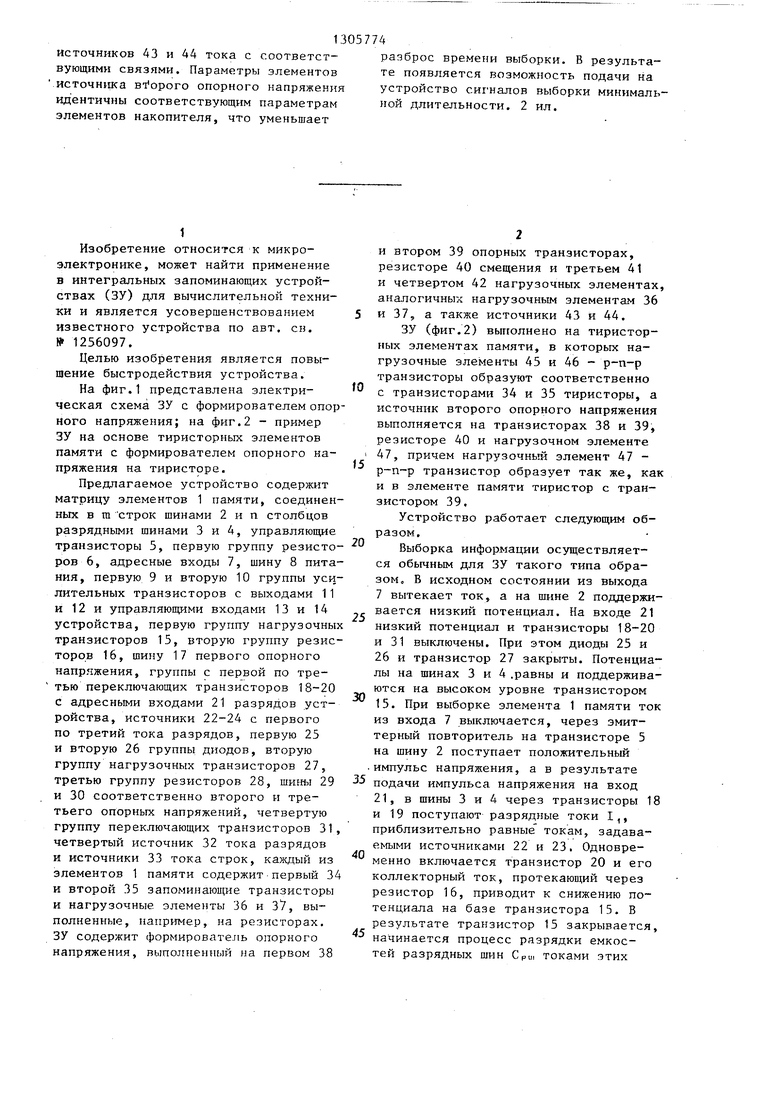

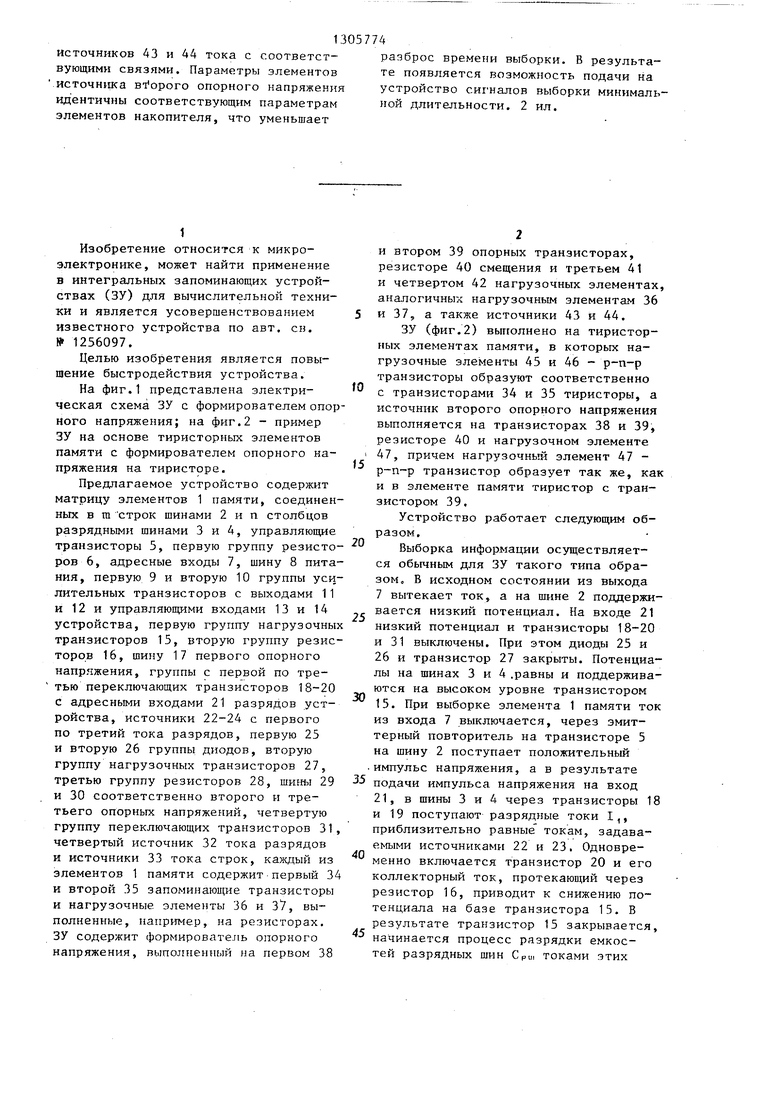

На фиг.1 представлена электрическая схема ЗУ с формирователем опорного напряжения; на фиг.2 - пример ЗУ на основе тиристорных элементов памяти с формирователем опорного напряжения на тиристоре.

Предлагаемое устройство содержит матрицу элементов 1 памяти, соединенных в m строк шинами 2 и п столбцов разрядными шинами 3 и 4, управляющие транзисторы 5, первую группу резисторов 6, адресные входы 7, шину 8 питания, первую 9 и вторую 10 группы усилительных транзисторов с выходами 11 и 12 и управляющими входами 13 и 14 устройства, первую группу нагрузочных транзисторов 15, вторую группу резисторов 16, шину 17 первого опорного напряжения, группы с первой по третью переключающих транзисторов 18-20 С адресными входами 21 разрядов устройства, источники 22-24 с первого по третий тока разрядов, первую 25 и вторую 26 группы диодов, вторую группу нагрузочных транзисторов 27, третью группу резисторов 28, ши1ш 29 и 30 соответственно второго и третьего опорных напряжений, четвертую группу переключающих транзисторов 31, четвертый источник 32 тока разрядов и источники 33 тока строк, каждый из элементов 1 памяти содержитпервый 34 и второй 35 запоминающие транзисторы и нагрузочные элементы 36 и 37, выполненные, например, на резисторах. ЗУ содержит формирователь опорного напряжения, выполненныр на первом 38

разброс времени выборки. В результате появляется возможность подачи на устройство сигналов выборки минимальной длительности. 2 ил.

и втором 39 опорных транзисторах, резисторе 40 смещения и третьем 41 и четвертом 42 нагрузочных элементах, анапогичных нагрузочным элементам 36 и 37, а также источники 43 и 44.

ЗУ (фиг.2) выполнено на тиристорных элементах памяти, в которых нагрузочные элементы 45 и 46 - р-п-р транзисторы образуют соответственно с транзисторами 34 и 35 тиристоры, а источник второго опорного напряжения выполняется на транзисторах 38 и 39, резисторе 40 и нагрузочном элементе 47, причем нагрузочный элемент 47 - р-п-р транзистор образует так же, как и в элементе памяти тиристор с транзистором 39.

Устройство работает следующим образом.

Выборка информации осуществляется обычным для ЗУ такого типа образом, В исходном состоянии из выхода 7 вытекает ток, а на шине 2 поддерживается низкий потенциал. На входе 21 низкий потенциал и транзисторы 18-20 и 31 выключены. При этом диоды 25 и 26 и транзистор 27 закрыты. Потенциалы на шинах 3 и 4 .равны и поддерживаются на высоком уровне транзистором 15. При выборке элемента 1 памяти ток из входа 7 выключается, через эмит- терный повторитель на транзисторе 5 на шину 2 поступает положительный импульс напряжения, а в результате

5

0

5

0

5

подачи импульса напряжения на вход 21, в шины 3 и 4 через транзисторы 18 и 19 поступают разрядные токи I, приблизительно равные токам, задаваемыми источниками 22 и 23 Одновременно включается: транзистор 20 и его коллекторный ток, протекающий через резистор 16, приводит к снижению потенциала на базе транзистора 15. В результате транзистор 15 закрывается, начинается процесс разрядки емкостей разрядных шин CPU. токами этих

шин I р, и потенциалы на этих шинах понижаются. При выборке включается также транзистор 31, его коллекторный ток протекает через резистор 28 и понижает потенциал на коллекторе транзистора 31. В результате диоды 25 и 26 отпираются, часть тока 1 через эти диоды поступает в шины 3 и 4, ускоряя процесс разряда емкостей С , и соответственно увеличивается быстродействие устройства. По окончании процесса разряда емкости шины 4 отпирается эмиттерный переход транзистора 35, диод 26 закрывается, а транзистор 27 открьгоается и ток I отводится в транзистор 27. Для обеспечения этого режима величины Е на шине 29 выбирается из уравнения и , и, где и, Us,.,s-U65 -5- «

е 002 6927 ЗУЛ

.е

напряжения на прямо смещенном эмит- терном переходе транзисторов 27, 35 и диода 26 соответственно, а Ug,-,- - потенциал базы транзистора 35 в режиме выборки. Поскольку это условие определяет момент отвода тока из шины 4 в транзистор 27, отклонение от него, обусловленное технологическим разбросом величин, приводит к технологическому разбросу времени считывания. Транзистор 38 работает в активном режиме, а транзистор 39 - в режиме насыщения, т.е. аналогично режимам работы транзисторов 5 и 35 соответственно.

Пусть нагрузочные элементы 36 и 37 и соответственно 41 и 42 вьшолне- ны в виде резисторов. Величина U (фиг.1) определяется уравнением

IT F - . D -и Li.-R

i % B, +1,6 3s 1+ B,, /5„ 36

- и

8 345

- Ua,

где Ef, - величина напряжения источника 8 питания;

I - ток питания строки, задаваемый источником 33 тока;

R и R - сопротивление резистора 6 и

Л резистора 36 соответственно.

Величина U, определяется уравнением

и.Еп- ,,« - Ьзз -

R. ,/5,,

где 1 и Ig - токи источников 43 и 44

соответственно;

R и R - сопротивления резисторов 40 и нагрузочного

элемента 41.

Если I.. I,, Р.,, К, R

S6 ГО

БЗЗ S . Кроме того, если I 1 и R R, и относительный разброс номиqO t

налов резисторов, величин Uj, и В транзисторов, расположенных на одном, кристалле, незначителен,- то U-, U с высокой точностью.

Формула изобретения

Запоминающее устройство по авт; .св. № 1256097, отличающее- с я тем, что, с целью повышения быстродействия устройства, в него введен формирователь опорного напряжения, состоящий из двух опорных транзисторов, резистора смещения,нагрузочных элементов и двух источников тока, первые выводы которых подключены к шине нулевого потенциала устройства, а вторые - к эмиттерам первого и второго опорных транзисторов соответственно, коллектор первого опорного транзистора соединен с шиной питания устройства и с первым выводом резистора смещения, второй вывод которого соединен с базой первого опорного транзистора, эмиттер которого соединен с первьми выводами нагрузочных элементов, вторые выводы которых соединены с коллектором и базой второго опорного транзистора соответственно, эмиттер которого подключен к шине второго опорного напряжения устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| Запоминающее устройство | 1985 |

|

SU1256097A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1689991A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1575234A1 |

| Накопитель | 1989 |

|

SU1656595A1 |

| Запоминающее устройство | 1981 |

|

SU959165A1 |

| Накопитель для оперативного запоминающего устройства | 1990 |

|

SU1751815A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1133621A1 |

Изобретение относится к вычислительной технике и может найти применение в интегральных запоминающих устройств ах. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается путем введения в запоминающее устройство формирователя опорного напряжения, состоящего из двух опорных транзисторов 38 и 39, опорного резистора 40, нагрузочных элементов 41 и 42 и двух - у - -«ч (Л ОО о СП | 4 W - у .-..1 ij. гч Риг.1

Редактор И.Шулла

Составитель С.Королев

Техред В.КадарКорректор А.Обручар

Заказ 1460/51 Тираж 590Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| , Авторское свидетельство СССР № 1256097, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-04-23—Публикация

1985-11-22—Подача