1

Изобретение относится к цифро- юй технике и может быть использо- ано при создании хронизаторов, (ифровых синтезаторов частоты и т.п.

Цель изобретения - повьшение на дежности работы устройства за счет введения синхронного режима работы, а также уменьшения числа элементов и связей, что одновременно приводит к упрощению устройства.

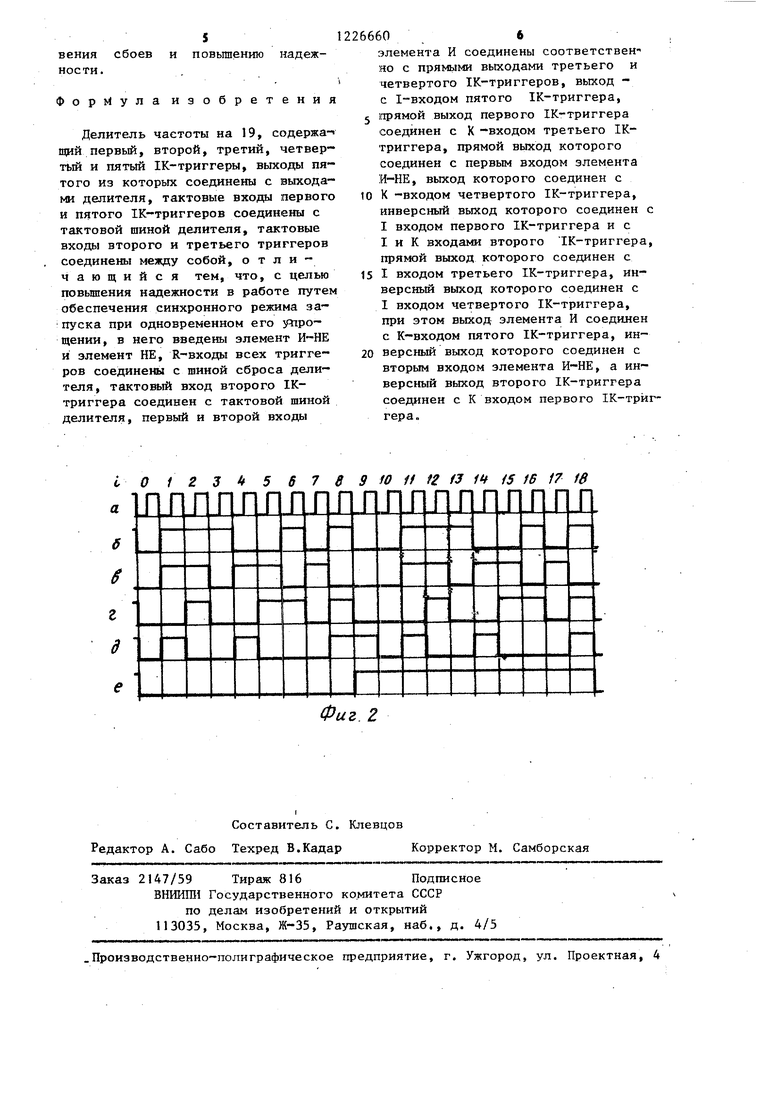

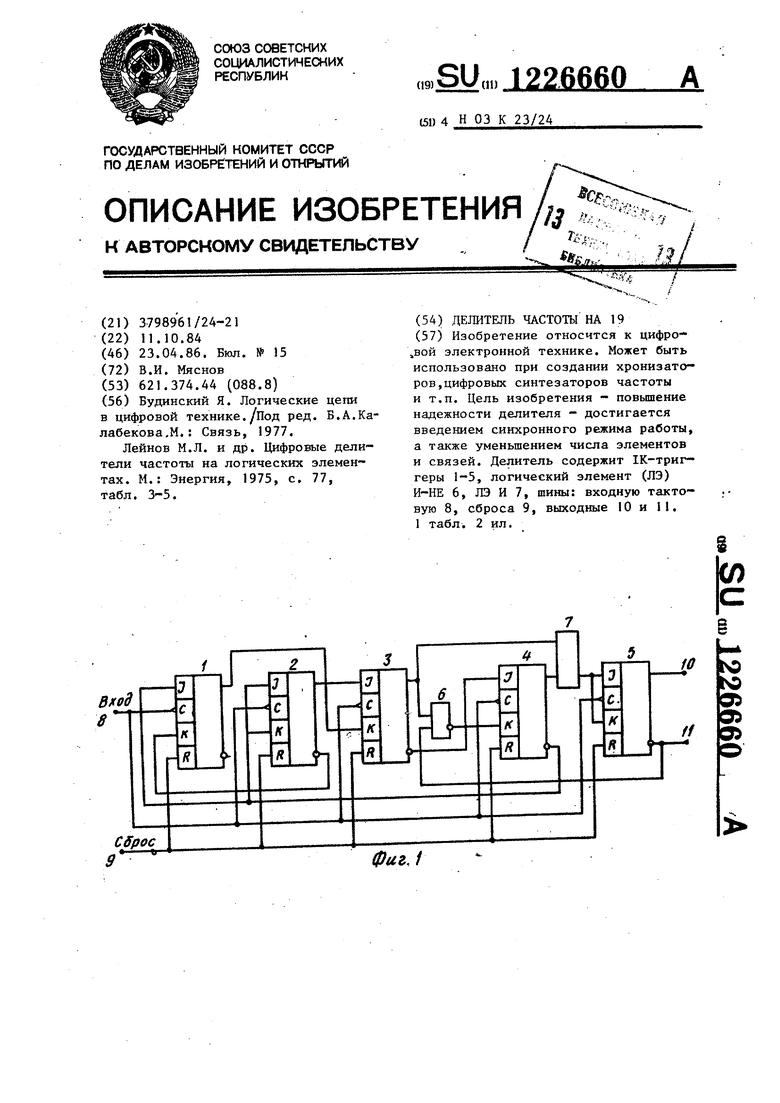

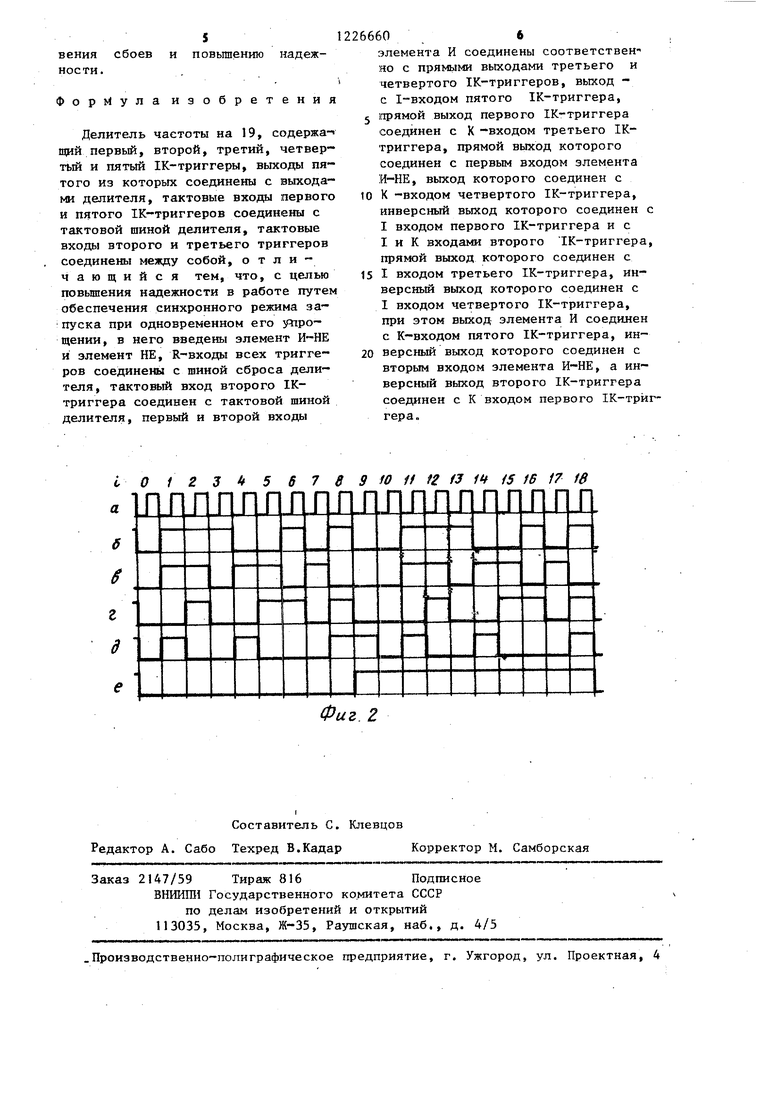

На фиг. 1 приведена функциональная схема делителя частоты на 19; на фиг. 2 - временные диаграммы его работы.

Делитель частоты на 19 содержит 1К-триггеры 1 - 5, элемент И-НЕ 6 и элемент И 7, а также входную так товую шину 8, шину 9 сброса, и выходные шины 10 и 11. Счетные входы С всех 1К-триггеров соединены с тактовой шиной 8, R-входы всех ХК-три геров соединены с шиной 9 сброса устройства, выходы пятого 1К-тригге ра образуют выходные шины 10 и 11 устройства. При этом прямой выход первого 1К-триггера соединен с К-входом третьего IK-триггер а. прямой вькод которого соединен с первыми входами элементов И-НЕ 6 и И7, выходы которых соединены соответственно с К- входом четвертого IK-триггера и с I- и К-входами пятого 1К-триггера, инверсный выход которого соединен с вторым входом элемента 6, прямой выход второго 1К-триггера 2 соединен с 1-входом третьего 1К-триггера 3, инверсный выход которого соединен с 1-входом четвертого 1К-триггера 4, прямой выход которого соединен с вторым входом элемента И 7, а инверсный выход соединен с 1-входом первого 1К-тригге- ра 1 и с I- и К-входами второго 1К-триггера 2, инверсный выход второго 1К-триггера 2 соединен с К-вхо дом первого 1К-триггера 1.

На фиг. 2 обозначено: а - входны тактовые импульсы на тактовой шине 8, & - сигнал Q, на прямом выходе Q, первого 1К-триггера 1, - сигнал Qj на прямом выходе Q второг 1К-триггера 2, г - сигнал Qj на прямом выходе 0 третьего IK-триг- гера 3, 5 сигнал Q на прямом выходе Q4 четвертого 1К-триггера 4; е - сигнал Q на прямом выходе Q пятого 1К-триггера 5.

При указанной схеме соединения элементов логические уравнения для

2266602

I- и К-входов всех 1К-триггеров преддшгаемого делителя частоты на 19 следующие:

I,Q,; I,Q4; I, I q

Q,Q4;

3

K, ,; K,Q, ; K,Q,vQ

Q,Q.r; .

По сигналу Сброс, поступающему в виде импульса по шине 9 сброса, все 1К-триггеры 1-5 устанавливаются в нулевое положение. При этом состояния выходов равны (фиг. 2 при ) Q,0, Q., , , .

Ha основании логических уравнений ,цля I- и К-входов .1К-триггеров устройства состояния входов следуютщие:., . i; I,

,1; ,

25

Kj Q 1; K,

, .

IK-трйггеры переключаются в противоположное состояние по отрица

тельному перепаду сигнала на счетном входе С (фиг.1 и 2).

По первому тактовому импульсу, появившемуся на тактовой шине 8 после окончания действия импульса

Сброс на шине 9 сброса первый, второй и четвертый 1К-триггеры 1,2 и 4 переключатся в противоположное, единичное, состояние (так как у них и , где j l,2,4), а третий и пятый 1К-триггеры 3 и 5 не изменяют своего состояния (так как у них I: О и , где ). После переключения триггеров под действием первого тактового импульса

состояния выходов равны (фиг.2 при

)

Q,1, . этом изменятся и состояния входов:

1,0; IjrO; К,0; К,1; . .

В результате этого по следующему, второму, тактовому импульсу устройство переходит во второе состояние (фиг. 2 при ), которое характеризуется следующими значе ниями выходов и входов 1К-триггеров 1-5:

312266604

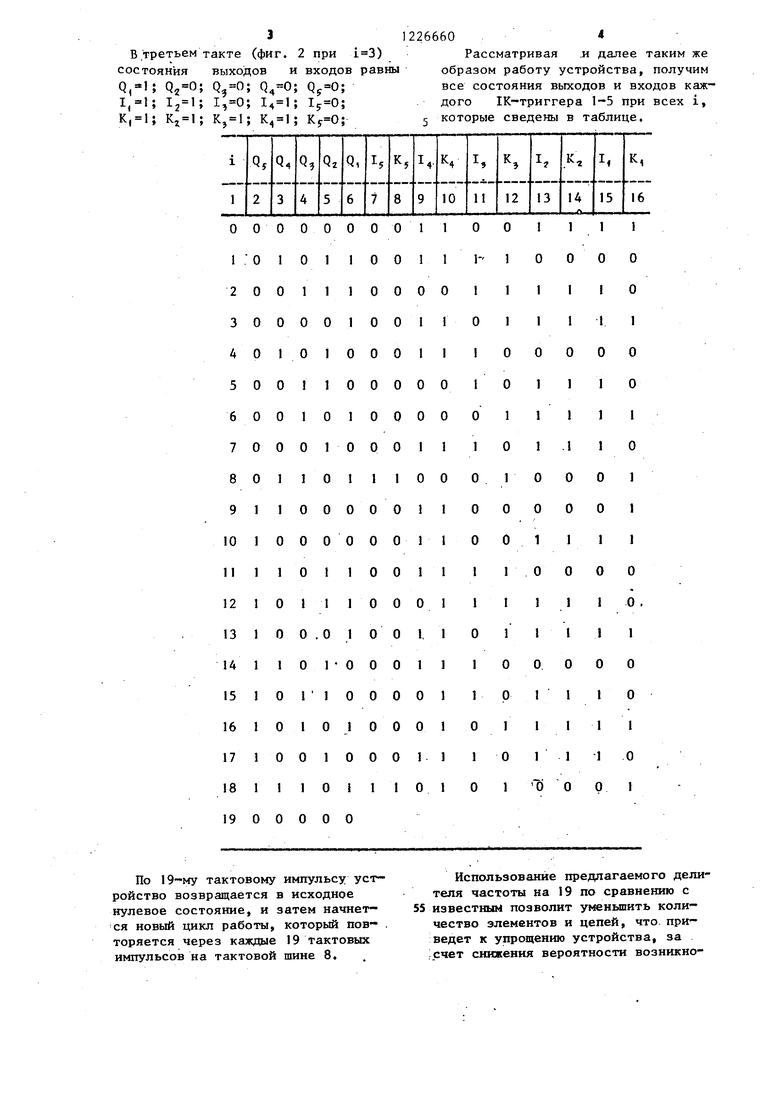

В,третьем такте (фиг. 2 при ) Рассматривая .и далее таким же состояния выходов и входов равны образом работу устройства, получим

все состояния выходов и входов каждого 1К-триггера 1-5 при всех i.

Q,-l; Q,0; Q,.0; I,.l; I2 l; I,0; K,l; K,l;

5 которые сведены в таблице.

По 19-му тактовому импульсу устройство возвращается в исходное нулевое состояние, и затем начнется новый цикл работы, который пов- торяется через каждые 19 тактовых импульсов на тактовой шине 8.

5 которые сведены в таблице.

Использование предлагаемого делителя частоты на 19 по сравнению с 5S известным позволит уменыпить количество элементов и цепей, что. приведет к упрощению устройства, за ;счет снижения вероятности возникно5

вения сбоев и повьшению надежности.

изобретения

Делитель частоты на 19, содержа- щий первый, второй, третий, четвертый и пятый 1К-триггеры, выходы пятого из которых соединены с выходами делителя, тактовые входы первого и пятого 1К-триггеров соединены с тактовой шиной делителя, тактовые входы второго и третьего триггеров соединены между собой, отличающийся тем, что, с целью повьшения надежности в работе путем обеспечения синхронного режима запуска при одновременном его jRipo- щении, в него введены элемент И-НЕ и элемент НЕ, R-входы всех триггеров соединетл с шиной сброса делителя, тактовый вход второго IK- триггера соединен с тактовой шиной делителя, первый и второй входы

10 / 2 J « 5 6 7 в 9 10 И fZ 13 itt 15 16 17 1$

б

$

г д

Фиг. г

Составитель С. Клевцов Редактор А. Сабо Техред В.Кадар Корректор М. Самборская

Заказ 2147/59 Тираж 816Подписное

ВНИИПИ Государственного ко.митета СССР

по делам иэобретений и открытий 113035, Москва, Ж-35, Раушская, наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

266606

элемента И соединены соответствен но с прямыми выходами третьего и четвертого 1К-триггеров, выход - с 1-входом пятого 1К-триггера,

5 1прямой выход первого 1К-триггера соединен с К -входом третьего IK- триггера, прямой выход которого соединен с первым входом элемента И-НЕ, выход которого соединен с

10 К -входом четвертого 1К-триггера, инверсный выход которого соединен с 1 входом первого 1К-триггера и с I и К входами второго 1К-триггера, прямой выход которого соединен с

15 I входом третьего 1К-триггера, инверсный выход которого соединен с I входом четвертого 1К-триггера, при этом выход элемента И соединен с К-входом пятого 1К-триггера, ин20 версный выход которого соединен с вторым входом элемента И-НЕ, а инверсный выход второго 1К-триггера соединен с К входом первого 1К-триг- гера

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный делитель частоты на 17 | 1985 |

|

SU1285593A1 |

| Синхронный делитель частоты | 1987 |

|

SU1431066A1 |

| Делитель частоты | 1985 |

|

SU1338062A1 |

| Делитель частоты на 11 | 1987 |

|

SU1522398A1 |

| Синхронный делитель частоты | 1986 |

|

SU1406787A1 |

| Синхронный делитель частоты на 14 | 1986 |

|

SU1368983A1 |

| Синхронный делитель частоты на 10 | 1984 |

|

SU1225009A1 |

| Синхронный делитель частоты | 1986 |

|

SU1396273A1 |

| Синхронный делитель частоты | 1986 |

|

SU1396275A1 |

| Синхронный делитель частоты | 1986 |

|

SU1429317A1 |

Изобретение относится к цифро- .,вой электронной технике. Может быть использовано при создании хронизато- ров,цифровых синтезаторов частоты и т.п. Цель изобретения - повышение надежности делителя - достигается введением синхронного режима работы, а также уменьшением числа элементов и связей. Делитель содержит 1К-триг- геры 1-5, логический элемент (ЛЭ) И-НЕ 6, ЛЭ И 7, шины: входную тактовую 8, сброса 9, выходные 10 и И. 1 табл. 2 ил. фиг. 1

| Будинский Я | |||

| Логические цепи в цифровой технике./Под ред | |||

| Б.А.Калабекова.М.: Связь, 1977 | |||

| Лейнов М.Л | |||

| и др | |||

| Цифровые делители частоты иа логических элементах | |||

| М.: Энергия, 1975, с | |||

| Спускная труба при плотине | 0 |

|

SU77A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-04-23—Публикация

1984-10-11—Подача