Изобретение относится к цифровой технике и может быть использовано, например, для построения хронизато- ров, цифровых синтезаторов частоты, электромузыкальных инструментов и т.п.

Цель изобретения - повышение надежности работы путем уменьшения скважности импульса переноса на выходе устройства.

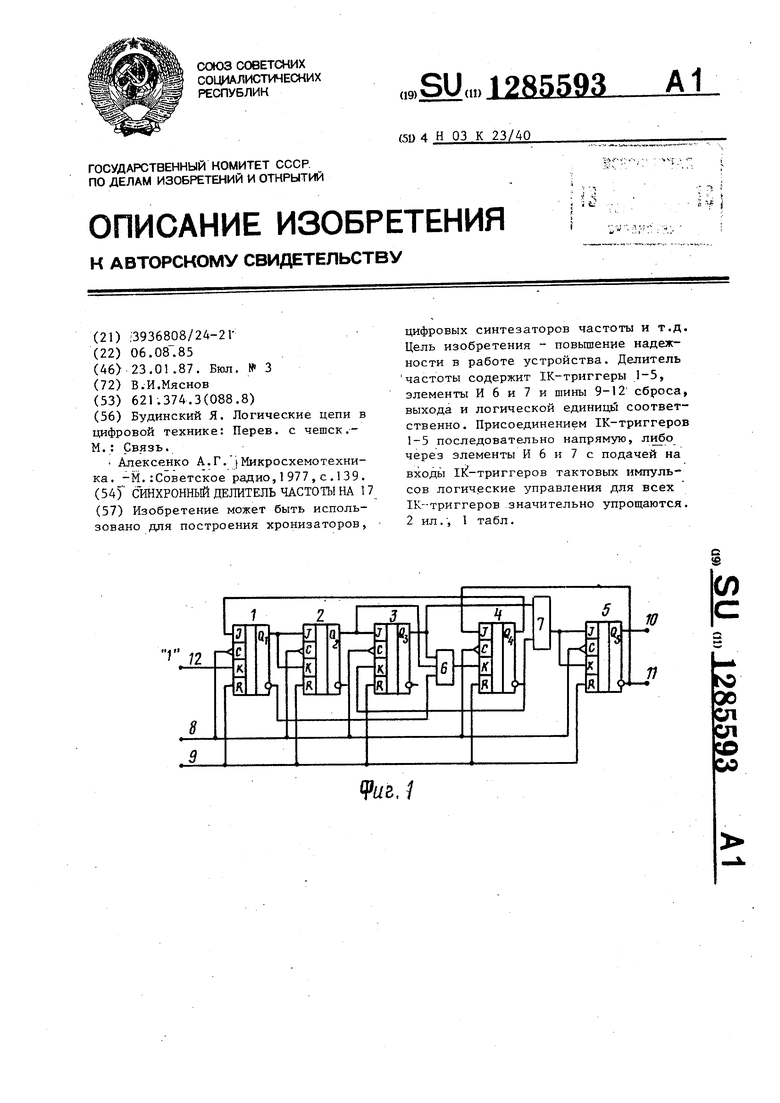

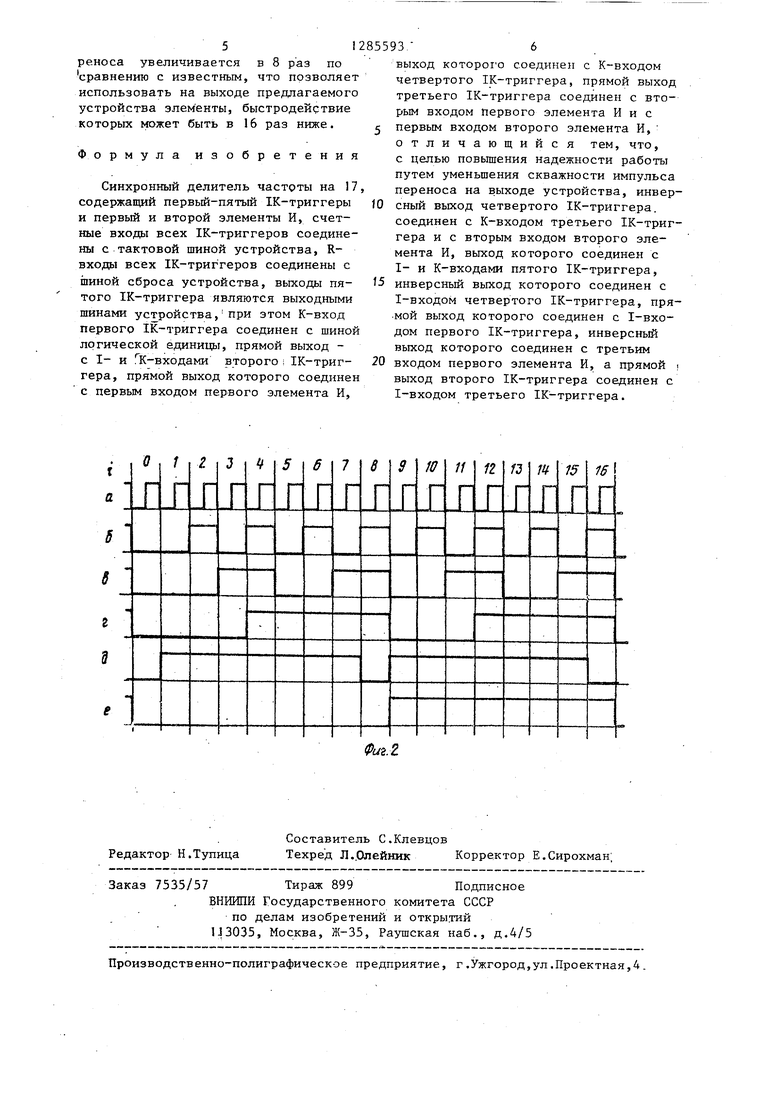

На фиг. приведена функциональная схема синхронного делителя частоты на 17; на фиг.2 - временные диаграммы работы устройства.

Синхронный делитель частоты на 17 содержит первый-пятый 1К-триггеры 1-5, первый 6 и второй 7 элементы И, тактову70 шину 8, шину 9 сброса усройства и выходные шины 10 и 11, а также шину 12 логической единицы.

Счетные входы всех 1К-триггеров 1-5 соединены-с тактовой шиной 8, R-йходы всех 1К-триггеров 1 - 5 соединены с шиной 9 сброса устройства, выходы пятого 1К.-триггера 5 являются выходными шинами 10 и 11 устройства.

Прямой выход первого 1К-трИггера 1 соединен с I- и К-входами второго .1К-триггвра 2, прямой выход которого соединен с первым входом первого элемента-И 6 и с 1 входом третьего 1К-триггера 3, прямой выход которого соединен с вторым входом первого элемента Ибис первым входом второго элемента И 7, выход которого соеди- нен с I- и- К-входами пятого 1К-триг гера 5, инверсный выход которого сое Динен с 1-входом четвертого 1К-тригг

ра 4, прямой выход которого соединен

с 1-входом первого 1К-триггера 1, ин

версныи выход которого соединен с третьим входом элемента И 6, выход которого соединен с К-входом четвертого 1К-триггера 4, инверсный выход которого соединен с вторым входом втрого элемента И 7 и с К-входом третьего 1К-триггера, первого IK- триггера 1 соединен .с шиной логичес- кой единиидз, прямой выход второго 1К триггера 2 соединен с 1-входом третьего 1К-триггера 3,

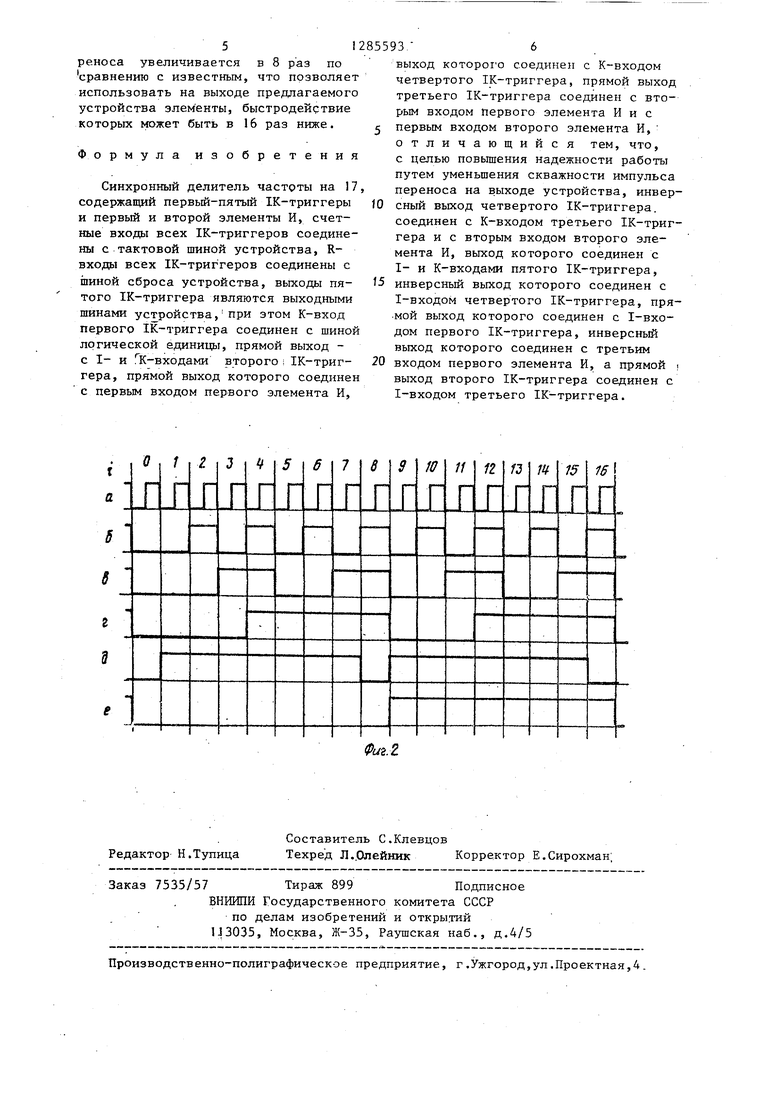

.Вследствие такой схемы соединений элементов логические уравнения для I- и К-входрв всех 1К-триггероа 1-5 синхронного делителя частоты на 17 следующие (фиг.1):

if-Q4,; .i,Q,;i,Q,, ,Q4L K,,;K,Q4;K4 Q,,Q4

5

0

50

5

0

j Q

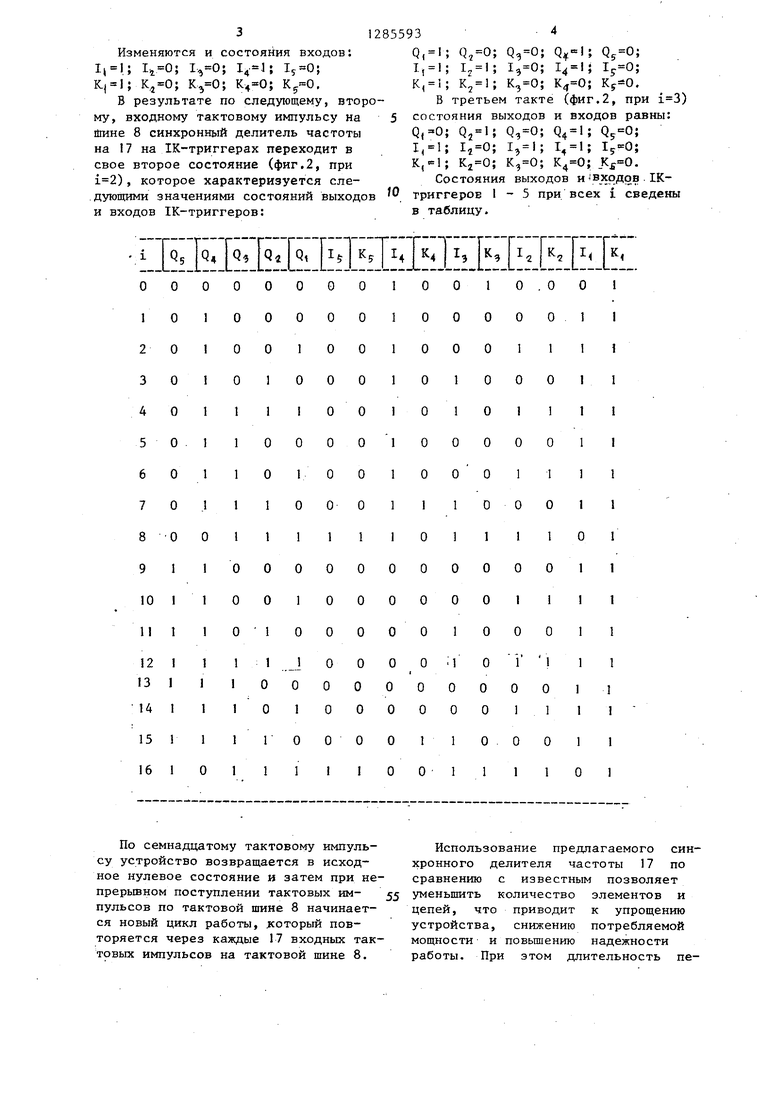

На фиг.2 обозначено: Г - порядковый номер состояния предлагаемого синхронного делителя часто ты на 17 на 1К-триггерах, порядковый номер входного тактового импульса на тактовой шине 8; а - входной сигнал на тактовой шине 8; 8 - сигнал Q( на прямом выходе Q( первого 1К-триггера IJ сигнал Qj на прямом выходе Qj второго 1К-триггера 2; i - сигнал Q на прямом выходе Qj третьего 1К-тригге- ра 3; .- сигнал Q на прямом выходе Q( четвертого 1К-триггера 4; е - сигнал Qy на прямом выходе Q IK- триггера 5.

Примем, что 1К-триггеры 1 - 5 устройства переключаются под действием отрицательного перепада сигнала в момент его изменения с высокого уровня .(логической единицы)до низкого уровня (логического нуля) на входной тактовой шине 8.

Работа синхронного делителя частоты полностью определяется логическими уравнениями для I- и К-входов его 1К триггеров.

По сигналу Сброс, пост щагощему по шине 9 сброса устройства, по входам R все 1К- триггеры 1 - 5 устанавливаются в исходное нулевое состояние. В этом случае при (фиг.2) состояния выходов pasifti:

Q,0; Q, Q,0; . . Ha основании логических уравнений I-и К-входов IK-триггеров 1 - 5 состояния входов следующие: I, ,

j Q

К Q 0;

5

K,Q,

0; .

Поскольку IK-триггер по последу- юш,ему входному тактовому импульсу на тактовой шине 8 при и не изменяет своего состояния, при и переключается в противоположное состояние, при и К О переключается в состояние логической едини1.Ыэ а при 1 состояние .логического нуля, то по первому входному тактовому импульсу на тактовой шине 8 четвертый 1К-триггер 4 переключается в состояние логической единицы, а остальные 1К-триггеры 1, 2, 3 и 5 не изменяют своего состояния 1(фиг.2, при i.l). При этом состояния выходов равны:

Q,0; Q,0; .

Изменяются и состояния входов: 1)1; Г,0; К,0; ,

В результате по следующему, второму, входному тактовому импульсу на шине 8 синхроннь1й делитель частоты на 17 на 1К-триггерах переходит в свое второе состояние (фиг.2, при ), которое характеризуется слеQ, l; Q,0; . I,l; I,0; K,l; K,0; .

В третьем такте (фиг.2, при ) 5 состояния выходов и входов равны: Q,-0; Q,0; 1; I, l; 1 1;

K, K,0; .

Состояния выходов и ВХОДОВ. IKдующими значениями состояний выходов триггеров 1 - 5 при/всех i сведены и входов IK-триггеров:в таблицу.

По семнадцатому тактовому импульсу устройство возвращается в исходное нулевое состояние и затем при не- прерьшном поступлении тактовых им- пульсов по тактовой шине 8 начинается новый цикл работы, соторый повторяется через каждые 17 входных тактовых импульсов на тактовой шине 8.

Q, l; Q,0; . I,l; I,0; K,l; K,0; .

В третьем такте (фиг.2, при ) состояния выходов и входов равны: Q,-0; Q,0; 1; I, l; 1 1;

K, K,0; .

Использование предлагаемого синхронного делителя частоты 17 по сравнению с известным позволяет уменьшить количество элементов и цепей, что приводит к упрощению устройства, снижению потребляемой мощности и повышению надежности работы. При этом длительность переноса увеличивается в 8 раз по сравнению с известным, что позволяет использовать на выходе предлагаемого устройства элементы, быстродействие которых может быть в 16 раз ниже.

Формула изобретения

Синхронный делитель частоты на 17 содержащий первый-пятый 1К-триггеры и первый и второй элементы И, счетные входы всех 1К-триггеров соединены с тактовой шиной устройства, R- входы всех 1К-триггеров соединены с шиной сброса устройства, выходы пятого 1К-триггера являются выходными шинами устройства, при этом К-вход первого 1К триггера соединен с шиной логической единицы, прямой выход - с I- и К-входами второго ; 1К-триг- гера, прямой выход которого соединен с первым входом первого элемента И,

Редактор Н.Тупица

Составитель С.Клевцов

Техред Л..0лейник Корректор Е.Сирохман;

Заказ 7535/57 Тираж 899Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий U3035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород,ул.Проектная,4.

выход которого соединен с К-входом четвертого 1К-триггера, прямой выход третьего 1К-триггера соединен с вторым входом Первого элемента И и с

первым входом второго элемента И, отличающийся тем, что, с целью повьшения надежности работы путем уменьшения скважности импульса переноса на выходе устройства, инверсный выход четвертого 1К-триггера. соединен с К-входом третьего 1К-триг- гера и с вторым входом второго элемента И, выход которого соединен с I- и К-входами пятого 1К-триггера,

инверсный выход которого соединен с 1-входом четвертого 1К-триггера, пря- мой выход которого соединен с 1-входом первого 1К-триггера, инверсный выход которого соединен с третьим

входом первого элемента И, а прямой i выход второго 1К-триггера соединен с 1-входом третьего 1К-триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный делитель частоты на 14 | 1986 |

|

SU1368983A1 |

| Синхронный делитель частоты | 1986 |

|

SU1396275A1 |

| Синхронный делитель частоты | 1986 |

|

SU1396274A1 |

| Делитель частоты на 19 | 1984 |

|

SU1226660A1 |

| Синхронный делитель частоты | 1986 |

|

SU1406787A1 |

| Декадный счетчик для семисегментных индикаторов | 1985 |

|

SU1330757A1 |

| Синхронный делитель частоты | 1986 |

|

SU1396273A1 |

| Синхронный делитель частоты | 1987 |

|

SU1431066A1 |

| Синхронный делитель частоты | 1986 |

|

SU1354415A1 |

| Синхронный делитель частоты на 12 | 1984 |

|

SU1221747A1 |

Изобретение может быть использовано для построения хронизаторов, цифровых синтезаторов частоты и т.д. Цель изобретения - повышение надежности в работе устройства. Делитель частоты содержит 1К-триггеры 1-5, элементы И 6 и 7 и шины 9-12 сброса, выхода и логической единицы соответственно. Присоединением 1К-триггеров 1-5 последовательно напрямую, либо через элементы И 6 и 7 с подачей на входы 1 -триггеров тактовых импульсов логические управления для всех IK-триггеров значительно упрощаются. 2 ил., 1 табл. Фиг,/

| Будинский Я | |||

| Логические цепи в цифровой технике: Перев | |||

| с чешек.- М.: Связь | |||

| Алексенко А.Г | |||

| Микросхемотехника | |||

| -М.:Советское радио,1977,с | |||

| Способ подпочвенного орошения с применением труб | 1921 |

|

SU139A1 |

Авторы

Даты

1987-01-23—Публикация

1985-08-06—Подача