Изобретение относится к цифровой технике и может быть использовано при построении хронизаторов, цифровы синтезаторов частоты, электронных часов и т. п.

Цель, изобретения - расширение функциональных возможностей путем получения сигнала переноса и нулевого исходно- Vo состояния, при этом сокращается число связей, необходимых для сброса устройства.

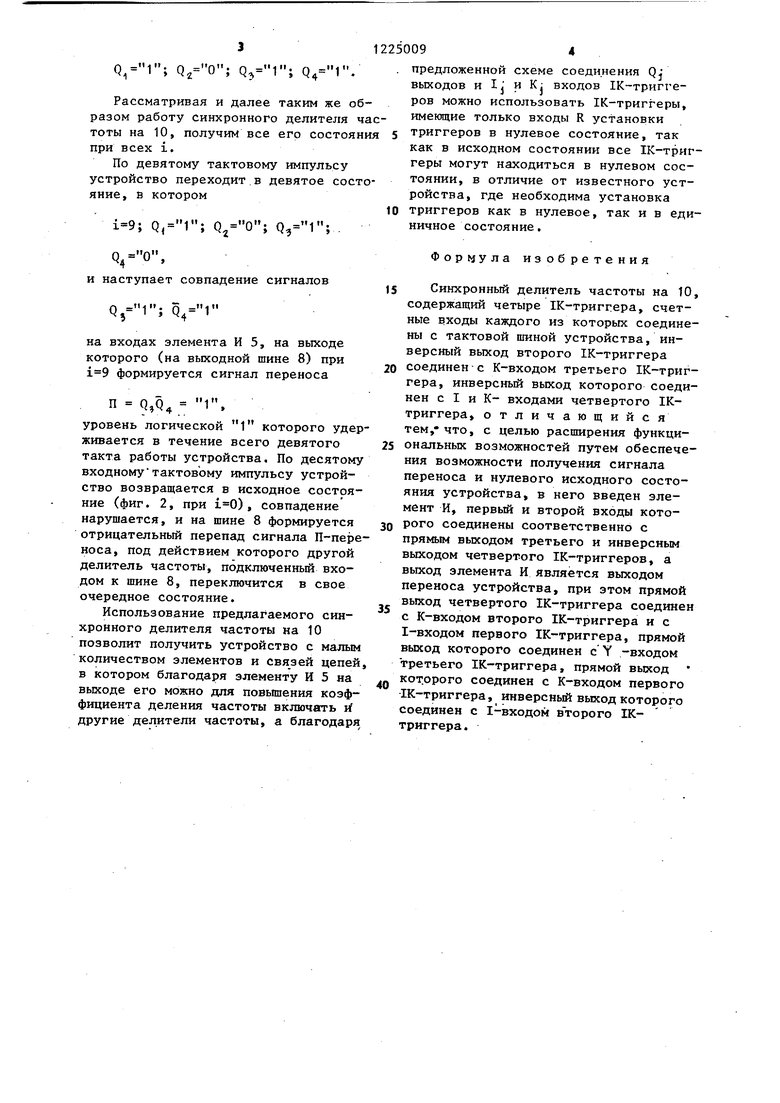

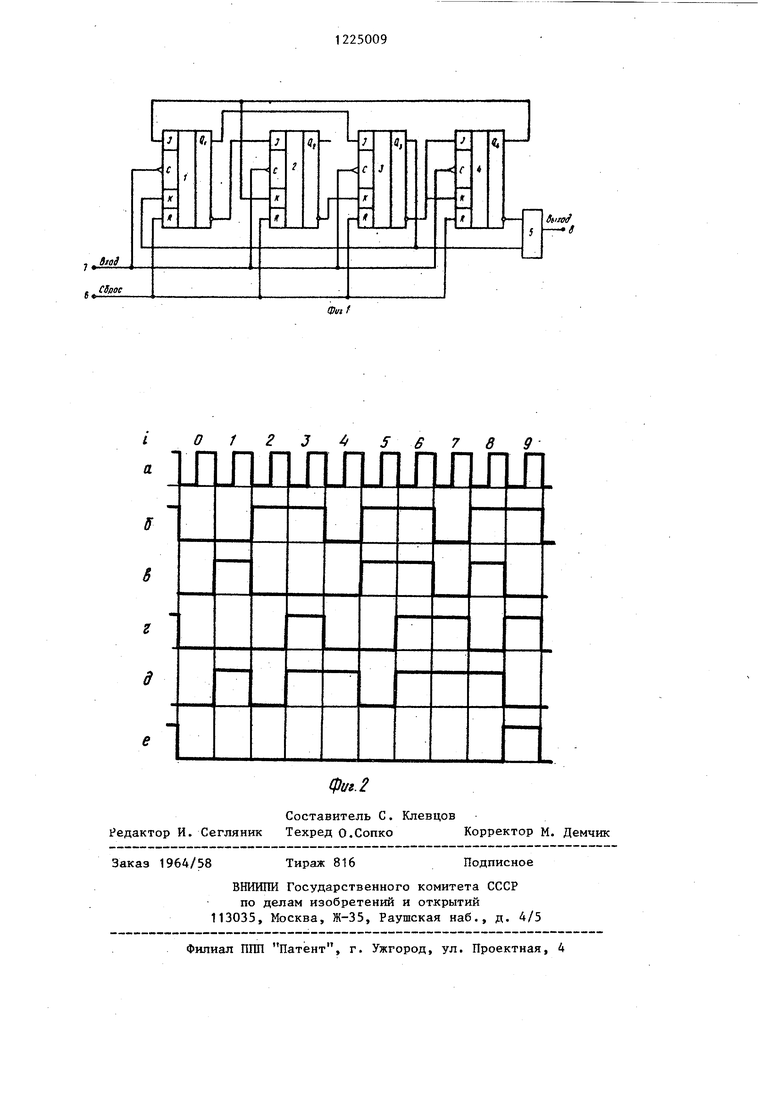

На фиг. 1 приведена функциональная схема синхронного делителя частоты на 10; на фиг. 2 - временные диаграммы работы устройства, где а - входные тактовые импульсы на тактово шине; - сигнал Q f на прямом выходе Q первого 1К-триггера; о - сигнал С 2 на прямом выходе Q „ второго IK- триггера; г - сигнал Qj на прямом выходе Q 5 третьего 1К-триггера; сигнал Q на прямом вЬгходе Q четвертого 1К-триггера; 6 - сигнал переноса на выходе устройства.

Синхронный делитель частоты на 10 содержит чет ыре 1К-триггера 1-4 и элемент 5 И, шину сброса 6, тактовую шину 7. Счетные входы всех 1К-триг- .геров соединены с тактовой шиной 7 устройства, инверсньй выход второго 1К-триггера 2 соединен с К-входом третьего 1К-триггера 3, инверсньй выход которого соединен с I и К- : входами четвертого Ш-триггера 4, первый и второй входы элемента 5 И соединены соответственно с прямым выходом третьего 3 и инверсным выходом четвертого 4 1К-триггера, а выг ход - с выходной шиной 8 устройства, при этом прямой выход, четвертого 1К-триггера 4 соединен с 1-входом первого 1К-триггера. 1, прямой выход которого соединен с 1-входом третьег 1К-триггера 3, прямой выход которого со единен с К-входом первого 1К-триг- гера 1, инверсньй выход которого соединен с 1-входом второго IK-триггера 2 К-вход которого соединен с прямым - выходом четвертого 1К-триггера 4.

При указанной .схеме соединения элементов логические уравнения I- и К-входов всех 1К-триггеров делителя частоты на 10 следукяцие

i(Q4; ,; ,; 14

К, Q,; .K,Qi; К,

По импульсу Сброс на шине 6 сброса все 1К-триггеры устройства

устанавливаются в исходное нулевое состояние. При этом состояния выходов равны (фиг. 2 при )

Q, Q, Q, .

На основании логических уравнений для I- и К-входов устройства состояния входов следующие

10

Т П т П 1. -ч х 2 И

Ч.

Т п п

J-5 1,- и ,

K,Q,

V n n 1

. 4j I 4-43- I

Ha фиг. 1 и 2 принято, что IK- триггеры переключаются в противоположное состояние по отрицательному перепаду сигнала на счетном входе.

По первому тактовому импульсу первый 1К-триггер 1 не изменит своего состояния (так как в исходном состоянии при у него 1,), вто- рой 1К-триггер 2 переключится в состояние логической единиш 1 (так как при , ), третий 1К-триггер 3 не изменит своего состояния (так как при , и первьй тактовьй импульс лишь подтвердит его нулевое состояние), чет- вертьй 1К-триггер 4 переключится в противоположное, единичное, состояние (так как при ), и состояния выходов (диаграммы на ,фиг. 2 при ) станут равны

Qj, Q, . Изменяются и состояния входов

1,

К, .

В результате, после второго тактового импульса, устройство перейдет во второе состояние (фиг. 2 при ), характеризующееся следующими значениями выходов и входов

Q,

I,

т i-) I ,

55

к к V 1. V f Z 9 4

По третьему тактовому импульсу устройство переключится в третье сое- тояние (фиг. 2 при );

л 11ч1 . п П П 1

1 Z 3 4

Рассматривая и далее таким же образом работу синхронного делителя частоты на 10, получим все его состояния при всех 1.

По девятому тактовому импульсу устройство переходит.в девятое состояние, в котором

Q, .

, и наступает совпадение сигналов

Q 1

на входах элемента И 5, на выходе которого (на выходной шине 8) при формируется сигнал переноса

П Q,Q 1,

уровень логической 1 которого удерживается в течение всего девятого такта работы устройства. По десятому входному тактовому импульсу устройство возвращается в исходное состояние (фиг. 2, при ), совпадение нарушается, и на шине 8 формируется отрицательный перепад сигнала П-пере- носа, под действием которого другой делитель частоты, подключенный входом к шине 8, переключится в свое очередное состояние.

Использование предлагаемого синхронного делителя частоты на 10 позволит получить устройство с малым количеством элементов и связей цепей, в котором благодаря элементу И 5 на выходе его можно для повьштения коэффициента деления частоты включать rf другие делители частоты, а благодаря

094

предложенной схеме соединения Qj виходов и 1 и Kj входов 1К-тригге- ров можно использовать 1К-триггеры, имеющие только входы R установки триггеров в нулевое состояние, так как в исходном состоянии все 1К-триг- геры могут находиться в нулевом состоянии, в отличие от известного устройства, где необходима установка триггеров как в нулевое, так и в единичное состояние.

Формула изобретения

Синхронный делитель частоты на 10, содержащий четыре 1К-триггера, счетные входы каждого из которых соединены с тактовой шиной устройства, инверсный выход второго IK-триггера соединен с К-входом третьего 1К-триг- гера, инверсный выход которого соединен с I и К- входами четвертого IK- триггера, отличающийся тем, что, с целью расширения функциональных возможностей путем обеспечения возможности получения сигнала переноса и нулевого исходного состояния устройства, в него введен элемент И, первый и второй входы которого соединены соответственно с прямым выходом третьего и инверсным выходом четвертого 1К-триггеров, а выход элемента И является выходом переноса устройства, при этом прямой выход четвертого 1К-триггера соединен с К-входом второго 1К-триггера и с 1-входом первого 1К-триггера, прямой выход которого соединен с Y -входом третьего 1К-триггера, прямой выход которого соединен с К-входом первого 1К-триггера, инверсный выход которого соединен с 1-входом второго IK- триггера.

0123 56789

фиг. 2

Составитель С. Клевцов

Редактор И. Сегляник Техред О.Сопке

Заказ 1964/58

Тираж 816

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Корректор М. Демчик

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты на 19 | 1984 |

|

SU1226660A1 |

| Синхронный делитель частоты на 14 | 1986 |

|

SU1368983A1 |

| Синхронный делитель частоты на 17 | 1985 |

|

SU1285593A1 |

| Делитель частоты на 11 | 1987 |

|

SU1522398A1 |

| Синхронный делитель частоты на 9 | 1986 |

|

SU1378055A1 |

| Синхронный делитель частоты | 1986 |

|

SU1396273A1 |

| Синхронный делитель частоты | 1986 |

|

SU1406787A1 |

| Синхронный делитель частоты | 1986 |

|

SU1396274A1 |

| Синхронный делитель частоты | 1987 |

|

SU1431066A1 |

| Делитель частоты | 1985 |

|

SU1338062A1 |

Изобретение относится к ци$5й- вой технике и может быть использовано при построении хронизаторов, цифровых синтезаторов частоты и т.д. Цель изобретения - расширение функциональных возможностей. Устройство содержит 1К-триггеры 1-А, элемент И 5, шину 6 сброса, тактовую шину 7 и выходную шину 8. Введение в устройство элемента И и образование новых связей между его элементами позволяет получить сигнал переноса и нулевого исходного состояния и сократить число связей, необходимых для сброса устройства. 2 ил.

| Лейнов М.Л | |||

| и др | |||

| Цифровые дели тели частоты на логических элементах М.: Энергия, 1975 | |||

| Пересчетная декада | 1982 |

|

SU1064478A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-04-15—Публикация

1984-10-04—Подача