1 1

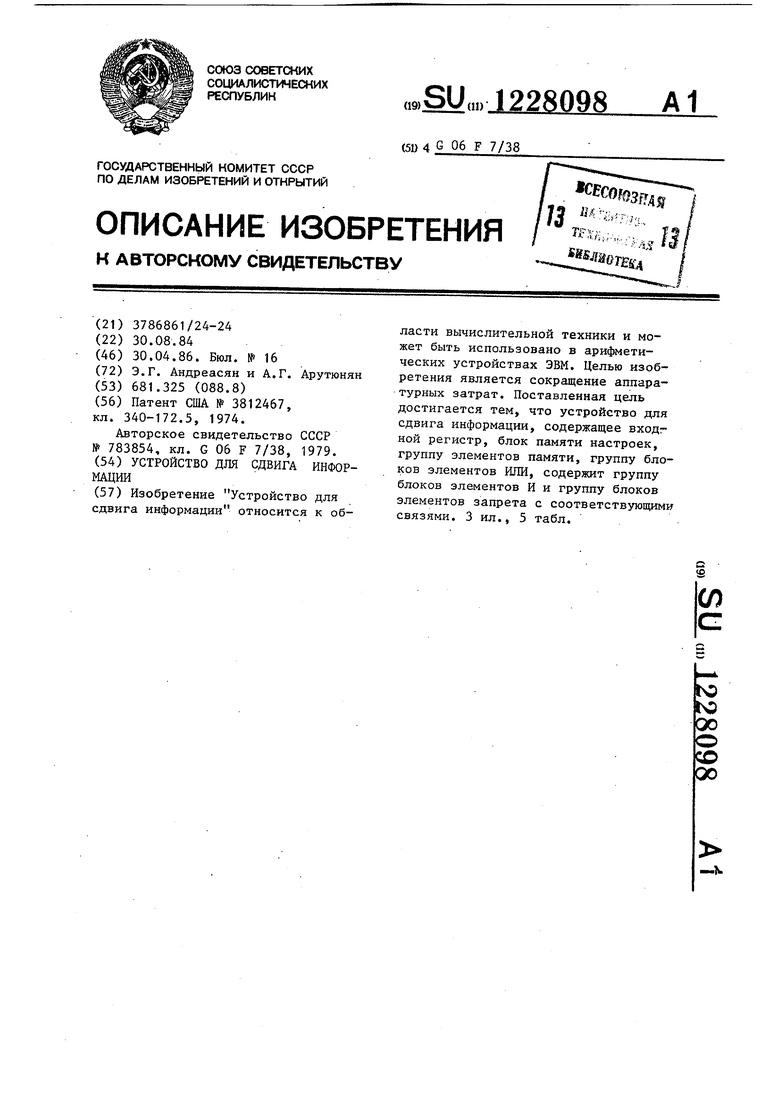

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах ЭВМ для сдвига и преобразования форматов данных.

Цель изобретения - сокращение аппаратурных затрат.

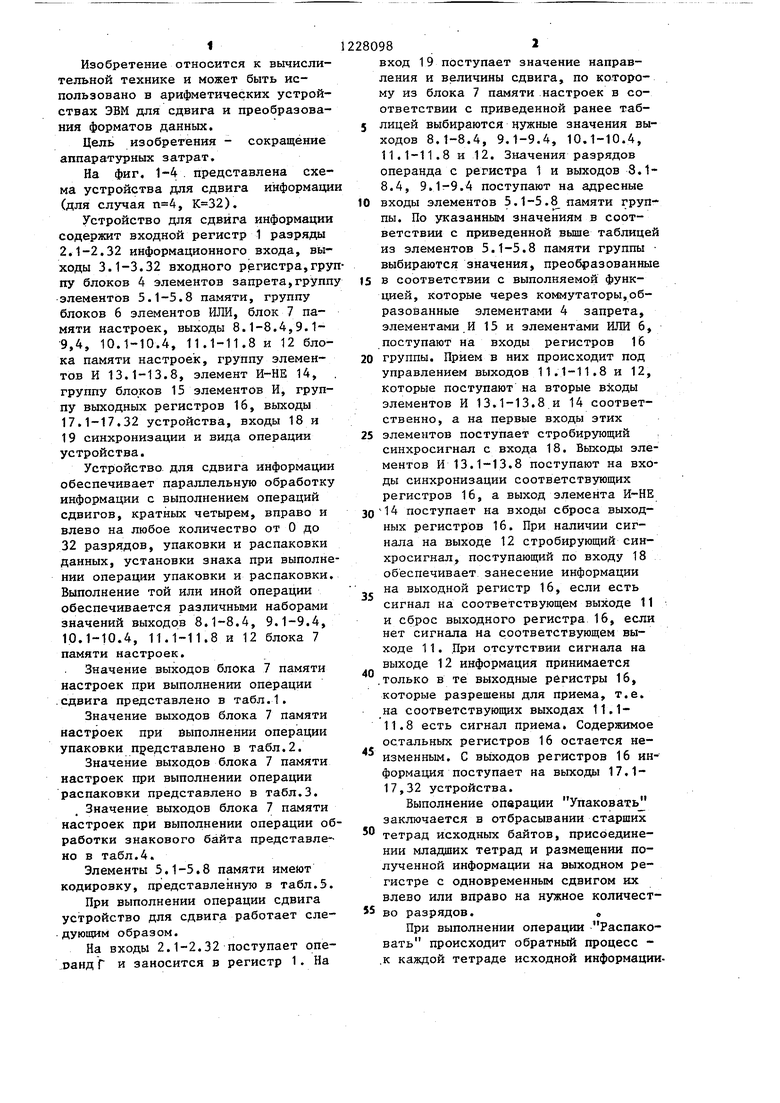

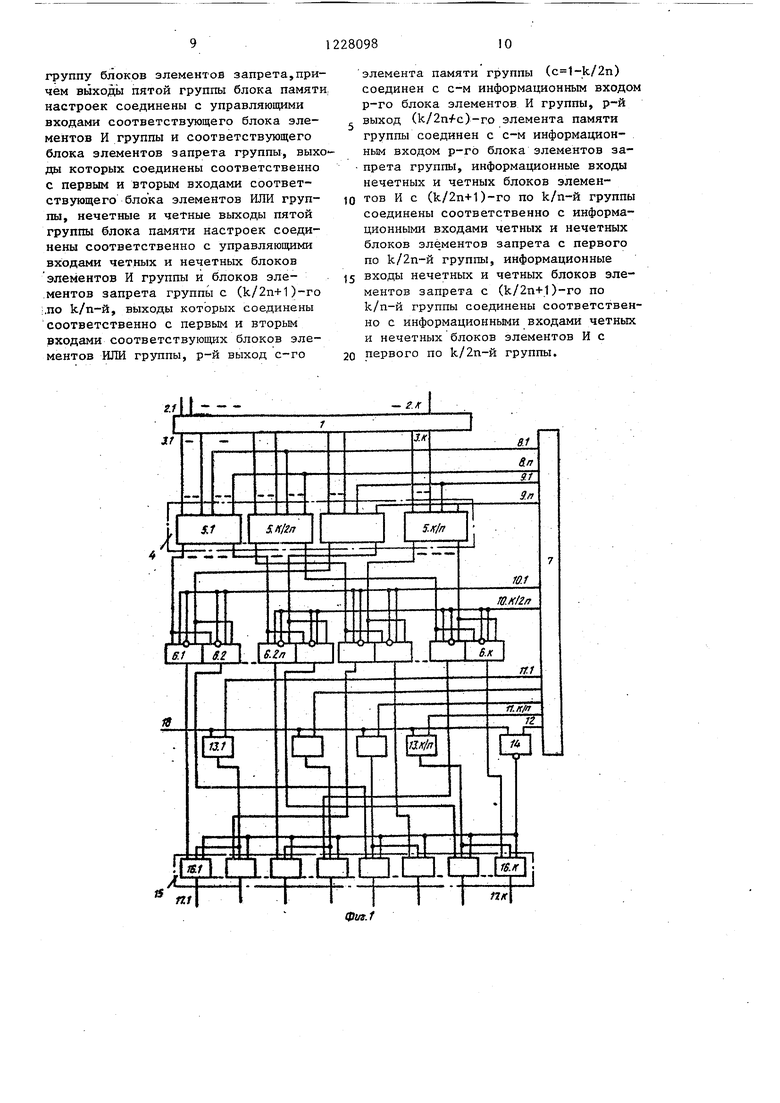

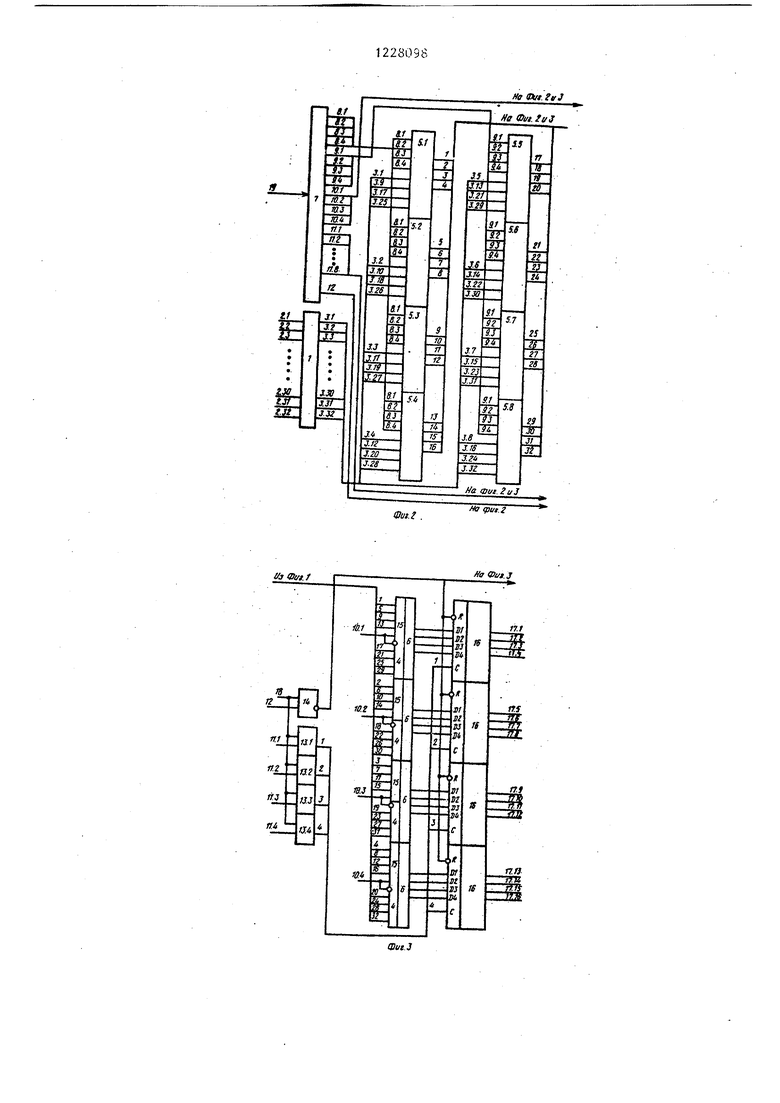

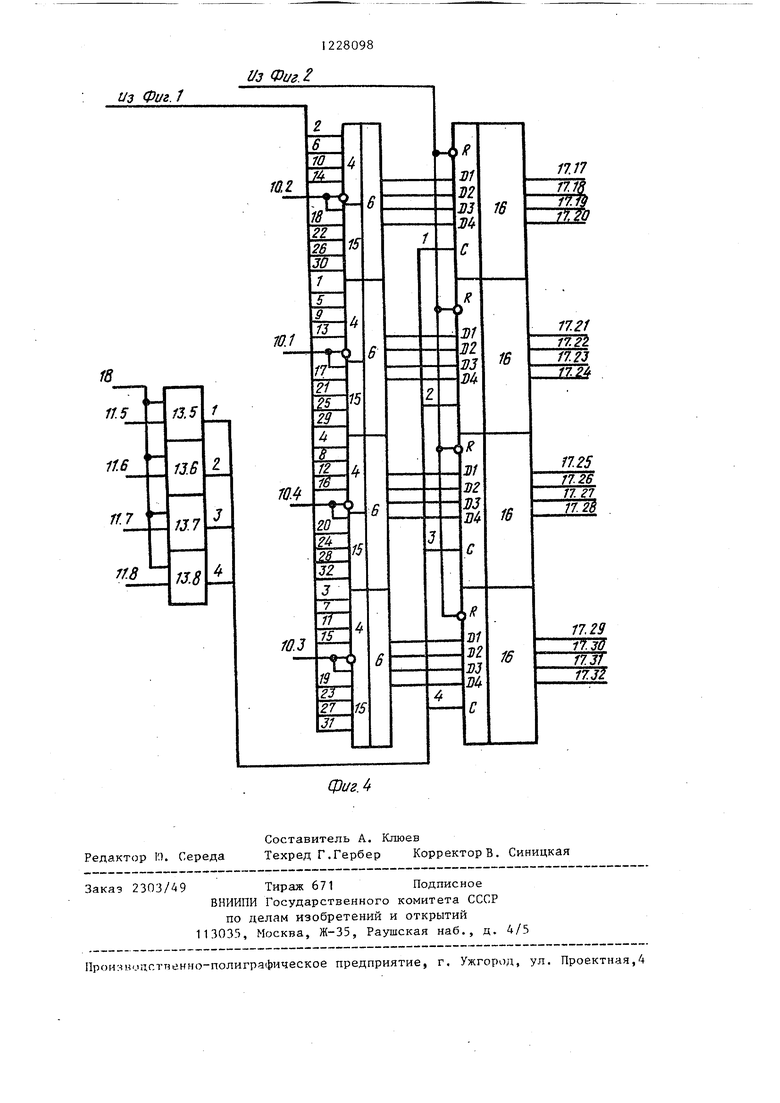

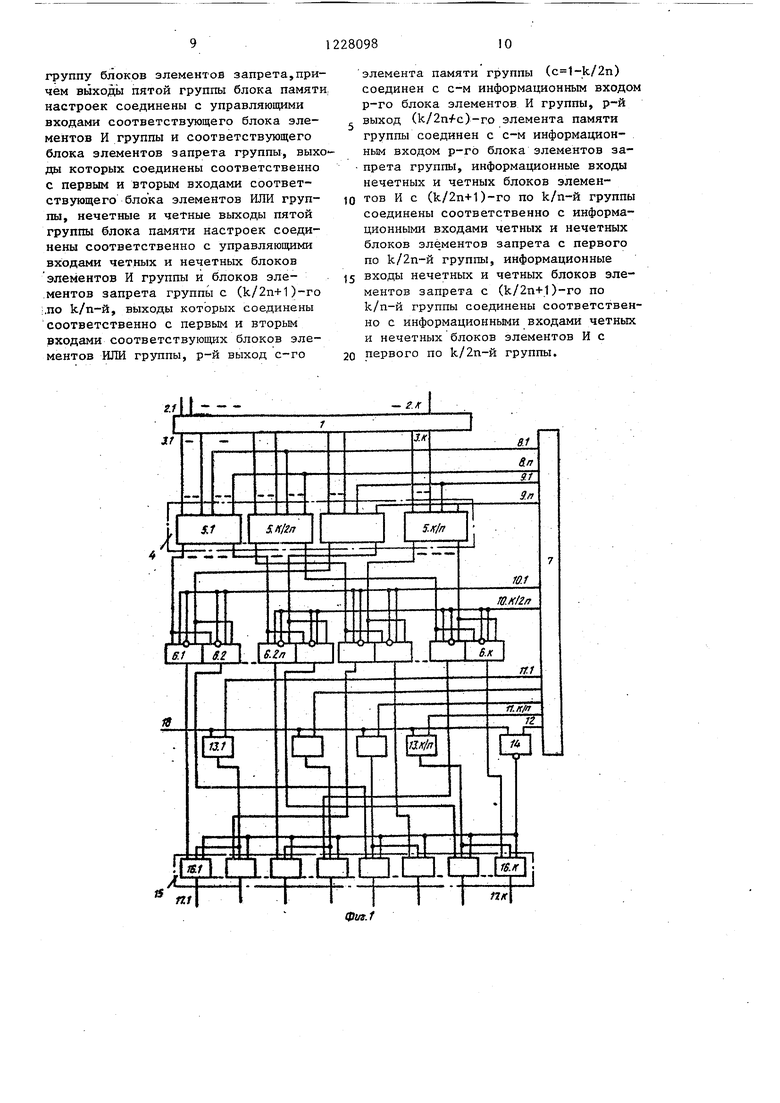

На фиг, 1-4 . представлена схема устройства для сдвига информации (для случая , ).

Устройство для сдвига информации содержит входной регистр 1 разряды 2.1-2.32 информационного входа, выходы 3.1-3.32 входного регистра,группу блоков 4 элементов запрета,группу элементов 5.1-5.8 памяти, группу блоков 6 элементов ИЛИ, блок 7 памяти настроек, выходы 8.1-8.4,9.1- 9,4, 10.1-10.4, 11.1-11.8 и 12 блока памяти настроек, группу элементов И 13.1-13.8, элемент И-НЕ 14, , группу блоков 15 элементов И, группу выходных регистров 16, выходы 17.1-17.32 устройства, входы 18 и 19 синхронизации и вида операции устройства.

Устройство, для сдвига информации обеспечивает параллельную обработку информации с выполнением операций сдвигов, кратных четырем, вправо и влево на любое количество от О до 32 разрядов, упаковки и распаковки данных, установки знака при выполнении операции упаковки и распаковки. Выполнение той или иной операции обеспечивается различными наборами значений выходов 8.1-8.4, 9.1-9.4, 10.1-10.4, 11.1-11.8 и 12 блока 7 памяти настроек.

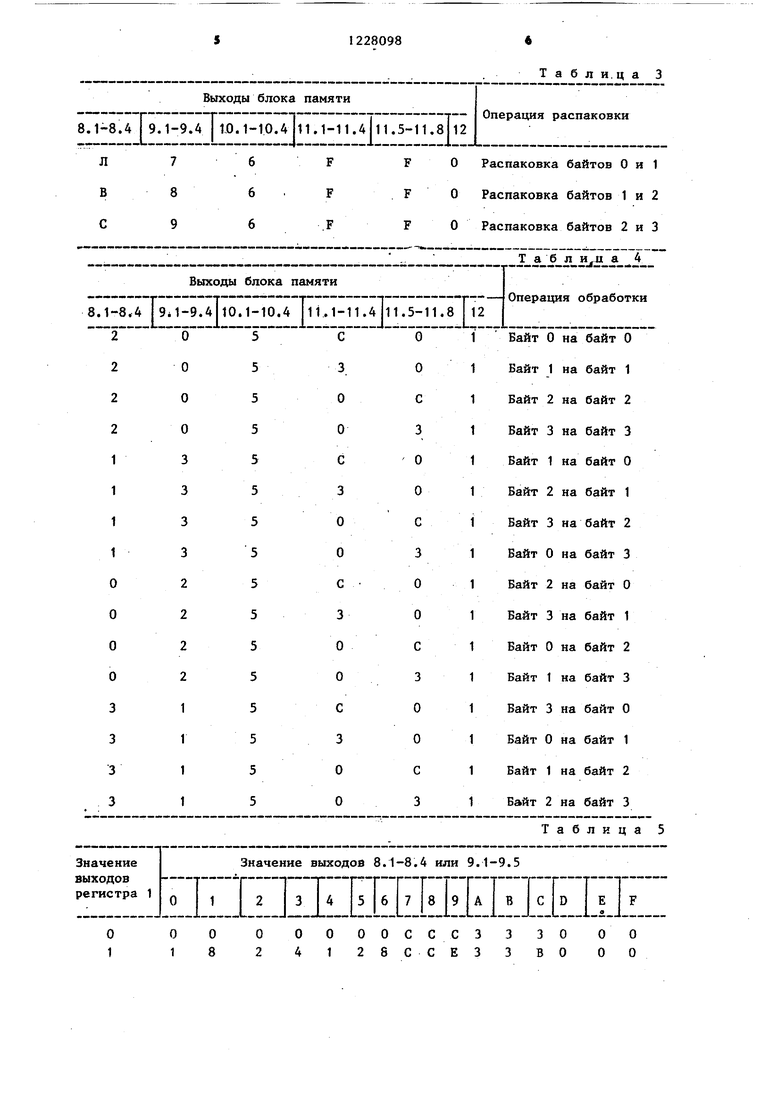

Значение выходов блока 7 памяти настроек при выполнении операции двига представлено в табл.1.

Значение выходов блока 7 памяти астроек при выполнении операции паковки представлено в табл.2.

Значение выходов блока 7 памяти астроек при выполнении операции аспаковки представлено в табл.3.

Значение выходов блока 7 памяти настроек при выполнении операции обаботки знакового байта представлео в табл.4.

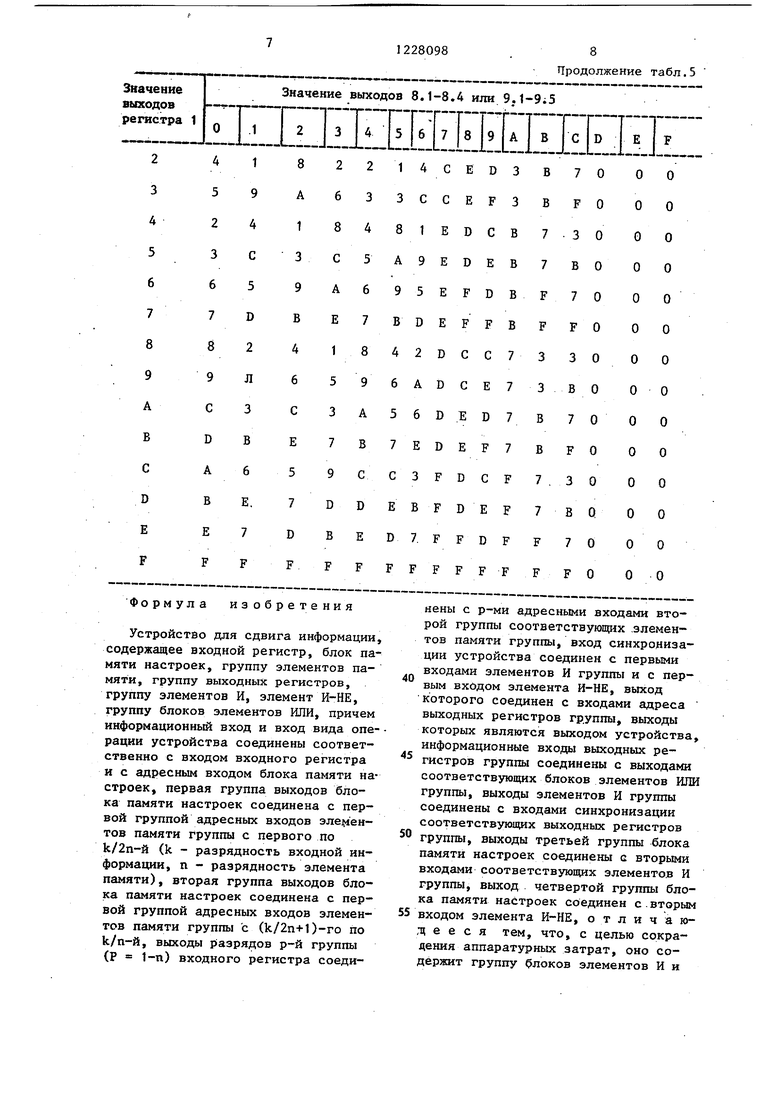

Элементы 5.1-5.8 памяти имеют одировку, представленную в табл.5.

При выполнении операции сдвига стройство для сдвига работает сле- ующим образом.

На входы 2.1-2.32 поступает опеанд Г и заносится в регистр 1. На

28098J

вход 19 поступает значение направления и величины сдвига, по которому из блока 7 памяти .настроек в соответствии с приведенной ранее таб-

5 лицей выбираются нужные значения выходов 8.1-8.4, 9.1-9.4, 10.1-10.4, 11.1-11.8 и 12. Значения разрядов операнда с регистра 1 и выходов 8.1-- 8.4, 9.1-9.4 поступают на адресные

10 входы элементов 5.1-5 .8 памяти группы. По указанным значениям в соответствии с приведенной выше таблицей из элементов 5.1-5.8 памяти группы выбираются значения, преобразованные

15 в соответствии с выполняемой функцией, которые через коммутаторы,образованные элементами 4 запрета, элементами И 15 и элементами ИЛИ 6, поступают на входы регистров 16

20 группы. Прием в них происходит под управлением выходов 11.1-11.8 и 12, которые поступают на вторые входы элементов И 13.1-13.8и 14 соответственно, а на первые входы этих

25 элементов поступает стробирующий синхросигнал с входа 18. Выходы элементов И 13.1-13.8 поступают на входы синхронизации соответствующих регистров 16, а выход элемента И-НЕ

поступает на входы сброса выходных регистров 16. При наличии сигнала на выходе 12 стробирующий синхросигнал, поступающий по входу 18 обеспечивает занесение информации на выходной регистр 16, если есть сигнал на соответствующем выходе 11 и сброс выходного регистра 16, если нет сигнала на соответствующем выходе 11. При отсутствии сигнала на выходе 12 информация принимается .только в те выходные регистры 16, которые разрешены для приема, т.е. на соответствующих выходах 11.1- 11.8 есть сигнал приема. Содержимое остальных регистров 16 остается неизменным. С выходов регистров 16 информация поступает на выходы 17.1- 17,32 устройства.

Выполнение операции Упаковать заключается в отбрасывании старших тетрад исходньпс байтов, присоединении младших тетрад и размещении полученной информации на выходном регистре с одновременным сдвигом их влево или вправо на нужное количест 5 во разрядов.„

При выполнении операции Распаковать происходит обратный процесс - .к каждой тетраде исходной информации35

40

50

пристраивается тетрада с единицами во всех разрядах и полученные байты передаются на выходной регистр. В этих операциях происходит параллельное получение до четьфех байтов результата.

Операции обрабо 1 ки знакового байта применяются в командах упаковки и распаковки данных. При выполнении этих команд в исходный момент производится обработка знакового байта, одна из тетрад которого содержит

О

О О

5 .6

F С

3 О

2280984

младшую цифру числа,а другая - шестнадцатиричный код знака этого числа, Преобразов.ание этого байта сводится к сдвигу вправо левой тетрады и сдви- 5 гу влево правой тетрады этого .байта на четьфе разряда, -а затем размещению полученного байта в требуемом регистре 16.

Указанные олерации выполняются to аналогично операции сдвига с учетом соответствующих кодировок блока 7 памяти настроек.

Таблица 1

Таблица 2

О 1 Результат на байты О и 1

С 1 Результат на байты 1 и 2 F 1 Результат на байты 2 и 3

Табли.ца 3

Значение выходов регистра 1

Значение выходов 8.1-8.4 или 9.1-9;5

2 3 4 5 6 7 8 9 А В С D Е F

4 5 2 3 6 7 8 9 С D А В Е F

- пачспис oDiAu ua о. |-о.ч или у, |.J

Е1П1ЕШП1Ш1Ш11-

1

9

4

С

5

D

2

Л

3

В

6

Е.

7

F

8 А 1 3 9 В 4 6 С Е 5 7 D F

2 2 1 4 С Е D 3 6 3 3CCEF3

84 8 1 Е D С В С 5 A9EDEB А 6 95EFDB

В D Е F F В

42 D С С 7

6А D С Е 7

56 D Е D 7

7Е D Е F 7

9CC3FDCF D D EBFDEF

D 7. F F D F

В В

7

7 8 9

A В

В Е F F

F F F F F F

70

F0

30

7В0 F 70 F F0 330 3 В0

870 В FО 7.3О 7 ВQ F 7О F FО

О

О

О

О

О

О

О

О

О

О

О

О

о

о

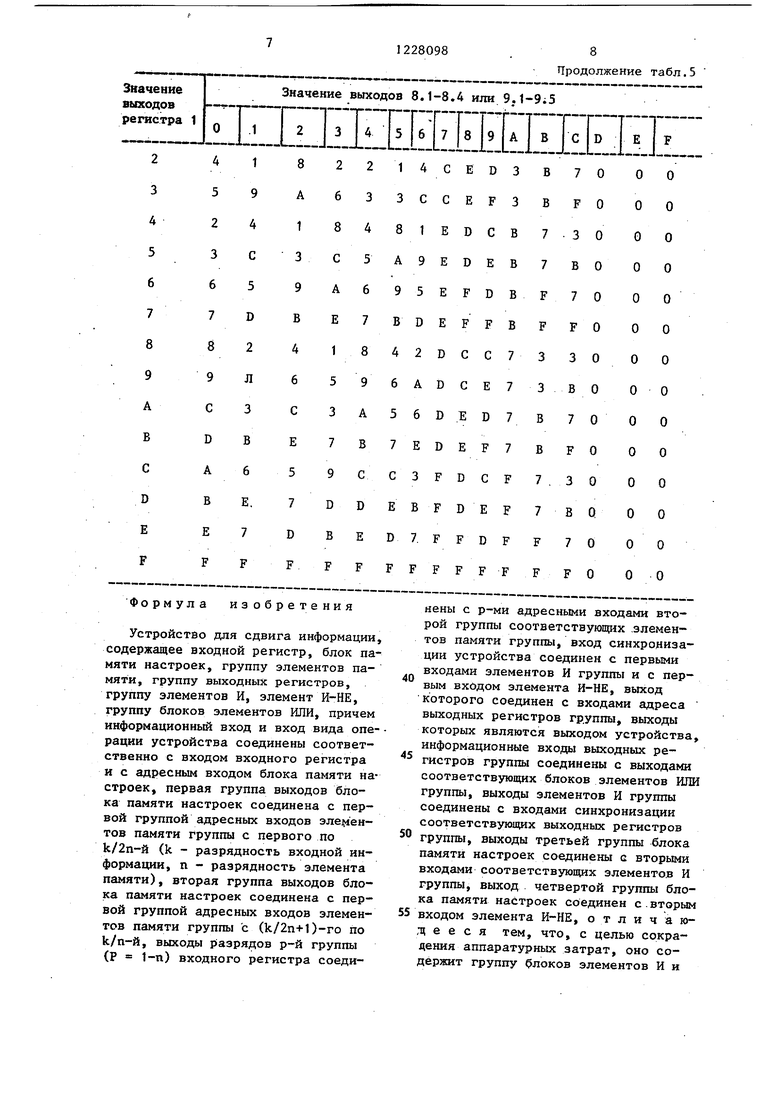

Формула изобретения

Устройство для сдвига информации, содержащее входной регистр, блок памяти настроек, группу элементов памяти, группу выходных регистров, группу элементов И, элемент И-НЕ, группу блоков элементов ИЛИ, причем информационный вход и вход вида операции устройства соединены соответственно с входом входного регистра и с адресным входом блока памяти настроек, первая группа выходов блока памяти настроек соединена с первой группой адресных входов элементов памяти группы с первого по и/2п-й (k - разрядность входной информации, п - разрядность элемента памяти), вторая группа выходов блока памяти настроек соединена с первой группой адресных входов элементов памяти группы с (k/2n+1)-ro по k/п-й, выходы разрядов р-й группы (Р 1-п) входного регистра соедиШП1Ш1Ш11-

2 1 4 С Е D 3 3 3CCEF3

4 8 1 Е D С В 5 A9EDEB 6 95EFDB

В D Е F F В

42 D С С 7

6А D С Е 7

56 D Е D 7

7Е D Е F 7

C3FDCF EBFDEF

D 7. F F D F

В В

7

7 8 9

В

F F F F F F

70

F0

30

7В0 F 70 F F0 330 3 В0

870 В FО 7.3О 7 ВQ F 7О F FО

F

ОО

ОО

ОО

ОО

ОО

ОО

ОО

ОО

ОО

ОО

ОО

Оо

оо

оо

йены с р-ми адресными входами второй группы соответствующих .элементов памяти группы, вход синхронизации устройства соединен с первыми входами элементов И группы и с первым входом элемента И-НЕ, выход которого соединен с входами адреса выходных регистров группы, выходы которых являются выходом устройства, информационные входы выходных регистров группы соединены с выходами соответствующих блоков элементов ИЛИ группы, выходы элементов И группы соединены с входами синхронизации соответствующих выходных регистров

группы, выходы третьей группы блока памяти настроек соединены с вторыми входами соответствующих элементов И группы, выход четвертой группы блока памяти настроек соединен с.вторым

входом элемента И-НЕ, отличающееся тем, что, с целью сокра- дення аппаратурных затрат, оно содержит группу блоков элементов И и

группу блоков элементов запрета,причем выходы пятой группы блока памятИ настроек соединены с управляющими входами соответствующего блока элементов И группы и соответствующего блока элементов запрета группы, выходы которых соединены соответственно с первым и вторым входами соответствующего блока элементов ИЛИ группы, нечетные и четные выходы пятой группы блока памяти настроек соединены соответственно с управляющими входами четных и нечетньк блоков элементов И группы и блоков эле- .ментов запрета группы с (k/2n+1)-ro ;.по k/n-й, выходы которых соединены соответственно с первым и вторым входами соответствующих блоков элементов ИЛИ группы, р-й выход с-го

элемента памяти группы (c 1-k/2n) соединен с с-м информационным входом р-го блока элементов И группы, р-й J выход (k/2nfc)-ro элемента памяти группы соединен с с-м информационным входом р-го блока элементов за- прета группы, информационные входы нечетных и четных блоков элемен10 тов И с (k/2n+1)-ro по k/n-й группы соединены соответственно с информационными входами четных и нечетных блоков элементов запрета с первого по k/2n-й группы, информационные

15 входы нечетных и четных блоков элементов запрета с (k/2n+1)-ro по k/n-й группы соединены соответственно с информационными входами четных и нечетных блоков элементов И с

20 первого по k/2n-й группы.

iSut.Z .

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОЛИНОМИАЛЬНЫЙ МОДУЛЯРНЫЙ ВЫЧИСЛИТЕЛЬ СИСТЕМ БУЛЕВЫХ ФУНКЦИЙ С ОБНАРУЖЕНИЕМ ОШИБОК | 2015 |

|

RU2586574C1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Арифметическое устройство процессора быстрого преобразования Фурье | 1981 |

|

SU999061A1 |

| Устройство для масштабирования числа в интервально-модулярном коде | 1986 |

|

SU1305678A1 |

| Устройство для сдвига информации | 1979 |

|

SU783854A1 |

| Система обработки нечеткой информации | 1987 |

|

SU1444803A1 |

| Устройство для умножения 12N-разрядных двоичных чисел | 1988 |

|

SU1589271A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОКАЛЬНЫХ ПОРЯДКОВЫХ СТАТИСТИК | 1990 |

|

RU2024934C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Устройство для умножения | 1985 |

|

SU1278838A1 |

Изобретение Устройство для сдвига информации относится к области вычислительной техники и может быть использовано в арифметических устройствах ЭВМ. Целью изобретения является сокращение аппаратурных затрат. Поставленная цель достигается тем, что устройство для сдвига информации, содержащее входг ной регистр, блок памяти настроек, группу элементов памяти, группу блоков элементов ИЛИ, содержит группу блоков элементов И и группу блоков элементов запрета с соответствующими связями. 3 ил., 5 табл. (Л G .

Оз tDift.t

Us Фиг.

фиг Л

Редактор I ). Середа

Составитель А. Клюев

Техред Г.Гербер КорректорВ. Синицкая

Заказ 2303/49 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113033, Москва, Ж-35, Раушская наб., д. 4/5

Прон; нм11сгпенмо-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

| Патент США № 3812467, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Устройство для сдвига информации | 1979 |

|

SU783854A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-04-30—Публикация

1984-08-30—Подача