Г -- -

Изобретение относится к области вычислительной техники и может быть использовано в арифметических логических устройствах вычислительных машин для сдвига и преобразования форма тов данных.

Известны устройства для сдвига данных, содержание ряд клапанов, расположенных в виде прямоугольной матрицы, предназначенные для циклического и нециклического смещения в одном такте многоразрядного входного сигнала на заданное число разрядов влево или вправо lj . Это устройство . не обеспечивает преобразования форматов данных.

Известно также устройство для преобразования форматов данных, содержащее специальную логическую схему состоящую из многоканальных ин- . формационных селекторов,посредством которых данные из запокшнающего устройства выводятся в преобразованной форме f2 .

Наиболее близким к изЬбретению по технической сущности является устройство, содержаг- ее входной и выходной регистры, к - азрядный сдвигатель, управляющий блок. Причем к-разрядный сдвИгатель построен на коммутаторах в h ярусов по тя коммутаторов в каждом, информационные входы коммутаторов соединены с выходами входного регистра,а управлякхиие входы - с выходами управляюгцего блока выполненного в виде счетчика .

Это устройство относительно сложное, а также оно не осуществляет

to функции преобразования формата данных, для выполнения которой в его состав необходимо включить новые цепи коммутаторов, что приведет к еще большему усложнению.

15

Цель изобретения - упрощение устройства.

Поставленная цель достигается тем, что в устройство для сдвига информации, содержащее входной ре20гистр, выходы которого соединены с первыми входами сдвигателя,блок управления, первые входы которого подключены ко вторым входам сдвигателя, выходной регистр,йыходы которого со

25 единены с выходами устройства,входы которого подсоединены ко входам входного регистра, и шину син хронизации, введены элементы И, элементы И-НЕ и элементы ИЛИ,

30

Яйдй которых соединены с выходами двигателя. Выходы элементов ИЛИ одключены к первым входам выходного регистра, вторые входы которых соединены с выходом элемента И-НЕ. дин из входов элемента И-НЕ сое- . инен со вторым выходом блока управёния, третьи выходы которого подклмчены к первым входам элементов И, вторые входы которых соединены с другим входом элемента И-НЕ и шиной синхронизации.

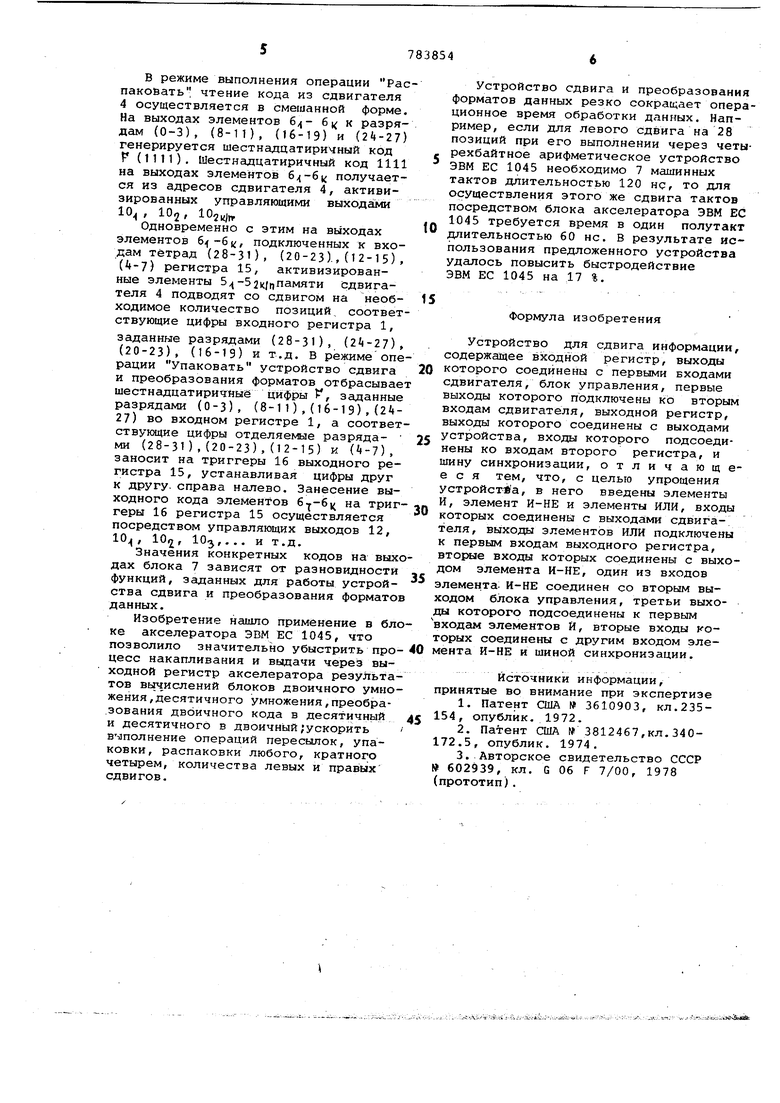

На чертеже изображена Лункцибнальная схема предложенного устройства .

Оно содержит входной регистр 1, . входы (где К -число разрядов), выходы входного регистра 1, сдвигатель 4, содержащий элементы 5 -Ьгц/г памяти (где П -количество информационных входов элементов памяти ), элементы ИЛИ , блок 7 управления с выхоЭД дами , 9д-9г,, ,,n, ,, и 12, элементы И , элемент И-НЕ 14, выходной регистр 15, содержащий триггеры , выходы , устройства и шину 18 синхронизации.25

Рассмотрим работу устройства при количестве разрядов к. 32, количестве информационных входов и выходов п - 4, управлякмдих входов п+1е4+1 5. Нумерация разрядов от О до 31, где О - стар-jQ ший разряд, 31 - младший разряд. Чтобы выполнить сдвиг 32 разрядов на любое . количество позиций влево или вправо необходимо задать 64 управляющие функции. Это в данном устройстве обес- е печивается двумя различными наборами выходов , и 10, 10(, ,.. ., 102ц|пИ комбинациями логических единиц и нулей на выходах И и 12 блока 7.

Если код на управляющих входах эле-40 ментов 5 т 5J,(rJ пaмяти-0000, а на информационных входах произвольное значение ХХХХ, то из элементов с адресам ООООХХХХ будет считан четырех разрядный код, идентичный 5 выходному коду, и подан через элементы ИЛИ )4 на входы регистра 15. В этом случае 32-раэрядный сдвигатель 4 может выполнять две элементарные операции: нет сдвига, если на выходах5д 11 -11з2 логические единицы, на выходе 12 - логический нуль, сдвиг 32 при логической единице на выходе 12 и логических нулях на выходах, ,,2 . Из изложенного следует, что каждый вес управляющих кодов на выходах и в данном устройстве может обесп1эчить выполнение двух операций сдвига. Если коду с определенным весом присвоить функцию правого сдвига на число позиций i , то этим же ко- 40 IfeWrtb Ho реалйзовать левый сдвиг на число позиций 32-i.Например,кодом сдвигп ,влево на 4 позиции обеспечиваотся npaBufi сдвиг нп 28 позиций ,сдвитп ппоно и nrjp.THo на 1(5 .иЯ обес- 5

печиваются тем же кодом и т.д.Когда код управления задает правый сдвиг на 8 и левый сдвиг на 24 позиции,на входах регистра 15 через элементы ИЛИ из элементов 5 и („памяти считывается и подводится следующее: на входы разрядов (0-23) - информация разрядов (8-31) входного регистра 1, на входы (24-31) - информация разрядов (0-7). При этом устройством выполняется левый сдвиг на 24 позиции(сдвиг влево 24), если на выходах 11 - llg логические единицы, а на выходах И - л гические нули, сдвиг вправо выполняется, если на выходах Но llj логические единицы, а на выходах 11g - логические нули.

В режиме выполнения операции Упаковать и распаковать в исходный момент работы устройства для сдвига и преобразования форматов производится обработка знакового байта, содержащего иве тетрады, одна-задающая самую крайнюю правую цифру числа, а другая - шестнадцатиричный код знака числа. Преобразование этого байта сводится к сдвигу вправо левой тетрады и сдвигу влево правой тетрады на четыре разряда, а затем к размещению полученного нового байта на место знакового байта в триггерах 16 выходного регистра 15. При преобразовании знакового байта возможны 16 различных случаев, что обусловлено адресами исходного знакового байта и байта назначения в триггерах 16 выходного регистра 15.

Пример 1. Позиция знакового байта во входном регистре 1 задана разрядами (24-31), а в триггерах 16 выходного регистра 15 - разрядами (8-15). Преобразование знакового байта Приведёт к передачам, к входам разрядов (8-11) выходного регистра 15 будет подана информация разрядов (28-31) регистра 1, а к входам разрядов (12-15) регистра 15 - разрядов (24-27) входного регистра 1. Одновременно с подачей этих сдвинутых кодов на выходах 12,11о-11|, будут установлены логические единицы, на выходах и llj H-ja логические нули.

Пример 2. Позиция знакового байта в регистре 1 определена разрядами (0-7), в регистре 15 - разрядами (16-23). Преобразование в этом случае вызываетпередачи: к входам разрядов (16-19) выходного регистра ,15 подводятся разряды(4-7) входного регистра 1, а на входы разрядов (2023) подводятся разряды (О-З) входного регистра 1. При этом логические единицы устанавливаются на выходах 12,lli-{ -1124 а на выходах , и lljy и llj устанавли чаются лог-ические нули. В режиме выполнения операции Рас пако&ать чтение кода из сдвигателя 4 осуществляется в смешанной форме, На выходах элементов 6 к разрядам (0-3), (8-11), (16-19) и генерируется шестнадцатиричный код Р (1111), Шестнадцатиричный код 1111 на выходах элементов бх-6( получается из адресов сдвигателя 4, активизированных управляющими выхода ли lOj , Одновременно с этим на выходах элементов (, подключенных к входам тетрад (28-31), (20-23)., (12-15) , (4-7) регистра 15, активизированные элементы 5 -52к/ппамяти сдвигателя 4 подводят со сдвигом на необходимое количество позиций, соответствующие цифры входного регистра 1, заданные разрядами (28-31), (), (20-23), (16-19) и т.д. В режиме опе рации Упаковать устройство сдвига и преобразования форматов отбрасывае шестнадцатиричные цифры f, заданные разрядами (0-3), (8-11) , (16-19),(2427) во входном регистре 1, а соответ ствующие цифры отделяемые разряда- ми (28-31), (20-23), (12-15) и (4-7), заносит на триггеры 16 выходного регистра 15, устанавливая цифры друг к другу, справа налево. Занесение выходного кода элементов на триг геры 16 регистра 15 осуществляется посредством управляющих выходов 12, 10, 102, 10з- т.д. Значения конкретных кодов на выхо дах блока 7 зависят от разновидности функций, заданных для работы устройства сдвига и преобразования форматов данных. Изобретение нашло применение в бло ке акселератора ЭВМ ЕС 1045, что позволило значительно убыстрить процесс накапливания и выдачи через выходной регистр акселератора результатов вычислений блоков двоичного умножения ,десятичного умножения,преобра.зования двоичного кода в десятичный и десятичного в двоичный/ускорить выполнение операций пересылок, упаковки, распаковки любого, кратного четырем, количества левых и правых сдвигов. Устройство сдвига и преобразования форматов данных резко сокращает операционное время обработки данных. Например, если для левого сдвига на 28 позиций при его выполнении через четырехбайтное арифметическое устройство ЭВМ ЕС 1045 необходимо 7 машинных тактов длительностью 120 не г то для осуществления этого же сдвига тактов посредством блока акселератора ЭВМ ЕС 1045 требуется время в один полутакт длительностью 60 не. В результате использования предложенного устройства удалось повысить быстродействие ЭВМ ЕС 1045 на 17 %. Формула изобретения Устройство для сдвига информации, содержащее входной регистр, выходы которого соединены с первыми входами сдвигателя, блок управления, первые выходы которого подключены ко вторым входам сдвигателя, выходной регистр, выходы которого соединены с выходами устройства, входы которого подсоединены ко входам второго регистра, и шину синхронизации, отличающееся тем, что, с целью упрощения устройства, в него введены элементы И, элемент И-НЕ и элементы ИЛИ, входы которых соединены с выхода1ми сдвигателя, выходы элементов ИЛИ подключены к первым входам выходного регистра, вторые входы которых соединены с выходом элемента И-НЕ, один из входов элемента- И-НЕ соединен со вторым выодом блока управления, третьи выхоы которого подсоединены к первым ходам элементов И, вторые входы коорых соединены с другим входом элеента И-НЕ и шиной синхронизации. Источники информации, принятые во внимание при экспертизе 1.Патент США № 3610903, кл.235154, опублик, 1972. 2.Патент США № 3812467,кл.340172.5, опублик. 1974. 3.Авторское свидетельство СССР № 602939, кл. G 06 F 7/00, 1978 (прототип).

; SgSi rV 3:k -i

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Устройство для сдвига информации | 1984 |

|

SU1228098A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1988 |

|

SU1621182A1 |

| Преобразователь форматов данных | 1982 |

|

SU1092490A1 |

| Преобразователь форматов данных | 1985 |

|

SU1290535A1 |

| Устройство для преобразования двоичных чисел в двоично-десятичные и обратно | 1983 |

|

SU1142826A1 |

| Матричное устройство для умножения | 1979 |

|

SU842800A1 |

| Устройство для обработки данных переменной длины | 1986 |

|

SU1675897A1 |

| Преобразователь форматов данных | 1986 |

|

SU1466012A1 |

n i

I7i I 7г

Kl

Авторы

Даты

1980-11-30—Публикация

1979-01-05—Подача