Арифметические устройства, выполняющие операцию умножения, известны. Основной недостаток подобных устройств заключается в ТОМ, ЧТО онерация умножения требует значительного времени. Это отрицательно сказывается на быстродействии машин. Значительное сокращение времени вынолнения улшожения в известных устройствах достигается одновременной расщифровкой значений нар разрядов множителя, но это значнтельно усложняет арифметическое устройство вычислительной машины.

Предлагаемое устройство обеспечивает сокращение времени необходимого для вьшол 1ения онерации умножения без значительного усложнения арифметического устройства. Этс достигается нрименением в электронной вычислительной машине параллельного действия логнческой схемы для выработки управляющих импульсов при расшифровке значений пар разрядов множителя.

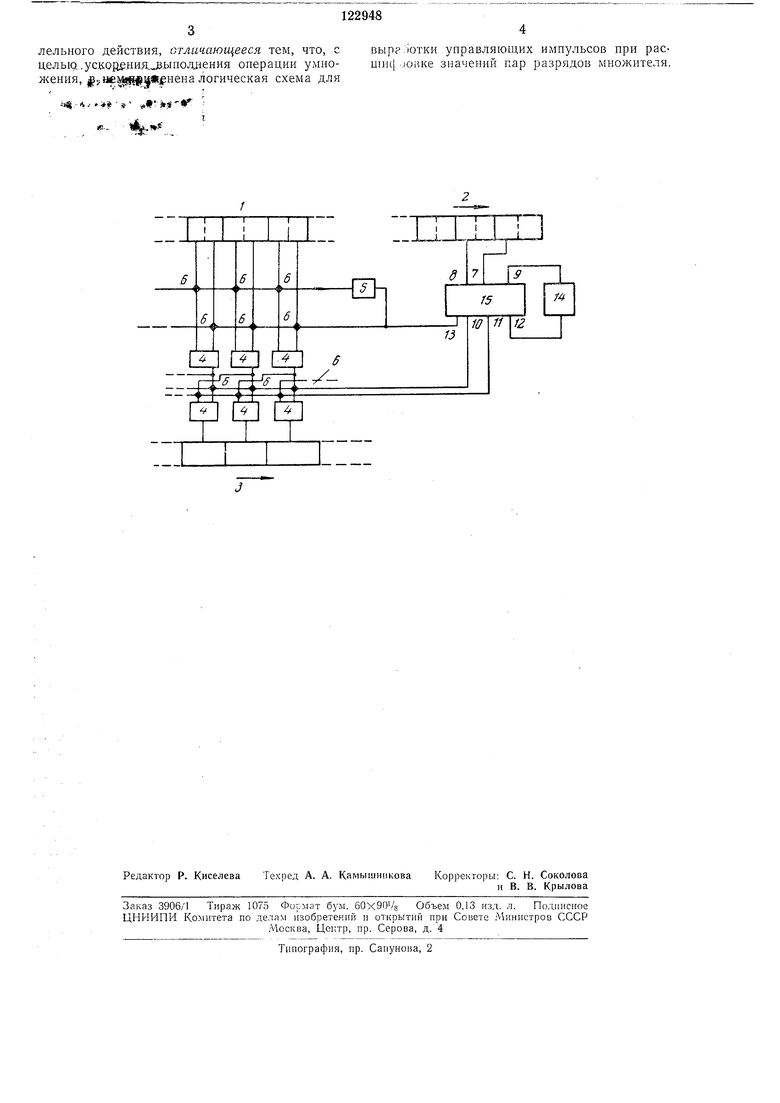

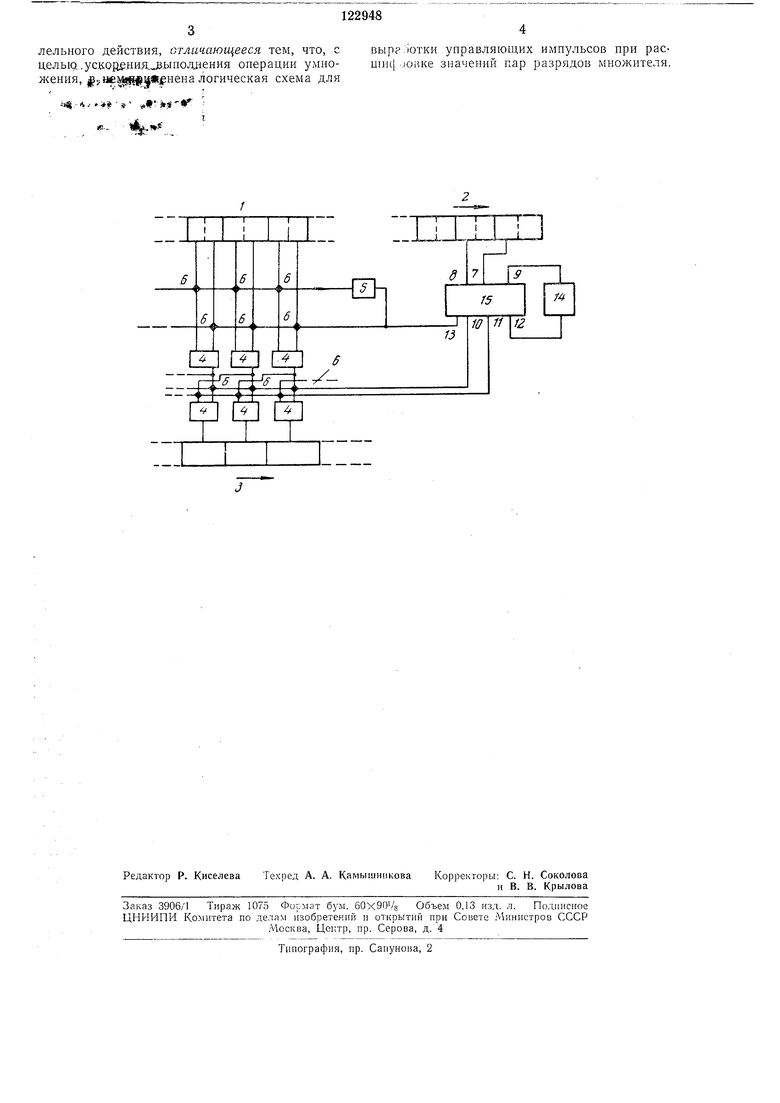

Скелетная схема устройства приведена на чертеже, где даны следующие обозначения:

1 - регистр множимого, 2 - регистр множителя, 3 - регистр произведения, 4 - логические устройства «ИЛИ, 5 - логическая схема «НЕТ, 6 - вентили, 7 - цифра, соответствующая младшему из нары разрядов множителя, на который производится умножение, 8 - цифра, соответствующая старшему

из нары разрядов множителя, 9 - единица переноса, возникающая в результате предшествующего такта частичного нроизведения,

10- переключательная функция, но признаку которой к частнчному нроизведению нрибавляется произведение множимого на 2,

11- переключательная функция, по признаку которой к частичному произведению прибавляется произведение множимого на 2t,

12 - единица переноса в старшнй разряд множителя, 13 - переключающая функция, по признаку которой к частичному нроизведенпю прибавляется произведение множимого на 2 в прямом или в обратном ходе, 14 -

цень задержки на время одного такта, 15 - логическая схема для выработки управляющих н.мпульсов.

Р1спользуя устройства «ПЛП н подавая через них на сумматор в нрямол; или обратном

коде произведение множимого на 2- или только в прямом коде пропзведеиие множимого на 2i, производя г умножение одновременно на два разряда множителя за один такт. При ЭТОМ сдвиг множнтеля и частичного ироизведения должен осуществляться одновремеиио на два разряда.

Предмет и з о б р е т е и и я

Арифмегическое ycTpoiicTBo для электронной цнфровой вычислительной машнны иараллельного действия, отличающееся тем, что, с. целью. ,ycйOj ieыия,.ыпoлjieния операции умпожения, p} jgf «j i-ieHa логическая схема для 1.-Ч.- . (. .. А.. выр,ютки управляющих импульсов при расшис1 jonKe значений пар разрядов множителя,

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для УСКОРЕННОГО УМНОЖЕНИЯ ЧИСЕЛ | 1970 |

|

SU269607A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ | 1972 |

|

SU357561A1 |

| Релейный вычислительный автомат | 1949 |

|

SU98799A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ | 1971 |

|

SU299845A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559340A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1971 |

|

SU302002A1 |

1

Г5

11

12

Iff

Авторы

Даты

1959-01-01—Публикация

1959-03-10—Подача