Изобретение относится к области вычислительной техники и может быть использовано в электронных вычислительных машинах.

Известны арифметические устройства для выполнения операции умножения, содержащие три регистра и сумматор. Результат операции формируется только после сложения всех произведений.

Цель изобретения - упрощение устройства.

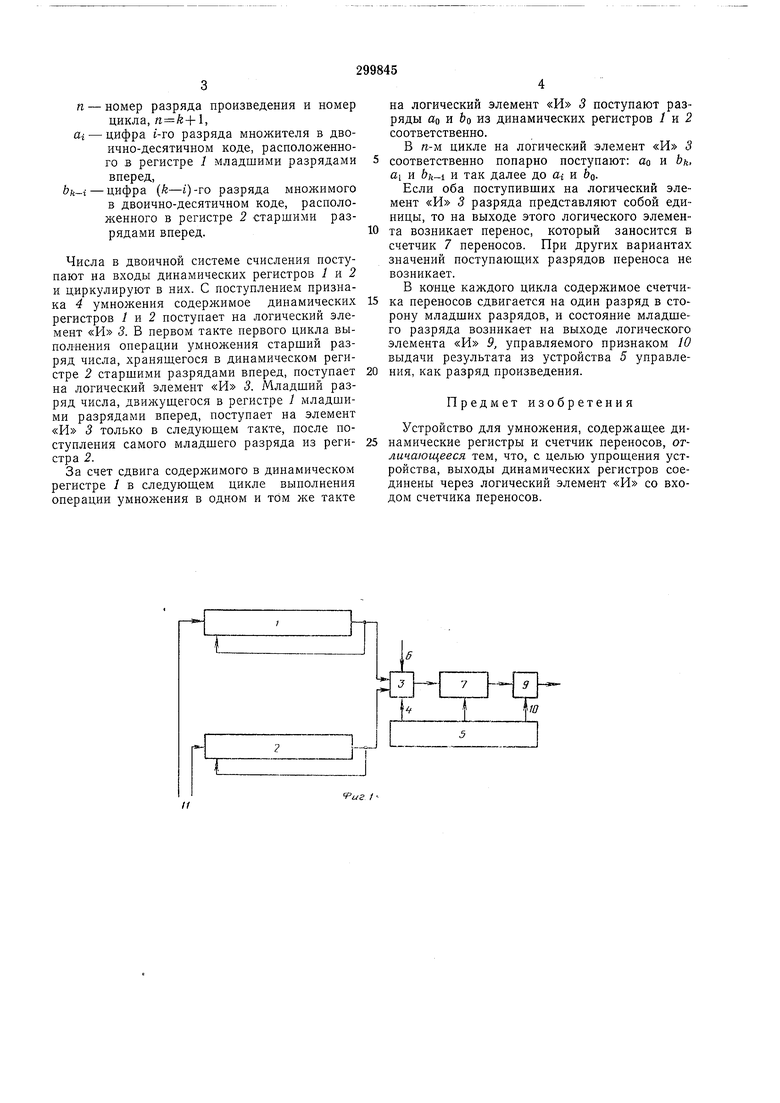

Это достигается применением двух динамических регистров, из которых один сдвиговый. Выходы регистров соединены через логический элемент «И со входом счетчика переносов.

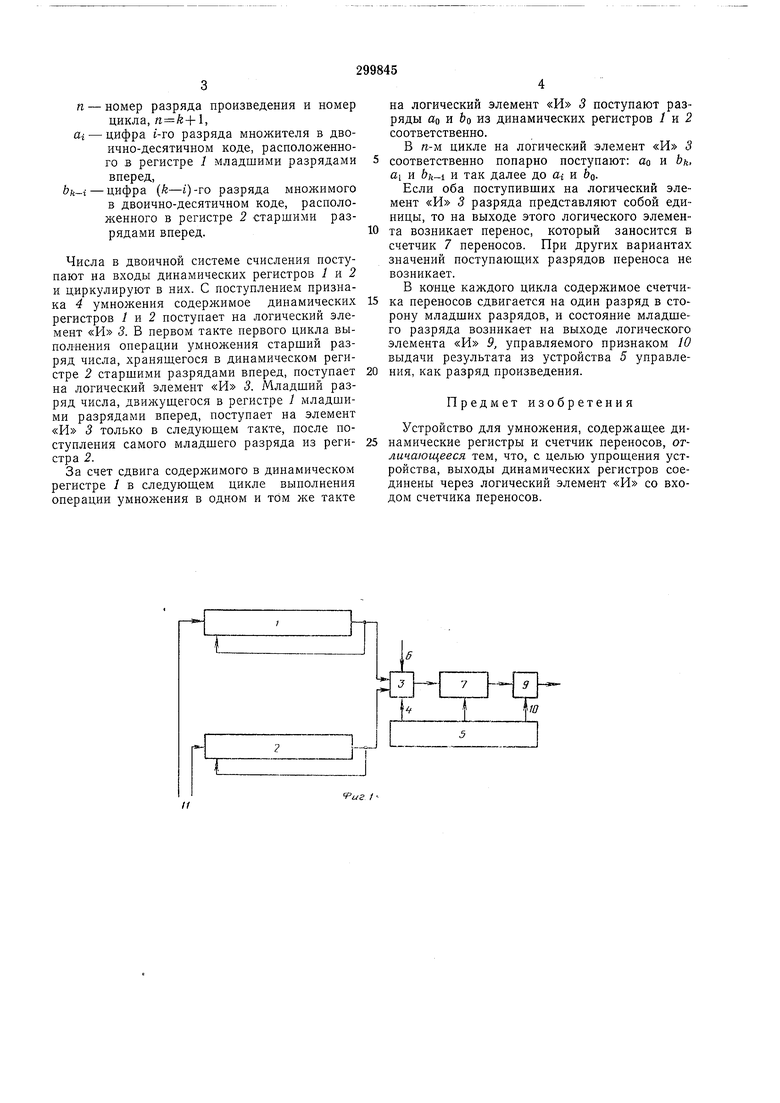

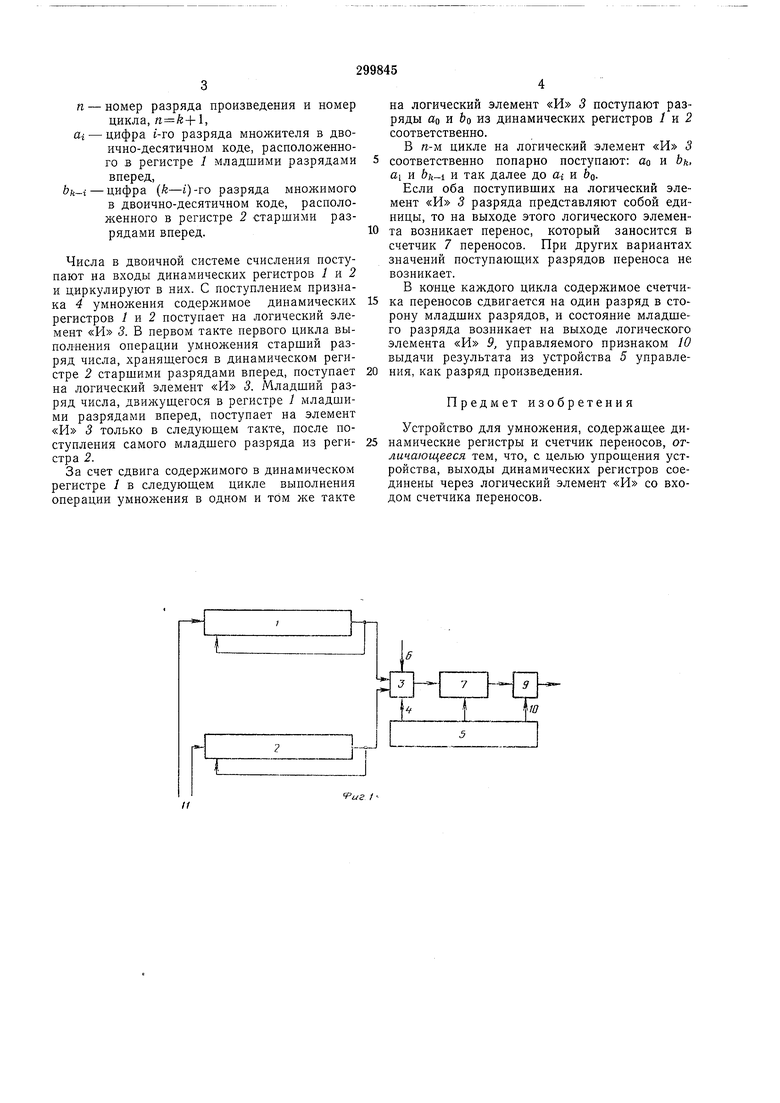

Длина динамических регистров устройства соответствует длине, необходимой для хранения удвоенного числа разрядов двоичного числа, в одном регистре множимое располагается младшими разрядами вперед, а в другом - множитель старшими разрядами вперед. Такое расположение чисел дает возможность за каждый цикл определять цифру соответствующего двоичного разряда произведения, начиная с младшего.

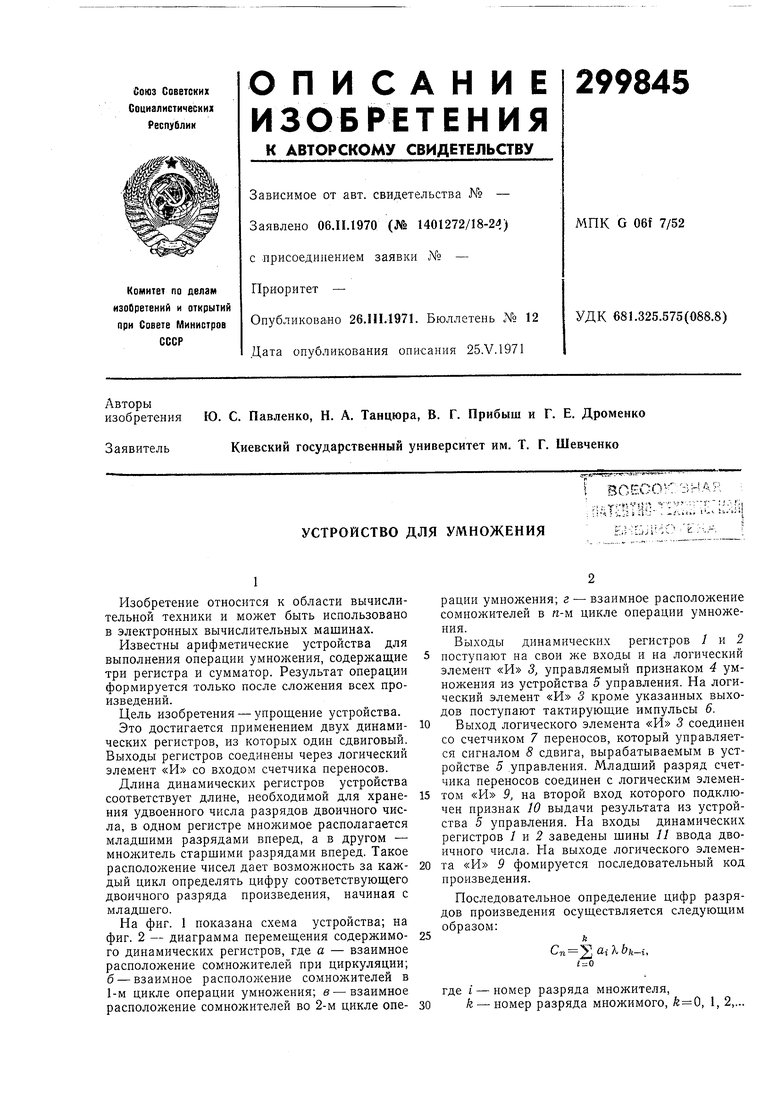

На фиг. 1 показана схема устройства; на фиг. 2 - диаграмма перемещения содержимого динамических регистров, где а - взаимное расположение сомножителей при циркуляции; б - взаимное расположение сомножителей в 1-м цикле операции умножения; в - взаимное расположение сомножителей во 2-м цикле операции умножения; г - взаимное расположение сомножителей в и-м цикле операции умножения.

Выходы динамических регистров / и 2 поступают на свои же входы и на логический элемент «И 3, управляемый признаком 4 умножения из устройства 5 управления. На логический элемент «И 3 кроме указанных выходов поступают тактирующие импульсы 6.

Выход логического элемента «И 3 соединен со счетчиком 7 переносов, который управляется сигналом 8 сдвига, вырабатываемым в устройстве 5 .управления. Младший разряд счетчика переносов соединен с логическим элементом «И 9, на второй вход которого подключен признак 10 выдачи результата из устройства 5 управления. На входы динамических регистров / и 2 заведены шины 11 ввода двоичного числа. На выходе логического элемента «И 9 фомируется последовательный код произведения.

Последовательное определение цифр разрядов произведения осуществляется следующим образом:

ft Cn aiKbh-i,

п - номер разряда произведения и номер

цикла, ,

иг - цифра t-ro разряда множителя в двоично-десятичном коде, расположенного в регистре 1 младшими разрядами вперед,

bk-i - цифра (k-i)-ro разряда множимого в двоично-десятичном коде, расположенного в регистре 2 старшими разрядами вперед.

Числа в двоичной системе счисления поступают на входы динамических регистров 1 я 2 и циркулируют в них. С поступлением признака 4 умножения содержимое динамических регистров / и 2 поступает на логический элемент «PI 3. В первом такте первого цикла выполнения операции умножения старший разряд числа, храняшегося в динамическом регистре 2 старшими разрядами вперед, поступает на логический элемент «И 3. Младший разряд числа, движущегося в регистре / младшими разрядами вперед, поступает на элемент «И 3 только в следующем такте, после поступления самого младшего разряда из регистра 2.

За счет сдвига содержимого в динамическом регистре / в следующем цикле выполнения операции умножения в одном и том же такте

на логический элемент «И 5 поступают разряды GO и bo из динамических регистров 1 и 2 соответственно.

В п-м цикле на логический элемент «И 3 соответственно попарно поступают: ао и bk, ai и bh-i и так далее до Cj и &оЕсли оба поступивших на логический элемент «И 3 разряда представляют собой единицы, то на выходе этого логического элемента возникает перенос, который заносится в счетчик 7 переносов. При других вариантах значений поступающих разрядов переноса не возникает.

В конце каждого цикла содержимое счетчика переносов сдвигается на один разряд в сторону младших разрядов, и состояние младшего разряда возникает на выходе логического элемента «И 9, управляемого признаком 10 выдачи результата из устройства 5 управления, как разряд произведения.

Предмет изобретения

Устройство для умножения, содержащее динамические регистры и счетчик переносов, отличающееся тем, что, с целью упрощения устройства, выходы динамических регистров соединены через логический элемент «И со входом счетчика переносов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Устройство для умножения | 1981 |

|

SU1032453A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

| УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249845C1 |

| Устройство для умножения десятичных чисел | 1981 |

|

SU1016780A1 |

| Устройство для умножения чисел | 1980 |

|

SU920713A1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| Устройство для умножения в избыточной системе счисления | 1983 |

|

SU1124286A1 |

1Л

ffff Of 02 ё

Авторы

Даты

1971-01-01—Публикация