Изобретение относится к области вычислительной техники и быть иснользовано в арифметических устройствах цифровых вычислительных машин.

Известно устройство умнол ения чисел в ЦВМ, основанное на запоминании цифр переноса и выполненное со сдвигом частичных воспроизведений вправо на один разряд, с анализом множителя, начиная с младших разрядов, и сохранением младшей части произведения в регистре множителя.

В известном устройстве умножение на два разряда множителя одновременно невозможно, т. е. быстродействие устройства не оптимально.

Цель изобретения - повышение быстродействия устройства.

Цель достигается за счет того, что предлагаемое устройство дополнительно содержит триггер запоминания, сумматор содержит два дополнительных младших разряда и один дополнительный старший разряд, регистр переносов содержит два дополнительных .младших разряда, выход переноса первого дополнительного младшего разряда сумматора соединен с входом младшего разряда регистра переносов, выход переноса второго дополнительного младшего разряда сумматора соединен с первым входом первого дополнительного младшего разряда сумматора, выходы сумм

дополнительных младших разрядов сумматора подключены к соответствуюш;им входам старших разрядов регистра множителя, выходы дополнительных младших разрядов регистра переносов соединены соответственно со вторыми входами дополнительных младших разрядов сумматора, третьи входы которых соединены соответственно с выходами младших разрядов регистра частичных произведений, выход

логической схемы преобразования мнол имого соединен с первым входом второго дополнительного младшего разряда сумматора и через триггер запоминания - с входами старшего и дополнительного старшего разрядов сул1матора.

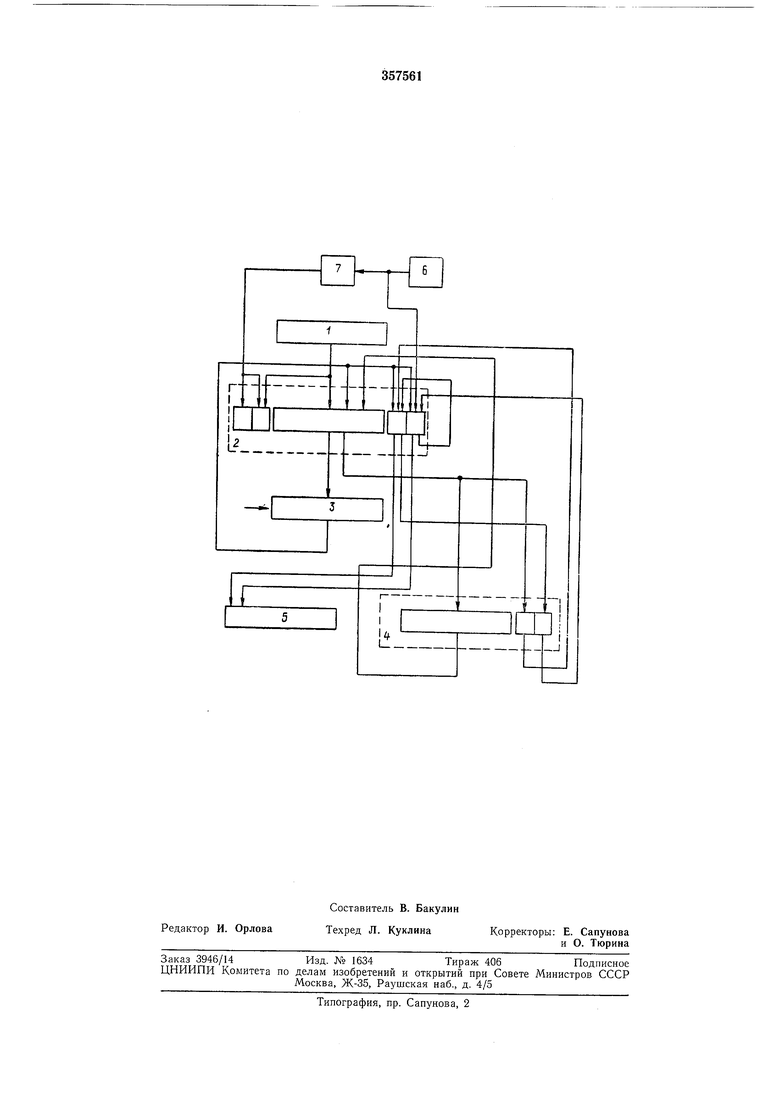

На чертел е нредставлена блок-схема предлагаемого устройства для выполнения умнолсения на два разряда множителя. Устройство содерл ит регистр / множимого,

сумматор 2, сдвигающий регистр 3 частичных произведений, регистр 4 переносов, сдвигаюший регистр 5 мнол ителя, логическую схему преобразования множимого, триггер 7 для запоминания передачи мнол ;имого в обратном

сумм по модулю 2 сумматора, за исключением двух дополиительных справа разрядов, соединен со входом регистра 3 частичных произведений, выходы двух дополнительных справа разрядов сумматора подключены к входам старших разрядов регистра 5 множителя, выход переноса сумматора соединен с регистром 4 переносов со сдвигом на один разряд вправо, выход логической схемы преобразования множимого подключен к младшему из дололнительных справа разрядов сумматора и ко входу триггера 7 запоминания обратного кода, выход которого соединен со входами двух дополнительных слева разрядов сумматора.

Устройство работает следуюш,им образом.

В исходном состоянии в регистре 1 хранится множимое, в регистре 5-множитель. В каждом такте умножения производится прямая или инверсная, либо прямая со сдвигом на один разряд влево передача множимого на один из входов сумматора, либо множимое совсем не передается. Вид передачи множимого зависит от результата анализа двух очередных младших цифр .множителя, производимого в логической схеме преобразования множителя (не показана).

На второй из входов сумматора поступает частичное .произведение с выхода регистра 3, полученное и сдвинутое на два разряда вправо в предыдушем такте умножения.

На третий вход сумматора поступают переносы из регистра 4, записанные в него непосредственно с выхода сумматора со сдвигом на один разряд вправо.

Получающаяся в каждом такте умножения сумма по модулю 2 с выхода сумматора записывается в регистр 3 частичных произведений, а поразрядные переносы с выходов переноса сумматора - в регистр 4 переносов. При этом два дополнительных справа разряда сумматора работают с последовательно включенным переносом.

Преобразование множимого при передаче его в обратном коде производится в следуюш;ем такте умнол ения. В младший из дополнительных справа разрядов сумматора из логической схемы 6 преобразования множимого записывается единица, преобразуюш,ая обратный код в дополнительный. Единицы записываются также в дополнительный слева разряд сумматора и в старший разряд основной разоядной сетки. Подача единиц в эти два разряда сумматора сохраняется во всех последующих тактах, независимо от вида передач множимого на су|Мматор. Это осуществляет триггер 7 запоминания передач множимого в обратном коде.

Получающиеся в каждом такте умножения два разряда произведения сдвигаются в два

старших разряда регистра 5 множителя. Эти разряды в предыдущем такте были освобождены при сдвиге множителя в регистре 5 ка два разряда вправо, выполняемом одновременно с суммированием множимого, частичного произведения и переносов.

Умножение на всю разрядную сетку множителя происходит за - тактов, где п - число

разрядов множителя, при этом последний такт суммирования производится со всеми сквозными переносами.

Предмет изобретения

Устройство для умножения, содержащее

сумматор, регистры множимого, множителя, переносов и частичных произведений и логическую схему преобразования множимого, причем выход регистра множимого соединен с первым входом сумматора, выход переноса

соединен с входом регистра переносов, а выход суммы - с входом регистра частичных произведений, выход которого подключен к второму входу сумматора, а выход регистра переносов - к третьему входу, отличающееся

тем, что, с целью повышения быстродействия, оно дополнительно содержит триггер запоминания, сумматор содержит два дополнительных младщих разряда и один дополнительный старший разряд, регистр переносов содержит

два дополнительных младших разряда, выход переноса первого дополнительного младшего разряда сумматора соединен с входом младшего разряда регистра переносов, выход переноса второго дополнительного младшего

разряда сумматора соединен с первым входом первого дополнительного младшего разряда сумматора, выходы сумм дополнительных младших разрядов сумматора подключены к соответствующим входам старших разрядов

регистра множителя, выходы дополнительных младших разрядов регистра переносов соединены соответственно со вторыми входами дополнительных младших разрядов сумматора, третьи входы Которых соединены соответственно с выходами младших разрядов регистра частичных произведений, выход логической схемы преобразования множимого соединен с первым входом второго дополнительного младшего разряда сумматора и через триггер

запоминания - с входами старшего и дополнительного старшего разрядов сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения двоичныхчиСЕл B дОпОлНиТЕльНыХ КОдАХ | 1979 |

|

SU813420A1 |

| ДВОИЧНОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1968 |

|

SU210491A1 |

| Устройство для умножения чисел | 1980 |

|

SU920713A1 |

| УСТРОЙСТВО для УМНОЖЕНИЯ ДВУХ я-РАЗРЯДНЫХ ЧИСЕЛ | 1968 |

|

SU222011A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| Устройство для умножения п-разрядных чисел | 1978 |

|

SU734683A1 |

| БКБЛЙОТЕК.Д | 1970 |

|

SU273520A1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

Даты

1972-01-01—Публикация