Изобретение относится к цифровой вычислительной технике и может быть использовано в устройствах, предназначенных для преобразования информации .

Целью изобретения является упрощение преобразователя и распшрение области его устойчивой работы.

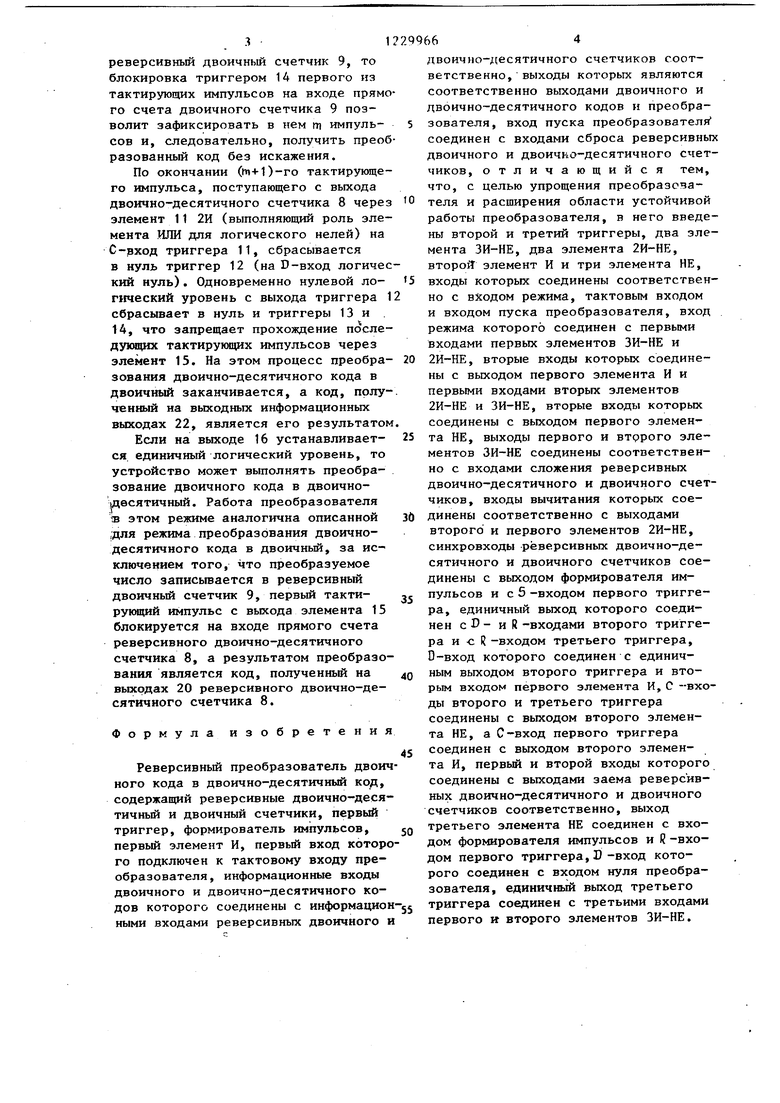

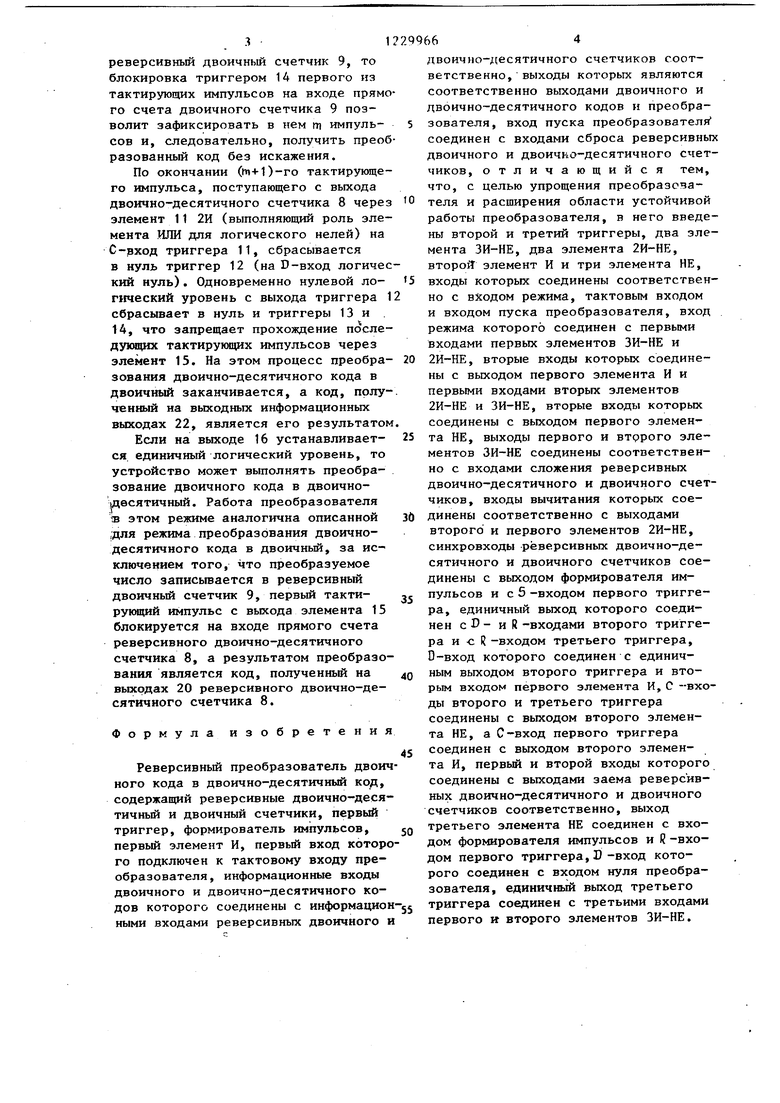

На чертеже приведена блок-схема предлагаемого преобразователя.

Преобразователь содержит элементы ЗИ-НЕ 1 и 2, элементы 2И-НЕ 3 и 4, элементы НЕ 5-7, реверсивный двоично-десятичный счетчик 8, реверсивный двоичный счетчик 9, формирователь 10 импульсов, элемент И 11, триггеры 12-14, элемент И 15, вход 16 режима работы преобразователя, вход 17 пуска преобразователя тактовый вход 18 преобразователя, входы двоично-десятичного кода 19, выходы

20двоично-десятичного кода, входы

21двоичного кода, выходы 22 двоичного кода, вход 23 логического нуля преобразователя.

Преобразователь работает следующим образом.

Если требуется выполнить преобразование двоично-десятичного кода в i двоичный, то на информационные входы двоично-десятичного счетчика 8 по входам 19 подаются тетраДы двоично- десятичного кода, а на входе 16 устанавливается нулевой логический уровень.

Процесс преобразования начинается с приходом сигнала, поступакнцего на вход 17. При этом по его фронту (переход из нулевого логического уровня в единичный) устанавливается в исходное (нулевое состояние) счетчики 8 и 9, а также триггер 12, на R-вход которого в этот момент приходит нулевой логический уровень с выхода эле10

15

20

прохождение последующих тактирующих импульсов через элемент И 15.

Таким образом, благодаря триггеру 13 начало процесса преобразования синхронизируется с моментом такти- рующих импульсов, что обеспечивает прохождение через элемент И 15 только одинаковых по длительности импульсов. Кром того, переключение триггера 13 приводит к изменению информации на D-входе триггера 14. До тех пор, пока триггер 14 находится в нулевом состоянии, прохождение тактовых импульсов через элементы ЗИ-НЕ 1 и 2 на входы прямого счета реверсивных счетчиков 8 и 9 блокируется При этом нулевой логический уровень со входа 16 запрещает поступление тактирующих импульсов через элемент 2И-НЕ 4 на вход обратного счета реверсивного двоичного счетчика 9 и дублирует запрет их прохождения через элемент ЗИ-НЕ 1 на вход прямого счета реверсивного двоично-десятичного счетчи- к-а 8.

Это приводит к тому, что первый с выхода элемента И 15 тактирующий импульс поступает через элемент 2И-НЕ 3 в реверсивный двоично-десятичный счетчик 8 и вычитает из него единицу, но двоичным счетчиком 9 не суммируется, так как блокируется его поступление через элемент 2И-НЕ 2 нулевым логическим уровнем с выхода 35 триггера 14. Кроме того, по окончании данного тактирующего импульса переключается в единичное состояние триггер 14 (на D-входе логическая единица) с выхода триггера 13, что разрещает прохождение всех последующих импульсов с выхода элемента 15 через элемент ЗИ-НЕ 2 на суммирование в реверсивный двоичный счетчик 9.

25

30

40

1

Таким образом, благодаря триггемента НЕ 6. По спаду сигнала, пришед- ру 14, в двоичный счетчик 9 поступашего на вход 17 (переход из единичного логического уровня в нулевой), запускается формирователь 10 импульсов, сигнал с выхода которого записывает значения тетрад в реверсивный двоично-десятичный счетчик 8 и устанавливает в единичное состояние триггер 12. Это приводит к тому, что по окончании ближайшего тактирующего импульса, поступившего через элемент НЕ 7 на С-входы триггеров 13 и 14, устанавливается в единичное состояние триггер 13, который разрешает

ет на один импульс меньше, чем в двоично-десятичный счетчик 8. Данную операцию необходимо произвести, так как в качестве сигналов окончания

50 преобразования используются импульсы обратного переноса, которые вырабатываются в счетчиках 8 и 9 при поступлении (т+1) -го тактирующего импульса, где Гч - количество тактирующих им-

55 пульсов, необходимое для считывания преобразуемого кода из счетчиков 8 или 9. Поскольку (т+1)-й импульс будет поступать для суммирования в

5

0

прохождение последующих тактирующих импульсов через элемент И 15.

Таким образом, благодаря триггеру 13 начало процесса преобразования синхронизируется с моментом такти- рующих импульсов, что обеспечивает прохождение через элемент И 15 только одинаковых по длительности импульсов. Кром того, переключение триггера 13 приводит к изменению информации на D-входе триггера 14. До тех пор, пока триггер 14 находится в нулевом состоянии, прохождение тактовых импульсов через элементы ЗИ-НЕ 1 и 2 на входы прямого счета реверсивных счетчиков 8 и 9 блокируется При этом нулевой логический уровень со входа 16 запрещает поступление тактирующих импульсов через элемент 2И-НЕ 4 на вход обратного счета реверсивного двоичного счетчика 9 и дублирует запрет их прохождения через элемент ЗИ-НЕ 1 на вход прямого счета реверсивного двоично-десятичного счетчи- к-а 8.

Это приводит к тому, что первый с выхода элемента И 15 тактирующий импульс поступает через элемент 2И-НЕ 3 в реверсивный двоично-десятичный счетчик 8 и вычитает из него единицу, но двоичным счетчиком 9 не суммируется, так как блокируется его поступление через элемент 2И-НЕ 2 нулевым логическим уровнем с выхода 5 триггера 14. Кроме того, по окончании данного тактирующего импульса переключается в единичное состояние триггер 14 (на D-входе логическая единица) с выхода триггера 13, что разрещает прохождение всех последующих импульсов с выхода элемента 15 через элемент ЗИ-НЕ 2 на суммирование в реверсивный двоичный счетчик 9.

5

0

0

1

Таким образом, благодаря тригге ру 14, в двоичный счетчик 9 поступает на один импульс меньше, чем в двоично-десятичный счетчик 8. Данную операцию необходимо произвести, так как в качестве сигналов окончания

преобразования используются импульсы обратного переноса, которые вырабатываются в счетчиках 8 и 9 при поступлении (т+1) -го тактирующего импульса, где Гч - количество тактирующих им-

пульсов, необходимое для считывания преобразуемого кода из счетчиков 8 или 9. Поскольку (т+1)-й импульс будет поступать для суммирования в

реверсивный двоичный счетчик 9, то блокировка триггером 14 первого из тактирующих импульсов на входе прямого счета двоичного счетчика 9 позволит зафиксировать в нем п импульсов и, следовательно, получить преобразованный код без искажения.

По окончании (tn+1)-ro тактирующего импульса, поступающего с выхода двоично-десятичного счетчика 8 через элемент 11 2И (выполняющий роль элемента ИЛИ для логического нелей) на С-вход триггера 11, сбрасывается в нуль триггер 12 (на D-вход логический нуль). Одновременно нулевой ло- гкческий уровень с выхода триггера сбрасывает в нуль и триггеры 13 и 14, что запрещает прохождение после- дукщих тактирующих импульсов через элемент 15. На этом процесс преобра- зования двоично-десятичного кода в двоичный заканчивается, а код, полученный на выходных информационных выходах 22, является его результатом

Если на выходе 16 устанавливает- ся единичный логический уровень, то устройство может выполнять преобра- зование двоичного кода в двоично- десятичный. Работа преобразователя я этом режиме аналогична описанной для режима преобразования двоично- десятичного кода в двоичный, за исключением того, что преобразуемое число записьгеается в реверсивный двоичный счетчик 9, первый тактирующий импульс с выхода элемента 15 блокируется на входе прямого счета реверсивного двоично-десятичного счетчика 8, а результатом преобразования является код, полученный на выходах 20 реверсивного двоично-десятичного счетчика 8.

Формула изобретения

4S

Реверсивный преобразователь двоичного кода в двоично-десятичный кор, содержащий реверсивные двоично-десятичный и двоичный счетчики, первый триггер, формирователь импульсов, 50 первый элемент И, первый вход которого подключен к тактовому входу преобразователя, информационные входы двоичного и двоично-десятичного кодов которого соединены с информацион-55 триггера соединен с третьими входами ными входами реверсивных двоичного и первого и второго элементов ЗИ-НЕ.

О 5 20

25 3U о

5

S

0

двоичио-десятичного счетчиков соответственно, выходы которых являются соответственно выходами двоичного и двоично-десятичного кодов и преобра- 5 зователя, вход пуска преобразователя соединен с входами сброса реверсивных двоичного и двоично-десятичного счетчиков, отличающийся тем, что, с целью упрощения преобразователя и расширения области устойчивой работы преобразователя, в него введены второй и третий триггеры, два элемента ЗИ-НЕ, два элемента 2И-НЕ, BTopoiT элемент И и три элемента НЕ, входы которых соединены соответственно с входом режима, тактовым входом и входом пуска преобразователя, вход режима которого соединен с первыми входами первых элементов ЗИ-НЕ и 2И-НЕ, вторые входы которых соединены с выходом первого элемента И и первыми входами вторых элементов 2И-НЕ и ЗИ-НЕ, вторые входы которых соединены с выходом первого элемента НЕ, выходы первого и втррого элементов ЗИ-НЕ соединены соответственно с входами сложения реверсивных двоично-десятичного и двоичного счетчиков, входы вычитания которых соединены соответственно с выходами второго и первого элементов 2И-НЕ, синхровходы -реверсивных двоично-десятичного и двоичного счетчиков соединены с выходом формирователя импульсов и с 5-входом первого триггера, единичный выход которого соединен с D- и R-входами второго триггера и с R -входом третьего триггера, D-вход которого соединен с единичным выходом второго триггера и вторым входом первого элемента И, С --входы второго и третьего триггера соединены с выходом второго элемента НЕ, а С-вход первого триггера соединен с выходом второго элемента И, первый и второй входы которого соединены с выходами заема реверсивных двоично-десятичного и двоичного счетчиков соответственно, выход третьего элемента НЕ соединен с входом формирователя импульсов и R-входом первого триггера,D -вход которого соединен с входом нуля преобразователя, единичный выход третьего

Редактор Н. Егорова

Составитель М. Аршавский Техред Л.Олейник

Заказ 2460/59 Тираж 816 - Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственнг-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор А. Ференц

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1985 |

|

SU1305869A1 |

| Преобразователь двоичного кода | 1984 |

|

SU1208607A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1986 |

|

SU1349008A2 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1984 |

|

SU1266008A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU941991A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1501276A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1983 |

|

SU1124282A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1989 |

|

SU1667259A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в устройствах преобразования информации. Целью изобретения является упрощение и расширение области устойчивой работы преобразователя. Поставленная цель достигается тем, что в преобразователе, поЬтроенном на реверсивных счетчиках, индикатором окончания преобразования являются сигналы заема и тем, что в него введены входной коммутатор для переключения тактовых сигналов, блок; привязки управляющих сигналов к тактовой частоте и триггер коррекции ошибки. 1 ил.

| Приборы и техника эксперимента, № 2, 1982, с | |||

| Аппарат, предназначенный для летания | 0 |

|

SU76A1 |

| I Авторское свидетельство СССР № 756401, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-07—Публикация

1982-09-03—Подача