содержащий задающий генератор I импульсов, счетчик 2 импульсов, триггер 6, инвертор 7, регистр 5, введены блок 3 элементов И-ИЛИ, оперативный накопитель микропрограмм А, элемент И-НЕ 14, адресный шифратор 9, элемент задержки 8, что позволило путем обеспечения одновременного формирования нескольких последоваИзобретение относится к импульсной технике и может быть использовано в частотно-измерительной и преобразующей аппаратуре.

Целью изобретения является расширение функциональных возможностей путем обеспечения одновременного фомирования нескольких последовательностей и шyльcoв, изменяемых по нескольким параметрам (скважности, частоте, фазе), обеспечение оперативной перестройки микропрограмм.

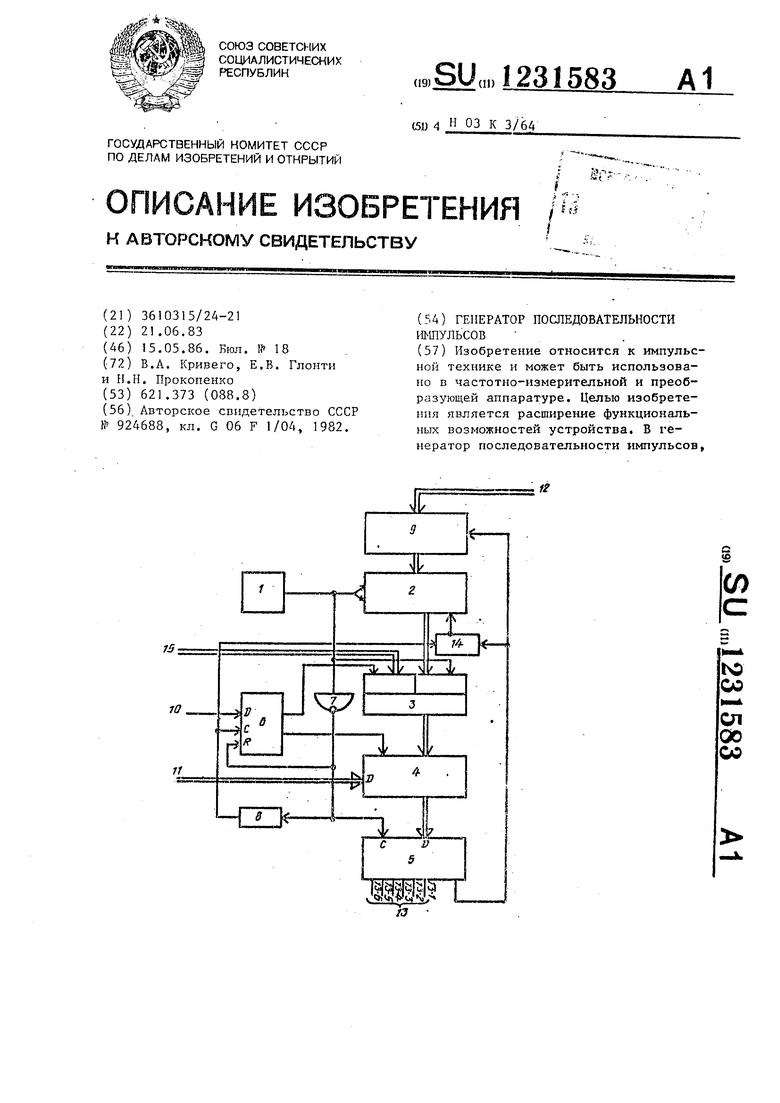

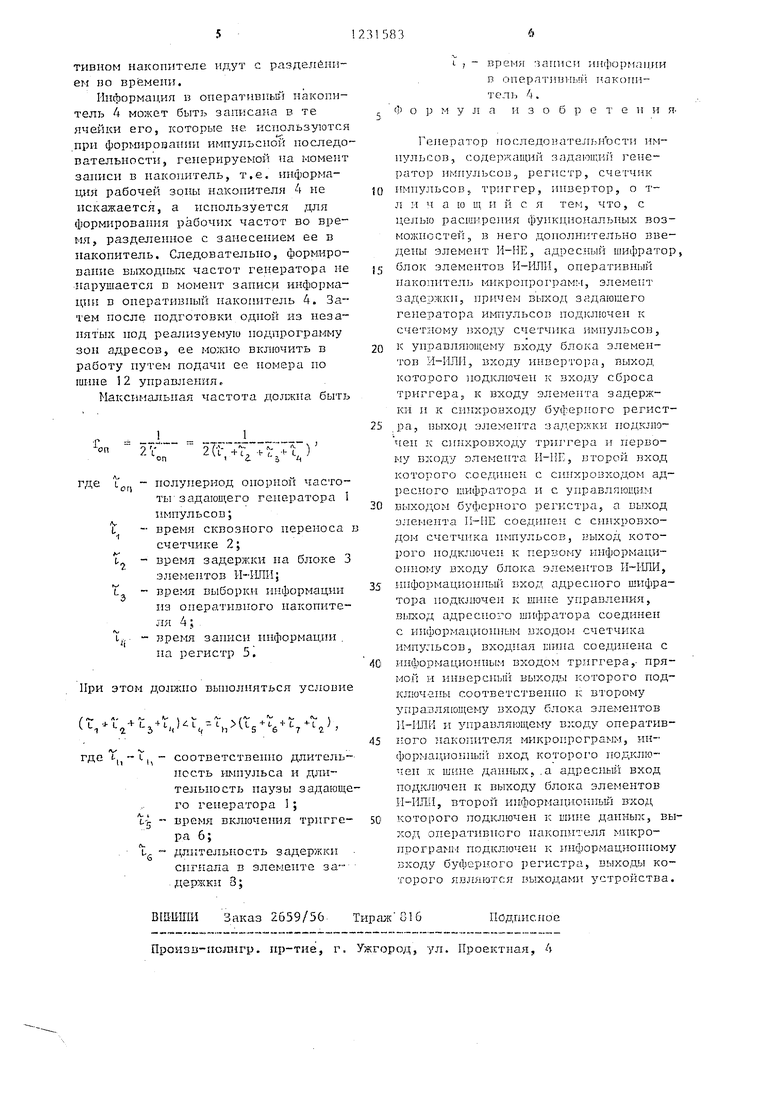

На чертеже представлена функциональная схема генератора последовательности импульсов.

Генератор последовательности импульсов содержит задающий генератор 1 импульсов, счетчик 2 импульсов, блок 3 элементов И-ШБ-, оператив- Hbtti накопитель шкpoпpoгpaмll А, регистр 5, триггер 6, инвертор 7, элемент Задержки 8, адресный шифратор 9, шину 10 Пуск, шину П.данных, шипу 12 управления, выходные шины 13, элемент И-НЕ 14, шину 15 адреса

Выход задающего генератора 1 импульсов подключен к счетному входу счетчика 2, к управляющему входу блока 3 элементов И-ИЛИ, а через инвертор 7 - к входу сброса триггера 6 и к входу элемента задержки 8, выход которого подключен к синхро- входу триггера 6 и первому входу элемента И-НЕ 14, второй вход элемента И-НЕ 14 подключен к одному из выходов регистра 5 и к управляющему входу адресного шифратора 9, информационный вход которого подключен к шине 12 управления, выход адресного шифратора 9 подключен к информационному входу счетчика 2, вытельностей импульсов, изменяем1з1Х по нескольким параметрам (скважности, частоте., Лазе), и обеспечения оперативной перестройки микропрограмм достигнуть поставленной цели. Генератор последовательности импульсов также содержит ши1-Ш1 10 Пуск, 1 данных, 12 управления, выходную 13, 15 адреса. 1 ил.

ход которого подключен к первому информационному входу блока 3 элементов И-11ПИ, второй информационньш вход блока элементов И-ИЛИ подключен к шине 15 адреса, информационный вход триггера 6 подключен к шине 10 Пуск, а прямой и инверсный выходы триггера 6 подключены соответственно к второму управляющему входу блока 3 элементов И-ИЛИ и управляющему входу оперативного накопителя микропрограмм 4, информационный вход которого подключен к шине 11 данных, выход оперативного накопителя мнкропрограмм 4 подключен к информационному входу регистра 5.

Генератор последовательности импульсов работает следуюшд м образом. Задающий генератор 1 импульсов

формирует меапдровую (прямоугольную со скважностью два) импульсную последовательность (fon ) которая поступает на счетньш вход счетчика 2. Счетчик 2, предварительно (перед

работы) сброшенньш в нуль, фор)О1рует последовательность параллельных адресных кодов от нулевого до заданного значения. Последующие, начальное и конечное, значения адресных кодов, формируемых счетчиком 2, определяются состоянием шины 12 управления и микропрограммой, занесенной в оперативный накопитель микропрограмм 4.

Параллельньй код с разрядностью, равной АхБ, поступает через блок 3 элементов И-ИЛИ на адресньш вход оперативного накопителя микропрог- paMivi 4.

Момент прохождения группы БхА разрядов через блок 3 элементов

Ш1И стробируется положительным по- лупернодом импульсов задающего гене ратора 1.

Триггер 6, пз условия начальной установки, сбрасываемой на О отри- цательным полупериодом частоты зада 1ощего генератора 1 , имеет на выходе Q высокий потенциал, определяющий режим чтения информации из ячейки оперативного накопителя 4 по задан- ному адресу.

Накопитель микропрограмм 4 представляет собой оперативную или полу оператнвную запоминающую матрицу, . информация в которой разделяется по адресам, составляя информационное, слово, жестко связанное со своим адресом в котором оно зафиксировано.

При подаче кода адреса на адрес- вый вход накопителя микропрограьш А в режиме чтения информационное слово, соответствующее этому адресу поразрядно формируется на информаЦИО11НОМ выходе накопителя микропрог- рамм 4 и подается на вход регистра 5.

По заднему фронту импульсов задающего генератора 1, воздействующего на синхровходы регистра 5, информация с оперативного накопителя 4 поразрядно фиксируется на регистре 5, где удерживается до прихода следующего заднего фронта положительного импульса задающего гене- ратора 1, т.е. в течении всего периода опорной частоты f .

Обязательным условием уверенной записи информации с оперативного накопителя микропрограмм 4 в регистр 5 по адресу, формируемому на счетчике 2, является соотношение

.San.,

где время переноса в счетчике ij- время задержки на блоке 3

элементов И-ИЛИ; ij - время выборки информации и оперативного накопителя микропрограмм 4; f - время задержки на инверто-

имб

ре 7; ijnn - время записи информации в

регистр 5.

Информация, снимаемая (считываемая) с регистра 5 должна рассматриваться поразрядно, т.е. каждьй раз

$

5

20

30 5

0

5

0

5

583

ряд регистра 5 представляет собой выход канала, генерирующего соотпет- ствующую частоту 1гмпульсоп. Эти частоты могут быть связаны по фазе или по другим Бзаимоопределяюп1Им параметр ам.

Один из разрядов регистра 5 отведен для управления цикличностью работы генератора, в этом разряде формируется микрокоманда, управляющая работой адресного шифратора 9 и записью начального кода А в счетчик 2.

Оперативное занесение микропрограмм в оперативньй накопитель 4 может производиться без нарушения ге- ;нерируемьгх последовательностей.

Запись информации в оперативный накопитель 4 производится пословно по адресу, задаваемому по шине 15 адреса, по которой подается код адреса, а по шине 11 данных. - значение (код) заносимого информационного слова, затем по шине 10 Пуск наступает со сдвигом относительно передних фронтов адресных сигналов и сигналов данных синхронизирующий сигнал, который разрешает по D-входу работу триггера 6. По переднему фронту паузы f, (инверсного значения сигнала от задающего генератора импульсов I , заде ржанного п элементе задержки 8) триггер б устанавливается в единичное состояние и сигналом со своего единичного выхода открывает блок 3 элементов И-ИПП, пропуская на адресньи вход оперативного накопителя микропрограмм 4 код адреса, подаваем.,п 1 по шине 15 адреса. При этом нулевое плечо триггера 6 обеспечипает подачу режима Запись на оперативньй накопитель микропрограмм 4, и информация с шины 11 дан- iffitx в этом режиме заносится в соответствующую ячейку оперативного накопителя 4, После окончатся паузы триггер 6 устанавливается в исходное состояние, а .сигнал Пуск с шнны 10 Пуск должен быть снят.

Таким образом, запись информации в оператнвньй накопитель 4 производится в момент де1 1ствпя паузы в периоде частоты f (поступающей от задающего генератора импульсов J), а запись в регистр 5 из оперативного накопителя 4 производится за время действия импульса в периоде частоты f , т.е. эти два процесса в оперативном накопителе идут с разделением во времени.

Информация в оператнБИьй накопитель А может быть записар.а в те ячейки его, которые не используются при формировании импульсной носледо вательпости, генерируемой на момент записи в накопитель, т.е. информация рабочей зоны накопителя не искажается, а используется для формпроваппя рабочих частот во время, разделенное с занесением ее в накопитель. Следовательно, формирование выходных частот генератора не нарушается в момент записи информа ции в оперативный накопитель 4. Затем после подготовки одной из неза- нятьпс нод peajnisyeMyio подпрограмму зон адресов, ее можно включить в работу путем подачи ее номера п:о шине 12 управления

Максниальпая частота должпа быть

2 V

г7 /, IV. л., л.

2(1 +(. -ь ,:, с )

1C. Ъ

риод онорпой час ты задающего генератора 1

- полунериод онорпои частоимпульсов;- время сквозного переноса в

счетчике 2; время задерз элементов И-1ШИ;

- время задерлски на блоке 3

30

время выборки 1П1формащш 35 из оперативного накопителя 4;

L;, - время записи 1И1формации па регистр 5.

При этом должно вынолняться условие

S 4 -3 S 4 -S.

i t Г

г г

V %

де i-, ц соответственно длительность импульса и длительность паузы задающего генератора 1; t , - время включетшя тригге- 50

ра 6;

, tg длительность задержки сигнала в элементе за- ,держки 3;

ВШ-МШ Заказ 2659/56. Тирсик 81б Подписное Произ1 - 1о;шгр. пр-тие, г. Ужгород, ул. Проектная, 4

jo д 20

2S

30

35

Ю

5

50

I- 7 - время записи инфор.мации в оператив1-1ый пакотш- тель i. о з м у J а и 3 о б р е т е н и яГенератор последонателг-н ости импульсов, зада1оа;ий генератор импульсов, регистр, счетчик импульсов, триггер, инвертор, о т- л и ч а ю ш и и с я тем, что, с целью расшире п-1я функциональпых возможностей, в него дополнительно вве- д,ены элемент И-НЕ, адресный шифратор, блок элементов И-ИЛИ, оперативный накопитель микропрограмм, элемент задержки, причем выход задающего геператора импульсов .пючен к счетному входу счетчика импульсов, к управляющему входу блока элементов И-ГШИ, входу инвертора, выход которого подключен к входу сброса триггера, к входу элемеггга задержки и к синхровходу буф-ерпого регистра, выход элемента задержки подключен к синхровходу триггера и первому входу элемента Н-НЕ, второй вход которого соединен с синхровходом адресного шифратора и с управляющим выходном буферного регистра, а выход элемггпта И-11Е соединен с синхровхо- Д01-1 счетчика импульсов, выход которого иодключен к nep-jOMy информационному входу блока элементов И-ИЛИ, ииформац1юпньш вход адресного шифратора иодключеп к шине управления, выход адресного шифратора соединен с ин(Ьормационным входом счетчика импульсов, входная lanna соед.инена с ипформацио1И1ым входом триггера,- прямой и инверсны выходы к.оторого подключены соответственно к второму управляющему входу блока элементов И-ГШИ и управляющему в:соду оперативного накопителя микропрограмм, информационный вход которого подклю- чеп к шнне данных,.а адресный вход подключен к выходу блока элементов И-ИЛ Л, второй ицформап,ио1и1ый вход которого подключен к шине дапных, выход операти.впого па сопителя микропрограмм подключен к информационному входу буферного регистра, выходы которого являются вы.ходами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор функциональных зависимостей | 1983 |

|

SU1130853A1 |

| Многоканальный преобразователь код-частота | 1985 |

|

SU1267621A1 |

| Устройство для контроля трассировки и воспроизведения информации о прокладке кабельной трассы | 1984 |

|

SU1238106A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| МОДУЛЬ СИСТЕМЫ МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2152071C1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Устройство для контроля неисправностей | 1991 |

|

SU1798787A1 |

Изобретение относится к импульсной технике и может быть использовано в частотно-измерительной и преобразующей аппаратуре. Целью изобретения является расширение функциональных возможностей устройства. В генератор последовательности импульсов, ьо со ел 00 со

| Устройство для формирования регулируемой временной последовательности импульсов | 1980 |

|

SU924688A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-15—Публикация

1983-06-21—Подача