11

Изобретение относится к цифровой вычислительной технике, конкретнее к устройствам для обработки цифровых данных, и может быть использовано дл решения дифференциальных уравнений в частных производных.

Цель изобретения - повышение производительности устройства.

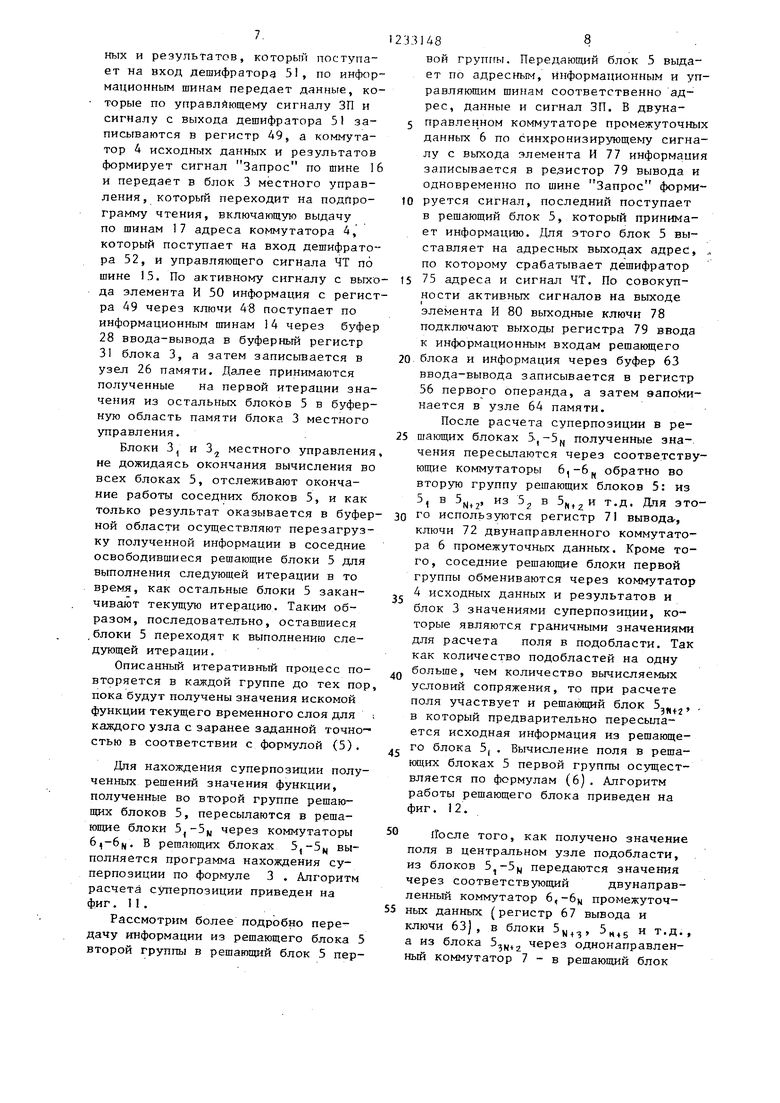

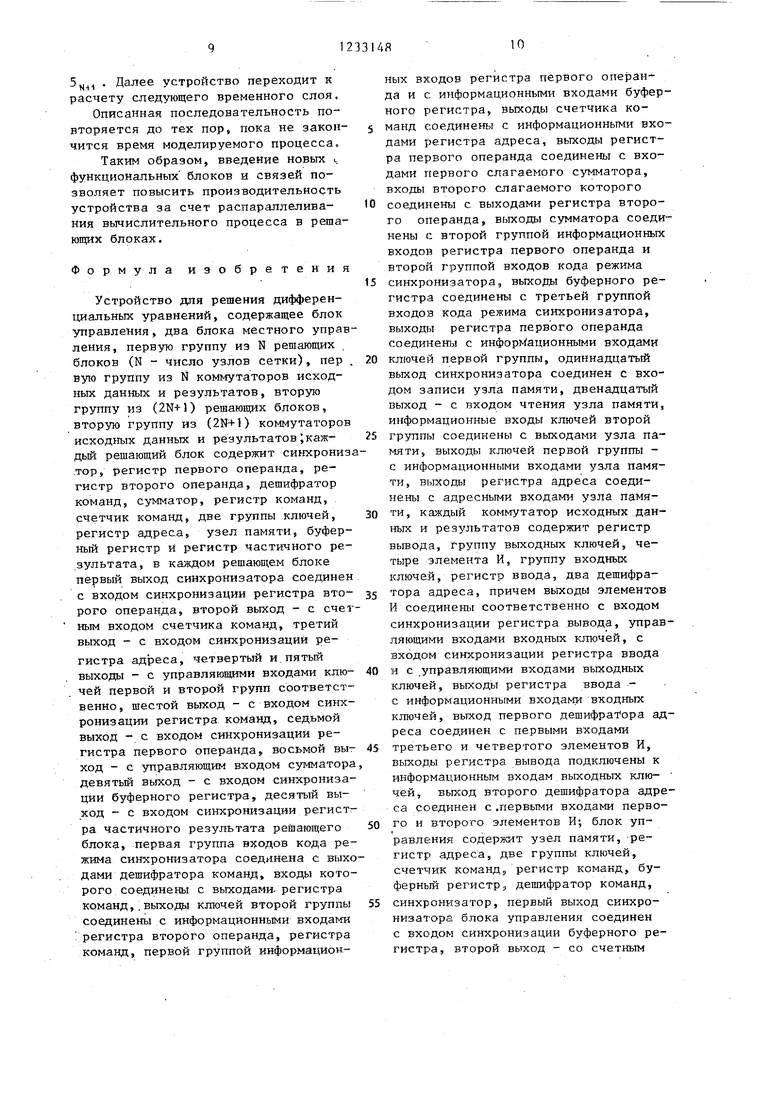

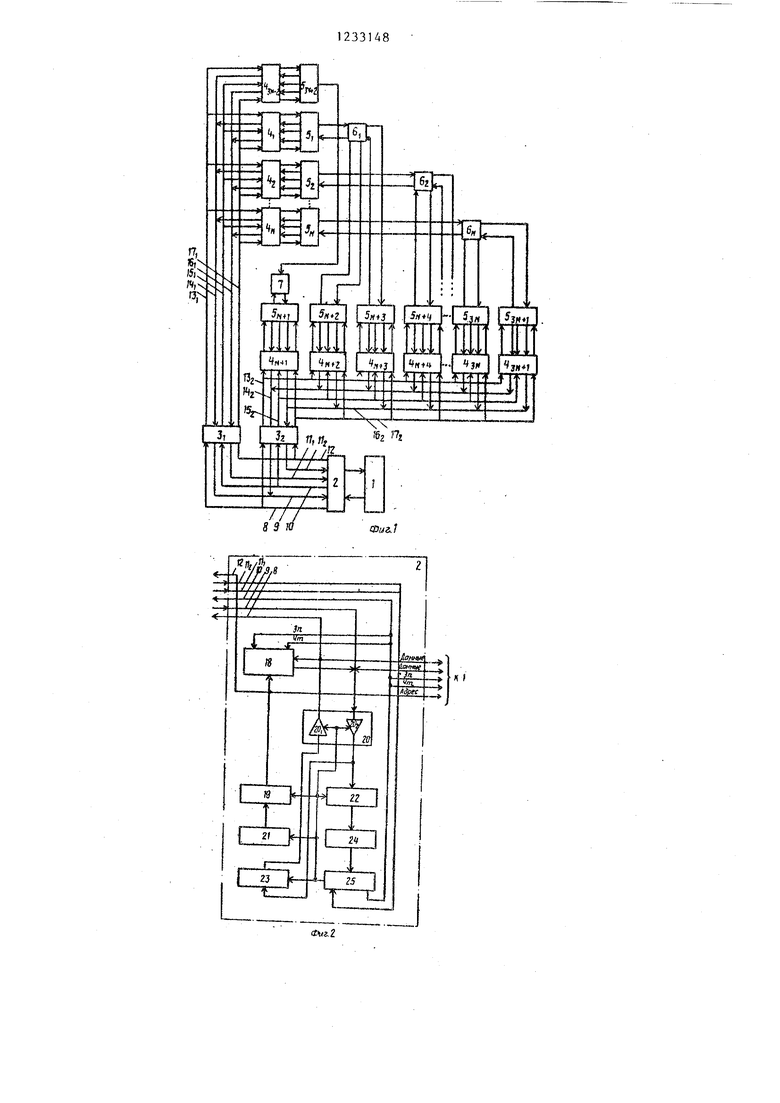

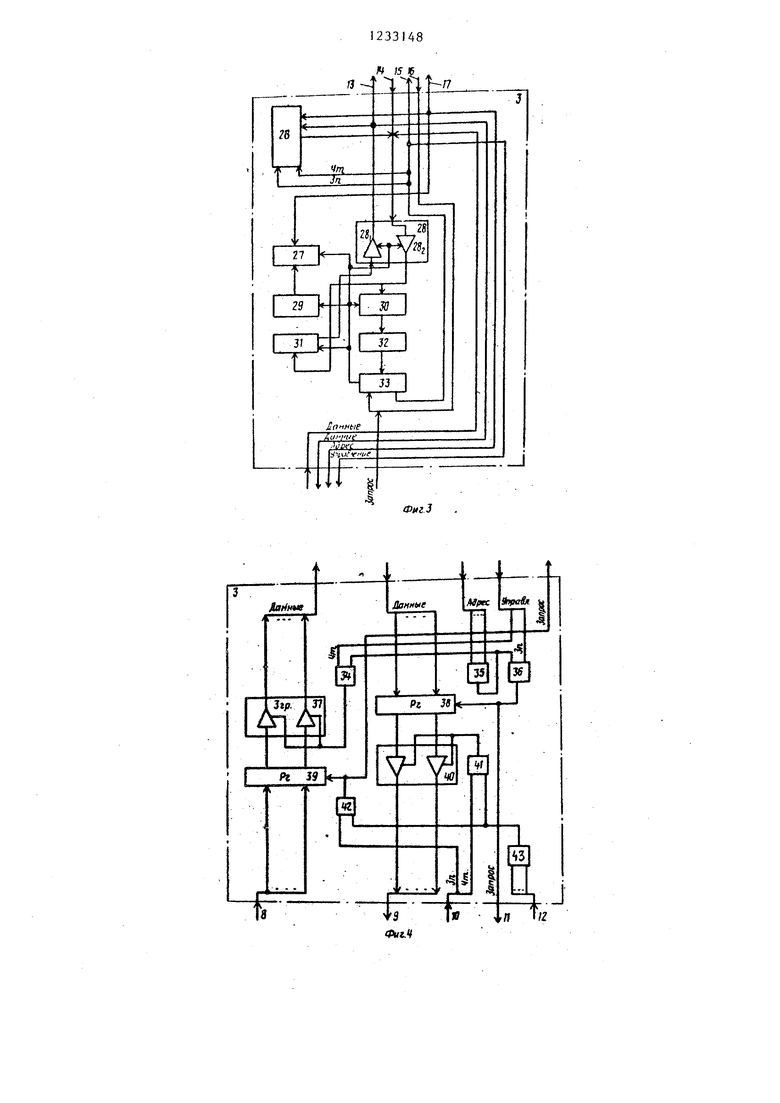

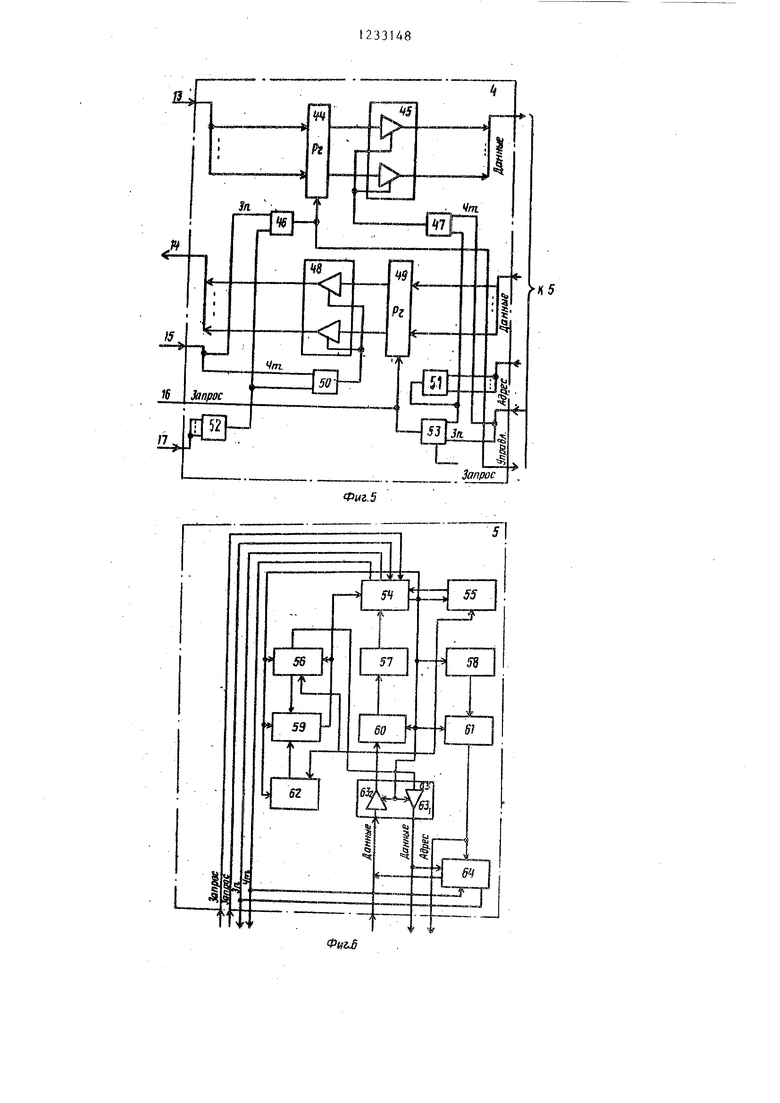

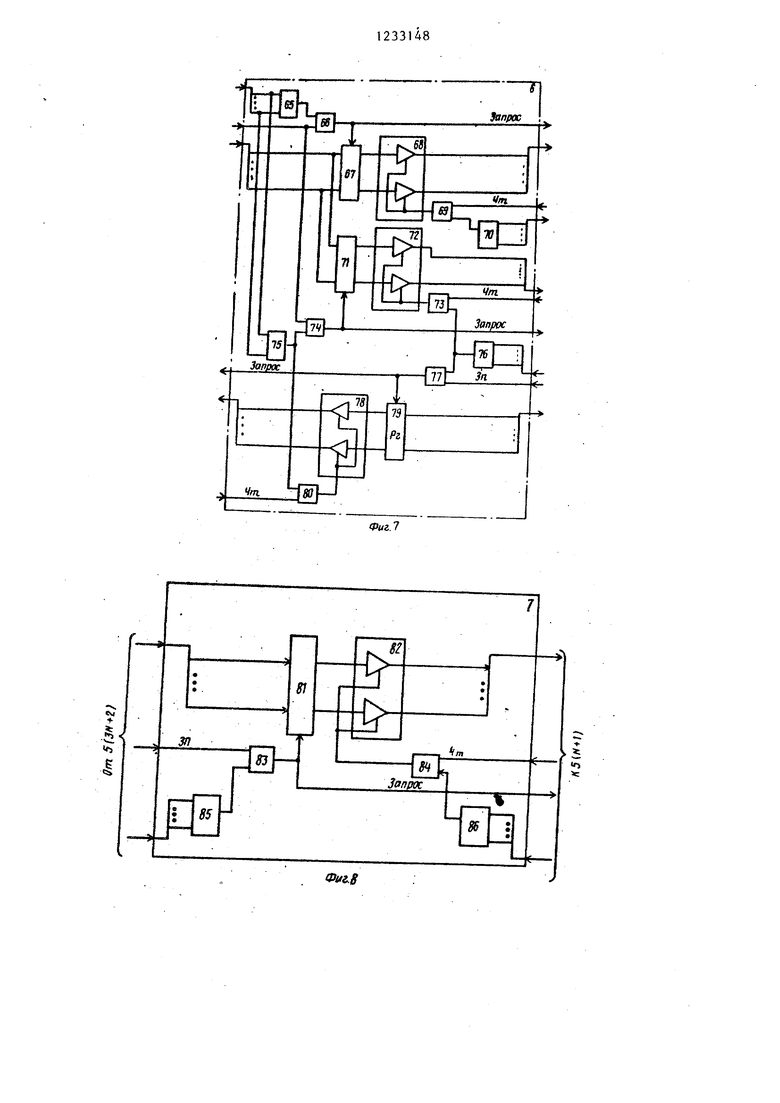

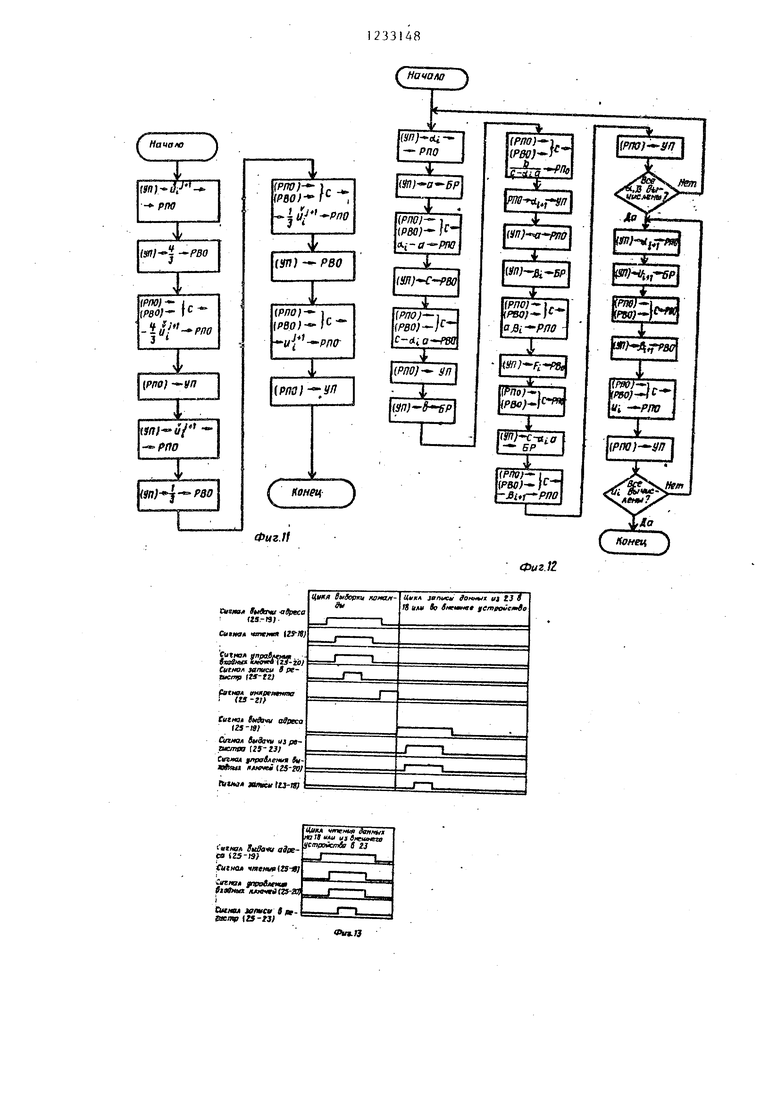

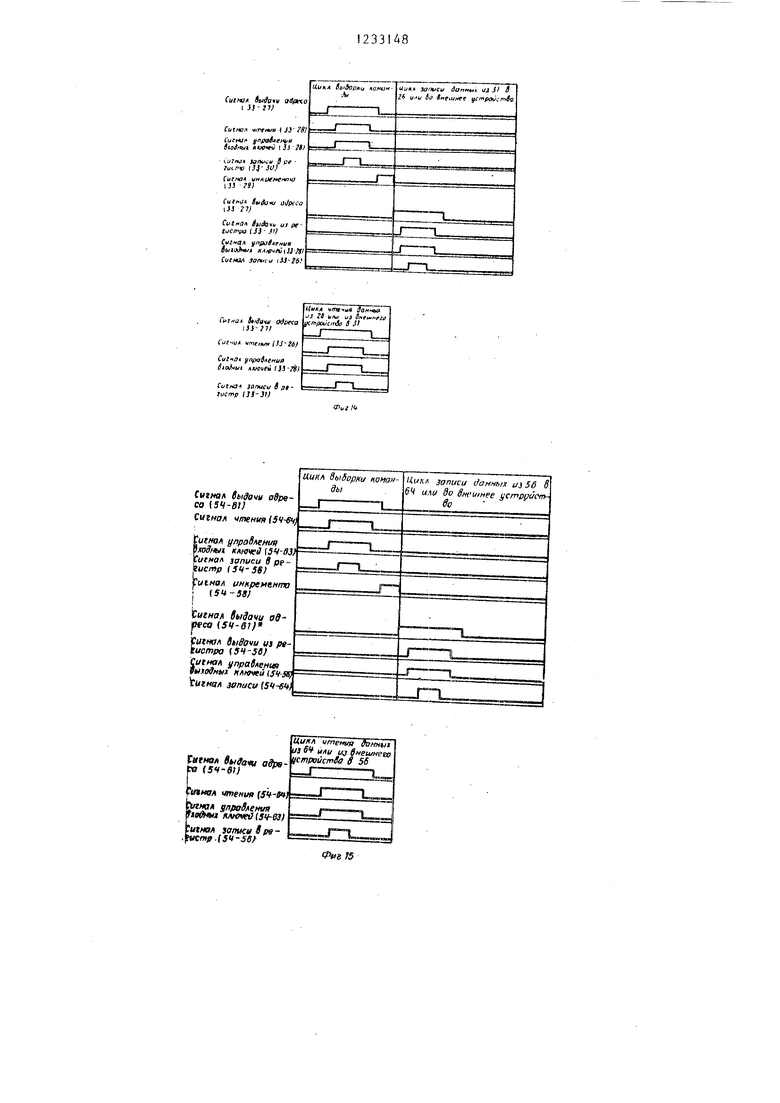

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - структурная схема блока управления, на фиг. 3 и 4 - структурная схема блока местного управления; на фиг.5- структурная схема KONmyTaTopa исход- ньпс данных и результатов; на фиг.6- структурная схема решающего блока-, на фиг. 7 - конкретная реализация, двунаправленного коммутатора промежуточных данных; на фиг. 8 - структурная схема однонаправленного коммутатора промежуточных данных на .фиг. 9 - временная диаграмма работы устройства; на фиг. 10 - алгоритм работы решающего блока для-метода простой итерации; на фиг. 11 - алгоритм расчета суперпозиции в решающем блоке, на фиг. 12 - алгоритм работы решающего блока для метода прогонки, на фиг. 13-15 - временные диаграммы синхронизаторов (в скобках указаны номера узлов блоков 2, 3 и 5 соответственно, между которыми передаются синхронизирующие сигналы), на фиг. 16 - алгоритм работы блока управления; на фиг. 17 и 18 - алгоритм работы блоков местного управления. (Условные обозначения для фиг. 9: РБ - решающи1{ блок 5; БМУ - блок 3 местного управления i БУ - блок 2 управления, для фиг. 10-12: УП - узел 64 памяти РПО - регистр 56 первого операнда, ;РВО - регистр второго операнда,- БР - .буферный регистр 55; С - сумматор 59, для фиг, 6: УП - узел 8 памяти, РК - регистр 22 кома}1д; СХ - син ронизатор 25 импульсов; РА - рег истр 19 адреса; СК - счетчик 21 командi .Б - буферный регистр Р5 j КО - код операции КЛ - ключи 20, для фиг.7: УП - узел 26 памяти, РК - регистр 30 команд; ДК - дешифратор 32 команд СХ - синхронизатор 33; РА - регистр 27 адреса, СК - счетчик 29 командj БР - буферш.гй регистр 31; КО - код операции КЛ - ключи; Р - регистр; И - элемент И; ДА - дешифратор адрес БУ - блок 2 управления, для фиг. 18:

31482

УП - узел 26 памяти5 РК - регистр 30 команд, ДК -- дешифратор 32 команд; СХ - си}1хронизатор 33, РА - регистр 27 адреса; ОК - счетчик 29 командi 5 БР - буферный регистр 31; КО - код операции-, КЛ - ключи 20) .

.Устройство для решения дифференциальных уравнений (фиг. 1) содержит блок 1 ввода-выврда, блок 2 управле- 0 ния 5 блоки 3, 3j местного управления, первую-группу коммутаторов 4jj исходных данных и результатов,

вторую группу коммутаторов и,,щ

исходга,1х данных и результатов, до полнительный комьгутатор ,исхоц.т:Гх данных и результатов, группу решаводшс блоков 5,-5, вторую группу решающюс блоков 5jj,,, дополнительный решающий блок 5, , группу двуна20 правленных KONft-iyTaTopoB 6, -6 проме- жуточных. данных, однонаправленный коммутатор 7 промежуточных данных, системные выходные информационные шины 8, системные входные информационные

25 шины 9, системные выходные управляю- пще шины 10, системнь е входные управляющие шины И, и I1, системные адрест)1е тины 12, входные информационные шины 13., и 13,, входные инфор30 мационш 1е шины 1 А| и 14,выходные управляющие шины 5( и 1 5г,входные управляющие шины I6i и 162 и адресные шины 17, и 17,,.

Блок 2 управления (фиг. 2) содер,, жит узел 18 памяти , регистр 19 адре-- са, буфер 20 ввода-вывода, содержащий две группы ключей 20, и 20, счетчик 21 команд, регистр 22 команд, буферньгй регистр 23, дешифра д тор 24 команд, синхронизатор 25.

Блок 3 местного управления (фиг.З и 4 содержит узел 26 памяти, регистр адреса 27, буфер 28 ввода-вывода, содержащий две группы ключей 28;j и

15 28, счетчик 29 команд, регистр 30 команд, буферньш регистр 3i, дешифратор 32 команд, синхронизатор 33, элемент И 34, дешифратор 35 адреса, элемент И 36, группу ключей 37, гистр 38 ввода, регистр 39 вьшода, группу ключей 40, элемент И 41, элемент И 42, дешифратор 43 адре.са.

Коммутатор 4 исходных данных и результатов (фиг. 5) -содержит ре- i5 гистр 44 вывода, группу вь1ходньгх ключей 45, элемент И 46, элемент И 47, группу входных ключей 48, регистр 49 ввода, элемент И 50, де

3

шифраторы 51 и 52 адреса и элемент И 53,

Решающий блок 5 (фиг. 6) содержи синхронизатор 54, буферный регистр 55, регистр 56 первого операнда, дешифратор 57 команд, счетчик 58 команд, сумматор 59, .регистр 60 команд, регистр 6 Г адреса, регистр 62 второго операнда, буфер 63 ввода-вывода, содержащий две группы ключей 63 и 63 и узел 64 памяти.

Двунаправленный коммутатор 6 промежуточных данных (фиг, 7) содержит дешифратор 65 адреса, элемент И 66, регистр 67 вывода, группу выходных ключей 68, элемент И 69, дешифратор 70 адреса, регистр 7 вывода, группу выходных ключей 72, элемент И 73 элемент И 74, дешифраторы 75 и 76 адреса, элемент И 77, группу входных 1слючей 78, регистр 79 ввода и элемент И 80.

Однонаправленный коммутатор 7 промежуточных данных (фиг. 8) содержит регистр 81, группу ключей 82, элементы И 83 и 84 и дешифраторы 85 и 86 адреса.

Блок 2 управления через системные шины 8, 9, 10,11,, llg и 12 соединен с блоками 3, и 32 местного управления, которые через шины 1317и коммутаторы 4 -4.исходных данных и результатов соединеньг с соответствующими группами решающих блоков 5,-5, 5,, и 5, -5,,,, кро- ме того, первая и вторая группа решающих блоков 5 соединена через двунаправленные коммутаторы , промежуточных данных и однонаправленный коммутатор 7 промежуточных данны

Временные диаграммы работы синхронизаторов- 25, 33 и 54 приведены на фиг. 13-15 соответственно.

Устройство работает следующим образом.

В исходном состоянии устройство подготовлено к работе, т.е. в узел

18памяти блока 2 управления записаны через устройство 1 ввода управля ющие программы, в узел 26 памяти блока местного з равления за- писаны блоком 2 управления управляющие программы, массивы коэффициентов, начальные и граничные условия, а в узлах 64 памяти рещающих блоков 5, и 5,2 управляющие программы.

Рассмотрим работу устройства на примере решения одномерного урав- - нения параболического типа:

48

зх

. (О

заданного на единичном отрезке , аппроксимируемого метод конечных разностей

1+ i jt- j + i J-H -ni n. OTI -4.TT

HLiUi -r

U;.,-2U; -HJj-,

V

Исходную область G() покрывают сеткой W. Расчет на последовательности сеток Ыц е м, ь зволяет получить в узлах сетки СО решение с требуемой точностью. Суммарное количество узлов в сетке а)ц и Un/2 меньше, чем в сетке СО, ,

Алгоритм решения задачи включает следую цие этапы:

1)Расчет условий опережения по формуле (2) с шагом в решающих блоках , например, методом простой итерации, в результате получа- ем Uf Г

2)Расчет условий сопряжения по формуле (2) с шагом в решающих блоках 5,,-5.,, , например, методом простой итерации, в результате полуЛ ч

чаем и

J4I

3)Пересылка результатов решения ил .решающих блоков 5 , 5, ,, ,5,,| через двунаправленные коммутаторы промежуточных данных в решающие блоки 5, -5ц, , где определяется суперпозиция полученных решений

И Д Itf Jtl I ,/ j и. -u. - u (3)

4)Обратная пересылка результатов суперпозиции из решающих блоков ,5 в решающие блоки 5,-5,,,., через двунаправленные коммутаторы 6,-6 ц промежуточньгх данных для расчета по п, 2 следующего временного слоя.

5)Обмен условиями сопряжения через блок 3| местного управления между решающими блоками 5, , 5,, 5 и 5j и т,д.

6)Нахождение значений поля в подобластях в решающих блоках 5,-5,

7)Пересылка значений поля в центральных узлах из рещающих блоков 5,-5„, 5.2 решающие блоки 5 , 5,, , . ,5 через двунаправленные коммутаторы 6., -6 промежуток данных и однонаправленный коммутатор 7 промежуточных данных для расчета

по п. 2 следующего временного слоя.

Переход к расчету следующего йре- менного слоя осуществляют по пп, 1 и 2.

Во время расчета следующего временного слоя блок 2 управления выводит промежуточные результаты через блок 1 вывода пользователю.

Совмещенные вьшолнения основных этапов описанного алгоритма отражены на временной диаграмме (фиг. 9)

Формулы метода простой итерации:

J4l(n,) j - Г JM(m) ичЫ

U: U;+vT - +U

J |(тЬ W, J

(4)

где m - номер итерации,

гГлИ

t--

(5)

с-

где с ; - невязка.

прогонки

(6)

re ,,UiM.f +PU

Для реализации вычислительного процесса по командам блока 2 управления (подобный алгоритм работы блока 2 управления приведен на фиг. 16) блоки 3 и 3 местного управления по собственным программам параллельно загружают исходную .информацию (коэффициенты, значения граничных условий) в соответствующую группу (в первый решающий блок 5, - ДЛя первой группы и в решающий блок 5 , , - для второй группы). Для этого блок 3 местного управления выдает по шинам 17, 13 и 15 соответственно адреса, данные и управляющий сигнал Запись (ЗП). В коммутаторе 4 исходных данных и результатов, к которому адресуется блок 3 местного управления срабатывает дешифратор 52 адреса (фиг. 5), с выхода которого активный сигнал совместно с активным сигналом ЗП поступает на входы элемента И 46. По сигналу с вьп;ода элемента И .46 передаваемая информация записывается в регистр вьгоода и одновременно через первый выход запроса коммутатора 4 сигнал Запрос поступает в решающий блок 5 (распределитель импульсов).По сигналу Запрос

решающий блок 5 переходит на подпрограмму чтения информации из регистра 44 вывода. Для этого блок 3 вы- ставляет на адресных выходах адрес р:о1чмутатора 4 исход гых данных и результатов, который поступает на вход дешифратора 53 адреса, а по шине Чтение (ЧТ) - активный сигнал. По

совокупности активных сигналов на входе к информационным входам решающего блока 5 иг формация через буфер 63 пвода-рывода записывается в регистр 56 первого операнда, а затем запоминается в узле 64 памяти. Последней командой передаваемого массива блок 3 местного управления запускает решающий блок 5 на выполнение програм- }ф по решению одномерной задачи по

формуле (4). Для этого передается в решающий блок 5 код, соответствующий передаче управления, и адрес перехода, Подроб гый алгоритм работы решающего блока для метода простой итерации

приведен на .фиг. 10.

Затем е5локи 3, и 32 местного уп- равлен1.я переключаются соответственно через коммутаторы 4 и 4 исход- i-tbrx даиньнс и результатов к входам

решающей блоков 5 и 5,25 загружают исходной информацией и передают управление решающим блокам 5, которые начинают выполнять собственно программу,, а в то время блоки З,, и 3

местного управления переключаются каждый в своей группе к следующему блоку 5 и, таким образом, все N решающих: блоков 5 первой группы со смещением во времени параллельно выполняют программы первого итерационного цикла (подробный алгоритм работы блоком 3 и 3 , местного управления приведен на фиг. 17 в режиме обмена с блоками 2 и 5). Количество ремающих блоков 5 во второй группе равно ()-Nf поэтому блок 3 местного управления продолжает загружать оставшиеся решающие блоки 5, которые аналог мно первой группе выполняют

nporpat.iMbi первого итерационного цикла.

После того, как выполнено решение в любом из решающих блоков 5 в первом итерационном цикле, решающий блок 5 сообщает об этом блоку местного управления. Для этого решаняций блок 5 выставляет по адресным шинам адрес ком1.гутатора 4 исходных дан7.

ных и результатов, который поступает на вход дешифратора 51, по информационным шинам передает данные, которые по управлйющему сигналу ЗП и сигналу с выхода дешифратора 51 записываются в регистр 49, а коммутатор 4 исходных данных и результатов формирует сигнал Запрос по шине 16 и передает в блок 3 местного управления, который переходит на подпрограмму чтения, включающую выдачу по шинам 17 адреса коммутатора 4, который поступает на вход дешифратора 52, и управляющего сигнала ЧТ по шине 15. По активному сигналу с выхода элемента И 50 информация с регистра 49 через ключи 48 поступает по информационным пганам 14 через буфер 28 ввода-вывода в буферный регистр 31 блока 3, а затем записьгоается в узел 26 памяти. Далее принимаются полученные на первой итерации значения из остальных блоков 5 в буферную область памяти блока 3 местного управления.

Блоки 3, и 3 местного управления не дожидаясь окончания вычисления во всех блоках 5, отслеживают окончание работы соседних блоков 5, и как только результат оказывается в буферной области осуществляют перезагрузку полученной информации в соседние освободившиеся решающие блоки 5 для выполнения следующей итерации в то времл, как остальные блоки 5 заканчивают текущую итерацию. Таким образом, последовател ьно, оставшиеся блоки 5 переходят к выполнению следующей итерации.

Описанный итеративный процесс повторяется в каждой группе до тех пор пока будут получены значения искомой функции текущего временного слоя для каждого узла с заранее заданной точностью в соответствии с формулой (5).

Для нахождения суперпозиции полученных решений значения функции, полученные во второй группе решающих блоков 5, пересылаются в решающие блоки 5j-5y через коммутаторы . В решающих блоках 5,-5ц вы полняется программа нахождения суперпозиции по формуле 3 . Алгоритм расчета суперпозиции приведен на фиг.11.

Рассмотрим более подробно передачу информации из решающего блока 5 второй группы в решающий блок 5 пер33148о

вой групггы. Передающий блок 5 выдает по адресным, информационным и управляющим шинам соответственно адрес, данные и сигнал ЗП. В двуна5 правленном коммутаторе промежуточных данных 6 по синхронизирующему сигналу с выхода элемента И 77 информация записывается в резистор 79 вывода и одновременно по шине Запрос форми10 руется сигнал, последний поступает в решающий блок 5, который принимает информацию. Для этого блок 5 выставляет на адресных выходах адрес, „ по которому срабатывает дешифратор

15 75 адреса и сигнал ЧТ. По совокупности активных сигналов на выходе элемента И 80 выходные ключи 78 подключают выходы регистра 79 ввода к информационным входам решающего

20 блока и информация через буфер 63 ввода-вывода записывается в регистр 56 первого операнда, а затем запоминается в узле 64 памяти.

После расчета суперпозиции в ре25 шакщих блоках 5,-5, полученные значения пересылаются через соответствующие коммутаторы 6,-6 обратно во вторую группу решающих блоков 5: из

5, в 3 2 Ntz 30 го используются регистр 71 вывода., ключи 72 двунаправленного коммутатора 6 промежуточных данных. Кроме того , соседние решающие блоди первой группы обмениваются через коммутатор 4 исходных данных и результатов и блок 3 значениями суперпозиции, которые являются граничными значениями для расчета поля в подобласти. Так как количество подобластей на одну Q больше, чем количество вычисляемых условий сопряжения, то при расчете поля участвует и решающий блок 5, , в который предварительно пересьша- ется исходная информация из решающе- - го блока 5, . Вычисление поля в решающих блоках 5 первой группы осуществляется по формулам (6). Алгоритм работы решающего блока приведен на фиг. 12.

0 гТосле того, как получено значение поля в центральном узле подобласти, из блоков передаются значения через соответствующий двунаправленный коммутатор 6,-6ц промежуточ5 ных данных (регистр 67 вывода и

ключи 63), в блоки 5, и т.д., а из блока 5, через однонаправленный коммутатор 7 - в решающий блок

5

N-t1

. Далее устройство переходит к

расчету следующего временного слоя. Описанная последовательность повторяется до тех пор, пока не закон- чится время моделируемого процесса Таким образом, введение новых ч функциональных блоков и связей позволяет повысить производительность устройства за счет распараллелива- НИН вычислительного процесса в решающих блоках.

Формула изобретения

Устройство для решения дифференциальных уравнений, содержащее блок управления, два блока местного управления, первую группу из N решающих , блоков (N - число узлов сетки), пер вуто группу из N коммутаторов исходных данных и результатов, вторую группу из (2N-t-1) решающих блоков , вторую группу из (2N-1-1) коммутаторов исходных данных и результатов каж- дый решающий блок содержит синхронизтор, регистр первого операнда, регистр второго операнда, дешифратор команд, сумматор, регистр команд, . счетчик команд, две группы ключей, регистр адреса, узел памяти, буферный регистр и регистр частичного результата, в каждом решающем блоке первый выход синхро-низатора соединен с входом синхронизации регистра вто- рого операнда, второй выход - с счетным входом счетчика команд, третий выход - с входом синхронизации регистра адреса, четвертый и пятый выходы - с управляющими входами клю- чей первой и второй групп соответственно , шестой выход - с входом синхронизации регистра команд, седьмой выход - с входом синхронизации регистра первого операнда, восьмой вы- ход - с управляющим входом сумматора девятый выход - с входом синхронизации буферного регистра, десятый выход с входом синхронизации регистра частичного результата решающего блока, первая группа входов кода режима синхронизатора соединена с выходами дешифратора команд, входы которого соединешз с выходами- регистра команд,,выходы ключей второй группы соединены .с информационными входами :;регистра второго операнда, регистра команд, первой группой информацион

ных входов регистра первого операнда и с информационными входами буферного регистра, выходы счетчика команд соединены с информационными входами регистра адреса, выходы регистра пер)вого операнда соединены с входами гсерного слагаемого сумматора, входы второго слагаемого которого соединены с выходами регистра второго операнда, выходы сумматора соединены с второй группой информационных входов регистра первого операнда и второй группой входов кода режима синхронизатора, выходы буферного регистра соединены с третьей группой входов кода режима синхронизатора, выходы регистра первого операнда соединен) с информационными входами ключей первой группы, одиннадцатый выход синхронизатора соединен с входом записи узла памяти, двенадцатый выход - с входом чтения узла памяти, информационные входы ключей второй группы соединены с выходами узла памяти, выходы ключей первой группы - с информационными входами узла памяти, выходы регистра адреса соединены с адресными входами узла памяти, каждый коммутатор исходных .данных и результатов содержит регистр вьшода, группу выходных ключей, четыре элемента И, группу входных ключей, регистр ввода, два дешифратора адреса, причем выходы элементов И соединены соответственно с входом синхронизации регистра вывода, управляющими входами входных ютючей, с входом синхронизации регистра ввода и с управляющими входами выходных ключей, выходы регистра ввода - с информационными входами входных ключей, выход первого дешифратора адреса соединен с первыми входами третьего и четвертого элементов И, выходы регистра вывода подключены к информационным входам выходных клю- чей, выход второго дешифратора адреса соединен с.первыми входами первого и второго элементов И; блок управления содержит узел памяти, -регистр адреса, две группы ключей, счетчик команд5 регистр команд, буферный регистрэ дешифратор команд, синхронизатор, первый выход синхронизатора блока управления соединен с входом синхронизации буферного регистра, второй выход - со счетным

входом счетчика команд, третий выход - с входом синхронизации регистра адреса, четвертый и пятый выходы - соответственно с управляющи- ми входами ключей первой и второй групп, шестой выход - с входом синхронизации perHCtpa команд, первая группа входов кода ре жима синхронизатора соединена с выходами дешифра- тора команд, входы которого соединены с выходами регистра команд, входы ключей первой группы соединены с выходами буферного регистра, выходы ключей второй группы - с информацион ными входами регистра команд и буферного регистра, выходы счетчика команд - с входами регистра, выходы ключей первой группы - с информационными входами узла памяти, входы клю- чей второй группы - с выходами узла памяти, выходы регистра адреса соединены с адресными входами узла памяти седьмой выход синхронизатора соединен с входом записи узла памяти, восьмой выход - с входом чтения узла памяти; каждый блок местного управления содержит узел памяти, регистр адреса, четыре группы ключей, счетчик команд, регистр команд, буферньн ре- гистр, дешифратор команд, синхронизатор, четыре элемента И, два дешифратора адреса, регистр ввода, регистр вывода, причем первый выход синхронизатора соединен с входом синхрониза- ции буферного регистра, второй выход - со счетным входом счетчика команд, третий выход - с входом синхронизации регистра адреса, четвёртьш и пятый выходы - соответственно с управляющими входами ключей первой и второй rpynnv шестой выход - с входо синхронизации регистра, первая группа входов кода режима синхронизатора соединена с выходами дешифратора команд, входы которого соединены с выходами регистра команд, информационные входы ключей первой группы соединены с выходами буферного регистра, выходы ключей второй группы - с ин- форма1|ионными входами регистра ко- манд и буферного регистра, выходы счетчика команд соединены с информа- ционньс и входами регистра адреса, выходьг которого соединены с адресными входами узла памяти, седьмой вы- ход синхронизатора соединен с входом записи узла памяти и с первым входом первого элемента И, восьмой выход

j 10 15 20 5 О с

0

с входом чтения узла памяти и первым входом второго элемента И, перв ый вход второй группы входом кода режима синхронизатора соединен с выходом третьего элемента И, информационные входы ключей третьей группы соеди- неШз с выходами регистра вывода, выход первого дешифратора адреса - с вторыми входами первого и второго элементов И, выход второго элемента И - с управляющими входами ключей третьей группы, выход первого элемента И - с входом синхронизации регистра ввода, выходы которого соединены с информационными входами ключей четвертой группы, управляющие входы которых соединены с выходом четвертого элемента И, выход третьего элемента И соединен с входом синхронизации регистра вывода, выход второго дешифратора адреса соединен с первыми входами третьего и четвертого элементов И, выхода ключей первой группы соединены с информационными входами узла памяти и регистра ввода, информационные входы ключей второй группы - с выходами узла памяти и ключей третьей группы, выходы ключей четвертой группы блоков местного управления подключены к информационным входам ключей второй группы блока управления, выходы ключей первой группы соединены с информационными входами узла памяти и регистра ввода, информационные входы ключей второй группы - с выходами узла памяти и ключей третьей группы, выходы ключей четвертой группы блоков местного управления подключены к информационным входам ключей второй группы блока управления, выхода ключей первой группы блока управления соединены с информационными входами регистров вывода блоков местного управления, седьмой и восьмой выходы синхронизатора блока управления соединены с вторыми входами соответственно третьего и четвертого элементов И блоков местного управления, выходы первых элементов И блоков местно- го управления соединены соответственно с первым и вторым вxoдa и второй группы входов кода режима синхронизатора, выходы регистра адреса которого соединены с входами вторых дешифраторов адреса блоков местного управления, выходы входных ключей каждого коммутатора исходных данных и результатов первой группы подключены к информационным входам ключей второй группы первого блока местного управ- ления, выходы ключей первой группы которого соединены с информационными входами регистров вывода каждого коммутатора исходных данных и результатов первой группы5 седьмой и восьмой выходы синхронизатора первого блока местного управления соединены с вторыми входами соответственно первого и второго элементов И каждого коммутатора исходных данных и результатов первой группыJ со второго по (К+1)-й входы второй группы входов кода режима сийхронизатора первого блока местного управления соединены с выходами третьих элементов И коммутачю- . ров исходных данных и результатов первой группы, выходы регистра адреса первого блока местного управления соединены с входами второго дешифратора адреса каждого коммутатора исход ных данных и результатов первой группы, выходы входных ключей группы коммутаторов исходных данньпк и результатов второй группы подключены к информационным входам ключей второй группы второго блока местного управ- ,ления, выходы ключей первой группы которого соединены с информационными входами регистров вывода каждого коммутатора исходных данных и результа- тов второй группы, седьмой и восьмой выходы синхронизатора второго блока местного управления соединены с вторыми входами соответственно первого и второго элементов И каждого коммута- тора исходных данных и результатов второй группы, со второго по (2N+2) входы второй группы входов кода режим синхронизации второго блока местного управления соединены с выходами тре- тьих элементов И соответствующих коммутаторов исходных данных и результатов второй группы, выходы регистра адреса второго блока местного управления соединены с входами второго де- .шифратора адреса каждого коммутатора ИСХОДНЫХ: данных и результ атов второй группы, выходы вьгкодных ключей, .MFI- формационные входы регистра ввода входы первого дешифратора адреса., второй третьего элемента И, второй вход четвертого элемента И, выход первого элемента И i-ro (,

3N-b) коммутатора исходных данных и результатов первой и второй групп соединены соответственно с информа- ционньп 1и входами ключей второй группы, вькодами ключей первой группы, выходами регистра адреса, одиннадцатым и двенадцатым выходами синхронизатора,, с первым входом четвертой группы входов кода режима синхронизатора i-го решающего блока соответственно первой и второй групп, отличающееся тем, что, с целью повышения производительности, в него введен, дополнительный коммутатор искодн1,1х данных и результатов, дополнительный решающий блок., однона- правлеипый коммутатор промежуточных данных и N двунаправленных коммутаторов промежуточных данных; однона- правленньпЯ коммутатор промежуточных данных содержит регистр, группу ключей, два элемента И, два дешифратора адреса, причем выход первого дешифратора адреса соединен с первым входом первого элемента И, выход которого соединен с синхронизирующим входом регистра, выход второго дешифратора адреса соединен с первым выводом зторого элемента И, выход которого соединен с управляющими входами ключей, каждый двунаправленный коммутатор промежуточных данных содержит четыре дешифратора адреса, дна регистра вывода, регистр ввода, две группы выходных ключей, группу входных: ключей, шесть элементов И, при этом выход первого дешифратора адреса соединен с первым входом первого элемента И, выход которого соединен с синхронизируюЕцим входом первого регистра вывода, вьрсоды которого соединены с информационными, входами ёъпс одных ключей первой 1груп- пы, вьгх:од второго дешифратора адреса соединен с первым входом второго элемента И, вьпсод которого соединен с управляющими входами ключей первой группы, выходы второго регистра вы- . вода соединены с информационными входами выходных ключей второй группы, управляющие входы которых соединены с выходом третьего элемента И, выход третьего дешифратора адреса соединен с первьии входами четвертого и пятого элементов И, выход четвертого элемента И соединен с синхронизирующим входом второго регистра вывода.

выход четвертого дешифратора адреса соединен с первыми входами третьего и шестого элементов И, выход шестого элемента И - с синхронизирующим входом регистра ввода, выходы которого соединены с информационным входами входных ключей группы, выход пятого элемента И соединен с управляющими входами входных ключей группы, выходы ключей первой группы входы ключей второй группы, седьмой и восьмой выходы синхронизатора, (М+)-й вход второй группы входов кода режима синхронизатора и выходы регистра адреса первого блрка местного управления соединены соответственно с информационными входами регистра вывода, выходами входнь1х ключей группы, вторыми входами первого и второго элементов И, выходом третьего элемента И и выходами второго дешифратора адреса дополнительного коммутатора исходных данных и результатов, выходы выходных ключей группы, информационные входы регистра ввода, входы первого дешифратора адреса, вторые входы третьего и четвертого элементов И и выход первого элемента И дополнительного коммутатора исходных данных и результатов соединены соответственно с информационными входами ключей второй группы, выходами ключей первой группы, выходами регистра адреса, одиннадцатым и двенадцатым выходами синхронизатора и четвертой группой входов кода режима синхронизатора дополнительного решающего блока, выходы ключей первой группы, первый выход второй группы выходов кода режима синхронизатора и выходы регистра адреса дополнительного решающего блока соединены соответственно с информационными входами регистра, вторьм входом первого элемента И и входами первого дешифратора адреса однонаправленного ком гутатора промежуточных данных,-выходы ключей группы, второй вход второго элемента И, выход первого элемента И и входы второго дешифратора адреса однонаправленного коммутатора промежуточных данных соединены соответствено с ми ключей второй группы, двенадцатым г выходом синхронизатора, вторым входом четвертой группы входов кода режима синхронизатора и выходами регистра адреса первого и решающего блоков второй группы, входы первого 10 и третьего дешифраторов адреса, вторые входы первого и четвертого элементов И, информационные входы первого и второго регистров вывода, выход шестого элемента И, выз4о;цз1 вход- 15 ных ключей группы и второй вход пятого элемента И i-го двунаправленного коммутатора промежуточных данных соединены соответственно с регистром адреса, одиннадцатым выходом синх- 20 ронизатора, выходами ключей первой группы, вторым входом четвертой г.руп- пы входов кода режима синхронизатора, информационными входами ключей второй группы и вторым входом второй 25 группы выходов :(-го решающего блока первой группы, выход первого элемента И, выходы выходньсх ключей первой группы, второй вход второго элемента и и входы дептфратора адреса i-ro 0 двунаправленного коммутатора промежуточных данных соединены соответственно с информационнъгми входами ключей второй группы, двенадцатым выходом синхронизатора, выходами регист- 5 ра адреса (j N- -3L)-ro решающего блока второй группы, выходы выходных ключей второй группы, второй вход ,третьего элемента И, выход четвертого элемента И, входы четвертого де- 0 шифратора адреса, второй-вход шестого элемента И и информационные входы регистра ввода -го двунаправленного коммутатора промежуточных данных соединены соответственно с информа- 5 ционными входами ключей второй группы, двенадцатым выходом синхронизатора и вторым входом четвертой группы кода режима, выходами регистра адреса , одиннадцатым выходом синхронизатора , выходами ключей первой группы ( + 2;)-ro решающего блока второй груп пы.

Й;5к ft,f3,4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения дифференциальных уравнений | 1983 |

|

SU1233149A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Устройство для решения дифференциальных уравнений | 1982 |

|

SU1104513A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для решения дифференциальных уравнений | 1985 |

|

SU1348854A1 |

| Устройство для реализации двумерного быстрого преобразования фурье | 1983 |

|

SU1142845A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Устройство для решения дифференциальных уравнений | 1985 |

|

SU1330635A1 |

| Устройство для обработки нечеткой информации | 1985 |

|

SU1564603A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ АВТОНОМНЫМ РОБОТОМ | 2008 |

|

RU2424105C2 |

Изобретение относится к цифровой вычислительной технике и предназначено для решения дифференциаль- ных уравнений в частных проиэводнык. Устройство содержит блок управления, два блока местного управления, коммутаторы исходныхданных и результатов, решающие блоки, двунаправленный и однонаправленный коммутаторы промежуточных данных. В устройстве достигнуто повьппение производительности за счет совмещения во времени этапа расчета поля и расчета супер- - позиции. 18 ил. (/} с I-ч 00 00 4;; 00

1 tS К .

I -/Ч +

ФнгЗ

IL,

5

.ft

Чп

48

tfS

Рг

H5

iS.

Ч«16

Janpoc

Чт.

i™

51

n

.fJU

Запрос

Фщ.8

Пкчет с июгон

IHk

-xit V

-wr

| 7Г

I /t1

Перетнма гктвд P6,t,PS,j

tatogSKO тювны famw

bcveflT ffSf

:3CDL

y-gfw(W pngfetmomoS

Г Начаяо J

9иг.9

T,

fOJO jt

..„/ Ly/ -i РЛО

Яег|7

Переход к CAt eijtou4su ите-

.- I Конец j

.(}д к t- isjtmy cynepno-

( Начали Л

Фиг.//

Огакм А/Лтчи-афесв МЯ.-ИГ

Савнал

««я (

ЙЖКйЙГ З -й/

CatHOf затки в ре- гиаяр ttf-tz)

Р

tNCM tnatpftttftfna

ts -гп

CutHOt ttOavu аврка

izs-iei

Сиыая виЗачи us пв актра (Zf- i3l Стмал учзавлелии h eiKta I4№ai I IS-let

ttiva ttmeu ttl-O)

e i S-«f fuzHOf чяеиив(а-Я1

la jtvnJtwMw I {чвмм /им«п)(

йклол затее t w- Вжя a-t3l

Фиг/2

CuffVf ailflHa 1 }}-lV

CtiCHOfl 4(rtMUH JJ S1

Сагм gnfai fma

rf « /4i/l ( JJ V t ) S p - (JJ-Ji ful a uнлt}t f O

1J j;

Гцглид aJflf o iJJ 77

Гугмал iuAivi4 ui fff- tafmia I i) - Ji)

ynfuiteHVH

HAffvfu lj- Sl

CVtfftfl SOntflJ l-SJ f6:

Ci tftiJ oiiDfttt 4i-n

CiJftllA vmcfMi liS-26f

Cvttfft управление tftoAftft

Cutha записи 6 yt- Jiicfnp iJS 3f)

ituKA vrnfuit Данила JJ 2S wj Sneuif eia fCfnfioijciTtSa S /

Сигнал быдачи адреса (54-81) Сигнал чтения t54-f j

tuemjA управления ЪтЯны {5Ч-вЗ сигнал записи в ре kucmp ЧЧ 5в)

Сигнал t Hxpeнекто I (

иенак выЗачи oS Pfca (54-61)

ftitHOA dt/ffavu u) p« tucmpa (УЧ-se/ CutHOK управления ffi OffMt/ нлачей lS4-fS)

сигнал зопаси (S4-6 t)

Нимл чтении ffamtit ji Sf или из внешне fa ycmpaucmta 8 5S

J 1„

| Вычислительная система для решения дифференциальных уравнений | 1975 |

|

SU620980A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для решения дифференциальных уравнений | 1982 |

|

SU1108460A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-23—Публикация

1983-12-19—Подача