первыми входами элементов ИЛИ второй группы решающего блока, входы ключей первой группы решающего блока соединены с информационными выходами узла памяти решающего блока, выходы ключей второй группы решающего блока соединены со вторыми входами элементов И первой группы решающего блока, выходы которых соединены со вторыми входами элементов ИЛИ первой группы решающего блока, выходы регистра адреса решающего блока соединены с первыми входами элементов И второй группы решающего блока, выходы которых соединены со вторыми входами элементов ИЛИ второй группы решающего блока, первый выход первой группы выходов распределителя импульсов решающего блока соединен со вторым входом первого элемента И решающего блока, второй выход первой группы выходов распределителя импульсов решающего блока соединен с входом чтения узла памяти решающего блока, выход первого элемента И решающего блока соединен со вторым входом элемента ИЛИ решающего блока, выход элемента ИЛИ решающего блока соединен со входом записи узла памяти решающего блока, выходы элементов ИЛИ первой и второй групп решающего блока соединены соответственно с информационными и адресными входами узла памяти решающего блока, первый выход второй группы выходов распределителя импульсов решающего блока соединен с управляющим входом регистра множителя решающего блока, второй выход второй группы выходов распределителя импульсов решающего блока соединен с управлякшщм входом счетчика команд решающего блока, третий выход второй группы выходов .распределителя импульсов решающего блока соединен с управляющим входом регистра адреса решающего блока, четвертый выход второй группы выходов распределителя импульсов решающего блока соединен с управляющими входами ключей первой группы решающего блока, пятый выход второй группы выходов распределителя импульсов решающего блока соединен с первыми входами элементов И пятой группы решающего блока, шестой выход второй групцы выходов распределителя импульсов решающего блока соединен с первыми входами элемен8460

тов и шестой группы решающего блока, седьмой выход второй группы выходов распределителя импульсов решающего блока соединен с управляющими входами ключей второй группы решающего блока, восьмой выход второй группы выходов распределителя импульсов решающего блока соединены с управляющим входом регистра команд решающего блока, девятый выход второй группы выходов распределителя импульсов решающего блока соединен с управляющим входом регистра результата прогонки решающего блока, десятый выход второй группы выходов распределителя импульсов решающего блока соединен с управляющим входом регистра множимого решающего блока, одиннадцатьй выход второй группы выходов распределителя импульсов решающего блока соединен с управляющим входом сумматора решающего блока, двенадцатый выход второй группы выходов распределителя импульсов решающего блока соединен с управляющим входом регистра частичного произведения решающего блока, первая группа входов распределителя импульсов решающего блока соединена с выходами дешифратора команд решающего блока, входы которого соединены с выходами регистра команд решающего блока, выходы регистра множителя соединены со вторыми входами элементов И пятой группы решающего блока, первая группа выходов регистра результата прогонки решающего блока соединена со вторыми входами элементов И шестой группы решающего блока, выходы элементов И пятой и шестой групп решающего блока соединены со входами элементов ИЛИ третьей группы решающего блока, выходы которых соединены с информационными входами ключей второй группы решающего блока, выходы ключей первой группы решающего блока соединены с информационными входами регистра множителя решающего блока, регистра команд решающего блока, регистра частичного произведения рещаклдего блока, первой группой информационных входов регистра множимого решающего блока, первой группой информационных входов регистра результата прогонки решающего блока, выходы счетчика команд решающего блока соединены с входами регистра адреса решакщего блока, выходы регистра частичного

произведения решающего блока соединены с первой группой входов сумматора решающего блока,вторая группа входов которого соединена с выходами регистра множимого решающего блока, выходы сумматора решающего блока соединены со второй группой информационных входов регистра результата прогонки решающего блока, вторая группа вьЬсодов которого соединена со второй группой информационных входов регистра множимого решающего блока, выходы выходных информационных ключей группы и выходы входных информационных ключей группы каждого коммутатора управляющих сигналов первой группы соединены соответственно с информационньми входами ключей первой группы и выходами ключей второй группы соответствующего решакщего блока первой группы, входы второго дешифратора адреса, второй вход четвертого элемента И, второй вход второго элемента И и выход первого элемента И каждого коммутатора первой группы соединены .соответственно с выходами регистра адреса, третьим и четвертым выходами первой группы выходов распределителя импульсов и первым входом второй группы входов распределителя импульсов соответствующего решающего блока первой группы, отличающееся тем, что, с целью повышения производительности, в него введены вторая группа из М решающих блоков, вторая группа из М коммутаторов управляющих сигналов, первый коммутатор данных, который содержит К узлов коммутации, и второй коммутатор данных, который содержит М узлов коммутации, каждый узел коммутации первого и второго коммутаторов данных содержит два дешифратора адреса, триггер заявок, два элемента НЕ, два элемента И, два элемента ИЛИ, группу выходных информационных ключей, группу выходных адресных ключей, выходной управляющий ключ, выходной триггер, группу входных адресных ключей, группу входных информационных ключей входной управляющий ключ, выход первого дешифратора адреса узла коммутации коммутатора данных соединен с синхронизирующим входом триггера заявок узла коммутации коммутатора даН ных, выход триггера заявок узла коммутации коммутатора данных соединен

08460

с первым входом первого элемента И и с первым входом первого элемента ИЛИ узла коммутации коммутатора данных, выход первого элемента ИЛИ предыдущего узла коммутации коммутатора данных соединен со входом первого элемента НЕ и со вторым входом первого элемента ИЛИ узла коммутации коммутатора данных, второй вход первого элемента ИЛИ первого узла коммутации коммутатора данных соединен с входом логического нуля устройства, выход первого элемента НЕ узла коммутации коммутатора данных соединен со вторым входом первого элемента И узла коммутации коммутатора данных, выход которого соединен с управляющими входами выходных информационных ключей группы узла коммутации коммутатора данных, выходных адр есных ключей группы и выходного управляющего ключа узла коммутации коммутатора данных, выход второго дешифратора адреса узла коммутации коммутатора данных соединен с первым входом второго элемента И узла коммутации коммутатора данных, выход второго элемента ИЛИ узла коммутации коммутатора данных соединен со вторым входом второго элемента И узла коммутации коммутатора данных, выход которого соединен с первым входом выходного триггера, со входом второго элемента НЕ и с управляющими входами входных адресных ключей группы, входных информационных ключей группы, входного управляющего ключа узла коммутации коммутатора данных, выход входного управляющего ключа узла коммутации коммутатора данных подключен к первому выходу записи в память узла коммутации коммутатора данных, выход второго элемента НЕ .узла коммутации коммутатора данных соединен со вторым входом выходного триггера узла коммутации коммутатора данных, блок управления содержит узел памяти, регистр адреса, две группы ключей, группу элементов ИЛИ, две группы элементов И, регистр половинного шага, счетчик команд, регистр команд,

сумматор, регистр коэффициента, дешифратор команд, регистр исходного шага, распределитель импульсов, регистр результата суперпозиции, выходы ключей первой группы блока управления соединены с информационными входами узла памяти блока управления, входы ключей второй группы

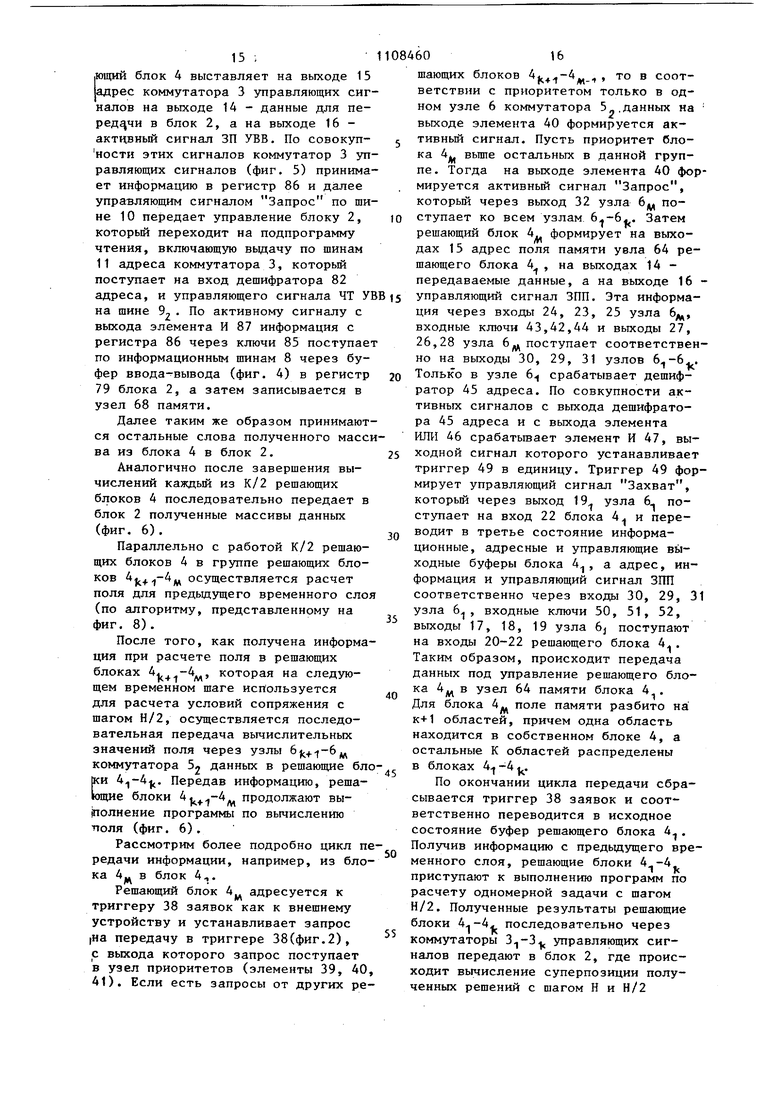

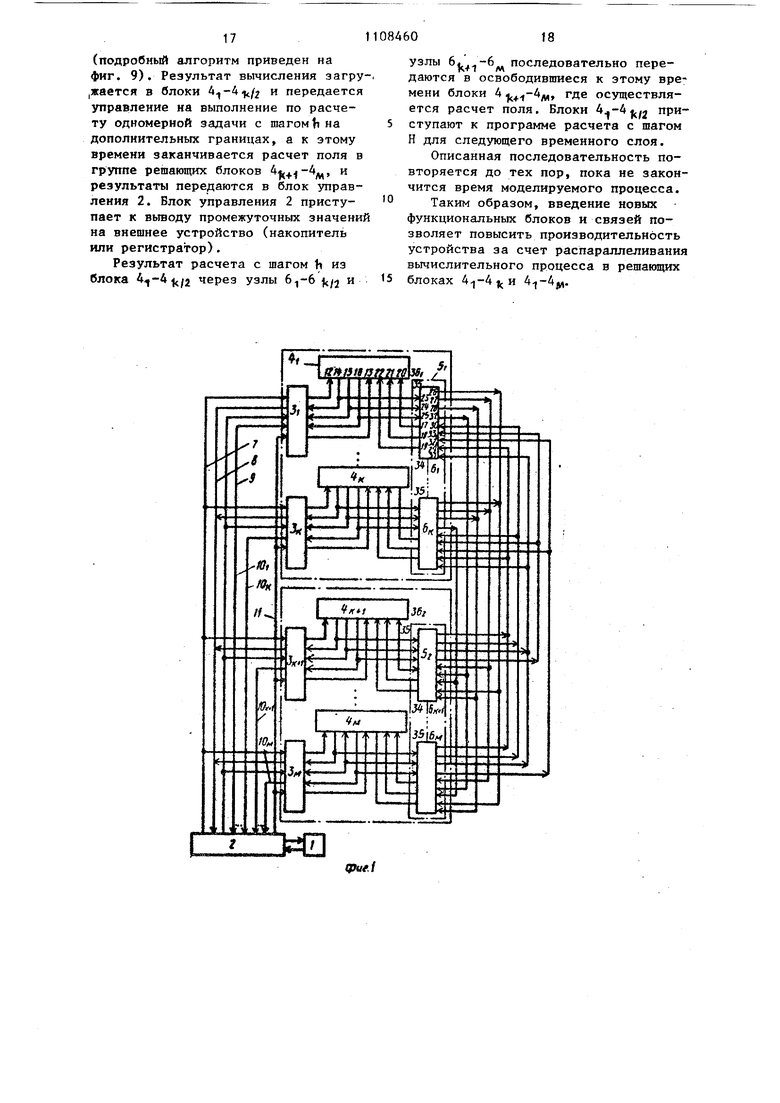

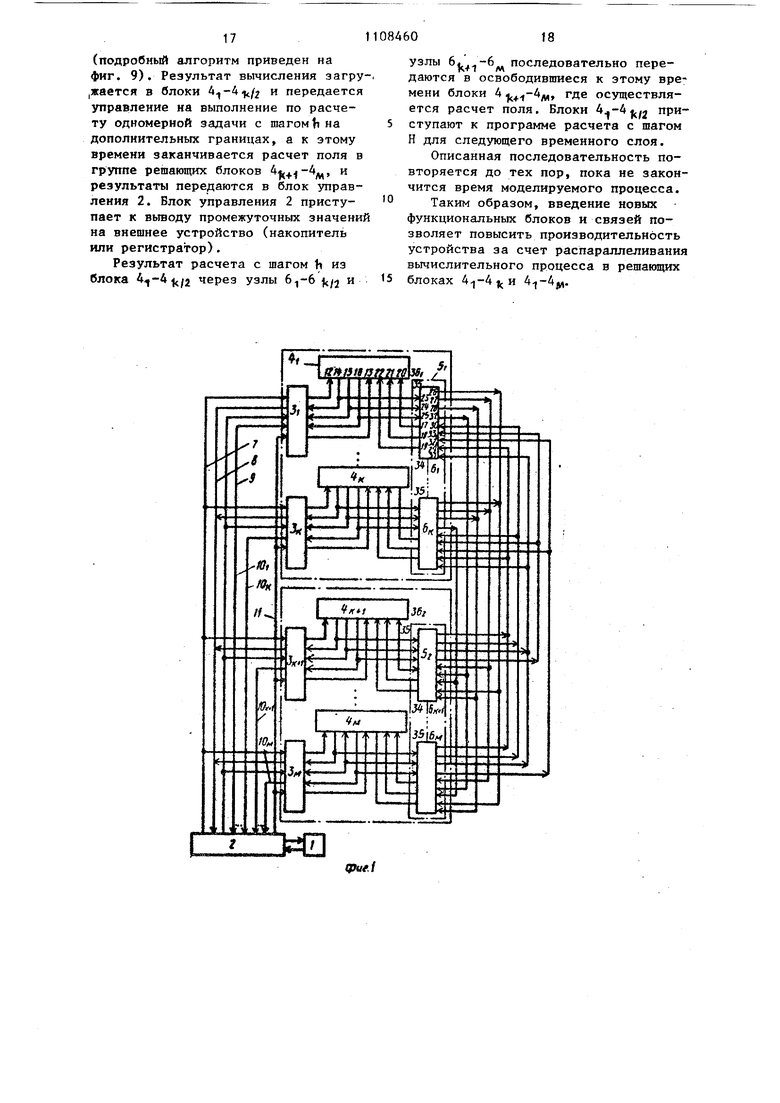

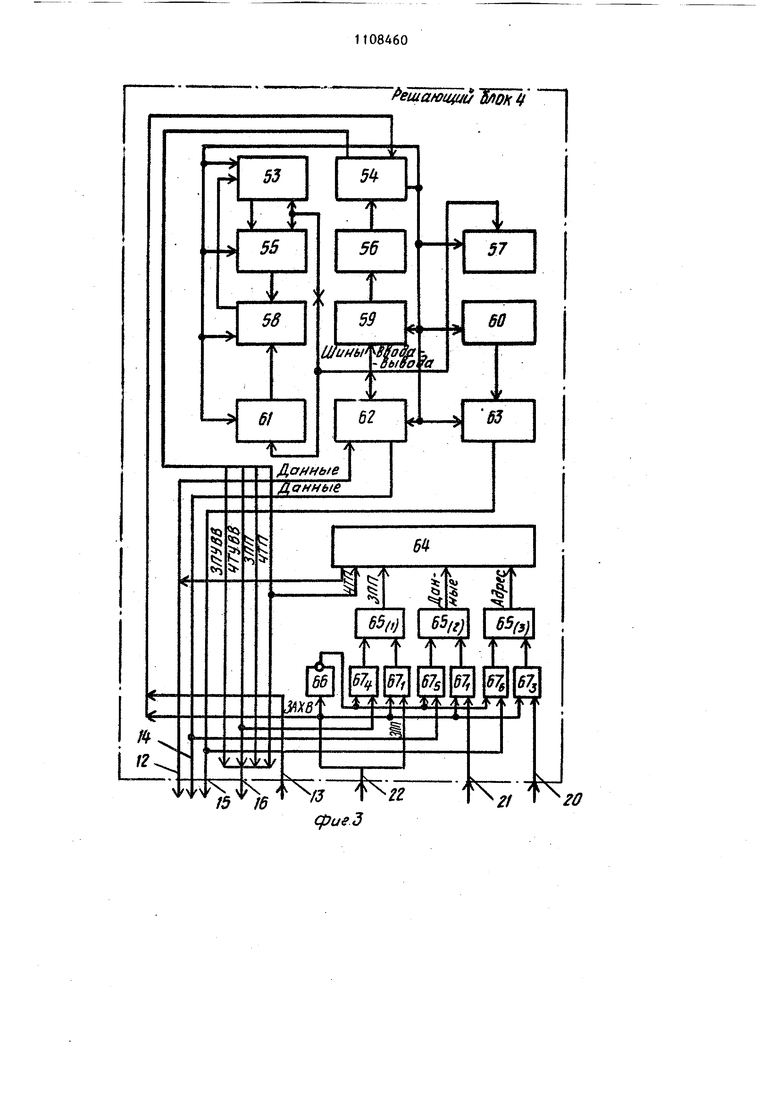

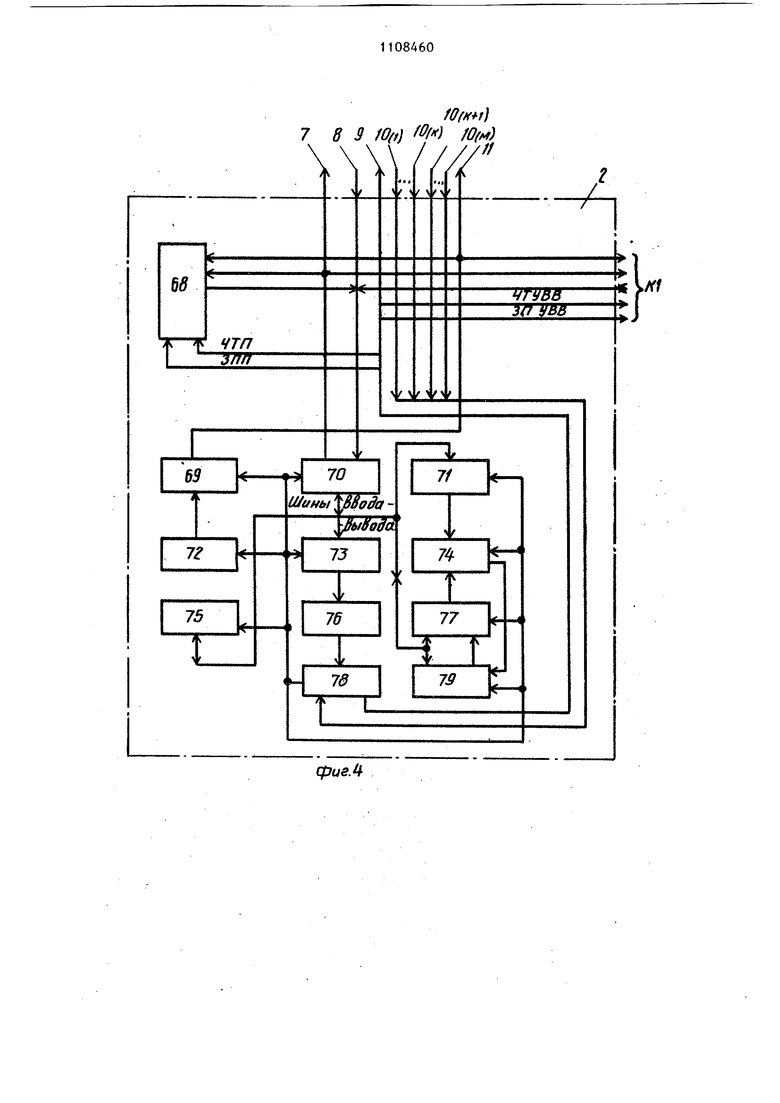

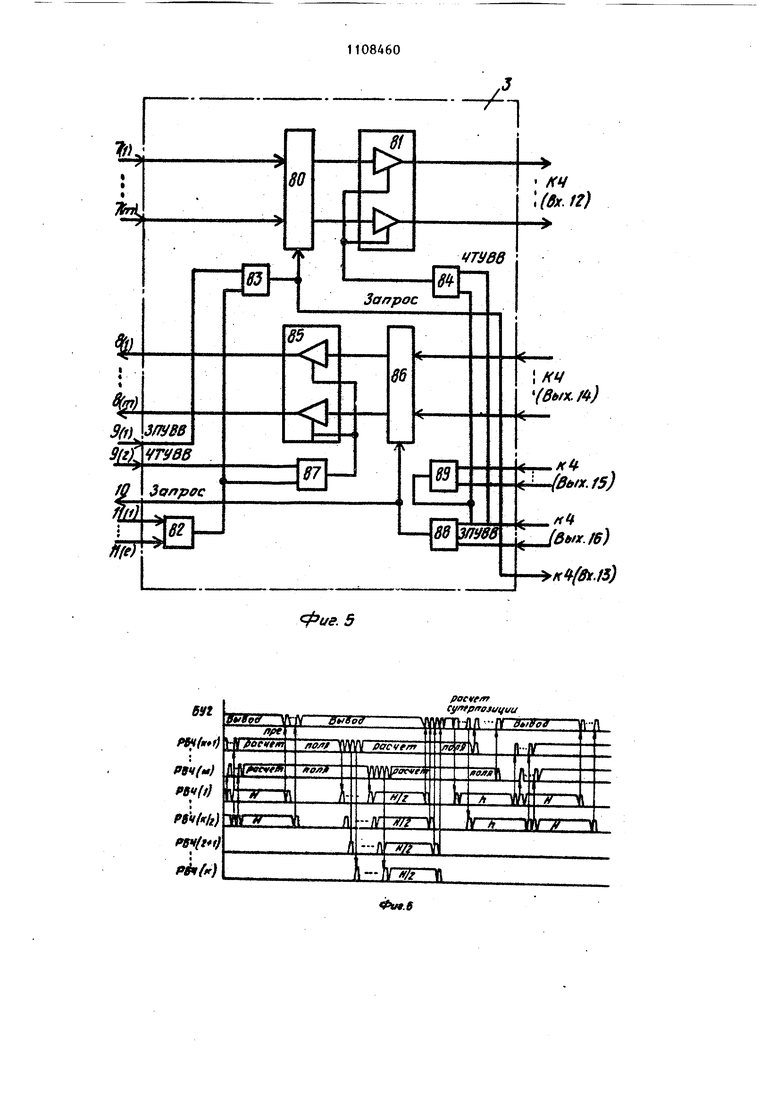

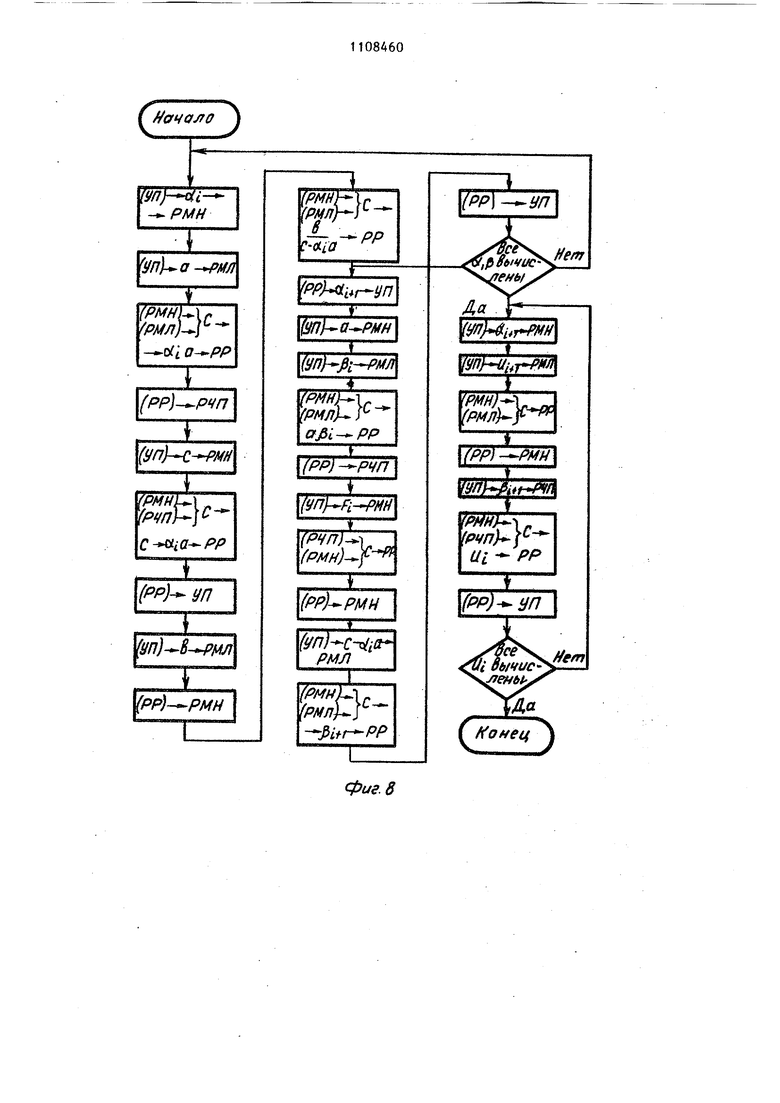

блока управления соединены с информациоиньп га выходами узла памяти блока управления, первый выход первой группы выходов распределителя :импульсов блока управления соединен с входом записи узла памяти блока управления, второй выход первой группы выходов распределителя импульсов блока управления соединен с входом чтения узла памяти блока управления, выходы регистра адреса блока управления соединены с адресными входами узла памяти блока управления, первый выход второй группы выходов распределителя импульсов блока управления соединен с управляющим входом регистра коэффициента блока управления, второй выход второй группы выходов распределителя импульсов блока управления соединен с управляющим входом счетчика команд блока управления, третий выход второй группы выходов распределтеля импульсов блока управления соединен с управляющим входом регистра адреса блока управления, четвертый выход второй группы выходов распределителя импульсов блока управления соединен с управляющими входами ключей первой группы блока управлен пятьй выход второй группы выходов распределителя импульсов блока управления соединен с первыми входами элементов И первой группы блока управления, шестой выход второй группы вьпсодов распределителя импульсов блока управления соединен с первыми входами элементов И второй группы блока управления, седьмой выход второй группы выходов распределител импульсов блока управления соединен с управляющими входами ключей второй группы блока управления, восьмой выход второй группы выходов распределителя импульсов блока управления соединен с управляющим входом регистра команд блока управлени девятый выход второй группы выходов распределителя шшульсов блока управления соединен с управляющим входом регистра результата суперпозиции блока управления, десятый выход второй группы выходов распределтеля импульсов блока управления соединен с управляющим входом регистра исходного шага блока управления, одиннадцатый выход второй группы выходов распределителя импульсов блока управления соединен с управляющим входом сумматора блока управления, двeнaдцatый выход второй группы вь ходов распределителя импульсов блока управления соединен с управляющим входом регистра половинного шага блока управления, перва группа входов распределителя импульсов блока управления соединена с выходами дешифратора команд блока управления, входы которого соединены с выходами регистра команд блока управления, выходы ключей второй групп блока управления соединены с информационными входами регистра коэффициента блока управления, регистра команд блока управления, регистра половинного шага блока управления, первыми группами информационных входов регистра исходного шага блока управления и регистра результата суперпозиции блока управления, информационные входы ключей первой группы блока управления соединены с выходами элементов ИЛИ группы блока управления, первые входы которых соединены выходами элементов И первой группы блока управления, вторые входы элементов ИЛИ группы блока управления соединены с выходами элементов И второй группы блока управления., вторые входы элементов И первой группы блока управления соединены с выходами регистра коэффициента блока управления, вторые входы элементов И второй группы блока управления соединены с первой группой выходов регистра результата суперпозиции блока управления, выходы счетчика команд блока управления соединены с информационными входами регистра адреса блока управления, вькоды регистра половинного шага блока управления соединены с первой группой входов сумматора блка управления, первая группа входов которого соединена с выходами регистра исходного шага блока управления, выходы сумматора блока управления соединены со второй группой информационных входов регистра результата суперпозиции блока управления, вторая группа выходов которого соединена со второй группой информационных входов регистра исходного шага блока управления, выходы ключей первой группы блока управления соединены с информационными входами регистра вывода коммутаторов управляющих сигналов первой и второй гРУПп, выходы входных информационных ключей коммутаторов управЛЯРОЩИХ сигналов, первой и второй групп соединены с информационными входами ключей первой группы блока управления, третий выход первой группы выходов распределителя импульсов которого соединен со вторыми входами первых элементов И коммутаторов управляющих сигналов первой и второй групп, чётвертьш выход первой группы выходов распределителя и п1ульсов соединен со вторыми входами третьих элементов И коммутаторов управляющих сигналов перво и второй групп, выходы четвертых Эле ментов И которых подключены ко второй группе входов распределителя импульсов блока управления, выходы регистра адреса которого соединены со входами первого дешифратора адреса коммутаторов управляющих сигналов первой и второй групп, выходы выходных информационных ключей группы и входы регистров ввода каждого коммутатора управляющих сигналов второй группы соединены с информационными входами ключей первой группы и выходами ключей второй группы соответствующего решающего блока второй группы, входы второго дешифратора адреса, второй вход четвертого элемента И, второй вход второго элемента И и выход первого элемента И каждого коммутатора управляющих сигналов второй группы соединены соответственно с выходами регистра адреса,тре тьим и четвертым выходами первой группы выходов распределителя импульсов и вторым входом второй группы входов распределителя импульсов соответству ющего решающего блока второй группы, выходы входных адресных ключей, выходы входных информационных ключей, выход выходного триггера, выход вход ного управляющего ключа каждого узла коммутации первого и второго коммутаторов данных соединены соответственно с первыми входами элементов И четвертой группы, с первыми входами элементов И третьей группы, с первым входом первой группы входов распре.делителя импульсов и вторьми входаt10 ми элементов И третьей и четвертой групп, вторым входом второго элемента И соответствующего решающего блока первой и второй групп, выходы ключей первой группы, выходы регистра адреса, первый и третий выходы первой группы выходов распределителя импульсов каждого блока первой и второй групп соединены соответственно с информационными входами выходных информационных ключей группы, информационными входами выходных адресных ключей группы, информационным входом выходного управляющего ключа, управляющим входом первого дешифратора соответствующего узла коммутации пегрвого и второго коммутаторов данных, выходы выходных информационных ключей каждого узла коммутации первого коммутатора данных соединены со входами входных информационных ключей узлов коммутации второго коммутатора данных, выходы выходных информационных ключей каждого узла коммутации второго коммутатора данных соединены со входами входных информационных ключей узлов коммутации первого коммутатора данных, выходы выходных адресных ключей группы, выходы выходных управляющих ключей, выходы выходных триггеров каждого узла коммутации первого коммутатора данных соединены соответственно с информационными входами входных адресных ключей группы, информационными входами входных управляющих ключей, со входами второго элемента ИЛИ узлов коммутации второго коммутатора данных, выходы выходных адресных ключей группы, выходы выходных управляющих ключей, выходы выходных триггеров каждого узла коммутации второго коммутатора данных соединены соответственно с информационными входами входных адресных ключей группы, информационными входами входных управляющих ключей, со входами второго элемента ИЛИ узлов коммутации первого коммутатора данных. 1 Изобретение относится к цифровой вычислительной технике, а именно к устройствам для обработки цифровых данных, и может быть использовано для решения дифференциальных уравнений в частных производных. Известно устройство для решения дифференциальных уравнений, содержащее решающие блоки, информационные связи, коммутаторы, информационн то шину, блок ввода-вывода, блок управления, а каждый решающий блок содержит микропроцессор, запоминающий блок, группы элементов ИЛИ tl3. Недостатком этого устройства является ограниченная пропускная способность информационной шины, которая является общей для всех решающих блоков и позволяет осуществлять загрузку и обмен между решающими блоками последовательно, что снижает общую производительность. Наиболее близким к предлагаемому является устройство, содержащее решающие блоки, каждый из которых через соответствующий коммутатор соединен двухсторонними связями с информационной шиной, устройство управления, соединенное двусторонними связями с устройством ввода-вывода с информационной шиной, а каждый ре шающий блок содержит регистры чтения и записи, ключи, узел связи, ми ропроцессор, соединенный двусторонними связями с запоминающим устройством, подключенным соответствующими входом и вькодом к входу и выходу решающего блока, соединенными коммутаторами, управляющие входы ка дого коммутатора соединены с соотве ствующими выходами устройства управ ления 2. Недостаток этого устройства низкая производительность, которая является следствием того, что, с од ной стороны, наличие общей управляющей шины для включения-выключения всех микропроцессоров обеспечивает только синхронный режим их работы, с другой - наличие общей информационной шины, которая связьшает между собой решающие блоки, приводит к не обходимости в последовательном обме не информацией между решающими блоками, в то время как микропроцессоры, ожидая окончания обмена, проста ивают. Целью изобретения является повышение производительности устройства 602 Поставленная цель достигается тем, что в устройство для решения информационных уравнений, содержащее блок управления, первую группу из К решающих блоков и первую группу из К коммутаторов управляющих сигналов, причем каждый коммутатор управляющих сигналов содержит регистр ввода, регистр вывода, группу выходных информационных ключей, группу входных информационных ключей, четыре элемента И и два дешифратора адреса, выходы регистра вывода коммутатора управляющих сигналов соединены с информационными входами выходных информационных ключей коммутатора управляющих сигналов, выходы регистра ввода коммутатора управляющих сигналов соединены с информационными входами входных информационных ключей коммутатора управляющих сигналов, выход первого элемента И коммутатора управляющих сигналов соединен с входом синхронизации регистра вывода коммутатора управляюсцих сигналов, выход второго элемента И коммутатора управляющих сигналов соединен с управляющими входами выходных информационных ключей коммутатора управляющих сигналов, выход первого дешифратора адреса коммутатора управляющих сигналов соединен с первьми входами первого и третьего элементов И коммутатора управляющих сигналов, выход третьего элемента И коммутатора управляющих сигналов соединен с управляющими входами входных информационных ключей коммутатора управляющих сигналов, выход второго дешифратора адреса коммутатора управляющих сигналов соединен с первыми входами второго и четвертого элементов И коммутатора управляющих сигналов, выход четвертого элемента И коммутатора управляющих сигналов соединен со входом синхронизации регистра ввода, решающий блок содержит регистр результата прогонки, распределитель импульсов, регистр множимого, дешифратор команд, регистр множителя, сумматор, регистр команд, счетчик команд, регистр частичного произведения, две группы ключей, шесть групп элементов И, три группы элементов ИЛИ, регистр адреса, узел памяти, элемент ШТИ, элемент НЕ, два элемента И, выход элемента НЕ решающего блока соединен с первыми входами элементов И первой и второй групп решающего блока, выход второго элемента И решающего блока соединен с первым входом элемента ИЛИ решающего блока, выходы элементов И третьей группы решающего блока соединены с первыми входами элементов РШИ пер вой группы решающего блока, выходы элементов И четвертой группы решающего- блока соединены с первыми входами элементов ИЛИ второй группы решающего блока, входы ключей перво группы решающего блока соединены с информационными выходами узла памят решающего блока, выходы ключей второй группы решающего блока соединен со вторыми входами элементов И первой группы решающего блока, выходы которых соединены со вторыми входами элементов ИЛИ первой группы решающ го блока , выходы регистра адреса решаю го блока соединены с первыми входами элементов И второй группы решающего бл ка, выходы которых соединены со вторым входами элементов ИЛИ второй группы решающего блока, первьй выход первой группы выходов распределителя импульсов решающего блока соединен со вторым входом первого элемента И решающего блока, второй выход первой группы выходов распределителя импульсов решающего блока соединен с входом чтения узла памяти решающего блока, выход первого элемента И реша ющего блока соединен со вторым входом элемента ИЛИ решающего блока, выход элемента ИЛИ решающего блока соединен со входом записи узла памяти решающего блока, выходы элементов ИЛИ первой и второй групп решающего блока соединены соответственно с информационными и адресными входам узла памяти решающего блока, первый .выход второй группы выходов распределителя импульсов решающего блока соединен с управляющими входом регистра множителя решающего блока, второй выход второй группы выходов распределителя импульсов решающего блока соединен с управляющим входом счетчика команд решающего блока, третий выход второй группы выходов распределителя импульсов решающего блока.соединен с управляющим входом регистра адреса решающего блока, четвертый выход второй группы выходов распределителя импульсов решающего блока соединен с управляющими входами ключей первой группы решающего блока, пятьй выход второй групп 0 распределителя импульсов ревыходовшающего блока соединен с первыми входами элементов И пятой группы решающего блока, тестой выход второй группы выходов распределителя импульсов решающего блока соединен с первыми входами элементов И шестой группы решающего блока, седьмой выход второй группы выходов распределителя импульсов решающего блока соединен с управляющими входами ключей второй группы решающего блока, восьмой выход второй группы выходов распределителя импульсов решающего блока соединен с управляющим входом регистра команд решающего блока, девятый выход второй группы выходов распределителя импульсов решающего блока соединен с управляющим входом регистра результата прогонки решающего блока, десятый выход второй группы выходов распределителя импульсов решающего блока соединен с управляющим входом регистра множимого решающего блока, одиннадцатый выход второй группы выходов распределителя импульсов решающего блока соединен с управляющим входом сумматора решающего блока, двенадцатый выход второй группы выходов распределителя импульсов решающего блока соединен с управляющим входом регистра частичного произведения решающего блока, первая группа входов распределителя импульсов решающего блока соединена с выходами дешифратора команд решающего блока, входы которого соединены с выходами регистра команд решающего блока, выходы регистра множителя соединены со вторыми входами элементов И пятой группы решающего блока, первая группа выходов регистра результата прогонки решающего блока соединена со вторыми входами элементов И шестой группы решающего блока, выходы элементов И пятой и шестой групп решающего блока соединены со входами элементов ИЛИ третьей группы решающего блока, выходы которых соединены с информационными входами ключей второй группы решающего блока, выходы ключей первой группы решающего блока соединены с информационными входами регистра множителя решающего блока, регистра команд решающего блока, регистра частичного произведения решающего блока первой группой информационных входов регистра множимого решаницего блока, первой группой информационных входов регистра результата прогонки решающего блока, выходы счетчика команд решающего блока соединены с входами регистра адреса решающего блока, выходы регистра частичного произведения решающего блока соединены с первой группой входов сумматора решающего блока, вторая группа входов которого соединена с выходами регистра множимого решающего блока, выходы сумматора решающего блока соединены со второй группой информационных входов регистра результата прогонки решающего блока вторая группа выходов которого соединена со второй группой информационных входов регистра множимого решающего блока, выходы выходных информационных ключей группы и- выходы входных информационных ключей группы каждого коммутатора управляющих сигналов первой группы соединены соответственно с информационными входами ключей первой группы и выходами ключей второй группы соответствующего решающего блока первой группы, входы второго дешифратора адреса, второй вход четвертого элемента И.второй вход второго элемента И и выход первого элемента И каждого коммутатсуза пе вой группы соединены соответственно с выходами регистра адреса, третьим и четвертым выходами первой группы выходов распределителя импульсов и первым входом второй группы входов распределителя импульсов соответствующего решающего блока первой группы, введены вторая группа из М решающих блоков, вторая группа из М коммутаторов управляющих сигналов, первый коммутатор данных, который содержит К узлов коммутации, и второй коммутатор данных, который содержит М узлов коммутации, каждый узел коммутации первого и второго коммутаторов данных содержит два дешифратора адреса, триггер заявок, два элемента НЕ, два элемента И, два элемента ИЛИ, группу выходных информационных ключей, группу выходных адресных ключей, выходной управляющий ключ, выходной триггер, группу входных адресных ключей, группу входных информационных ключей, входной управляющий ключ, выход первого дешйфратора адреса узла коммутации коммутатора данных соединен с синхронизирукяцим входом триггера заявок узла коммутации коммутатора данных, выход триггера заявок узла коммутации коммутатора данных соединен с первым входом первого элемента И и с первым входом первого элемента ИЛИ узла коммутации коммутатора данных, выход первого элемента ИЛИ предьщущего узла коммутации коммутатора данных соединен со входом первого элемента НЕ и со вторым входом первого элемента ИЛИ узла коммутации коммутатора данных, второй вход первого элемента ИЛИ первого узла коммутации коммутатора данных соединен с входом логического нуля устройства, выход первого элемента НЕ узла коммутации коммутатора данных соединен со вторым входом первого элемента И узла коммутации коммутатора данных, выход которого соединен с управляющими входами вьпсодных информационных ключей группы узла коммутации коммутатора данных, выходных адресных ключей группы и выходного управляющего ключа узла коммутации коммутатора данных, выход второго дешифратора адреса узла коммутации коммутатора данных соединен с первым входом второго элемента И узла коммутации коммутатора данных, выход второго элемента ИЛИ узла коммутации коммутатора данных соединен со вторым входом второго элемента И узла коммутации коммутатора данных, выход которого соединен с первым входом выходного триггера, со входом второго элемента НЕ и с управляющими входами входных адресных ключей группы, входных информационных ключей группы, входного управляющего ключа узла коммутации коммутатора данных, выход входного управляющего ключа узла коммутации коммутатора данных подключен к первому выходу записи в память узла коммутации коммутатора данньк, выход второго элемента НЕ узла коммутации коммутатора данньк соединен со вторым входом выходного триггера узла коммутации коммутатора данных, блок управления содержит узел памяти, регистр адреса, две группы ключей, группу элементов ИЛИ, две группы элементов И, регистр половинного шага, счетчик команд, регистр команд, сумматор, регистр коэффициента, дешифратор команд, регистр исходного шага, распределитель импульсов, регистр езультата суперпозиции, вьосоды ключей первой группы блока управления соединены с информационными входами узла памяти блока управления, входы ключей второй группы блока управления соединены с информационными выходами узла памяти блока управления первый выход первой группы выходов распределителя импульсов блока управления соединен с входом записи узла памяти блока управления, второй выход первой группы выходов распределителя импульсов блока управления соединен с входом чтения узла памяти блока управления, выходы регистра адреса блока управления соединены с адресными входами узла памяти блока управления, первый выход второй группы выходов распределителя импульсов блока управления соединен с управляющим входом регистра коэффи циента блока управления, второй выход второй группы выходов распределителя импульсов блока управления соединен с управляющим входом счетчи ка команд блока управления, третий выход второй группы выходов распределителя импульсов блока управления соединен с управляющим входом регистра адреса блока управления, четвертый выход второй группы выходов распределителя импульсов блока управления соединен с управляющими входами ключей первой группы блока управления, пятый выход второй группы выходов распределителя импульсов блока управления соединен с первыми входами злементов И первой группы блока управления, шестой выход второй группы выходов распределителя импульсов блока управления соединен с первыми входами элементов И второй группы блока управления, седьмой выход второй группы выходов распределителя импульсов блока управления соединен с управляющими входами ключей второй группы блока управления, восьмой выход второй группы выходов распределителя импульсов блока управления соединен с управляющим входом регистра команд блока управления девятый вьЬсод второй группы выходов распределителя импульсов блока управления соединен с управляющим входом регистра результата суперпозиции блока управления, десятый выход второй группы выходов распределителя. импульсов блока управления соединен с управляющим входом регистра исходного шага блока управления. одиннадцать выход второй-группы выходов распределителя импульсов бло ка управления соединен с управляющим входом сумматора блока управления, двенадцатый выход второй группы выходов распределит€ ля импульсов блока управления соединен с управляющим входом регистра половинного шага блока управления, первая группа входов распределителя импульсов блока управления соединена с выходами дешифратора команд блока управления, входы которого соединены с выходами регистра команд блока управления, выходы ключей второй группы блока управления соединены с информационнымч входами регистра коэффициента блока управления, регистра команд блока управления, регистра половинного шага блока управления, первыми группами информационных входов регистра исходного шага блока управления и регистра результата суперпозиции блока управления, информационные входы ключей первой группы блока управления соединены с выходами элементов ИЛИ группы блока управления, первые входы которых соединены с выходами элементов И первой группы блока управления, вторые входы элементов ИЛИ группы блока управления соединены с выходами злементов И второй группы блока управления, вторые входы элементов И первой группы блока управления соединены с выходами регистра коэффициента блока управления, вторые входы злементов И второй группы блока управления соединены с первой группой выходов регистра результата суперпозиции блока управления, выходы счетчика команд блока управления соединены с информационными входами регистра адреса блока управления, выходы регистра половинного шага блока управления соединены с первой группой входов сумматора блока управления, вторая группа входов которого соединена с выходами регистра половинного щага блока управления, выходы сумматора блока управления соединены со второй группой информационных входов регистра результата суперпозиции блока управления, вторая группа выходов которого соединена со второй группой информационных входов регистра исходного шага блока управления, выходы ключей первой группы блока управления соединены с информационными входами регистра вывода коммутаторов jrnpasляющих сигналов первой и второй групп, выходы входных информационных ключей коммутаторов управляющих сигналов первой и второй групп соединены с информационными входами ключей второй группы блока управле1 ия, третий выход первой группы выходов распределителя импульсов которого соединены со вторыми входами первых элементов И коммутаторов управляющих сигналов первой и второй групп, четвертый выход первой группы выходов распределителя импульсов соединен со вторыми входами третьих элементов И коммутаторов управляющих сигналов первой и второй групп, выходы четвер тых элементов И которых подключены ко второй группе входов распределите ля импульсов блока управления, выходы регистра адреса которого соединены со входами первого дешифратора адреса коммутаторов управляющих сигналов первой и второй групп, выходы выходных информационных ключей группы и входы регистров ввода каждого коммутатора управляющих сигналов второй группы соединены с информационными входами ключей первой групп и выходами ключей второй группы соответствующего решающего блока второй группы, входы второго дешифратора адреса, второй вход четвертого элемента И, второй вход второго элемента И и выход первого элемента И каждого коммутатора управляющих сигналов второй группы соединены соответственно с выходами регистра адреса, третьим и четвертым выходами первой группы выходов распределителя импульсов и вторым входом второй группы входов распределителя импульсов соответствующего решающего блока второй группы, выходы входных адресных ключей, выходы входных информационных ключей, выход выходного триггера, выход входного управляющего ключа каждого узла коммутации первого и второго коммутаторов данных соединены соответственно с первыми входами элементов И четвертой группы, с первыми входами элементов И третьей группы, с первым входом первой группы входов распределителя импульсов и вторыми входами элементов И третьей и четвертой групп, вторым входом второго элемента И соответствующего решающего блока перВОЙ и второй групп, выходы ключей первой группы, выходы регистра адреса, первый и третий выходы первой группы выходов распределителя импульсов каждого решающего блока первой и второй групп соединены соответственно с информационными входами выходных информационных ключей группы, информационными входами выходных адресных ключей группы, информационным входом выходного управляющего ключа, управляющим входом первого дешифратора соответствующего узла коммутации первого и второго коммутаторов данных, выходы выходных информационных ключей каждого узла коммутации первого коммутатора данных соединены со входами входных информационных ключей узлов коммутации второго коммутатора данных, выходы выходных информационных ключей каждого узла коммутации второго коммутатора данных соединены со входами входных информационных ключей узлов коммутации первого коммутатора данных, выходы выходных адресных ключей группы, выходы выходных управляющих ключей, выходы выходных триггеров каждого узла коммутации первого коммутатора данных соединены соответственно с информационными входами входных адресных ключей группы, информационными входами входных управляющих ключей, со входами второго элемента ИЛИ узлов коммутации второго коммутатора данных, выходы выходных адресных ключей группы, выходы выходных управляющих ключей, выходы выходных триггеров каждого узла коммутации второго коммутатора данных соединены соответственно с информационными входами входных адресных ключей группы, информационными входами входных управляющих ключей, со входами второго элемента ИЛИ узлов коммутации первого коммутатора данных. На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг. 2 - конкретная реализация узла коммутации; на фиг. 3 - конкретная реализация решающего блока; на фиг. 4 - конкретная реализация блока управления; на фиг. 5 - конкретная реализация коммутатора управляющих сигналов; на фиг. 6 - временная диаграмма работы устройства; на фиг. 7 - конкретная реализация буфера ввода-вывода-,; на фиг. 8 алгоритм работы решающего блока; на фиг. 9 - алгоритм расчета суперпозиции блоком управления. Устройство (фиг. 1) содержит бло 1 ввода-вывода, блок управления 2, коммУтаторы 3 -Зд, управляющих сигна лов, решающие блоки , коммутаторы . данных, каждый из которы содержит соответственно узлы коммутации 6,.-6 ..и 6 ,. Кроме того, устройство содержит выходные информационные шины 7, входные информаци онные шины 8, выходные управляющие шины 9, входные управляющие шины , адресные шины 11. Каждый решающий блок 4 содержит первую группу информационных входов 12, . вход запроса 13, группу информационных выходов 14, группу адресных выходов 15, выход записи, выход чтения, вькод записи в память 16, каждый узел 6 содержит первую групп адресных входов 17, первую группу выходов 18, выход захвата и первый выход записи в память 19. Каждый ре тающий блок 4 содержит группу адрес ных входов 20, вторую группу информационных входов 21, вход захвата и вход записи в память 22. Каждый узел 6 содержит первую группу входов 23., первую группу адресных вход 24, первый вход записи в память и вход записи 25, вторую группу инфор мационных выходов 26, вторую группу адресных выходов 27, второй выход записи в память 28, вторую группу входов 29, вторую группу адресных в дов 30, второй вход записи в память 31, выход запроса 32, входы запроса , приоритетный выход 34, при оритетный вход 35, вход логического нуля 36 устройства. Узел коммутации 6 коммутатора 5 данных (фиг. 2) содержит первый дешифратор 37 адреса, триггер 38 заявок, первый элемент НЕ 39, первый элемент И 40, первый элемент ИЛИ 41 группу выходных информационных ключей 42, группу выходных адресных ключей 43, выходной управляющий клю 44, второй дешифратор 45 адреса, второй элемент ИЛИ 46, второй элемент И 47, второй элемент НЕ 48, вы ходной триггер 49, группу входных адресных ключей 50, группу входных информационных ключей 51, входной управляющий ключ 52. Решающий блок (фиг. 3) содержит регистр результата прогонки 53, распределитель 54 импульсов, регистр множимого 55, де шифратор 56 команд, регистр множителя 57, сумматор 58, регистр 59 команд, счетчик 60 команд, регистр 61 частичного произведения, буфер 62 ввода-вывода, регистр 63 адреса, узел 64 памяти, элемент ИЛИ 65i, группы элементов ИЛИ 65, 65, элемент НЕ 66, элементы И 67- , 6 , группы элементов И 67,-67/. Блок управления 2 (фиг. 4) содержит узел 68 памяти, регистр 69 адреса, буфер 70 ввода-вьшода, регистр 71 половинного шага, счетчик 72 команд, регистр 73 команд, сумматор 74, регистр 75 коэффициента, дешифратор 76 команд, регистр 77 исходного шага, распределитель 78 импульсов, регистр 79 результата суперпозиции. Коммутатор 3 управляющих сигналов (фиг. 5) содержит регистр 80 вывода, группу выходных информационных ключей 81, первый дешифратор 82 адреса, первый элемент И 83, второй элемент И 84, группу входных информационных ключей 85, регистр 86 ввода, третий элемент И 87, четвертый элемент И 88, второй дешифратор 89 адреса. Буферы 62, 70 имеют структуру, представленную на фиг. 7, они содержат две группы элементов И 90, 91, группу элементов ИЛИ 92, две группы ключей 93,94. Устройство работает следующим образом. В исходном состоянии устройство подготовлено к работе, т.е. в узле 68 памяти блока управления 2 записаны через блок 1 управляющие программы, массивы коэффициентов, начальные и граничные условия, а в узлах 64 rfaмяти решающих блоков 4.-4 записаны управляющие программы. Рассмотрим работу устройства на примере двумерного уравнения параболического типа 01 заданного в единичном квадрате (, ), аппроксимируемого етодом конечных разностей с использованием локальноодномерных схем , t.e i,g f,g i,g 1-tt „ Т г - у2 Исходную сеточную область W, ра вивают на подобласти размерностью (|;х |), где Н , (f,1). На образовавшихся дополнительны границах, расположенных на рассто янии Н друг от друга, определяют условия сопряжения путем реализаци следующих этапов: решение одномерной задачи (2) с шагом Н U (например методом прогонки) в решающих блоках ., результате получают U , решение одномерной задачи (2) с шагом (например, методом про гонки) в решающих блоках ., в ,ч J 112 результате получают vJ о , Расчет суперпозицииполученных решений в блоке управления 2 по формуле .,j+W.4.,.jH/2 1,. i.n -ъ,г :ь i.e решение на дополнительных грани цах одномерной задачи (3) с шагом У AI (нипример, методом прогонки) в решающих блоках в резул тате получают U Решение задачи в подобластях осуществляется во второй группе ре шающих блоков ( например, (Методом прогонки. Формулы метода прогонки следующ t+l l-oC;Ol fii. . ( u.e ,. Для реализации описанного алгоритма блок управления 2 вьфабатывает по шинам 11,7,9 соответственно адрес, данные и сигнал ЗП УВВ. В ко мутаторе 3 управляющих сигналов, к которому адресуется блок управления 2, срабатьгоает дешифратор 82 адреса (фиг. 5), с выхода которого активный сигнал совместно с активным сиг налом ЗП УБВ поступают на входы эле мента И 83. По сигналу с выхода эле мента И 83 передаваемая информация тин 7 записывается в регистр 80 и одновременно через выход запроса коммутатора 3 сигнал запроса поступает в распределитель 54 импульсов решающего блока 4. По сигналу Запрос решающий блок 4 переходит на подпрограмму чтения информации из регистра ВО вывода. Для этого решающий блок 4 выставляет на адресных выходах адрес коммутатора 3. , который поступает на вход дешифратора 89 адреса, а по шине ЧТ УВВ - активный сигнал. По совокупности активных сигналов на входе элемента И 84 выходные ключи 81 подключают выходы регистра 80 к входам 12 решающего блока 4 и информация записывается через буфер 62 вводавывода в регистр результата прогонки 53, а затем запоминается в узле 64 памяти (фиг. 3). По командам блока управления 2 исходная информация (коэффициенты, значения, граничные условия) загружается в первый решающий блок 4 и последней командой передаваемого массива запускает решающий блок 4 на выполнение программы по решению одномерной задачи с шагом Н (методом прогонки). Для этого в решающий блок 4 передается код, соответствующий передаче управления, и адрес перехода (подробно алгоритм работы решающего блока 4 приведен на фиг. 8). Затем блок управления 2 переключается через коммутатор З управляющих сигналов ко второму решающему блоку 4, загружает исходной информацией узел 64 памяти и передает управление решающему блоку 4,, который начинает выполнять собственную программу, а в это время блок управления 2 переключается к следующему блоку 4, таким образом, все К/2 решающих блоков 4 со смещением во времени вьтолняют программы по определению условий сопряжения на этапе решения одномерной задачи с шагом Н. На фиг. 6 показана диаграмма занятости ресурсов предлагемого устройства для двумерной задачи, причем сначала показан этап вычисления поля на J-M временном слое с последующей привязкой этапов j+l-ro временного слоя. После того, как вьшолнено вычисление в любом из решающих локов 4 и определено значение поля с шагом Н, решающий блок 4 сообщает об этом блоку управления 2. Для этого реша|Ющий блок 4 выставляет на выходе 15 адрес коммутатора 3 управляющих сиг налов на выходе 14 - данные для перед чи в блок 2, а на выходе 16 активный сигнал ЗП УВВ. По совокупности этих сигналов коммутатор 3 уп равляющих сигналов (фиг. 5) принима ет информацию в регистр 86 и далее управляющим сигналом Запрос по ши не 10 передает управление блоку 2, который переходит на подпрограмму чтения, включающую выдачу по шинам 11 адреса коммутатора 3, которьш поступает на вход дешифратора 82 адреса, и управляющего сигнала ЧТ У на шине 9. По активному сигналу с выхода элемента И 87 информация с регистра 86 через ключи 85 поступае по информационным шинам 8 через буфер ввода вывода (фиг. 4) в регистр 79 блока 2, а затем записывается в узел 68 памяти. Далее таким же образом принимают ся остальные слова полученного масс ва из блока 4 в блок 2. Аналогично после завершения вычислений каждый из К/2 решающих блоков 4 последовательно передает в блок 2 полученные массивы данных (фиг. 6). Параллельно с работой К/2 решающих блоков 4 в группе решающих блоков осуществляется расчет поля для предьщущего временного сло (по алгоритму, представленному на фиг. 8), После того, как получена информа ция при расчете поля в решающих блоках i(4i M которая на следующем временном шаге используется для расчета условий сопряжения с шагом Н/2, осуществляется последовательная передача вычислительных значений поля через узлы коммутатора 5- данных в решаюш ие бл рси . Передав информацию, решающие блоки |.+.д, продолжают выГголнение программы по вычислению поля (фиг. 6). Рассмотрим более подробно цикл п редачи информации, например, из бло ка 4„ в блок 4-,. Решающий блок 4 адресуется к триггеру 38 заявок как к внешнему устройству и устанавливает запрос |На передачу в триггере 38(фиг.2), с выхода которого запрос поступает в узел приоритетов (элементы 39, 40 41). Если есть запросы от других ре шающих блоков ,. то в ветствии с приоритетом только ном узле 6 коммутатора 5„.данных выходе элемента 40 формируется активный сигнал. Пусть приоритет блока 4j вьште остальных в данной группе. Тогда на выходе элемента 40 формируется активный сигнал Запрос, который через выход 32 узла поступает ко всем узлам .. Затем решающий блок 4. формирует на выходах 15 адрес поля памяти уела 64 решающего блока 4 , на выходах передаваемые данные, а на выходе 16 управляющий сигнал ЗПП. Эта информация через входы 24, 23, 25 узла 6, входные ключи 43,42,44 и выходы 27, 26,28 узла 6., поступает соответственМ6,-6. но на выходы 30, 29, 31 узлов Только в узле 6 срабатывает дешифратор 45 адреса. По совкупности активных сигналов с выхода дешифратора 45 адреса и с выхода элемента ИЛИ 46 срабатывает элемент И 47, выходной сигнал которого устанавливает триггер 49 в единицу. Триггер 49 формирует управляющий сигнал Захват, который через выход 19 узла 6 поступает на вход 22 блока А и переводит в третье состояние информационные, адресные и управляющие выходные буферы блока 4, а адрес, информация и управляющий сигнал ЗПП соответственно через входы 30, 29, 31 узла 6, входные ключи 50, 51, 52, выходы 17, 18, 19 узла 6j поступают на входы 20-22 решающего блока 4. Таким образом, происходит передача данных под управление решающего блока 4 в узел 64 памяти блока 4 . Для блока 4 поле памяти разбито на к+1 областей, причем одна область находится в собственном блоке 4, а остальные К областей распределены в блоках 4 -4 . По окончании цикла передачи сбрасывается триггер 38 заявок и соответственно переводится в исходное состояние буфер решающего блока 4. Получив информацию с предыдущего временного слоя, решающие блоки -.. приступают к выполнению программ по расчету одномерной задачи с шагом Н/2. Полученные результаты решающие блоки последовательно через коммутаторы управляющих сигналов передают в блок 2, где происходит вычисление суперпозиции полученных решений с шагом Н и Н/2

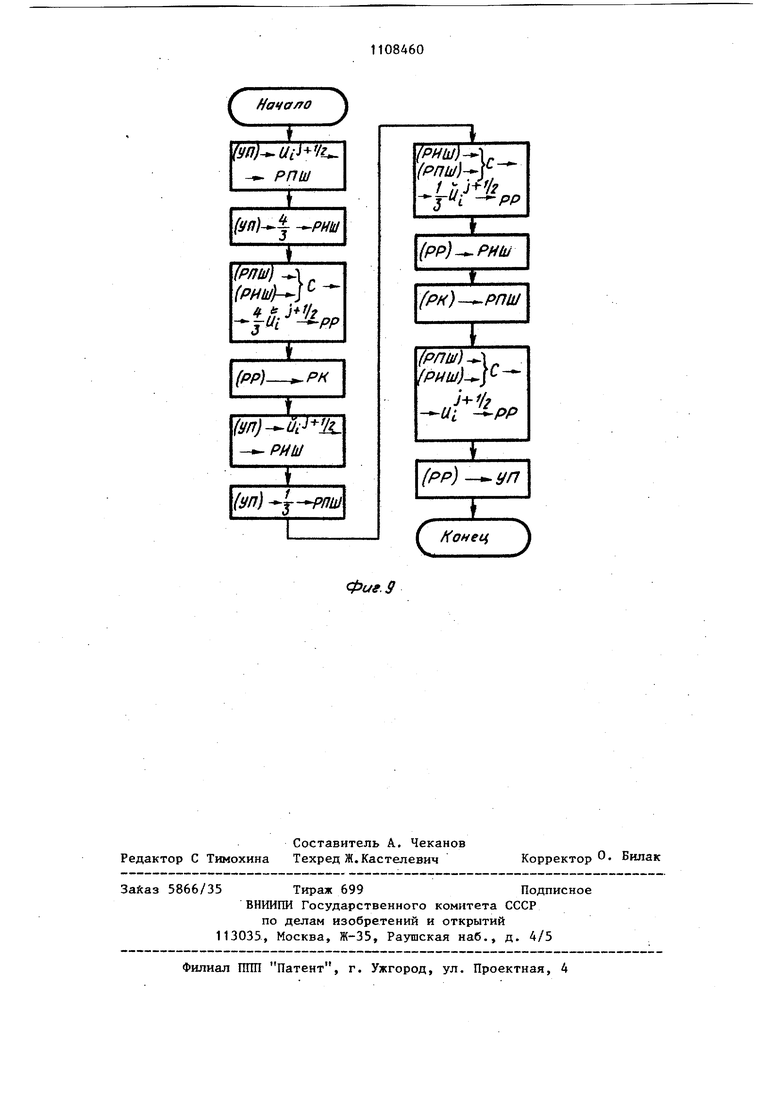

(подробный алгоритм приведен на фиг. 9). Результат вычисления загру|Жается в блоки передается управление на выполнение по расчету одномерной задачи с шагомЬ на дополнительных границах, а к этому времени заканчивается расчет поля в группе решающих блоков результаты передаются в блок управления 2. Блок управления 2 приступает к вьтоду промежуточных значений на внешнее устройство (накопитель или регистратор).

Результат расчета с шагом h из блока через узлы и

узлы последовательно передаются в освободившиеся к зтому времени блоки 4 -4д,, где осуществляется расчет поля. Блоки 1 fj приступают к программе расчета с шагом Н для следующего временного слоя.

Описанная последовательность повторяется до тех пор, пока не закончится время моделируемого процесса.

Таким образом, введение новых функциональных блоков и связей позволяет повысить производительность устройства за счет распараллеливания вычислительного процесса в решающих блоках 1 и 4-|-4дц. 789 fOft fOfx} /OfM)

I///

/

V f f

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения дифференциальных уравнений | 1982 |

|

SU1104513A1 |

| Устройство для решения дифференциальных уравнений | 1982 |

|

SU1134949A1 |

| Устройство для управления многоканальной измерительной системой | 1983 |

|

SU1149255A1 |

| Устройство для решения дифференциальных уравнений | 1983 |

|

SU1233148A1 |

| Контурная система программного управления | 1989 |

|

SU1681298A1 |

| Устройство для решения нелинейных краевых задач | 1987 |

|

SU1683028A1 |

| Устройство для решения дифференциальных уравнений | 1985 |

|

SU1348854A1 |

| Устройство для контроля высоковольтного тиристорного вентиля | 1983 |

|

SU1153374A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

УСТРОЙСТВО ДЛЯ РЕШЕНИЯ дафФЕРЕНЦИАПЬНЫХ УРАВНЕНИЙ, содержащее блок управления, первую группу из К решающих блоков и первую группу из ft коммутаторов управляющих сигналов, причем каждый коммутатор управляющих сигналов содержит регистр ввода, регистр вывода, группу выходных информационньпс ключей, группу входных информационных ключей, четыре элемента И и два дешифратора ад- реса, выходы регистра вывода коммутатора управляющих сигналов соединены с информационными входами выходных информационных ключей коммутатора управляющих сигналов, выходы регистра ввода коммутатора управляющих сигналов соединены с информационными входами входных информационных ключей коммутатора управляюоцпс сигналов, выход первого элемента И коммутатора управляющих сигналов соединен с входом синхронизации регистра вьгаода коммутатора управляющих сигналов, выход второго элемента И коммутатора управляющих сигналов соединен с управляющими входами выходных информационных ключей коммутатора управлянщих сигналов, выход первого дешифратора адреса коммутатора управляющих сигналов соединен с первыми входами первого и третьего элементов И коммутатора управляющих сигналов, выход третьего элемента И коммутатора управляющих сигналов соединен с управляющими входами входных информационных ключей ко 1мутатора управляющих сигналов, выход второго дешифратора адреса коммутатора управляющих сигналов соединен с первыми входами второго и четвертого элементов И коммутатора управляющих сигналов, выход четвертого элемента И коммутатора уп(Л равляюнщх сигналов соединен со входом синхронизации регистра ввода, решающий блок содержит регистр результата прогонки, распределитель импульсов, регистр множимого, дешифратор команд, регистр множителя, сумматор, регистр команд, счетчик команд, регистр частичного произведения, две группы ключей, шесть 00 4 OR) групп элементов И, три группы элементов ИЛИ, регистр адреса, узел памяти, элемент ИЛИ, элемент НЕ, два элемента И, выход элемента НЕ решающего блока соединен с первыми входами элементов И первой и второй групп решакщего блока, выход второго элемента И решающего блока соединен с первым входом элемента ИЛИ решающего блока, выходы элементов И третьей гр5шпы решанядего блока соединены с первыми входами элементов ШШ первой группы решающего блока, выходы элементов И четвертой группы решающего блока соединены с

68

Т-у Y

J77

ff1

ЧТУВВ

3(7 УВВ

сригЛ

)

РвЧ(ч) nvff)

f

P84(k) )

iUt/f/M Вы Soda

I

omS,78

m

Фие.7

фиг. 8

Фае. 9

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Вычислительная система для решения дифференциальных уравнений | 1975 |

|

SU620980A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-15—Публикация

1982-07-07—Подача