(54) ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА ДЛЯ РЕШЕНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительная система для решения дифференциальных уравнений | 1975 |

|

SU565299A1 |

| Вычислительная система для решения дифференциальных уравнений | 1977 |

|

SU674031A1 |

| Вычислительная система для решения дифференциальных уравнений | 1978 |

|

SU771674A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 1988 |

|

SU1840538A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для решения дифференциальных уравнений | 1982 |

|

SU1134949A1 |

| Вычислительная система | 1975 |

|

SU530337A1 |

| Устройство для решения дифференциальных уравнений | 1986 |

|

SU1383391A1 |

| Устройство логической обработки | 1982 |

|

SU1124317A1 |

| Устройство для решения дифференциальных уравнений | 1983 |

|

SU1233148A1 |

Изобретение относится к вычиспительной технике и может быть применено для решения обыкновенных дифференциальных уравнений и уравнений в частнь1Х производных.

Известны аналоговые вычислительные машины (АВМ)у которые содержат группу решающих блоков, выполняющих определенные математические операклп над переменными, представленными электрическими сигналами в аналоговой форме, и соединенных между собой в соответствии с решаемой системой дифференциальных у равнений 1 . В состав решающих блоков входят интеграторы, сумматоры, масштабные устройства и нелинейные устройства.

Аналоговые машины обладают высоким быстродействием, благодаря параллельному характеру выполнения всех математических Операций, Однако они имеют ограниченную точность, требуют большого объема оборудования даже для частичной автоматизации ввода в машину исходных данных о задаче.

Известны цифровые дифференциальные анализаторы, которые содержат группу интеграторов, выполняющих определенные математические операции нет переменными, представленными в цифровой форме, и связанных между собой в соответствии с решаемой системой дифференциальных уравнений ГзТ.

Однако неэффективности формул интегрирования в этих анализаторах требуется применять малый шаг интегрирования, что снижает их быстродействие. Кроме того им свойственна трудность автоматизации ввода схемы моделирования.

Наиболее близкой по технической,сущности к изобретению является вычислительная система, содержащая решающие блоки, каждый из которых через соответствующий коммутатор соединен двухсторонними связями с информационной шиной, устройство управления соединенное двухсторонними связями с устройством ввода-вывода и с информацион-

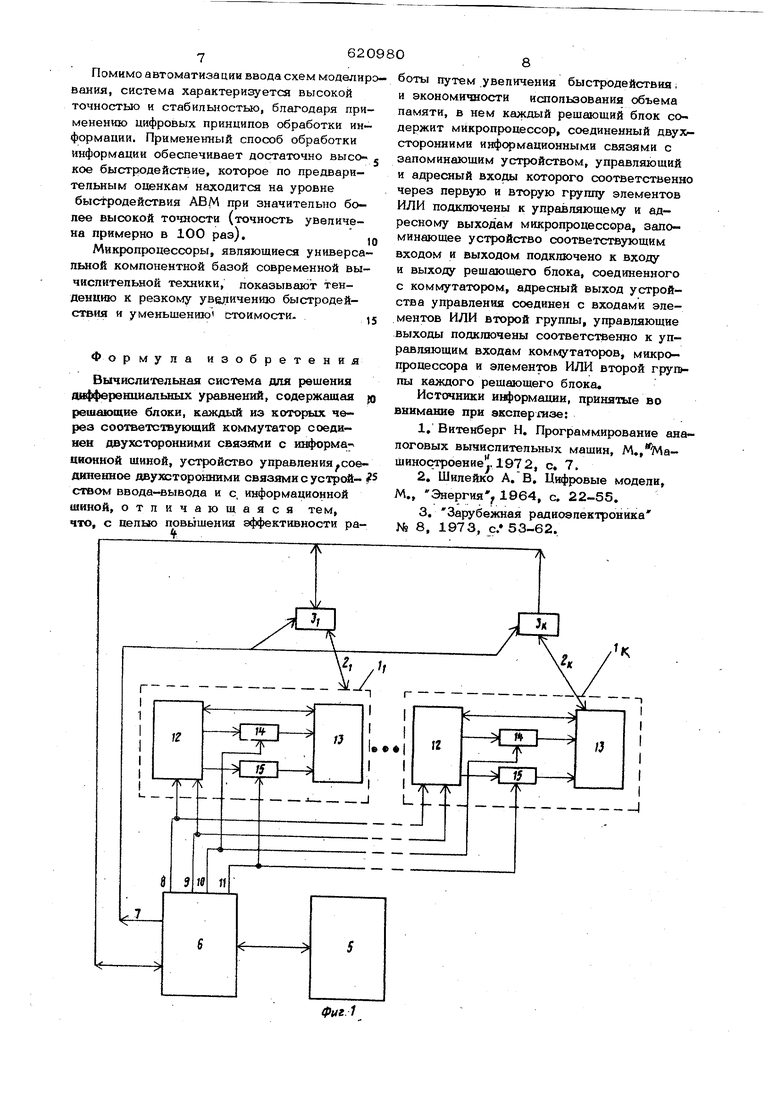

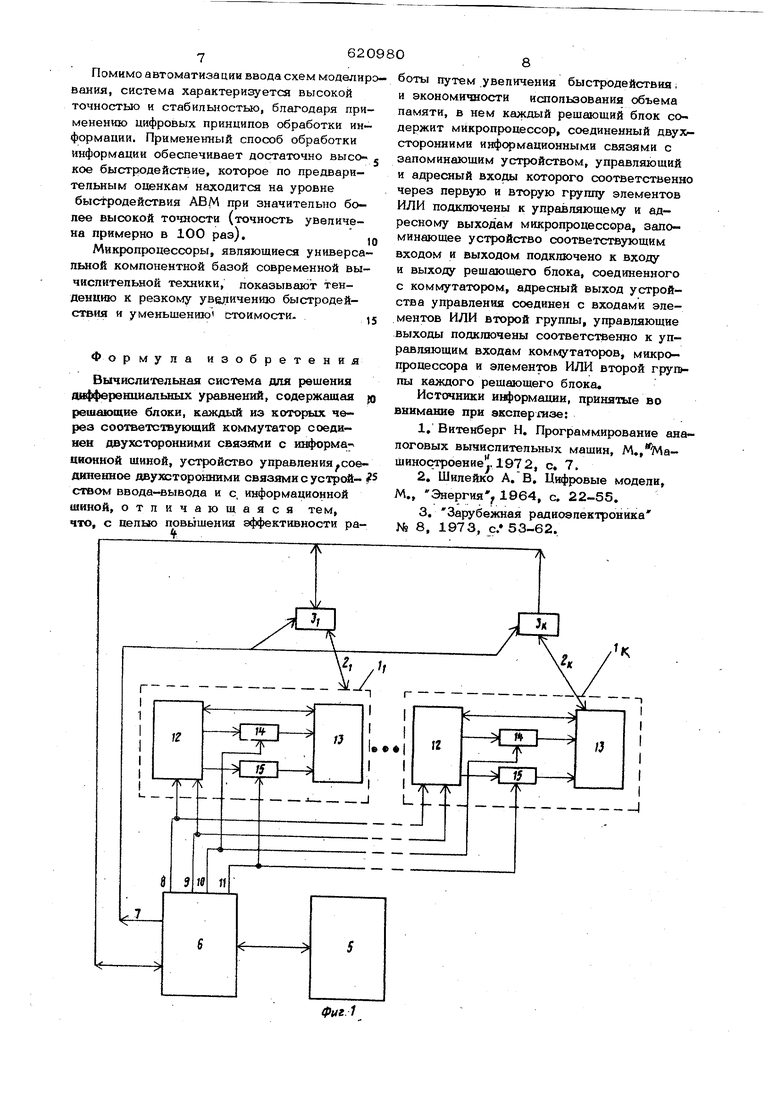

ной шиной 3. Однако трудность осуществления полного распаралпеливания процесса интегриро вания дифференциальных уравнений иэ- за необходимости применения большого количества малогабаритных электронных вычислительных машин (мини-ЭВМ) огра ничивает быстродействие системы и клас задач. Кроме этого, система оказывается громоздкой из-«а конструктивных и стру турных особенностей мини-ЭВМ и поэтому увеличение степени распараллеливания практически невозможно. Распараллеливание с использованием более 7-12 мини-ЭВМ практически нереализуемо. Кроме того, общая в указанной системе шин представляет собой сложное устройство, объединяющее а себе не только информационные, но и адресные- и управляющие шины, так как эта система предназначена для организации взаимодействия большого количества различных устройств, ад ресуемых 18-разрядными числами. При разделении задачи по уравнениям (группам) -трудно обеспечить одинаковую загрузку мини-ЭВМ, что приводит к их простоям и общей потере эффективности Программная обработка операции обмена приводит к увеличению времени, затрачиваемого на обмен, и к общему снижению быстродействия. Цепью изобретения является повышение эффективности работы путем увеличения быстродействия и экономичности использования объема памяти. Достигается это тем, что в системе кажаый решающий блок содержит микропроцессор, соединенный двухсторонними информационными связями с запоминающи устройством, управляющий и адресный входы которого соответственно ч&рез пер вую и вторую группу элементов ИЛИ под ключены к управляющему и адресному вь ходам микропроцессора, запоминающее устройство соответствующим входом и выходом подключено к входу и выходу решающего блока, соединенного с коммутатором, адресшлй выход устройства управления соединен с входами элементо ИЛИ второй группы, управляющие выходы подключены соответственно к управляющим входам коммутаторов, микропроцессора и элементов ИЛИ второй группы каждого решающего блока. Микропроцессор является элементом, предназначенным для массового производства, компактным, универсальным, посволяющим получить простую конструк цию и малые габариты. Он может программно настраиваться на выполнение про извольных математических операций и использоваться в качестве решающего бло ка при организации параллельных структур. Применение микропроцессора позволяет ввести большое количество решающих блоков, что приближает такую структуру к структуре АВМ, которая характеризуется большим быстродействием, вследствие высокой степени распараллеливания при со фаненки возможности атоматичеокого ввода схемы моделирования и ее параметров. Используемый в системе способ обмена информацией безразличен к количеству связей между блоками в отли-с чие от прототипа, что расширяет класс задач. , Обращение к запоминающему устройству при обмене информацией без программной обработки этого обращения увели, чивает скорость обмена этой ии})ормацией, т, е. увеличивает быстродействие. Этому же способствует одновременный прием информации запоминающими устройствами всех решающих блоков кроме одного, работающего на выдачу. За счет непосредственного управления запоминающим устройством по цепям управления записыо-чтением и адресным цепям от устройства управления исключается необходимость программной обработки операции обмена и достигается общеЪ величение быстродействия, В случае, когда каждый блок выдает одну выходную переменную, схема управления имеет простой вид. На фиг, 1 представлена блок-схема вычислительной системы, на фиг, 2 - блоксхема устройства у1фавления системой для случая, когда каждый решающий блок вырабатывает одну выходн Ю перс менную. Вычислительная система -предназначена для выполнения итеративных вычислений при численном интегрировании систем обыкновенных дифференциальных уравнений, которые могут быть записаны в форме задачи Коши. В каждом итеративном цикле вычисляются значения искомых переме ных для дискретных значений независимой переменной по итеративным формулам, просчет по которым может производиться параллельно, Система содержит решающие блоки информационные связи 2,-2| , каждая из которых содержит число линий по количеству /двоичных разрядов в чис ле; коммутаторы Зц , соединенные с информационной шиной 4, устройство ввода-вывода 5, устройство управления 6 с выходами 7-И; каждый решающий блок

содержит микропроцессор 12, запоминающее устройство 13, группы элементов

ИЛИ 14, 15.

Запоминающее устройство условно разделено на две части: информационное поле, одинаково устроенное во всех реша ющих блоках и содержащее выходные переменные всех рещающих блоков, н программную часть, содержащую программы работы, специфические для каждого рещающего блока..

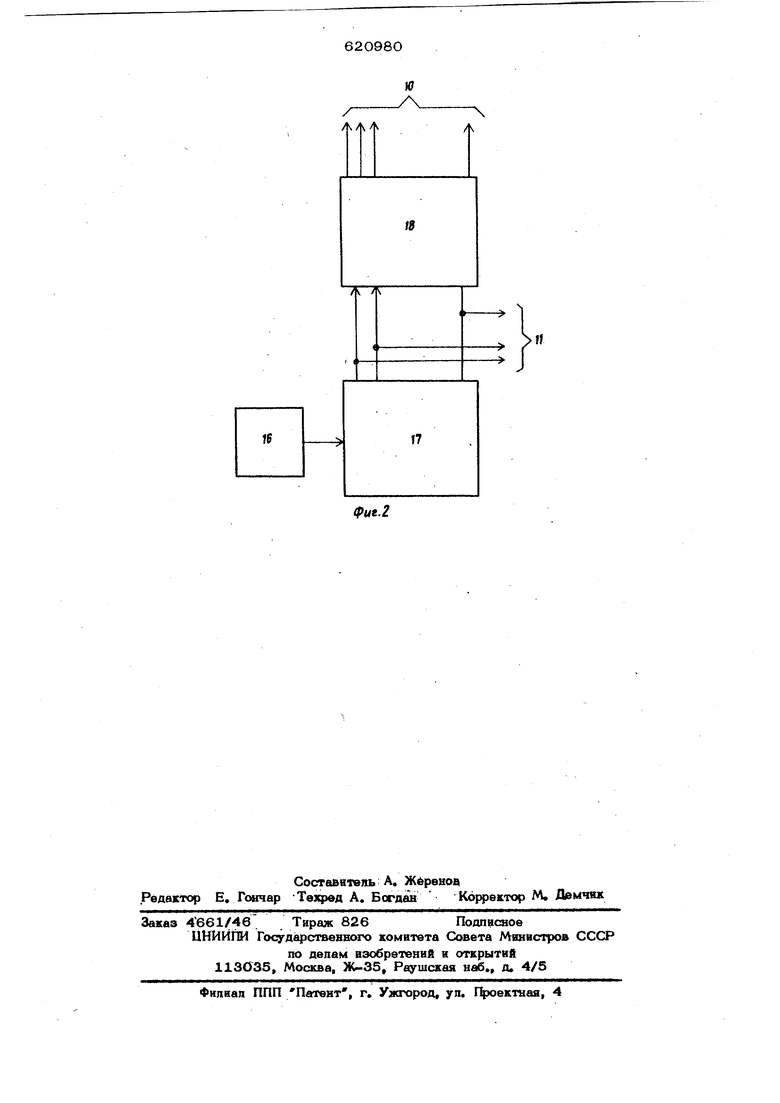

Схема управления содержит генератор тактовых импульсов 16, счетчик 17, дешифратор 18,

Микропроцессор 12 производит выборку инструкций из запоминающего устройства, их расщифровку, чтение данных из запоминающего устройства 13, выполнение инструкций и запись в запоминающее устройство результатов. Данные передают: ся по двусторонней шине 2, адрес регистра запоминающего устройства передается по щине llj сигнала чтение-запись поступает либо с выхода 10 устройства управления 6, либо от микропроцессора 12. Объединение этих сигналов проивзодится с помощью элементов ИЛИ. 14.

Адрес в запоминающее устройство 13 задеется либо с выхода 11 устройства управления 6, либо от микропроцессора 12.

Включение-выключение микропроцессора производится по сигналу, поступающему из устройства управления с выхода 8. Тактовые сигналы подаются на все микропроиессоры с выхода 9 устройства управнения.

С помоошю устройства 5 ввода-вывода информации производится загрузка рещающих блоков исходными данными и программами, а также вывод результатов в процессе решения.

Устройство управления 6 управляет работой системы в двух режимах: Подготовка и Работа. В режиме ГЬдготовка вводятся программы и заполняется информационное поле каждого решающего блока. При вводе программ последовательно включаются соответствующие коммутаторы, с выхода 11 задаются адреса инструкций, а сами инструкции - по щине 4 При загрузке информационного поля коммутаторы 3 одновременно включаются и с выхода 9 устройства управления 6 дается сипГап Запись.

В режиме Работа циклически повторяются два такта: параллельной работы решающих блоков и обмена информацией. В результате выполнения одной пары тактов производится очередной шаг

итеративного процесса и обновляется информационное попе решающих блоков. Останов всей системы производится по сигналу извне. В режиме Работа коммутаторы постоянно вкшочены.

В первом такте дается сигнал включения всех микропроцессоров (выход 8) на время, необходимое для выполнения программы одного итеративного шага в самом загруженном микропроцессоре. При этом сигналы извне (2, 1О, И) в рещающий блок не подаются. В результате работы микропроцессоров информационное поле каждого блока обновляется в той части, которая соответствует выходныь переменным каждого блока. В конце так- тавсе микропроцессоры находятся в исходном состоянии.

Во втором такте микропроцессоры и логические устройства всех решающих блоков отключены от цепей 2, 10, 11. Устройство управления 6 устанавливает на выходе 11 один за другим все адреса информационного поля, начиная с первого и кончая последним. При задании некоторого адреса дается сигнал Чтение на той блок, который в первом такте вырабатывает выходную переменную, размещенную в памяти по этому адресу. На все остальные блоки подается сигнал Запись. Сигналы Чтение и Запись подаются с выхода 10. В этом же такте производится кодкгаочение устройства 5 ввода-вывода информации в режиме вывода информации.

В случае, если каждый решающий блок вырабатывает одну выходную переменную (номер переменной при этом принимается равным номеру блока), управление обменом информацией может быть выполнено с помощью счетчика 17 (см.че фиг. 2), на вход которого подаются тактовые импульсы от генератора тактовых импульсов 16, и дещифратора 17, подключенного к счетчику. Счетчик последовательно вырабатывает адреса информационного поля, равным номеру выходной переменной. ,Одновременно дешифратор активизирует одну из линий выхода j 10, соответствующую решающему блоку, по которой подается сигнал Чтение .

Рассмотренная вычислительная система имеет те же области применения, что fi аналоговые вычислительные машины общего назначения и цифровые модели, но

выгодно от них отличается. Благодаря наличию автоматизированной настройки на схемы моделирования, она. может использоваться в составе автоматизированных вычислительных систем. 620 Помимо автоматизации ввода схем моделир вания, система характеризуется высокой точностью к стабильностью, благодаря при менению цифровых принципов обработки информации. Примененный способ обработки информации обеспечивает достаточно высокое быстродействие, которое по предварительным оценкам находится на уровне быстродействия АВМ при значительно более высокой точности (точность увеличена примерно в 100 раз). Микропроцессоры, являющиеся универса льной компонентной базой современной вычислительной техники, показывают тенденцию к резкому увеличению быстродействия и уменьшению стоимости. ла изобретения Фор м у Вычислительная система для решения (Ш| фврвнш1альных уравнений, содержащая решаюшие блоки, каждый из которых через соответстаующий коммутатор соединен двухсторонними связями с информа;; циониой шиной, устройство управления сое диненное двухсторонними связями с устройctBOM ввода-вывода и с, информационной шиной, отличающаяся тем, что, с целью повышения эффективности ра g быстродействия; боты путем увеличения и экономичности использования объема памяти, в нем каждый решающий блок содержит микропроцессор, соединенный двухсторонними информационными связями с запоминающим устройством, управляющий и адресный входы которого соответственно через первую и вторую группу элементов ИЛИ подключены к управляющему и адресному выходам микропроцессора, запоминающее устройство соответствующим входом и выходом подключено к входу и выходу решающего блока, соединенного с коммутатором, адресный выход устройства управления соединен с входами элементов ИЛИ второй группы, управляющие выходы подключены соответственно к управляющим входам коммутаторов, микропроцессора и элементов ИЛИ второй групн пы каждого решающего блока. Источники информации, принятые во внимание при экспертизе: 1,Витенберг Н. Программирование аналоговых вычислительных мащин, М.,7 4ащиностроение1.1972, с, 7. 2,Шилейко А. В, Цифровые модели, М., Энергия 1964, с, 22-55. 3,Зарубежная радиоэлектроника № 8, 1973, с/ 53-62.

/

/NA А

15

Ю

УЧ.

X

х

7

Авторы

Даты

1978-08-25—Публикация

1975-07-04—Подача