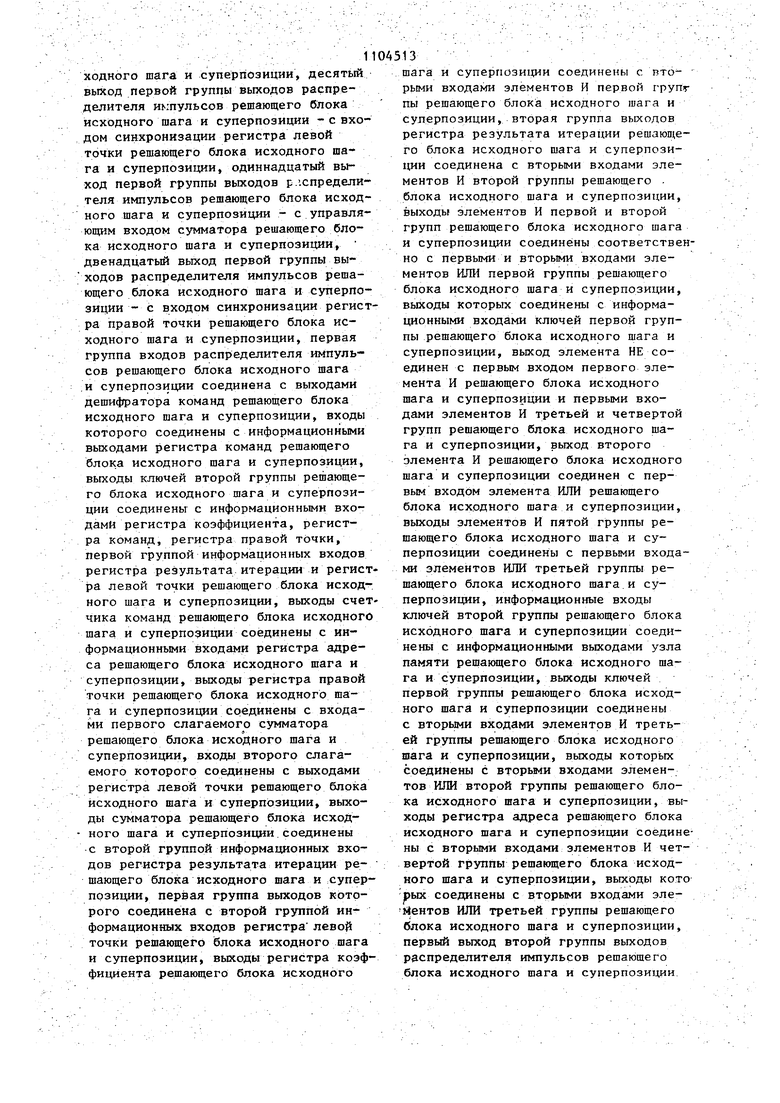

ходкого шага и суперпозиции, десятый выход первой группы выходов распределителя импульсов решающего блока исходного шага и суперпозиции - с входом синхронизации регистра левой точки решающего блока исходного шага и суперпозиции, одиннадцатый выход первой группы выходов р..спределителя импульсов решающего блока исходного шага и суперпозиции - с управляющим входом сумматора решающего блока исходного шага и суперпозиции, двенадцатый выход первой группы выходов распределителя импульсов решающего блока исходного шага и суперпозиции - с входом синхронизации регистра правой точки решанмцего блока исходного шага и суперпозиции, первая группа входов распределителя импульсов решающего блока исходного шага .и суперпозиции соединена с выходами дешифратора команд решающего блока исходного шага и суперпозиции, входы которого соединены с информационными выходами регистра команд решающего блока исходного шага и суперпозиции, выходы ключей второй группы решающего блока исходного шага и суперпозиции соединены с информационными входами регистра коэффициента, регистра команд, регистра правой точки, первой группой информационных входов регистра результата.итерации и регистра левой точки решающего блока исходного шага и суперпозиции, выходы счетчика команд решающего блока исходного шага и суперпозиции соединены с информационными входами регистра адреса решающего блока исходного шага и суперпозиции, выходы регистра правой точки решающего блока исходного шага и суперпозиции соединены с входами первого слагаемого сумматора решающего блока исходного шага и суперпозиции, входы второго слагаемого которого соединены с выходами регистра левой точки решающего блока исходного шага и суперпозиции, выходы сумматора решающего блока исходного шага и суперпозиции.соединены с второй группой информационных входов регистра результата итерации решающего блока исходного шага и :Супер- позиции, первая группа выходов которого соединена с второй группой информационных входов регистралевой точки решающего блока исходного шага и суперпозиции, выходы регистра коэффициента решающего блока исходного

шага и суперпозиции соединены с вто рыми входами элементов И первой груп пы решающего блока исходного шага и судерпозиции, вторая группа выходов регистра результата итерации решающего блока исходного шага и суперпозиции соединена с вторыми входами элементов И второй группы решающего . блока исходного шага и суперпозиции, выходы элементов И первой и второй групп решающего блока исходного шага и суперпозиции соединены соответствено с первыми и вторыми входами элементов ИЛИ первой группы решающего блока исходного шага и суперпозиции, выходы которых соединены с информационными входами ключей первой группы решающего блока исходного шага и суперпозиции, выход элемента НЕ соединен с первым входом первого элемента И решающего блока исходного шага и суперпозиции и первыми входами элементов И третьей и четвертой групп решающего блока исходного шага и суперпозиции, выход второго элемента И решающего блока исходного шага и суперпозиции соединен с первым входом элемента ИЛИ решающего блока исходного шага и суперпозиции, выходы элементов И пятой группы решающего блока исходного шага и суперпозиции соединены с первыми входами элементов ИЛИ третьей группы решающего блока исходного шага.и суперпозиции, информационные входы ключей второй группы решающего блока исходного щага и суперпозиции соединены с информационными выходами узла памяти рещакнцего блока исходного шага и суперпозиции, выходы ключей первой группы решающего блока исходного шага и суперпозиции соединены с вторыми входами элементов И третьей группы решающего блока исходного шага и суперпозиции, выходы которых соединены с вторьми входами элементов ИЛИ второй группы решающего блока исходного шага и суперпозиции, выходы регистра адреса решающего блока исходного шага и суперпозиции соединены с вторыми входами элементов и четвертой группы решающего блока исходного шага и суперпозиции, выходы кото рых соединены с вторыми входами элейентов ИЛИ третьей группы решающего блока исходного шага и суперпозиции, первый выход второй группы выходов распределителя импульсов решаюшего блока исходного шага и суперпозиции

соединен с вторым входом пер-зого элемента И решающего блока исходного шага и суперпозиции, второй выход второй группы выходов распределителя импульсов решающего блока исходного шага и суперпозиции соединен с входом чтения узла памяти решающего блока исходного шага и суперпозиции, выход первого элементам решающего блока исходного шага и суперпозиции соединен с вторьм входом элемента ИЛИ решающего блока исходного шага и суперпозиции, выходы элементов ИЛИ второй и третьей групп решающего блока исходного шага и суперпозиции соединены соответственно с информационными и адресными входами узла памяти решающего блока исходного шага и суперпозиции, выходы элементов И шестой группы соединены с первыми входами элементов ИЛИ второй группы, коммутатор управляющих сигналов содержит регистр вывода, группу выходных ключей, четыре элемента И, группу входных ключей, регистр ввода, два дешифратора адреса, выходы первого - четвертого элементов И коммутатора управляющих сигналов соединены соответственно с входом синхронизации регистра вывода, управляю1цими входами входных ключей, входом синхронизации регистра ввода и управляющими входами выходных ключей коммутатора управляющих сигналов, выходы регистра ввода коммутатора управляющих сигналов соединены с информационными входами входных ключей группы ко1 мутатора управляющих сигналов, выход первого дешифратора адреса коммутатора управляющих сигналов соединен с первыми входами третьего и четвертого элементов И коммутатора управляющих сигналов, выходы регистра вывода коммутатора управляющих сигналов подключены к информационным входам выходных ключей группы коммутатора управляющих сигналов, выход второго дешифратора адреса коммутатора управляющих сигналов соединен с первьми входами первого и второго элементов И коммутатора управляющих сигналов, выходы выходных ключей группы, информационные входы регистра ввода, входы первого дешифратора адреса, второй вход четвертого элемента И, второй вход третьего элемента И, выход первого элемента И каждого коммутатора управляющих сигналов первой группы соединены соответственно с информационными входам

ключей второй группы, выходами ключей первой группы, выходами регистра адреса, третьим выходом второй группы выходов распределителя импульсов, четвертым выходом второй группы выходов распределителя импульсов и первым входом второй группы входов распределителя импульсов соответствующего решающего блока исходного шага и суперпозиции, отличающеес я тем, что, с целью повышения производительности, в него введены N+1 решающих блоков половинного шага, вторая группа из N+1 коммутаторов управляющих сигналов, N блоков подготовки суперпозиции, третья группа из N коммутаторов управляющих сигналов, два блока местного управления и коммутатор данных, который содержит N узлов коммутации, причем решающий . блок половинного шага содержит регистр результата итерации, распределитель импульсов, регистр коэффициента, сумматор, регистр команд, регистр левой точки, дешифратор команд, счетчик команд, регистр правой точки, две группы ключей, две группы элементов И, группу элементов ИЛИ, регистр адреса, узел памяти, причем в каждом решающем блоке половинного шага первый выход первой группы выходов распределителя импульсов соединен с входом синхронизации регистра коэффициента решающего блока половинного шага, второй выход первой группы выходов распределителя импульсов решающего блока половинного шага - со счетным входом счетчика команд решающего блока половинного шага, третий выход первой группы выходов распределителя импульсов решающего блока половинного шага с входом синхронизации регистра адреса решающего блока половинного шага, четвертый выход первой группы выходов распределителя импульсов решающего блока половинного шага-с управляющи- . ми входами ключей первой группы решающего блока половинного шага, пятый выход первой группы выходов распределителя импульсов решающего блока половинного шага - с первыми входами элементов И первой группы решающего блока половинного шага, шестой выход первой группы выходов распределителя импульсов решающего блока половинного шаяа - с первьми входами элементов И второй группы решающего блока половинного шага, седьмой выход первой группы выходов распределителя импульсов

решающего блока половинного шага с управляющими входами ключей второй группы решающего блока половинногошага, восьмой выход первой группы вы ходов распределителя импульсов решающего блока половинного шага - с вхо дом синхронизации регистра команд решающего блока половинного шага, девятый выход первой группы выходов распределителя импульсов решающего блока половинного шага - с входом синхронизации регистра результата итерации решающего блока половинного шага, десятый выход первой группы вы ходов распределителя импульсов решающего блока половинного шага - с вхо дом синхронизации регистра левой точки решающего блока половинного шага, одиннадцатый выход первой груп пы выходов распределителя импульсов решающего блока половинного шага с управляющим входом сумматора решающего блока половинного шага, двенад цатый; выход первой группы выходов распределителя импульсов решающего блока половинного шага - с входом синхронизации регистра правой точки решающего блока половинного шага, первая группа входов распределителя импульсов решающе.го блока половинного шага соединена с выходами дешифратора команд решающего блока половинного шага, входы которого соединены с выходами регистра команд решающего блока половинного шага, выходы ключей второй группы решающего блока половинного шага соединены с информа ционными входами регистра коэффициента, регистра команд, регистра правой точки, первыми группами информационных входов регистра результата итерации и регистра левой точки решающего блока половинного шага, выходы счетчика команд решающего блока половинного шага соединены с информационными входами регистра адреса решающего блока половинного шага, выходы регистра правой точки решающего блока половинного шага соединены с входами правого слагаемого сумматора решающего блока половинного шага, входы второго слагаемого которого соединены с информационными выходами регистра левой точки решающего блока половинного шага, выходь| сумматора решающего блока половинйого шага соединены с второй группой информационных входов регистра итерации решающего блока половинного

4513

шага, первая группа выходов которого соединена с второй группой информационных входов регистра левой точки решающего блока половинного шага, выходы регистра коэффициента решающего блока половинного ша.га соединены с вторыми входами элементов И первой группы решающего блока половинного шага, вторая группа выходов регистра результата итерации решающего блока половинного шага соединена с вторыми входами элементов.И второй группы решающего блока половинного шага, выходы элементов И первой и второй групп решающего блока половинного шага соединены соответственно с первыми и вторыми входами группы элементов ИЛИ, выходы которых соединены с информационными входами ключей первой группы решающего блока половинного шага, первый выход второй группы выходов распределителя импульсов решающего блока половинного шага соединен с входом записи узла памяти решающего блока половинного шага, второй выход второй группы выходов распределителя импульсов решающего блока половинного шага соединен с входом чтения узла памяти решающего блока половинного шага, информационные входы ключей второй группы решающего блока половинного шага соединены с выходами узла памяти решающего блока половинного шага, выходы ключей первой гРУПпы решающего блока половинного шага соединены с информационными входами узла памяти .решающего блока половинного тага, выходы регистра адреса соединены с адресными входами узла памяти решающего блока половинного шага, решающий блок подготовки суперпозиции содержит регистр результата итерации, распределитель импульсов, регистр левой точки, дешифратор команд, регистр коэффициента, сумматор, регистр команд, счетчик команд, регистр правой точки, две группы ключей, две группы элементов И, группу элементов ИЛИ, регистр адреса, узел памяти, причем в блоке подготовки суперпозиции первьй выход первой группы выходов распределителя импульсов блока подготовки суперпозиции соединен с входом синхронизации регистра коэффициента блока подготовки суперпозиции, второй выход первой группы выходов распределителя импульсов блока подготовки суперпозиции - со счетным входом счетчика команд блока подготовки суперпозиции, третий выход первой группы выходов распределителя импульсов блока подготовки суперпозиции с входом синхронизации регистра адреса блока подготовки суперпозиции, четвертый выход первой группы выходов распределителя импульсов блока подготовки суперпозиции - с управляющими входами ключей первой группы блока подготовки суперпозиции, пятый выход первой группы выходов распределителя импульсов блока подготовки суперпозиции - с первыми входами элементов И первой группы блока подготовки суперпозиции, шестой выход первой группы выходов распределителя импульсов блока подготовки суперпозиции - с первыми входами элементов И второй группы блока подготовки суперпозиции, седьмой выход первой группы выходов распределителя импульсов блока подготовки суперпозиции - с управляющими входами ключей второй группы блока подготовки суперпозиции, восьмой выход первой группы выходов распределителя импульсов блока подготовки суперпозиции - с входом синхронизации регистра команд блока подготовки суперпозиции, девятый выход первой группы выходов распределителя импульсов блока подготовки суперпозиции - с входом синхронизации регистра резултата итерации блока подготовки суперпозиции, десятый выход первой группы выходов распределителя импульсов блока подготовки суперпозиции - с входом синхронизации регистра левой . точки блока подготовки суперпозиции, одиннадцатый выход первой группы выходов распределителя импульсов блока подготовки суперпозиции - с управляющим входом сумматора блока подготовки суперпозиции, двенадцатый выход первой группы выходов распределителя импульсов блока подготовки суперпозиции - с входом синхронизации регистра правой точки блока подготовки суперпозиции, первая группа входов . распределителя импульсов блока подготовки суперпозиции соединена с выходами дешифратора команд блока подготовки суперпозиции, входы которого соединены с выходами регистра команд блока подготовки суперпозиции, выходы ключей второй группы блока подготовки суперпозиции соединены с информационными входами регистра коэффициента блока подготовки суперпозиции, регистра команд, регистра правой точки, первой группой информационных входов регистра результата итерации и регистра левой точки блока подготовки суперпозиции, выходы счетчика команд блока подготовки суперпозиции соединены с информационными входами регистра адреса блока

подготовки суперпозиции, выходы регистра правой точки блока подготовки суперпозиции соединены с входами первого слагаемого сумматора блока подготовки суперпозиции, входы второго слагаемого которого соединены

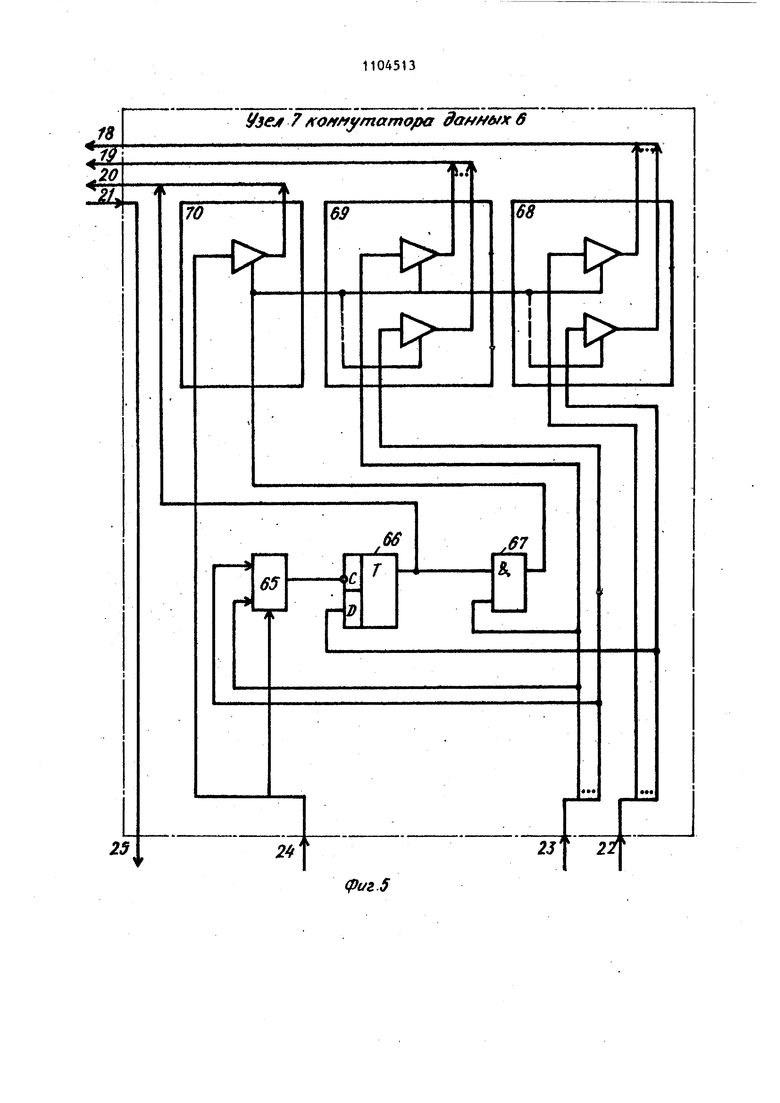

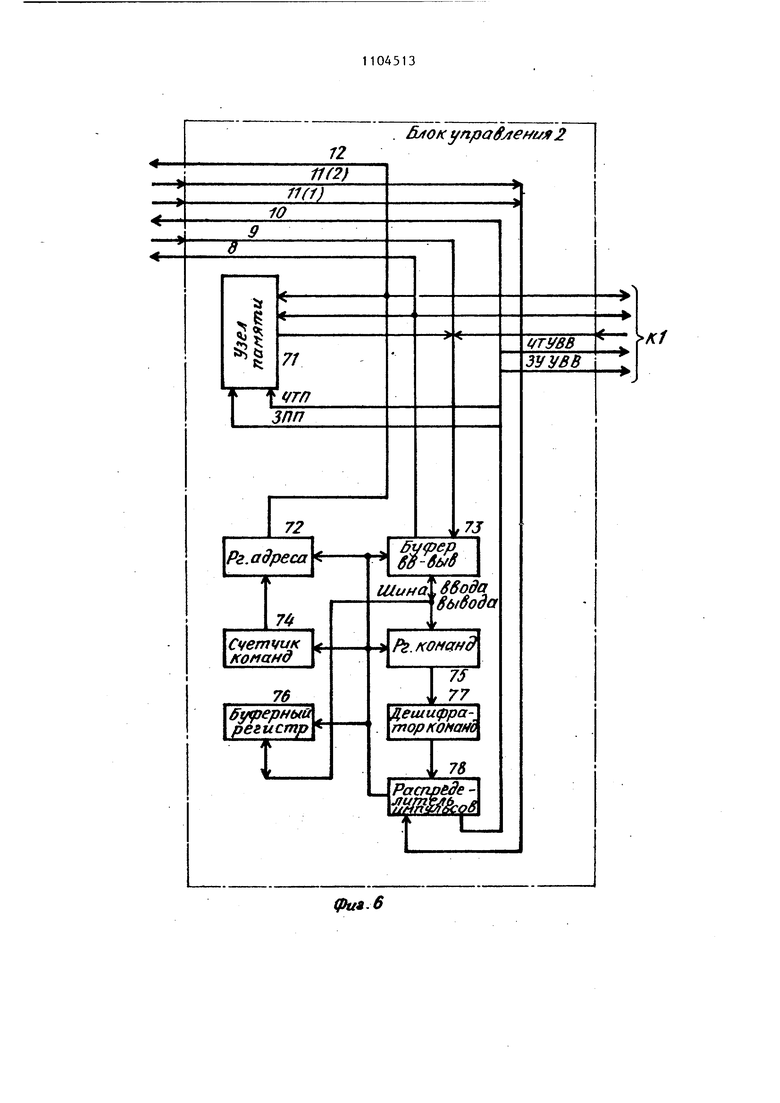

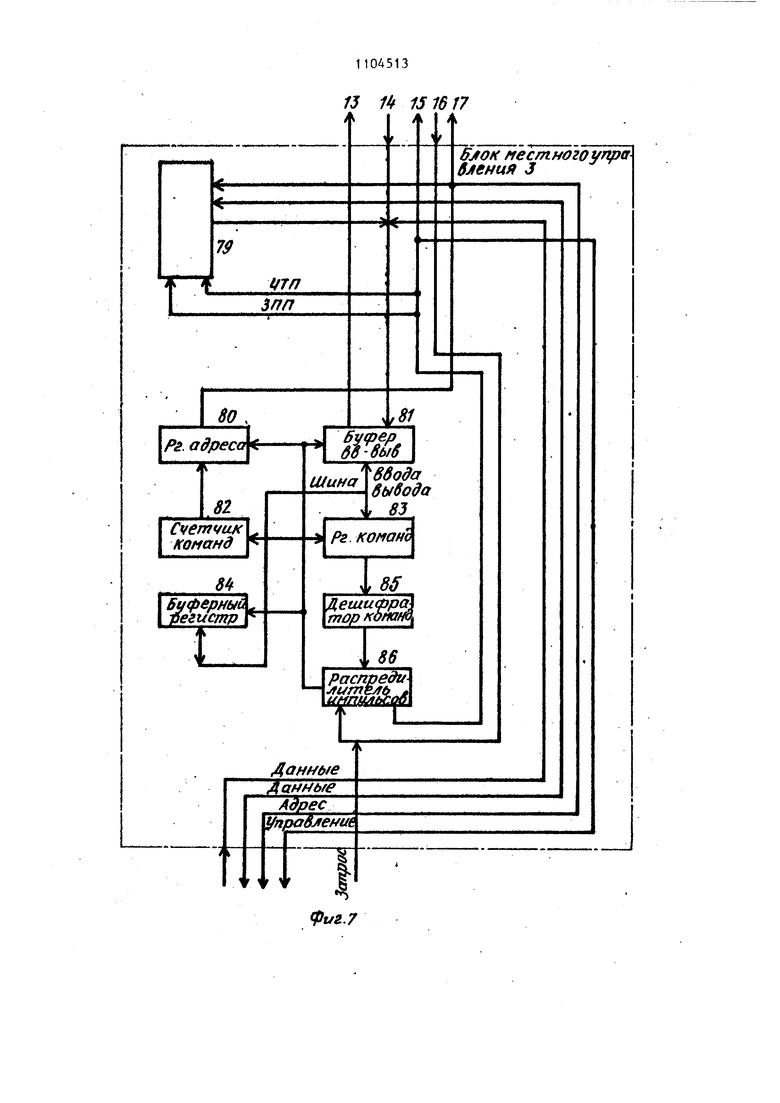

с выходами регистра левой точки блока подготовки суперпозиции, выходы сумматора блока подготовки суперпозиции соединены с второй группой информационных входов регистра результата итерации блока подготовки суперпозиции, первая группа выходов которого соединена с второй группой информационных входов регистра левой точки блока подготовки суперпозиции, выходы регистра коэффициента блока подготовки суперпозиции соединены с вторыми входами элементов И первой группы блока подготовки суперпозиции, вторая группа выходов регистра результата итерации блока подготовки суперпозиции соединена с вторыми входами элементов И второй группы блока подготовки суперпозиции, выходы первой и второй групп элементов И блока под-, готовки суперпозиции соединены соответственно с первыми и вторыми входами элементов ИЛИ группы блока подготовки суперпозиции, выходы которых соединены с информационными входами ключей первой группы блока подготовки суперпозиции, первый выход второй группы выходов распределителя импульсов блока подготовки суперпозиции соединен с входом записи узла памяти блока подготовки суперпозиции, второй выход второй группы выходов распределителя импульсов блока подготовки суперпозиции - с входом чтения узла памяти блока подготовки суперпозиции, информационные входы ключей второй группы блока подготовки суперпозиции соединены с выходами узла памяти блока подготовки суперпозиции, выходы ключей первой группы блока подготовки суперпозиции соединены с информационными входами узла памяти блока подготовки суперпозиции, выходы регистра адреса блока подготовки суперпозиции соединены с адресными входами узла памяти блока подготовки суперпозиции, узел коммутации коммутатора данныхсодержит дешифратор адреса, триггер, элемент И, группу информационных ключей, группу адресных ключей, управляющий ключ, выход дешифратора адреса подключен к входу синхронизации триггера узла коммутации коммутатора данных, выход которого соединен с первым входом элемента И узла коммутации коммутатора данных, выход которого подключен к управляющим входам информационных, адресных и управляющего ключей узла комутации коммутатора данных, блок управления содержит узел памяти, регис адреса, две группы ключей, счетчик команд, регистр команд, буферный регистр, дешифратор команд, распределитель импульсов, причем в блоке управления первый выход первой группы вьтходов распределителя импульсов соединен с входом синхронизации буфеного регистра блока управления, второй выход первой группы выходов распределителя импульсов блока управления - со счетным входом счетчика команд блока управления, третий выход первой группы выходов распределителя импульсов блока управления - с входом синхронизации регистра адреса блока управления, четвертый выход первой группывыходов распределителя импульсов блока управления - с управ ляющими входами ключей первой группы блока управления, пятый выход первой группы выходов распределителя импульсов блока управления - с управляюш11ми входами ключей второй группы блока управления, шестой выход первой группы выходов распределителя импульсов блока управления - с входом синхронизации регистра.команд блока управления, первая группа входов распределителя импульсов блока управления соединена с выходами дешифратора команд блока управления, входы которого соединены с выходами регистра команд блока управления, входы ключей первой группы блока управления соединены с информационными выходами буферного регистра блока управления, выходы информационных ключей второй группы блока управления соединены с входами регистра команд блока управления и буферного регистра блока управления, выходы счетчика команд блока управления соединены с входами регистра адреса блока упраления , выходы ключей первой группы блока управления соединены с информационными входами узла памяти блока управления, входы ключей второй группы блока управления соединены с выходами узла памяти блока управления, выходы регистра адреса блока управления соединены с адресными входами узла памяти блока управления, первый выход второй группы выходов распределителя импульсов блока управления соединен с входом записи узла памяти блока управления, второй выход второй группы выходов распределителя импульсов блока управления соединен с входом чтения узла памяти блока управления, блок местного управления содержит узел памяти, регистр .адреса, четыре группы ключей, счетчик команд, регистр команд, буферный регистр, дешифратор команд, распределитель импульсов, четыре элемента И, два дешифратора адреса, регистр ввода, регистр вывода,, причем в блоке местного управления первый выход первой группы выходов распределителя импульсов соединен с входом синхронизации буферного регистра блока местного управления, второй выход первой группы выходов распределителя импульсов блока местного управления - со счетным входом счетчика команд блока местного управления, третий выход первой группы выходов распределителя импульсов блока местного управления - с входом синхронизации регистра адреса блока местного управления, четвертый выход первой группы выходов распределителя Импульсов блока местного управления - с управляющими входами ключей первой группы блока местного управления, пя- тый выход первой группы выходов распределителя импульсов блока местного управления - с управляющими входами ключей второй группы блока местного управления, шестой выход первой группы выходов распределителя импульсов блока местного управления - с входом синхронизации регистра команд блока местного управления, первая группа входов распределителя импульсов блока местного управления соединена с выходами дешифратора команд блока местного управления, входы которого соединены с выходами регистра команд блока местного управления, информационные входы к.шочей первой группы блока местного управления соединены с выходами буферного регистра блока

местного управления, выходы ключей второй группы блока местного управления соединены с информационными входами регистра команд и буферного регистра блока местного управления, выходы счетчика команд блока местного управления соединены с информационными входами регистра адреса блока местного управления, выходы которого соединены с адресными входами узла памяти блока местного управления, с входами первого дешифратора адреса блока местного управления, первый выход второй группы выходов распределителя импульсов блока местного управления соединен с входом записи узла памяти блока местного управления, второй выход второй группы выходов распределителя импульсов блока местного управления соединен с входом чтения узла памяти блока местного управления, третий выход второй группы выходов распределителя импульсов блока местного управления соединен с первым входом первого элемента И блока местного управления, четвертый выход второй группы выходов распределителя импульсов блока местного управления соединен с первым входом второго элемента И блока местного управления, первый вход -второй группы входов распределителя импульсов блока местного управления соединен с выходом третьего элемента И блока местного управления, информационные входы ключей третьей группы соединены с выходами регистра вывода блока местного управления, выход первого дешифратора адреса блока местного управления соединен с вторыми входами первого и второго элементов И блока местного управления, выход второго элемента И блока местного управления соединен с управляющими входами ключей третьей группы блока местного управления, выход первого элемента И блока местного управления соединен с входом синхронизации регистра ввода блока местного управления, выходы регистра ввода блока местного управления соединены с информационными входами ключей четвертой группы блока местного управления, управляющие входы ключей четвертой группы блока местного управления соединены с выходом четвертого элемента И блока местного управления, вы- ход третьего элемента И блока местного управления соединен с входом синхронизации регистра вывода блока местного управления, выход второго дешифратора адреса блока местного управления соединен с первыми входами третьего и четвертого элементов И блока местного управления, выходы ключей первой группы блока местного управления соединены с информационными входами узла памяти и с информационными входами регистра ввода блока местного управления, информационные входы ключей второй группы блока местного управления соединены с выходами узла памяти и с выходами ключей третьей группы блока местного управления, причем выходы выходных ключей, информационные входы регистра ввода, входы первого дешифратора адреса,второй вход четвертого элемента И второй вход третьего элемента И, выход первого элемента И каждого коммутатора управляюш 1х сигналов второй группы соединены соответственно с информационными входами ключей второй группы, выходами ключей первой группы, выходами регистра адреса, третьим выходом второй группы выходов распределителя импульсов, четвертым выходом второй группы выходов распределителя импульсов и с входом распределителя импульсов решающего блока половинного шага, выходы выходных ключей, информационные входы регистра ввода, входы первого дешифратора адреса, второй вход четвертого элемента И, второй вход третьего элемента И выход первого элемента И каждого коммутатора управляющих сигналов третьей группы соединены соответственно с информационными входами ключей второй группы, выходами ключей первой группы, выходами регистра адреса, третьим выходом второй группы выходов распределителя импульсов, четвертым вьрсодом второй группы выходов распределителя импульсов, первым входом второй группы входов распределителя импульсов блока подготовки суперпозиции, выходы ключей четвертой группы первого и второго блоков местного управления подключены к информационным входам ключей второй группы блока управления, выходы ключей первой группы блока управления соединены с информационными входами регистров вывода первого и второго блоков местного управления, третий и четвертый выходы второй группы выходов распределителя импульсов блока управления соединены с вторыми входами соответственно третьего и четвертого элементов И первого и второго блоков местного управления, выходы первых элементов И первого и второго блоков местного управления соединены соответственно с первым и вторым входами второй группы входов распределителя импульсов блока управления, выходы регистра адреса которого соединены с входами вторых дешифраторов адреса первого и второго блоков местного управления, выходы входных ключей каждого коммутатора управляющих сигналов первой группы подключены к ин формационным входам ключей второй группы первого блока местного управления, выходы ключей первой группы которого соединены с информационными входами регистра вывода калодого коммутатора управляющих сигналов первой группы,-третий и четвертый выходы второй группы выходов распределителя импульсов первого блока местного управления соединены с вторыми входами соответственно первого и второго эле ментов И каждого коммутатора управля ющих сигналов первой группы, второй (Ы-И)-й входы второй группы входов распределителя импульсов первого бло ка местного управления соединены с выходами третьих элементов И соответствующих коммутаторов управляющих сигналов первой группы, выходы регистра адреса первого блока местного управления соединены с входами второ го дешифратора адреса каждого коммутатора управляющих сигналов первой группы, выходы входных ключей коммутатора управляющих сигналов второй и третьей групп подключены к,информационным входам ключей второй группы второго блока местного управления выходы ключей первой группы которого соединены с информационными входами регистров вывода каждого коммутатора управляющих сигналов второй и третьей групп, третий и четвертый выходы распределителя импульсов второго блока местного управления соеди иены с вторыми входами соответствен13но первого и второго элементов И каждого коммутатора управляющих сиг- налов второй и третьей групп, второй()-й входы второй группы входов распределителя импульсов второго блока местного управления соединены с выходами третьих элементов И соответствукйцих коммутаторов управляющих сигналов второй и третьей групп, выходы регистра адреса второго блока местного управления,соединены с входами вторых дешифраторов адреса каж- . дого коммутатора управляющих сигналов второй и третьей групп, выходы информационных ключей, выходы адресных ключей, выход управляющего ключа и выход триггера каладого i-ro (i 1, N) узла коммутации коммутатора данных соединены соответственно с вторыми входами элементов И шестой группы, вторыми входами элементов И пятой группы, вторым входом второго элемента И, вторым входом второй группы входов распределителя импульсов, входом элемента НЕ, с первым входом второго элемента И, с первыми входами элементов И пятой и шестой групп решающего блока исходного шага и суперпозиции, информационные входы информационных ключей, информационные входы адресных ключей, информационньй вход управляющего ключа, управляющий вход дешифратора адреса, информационный вход триггера каждого i-ro узла коммутации коммутатора данных соединены соответственно с выходами ключей первой группы, выходами регистра адреса, с первым выходом второй группы выходов распределителя импульсов, с третьим выходом второй группы выходов распределителя импульсов, с выходами ключей первой группы j N + 21 блока подготовки суперпозиции, пятый выход распределителя импульсов каждого решающего блока исходного шага и суперпозиции соединен с вторым входом второй группы входов распределителя импульсов COQT- ветствующего блока подготовки суперпозиции. 11 Изобретение относится к цифровой вычислительной технике, к устройства для обработки цифровых данных и може быть использовано для решения дифференциальных уравнений в частных производных. Известны устройства для решения дифференциальных уравнений, -содержа- щие решающие блоки, информационные связи, коммутаторы, информационную шину, блок ввода-вывода, блок управления, а каждый решающий блок содержит микропроцессор, запоминающий бло группы элементов ИЛИ lj . Недостатком этих устройств являет ся ограниченная пропускная способнос информационной шины, которая являетс общей для всех решающих блоков и поз воляет осуществлять загрузку и обмен между решающими блоками последовател но, что снижает общую производительность. Наиболее близким к предлагаемому является устройство, содержащее решающие блоки, каждый из которых через соответствующий коммутатор соеди нен двусторонними связями с информационной шиной, устройство управления соединенное двусторонними связями с устройством ввода-вывода и с информа ционной шиной, а каждый решающий блок содержит регистры чтения и запи си, ключи, узел связи, микропроцессор, соединенный двусторонними связями и запоминающим устройством,подключенным соответствующим входом и выходом к входу и выходу решающего блока, соединенным коммутаторами, уп равляющие входы каждого коммутатора соединены с соответствующими выходами устройства управления 2. Недостаток известного устройства низкая производительность, которая является следствием того, что, с одной стороны, наличие общей управляющей шины для включения - выключения всех микропроцессоров обеспечивает только синхронньй режим их работы, а с другой - наличие общей информационной шины, которая связывает между собой решающие блоки, приводит к необходимости последовательном обмене информацией между решающими блоками, в то время как микропроцессоры, ожидая окончания обмена, про- стаивают. V Целью изобретения является повышение производительности устройства. 3. 2 Поставленная цель достигается тем, что в устройство для решения дифференциальных уравнений, содержащее блок управления, N решающих блоков исходного шага и суперпозиции и первую группу из N коммутаторов управляющих сигналов, каждый решающий блок исходного шага и суперпозиции содержит регистр результата итерации, распределитель импульсов, регистр левой точки, дешифратор команд, регистр коэффициента, сумматор, регистр команд, счетчик команд, регистр правой точки, две группы ключей, шесть групп элементов И, три группы элементов ИЛИ, регистр адреса, узел памяти, элемент ИЛИ, элемент НЕ, два элемента И, причем первьп1 выход первой группы выходов распределителя импульсов решающего блока исходного шага и суперпозиции соединен с входом синхронизации регистра коэффициента решающего блока исходного шага и суперпозиции, второй выход первой группы выходов распределителя импульсов решающего блока исходного шага и суперпозиции со счетным входом счетчика команд решающего блока исходного шага и суперпозиции, третий выход первой группы выходов распределителя импульсов решающего блока исходного шага и суперпозиции - с входом синхронизации регистра адреса решающего блока исходного шага и суперпозиции, четвертый выход первой группы выходов распределителя импульсов решающего блока исходного шага и суперпозиции - с управляющими входами ключей первой группы решающего блока исходного шага и суперпозиции, пятый выход первой группы выходов распределителя импульсов решающего блока исходного шага и суперпозиции - с первыми входами элементов И первой группы решающего блока исходного шага и суперпозиции, шестой выход первой группы дов распределителя импульсов решающего блока исходного шага и суперпозиции - с первыми входами элементов И второй группы решающего блока исходного шага и суперпозиции, седьмой выход первой группы выходов распределителя импульсов решающего блока исходного шага и суперпозиции - с управляющими входами ключей второй группы решающего блока исходного шага и суперпозиции, восьмой выход первой группы выходов распределителя импульсов решающего блока исходного шага и суперпозиции - с входом синхронизации регистра команд решающего блока Исход ного шага и суперпозиции, девятый выход первой группы выходов распределителя импульсов решающего блока исходного шага и суперпозиции - с входом синхронизации регистра результата итерации решающего блока исходного шага и суперпозиции, десятый выход первой группы выходов распределителя импульсов решающего блока исходного шага и суперпозиции - с входом синхро низации регистра левой точки решающего блока исходного шага и суперпозиции, одиннадцатый выход первой группы выходов распределителя импульсов решающего блока исходного шага и суперпозиции - с управляющим входом сумматора решающего блока исходного шага и суперпозиции, двенадцатый выход первой группы выходов распределителя импульсов решающего блока исходного шага и суперпозиции - с входом синхронизации регистра правой точки решающего блока исходного шага и суперпозиции, первая группа входов распределителя импульсов решающего блока исходного шага и суперпозиции соединена с выходами дешифратора команд решающего блока исходного шага и суперпозиции-, вхоДы которого соединены с информационными выходами регистра команд решающего блока исходного щага и суперпозиции, выходы ключей второй группы решающего блока исходного шага и суперпозиции соединены с информационными входами регистра коэффициента, регистра команд, регистра правой точки, первой группой информационных входов регистра результата итерации и регистра левой точки решающего блока исходного шага и суперпозиции, выходы счётчика команд решающего блока исходного шага и .суперпозиции соединены с информационяыми.входами регистра адреса решающе|го блока исходного шага и суперпрзи|ции, выходы рег истра правой точки решающего блока исходного шага и суперпозиции соединены с входакш первого слагаемого сумматора решающего бло ка исходного шага и суперпозиции, вхо ды второго слагаемого которого соединены с выходами регистра левой точки решающего блока исходного шага и суперпозиции, выходы сумматора решающего блока исходного шага и суперпозиции соединены с второй группой информационных входов регистра результата итерации решающего блока исходного шага и суперпозиции, первая группа выходов которого соединена с второй группой информационных входов регистра левой точки решающего блока исходного шага и суперпозиции, выходы регистра коэффициента решающего блока исходного шага и суперпозиции соединены с вторыми входами элемента И первой группы решающего блока исходного шага и суперпозиции, вторая группа выходов регистра результата итерации решающего блока исходного шага и суперпозиции соединена с вторыми входами элементов И второй группы решающего блока исходного шага и суперпозиции, выходы элементов И первой и вто-. рой групп решающего блока исходного шага и суперпозиции соединены соот- . ветственно с первыми и вторыми входами элементов ИЛИ первой группы решающего блока исходного шага и суперпозиции, выходы которых соединены с информационными входами ключей первой группы решающего блока исходного шага и суперпозиции, выход элемента НЕ соединен с первым входом первого элемента И решающего блока исходного шага и суперпозиции и первыми входами элементов И третьей и четвертой групп решающего блока исходного шага и суперпозиции, выход второго элемента И решающего блока исходного шага и суперпозиции Соединен с первым входом элемента ИЛИ решающего блока исходного шага и суперпозиции, выходы элементов И пятой группы решающего .блока исходного шага и суперпозиции Соединены с первыми входами элементов ИЛИ третьей группы решающего блока исходного шага и суперпозиции, информационные входы ключей второй группы решающего блока исходного шага и суперпозиции соединены с информационными выходами узла памяти решающего блока исходного .шага и суперпози.ции, выходы ключей первой группы решающего блока исходного шага и супер-. позиции соединены с вторыми входами элементов И третьей группы решающего блока исходного шага и суперпозиции, выходы которых соединены с вторыми входами элементов ИЛИ второй группы решакнце го блока исходного шага и суперпоз1иции, выходы регистра адреса решающего блока исходного шага и суперпозиции соединены с вторыми входами элементов И четвертой группы решающего блока исходного шага и суперпозиции выходы которых соединены с вторыми входами элементов ИЛИ трет ей группы решающего блока исходного шага и суперпозиции, первый выход второй группы выходов распределителя импульсов решающего блока исходного шага и суперпозиции соединен с вторым входом Первого элемента И решающего блока исходного шага и суперпозиции, второй выход второй группы выходов распределителя импульсов решающего блока исходного шага и супер позиции соединен с входом чтения узла памяти решакнцего блока исходного шага и суперпозиции, выход первого элемента И решающего блока исходного шага и суперпозиции соединен с вторым входом элемента ИЛИ решающего блока исходного шага и суперпозиции, выходы элементов ИЛИ второй и третьей групп решающего блока исходного шага и суперпозиции соединены соответственно с информационными и адрес- 5 и ными входами узла памяти решающего блока исходного шага и суперпозиции, выходы элементов И шестой группы соединены с первьми входами элементов ИЛИ второй группы, коммутатор управляющих сигналов содержит регистр вывода, группу выходных ключей, четыре элемента И, группу входных ключей, регистр ввода, два дешифратора адреса, выходы первого - четвертого элементов И коммутатора управляющих сигналов соединены соответственно с входом синхронизации регистра вывода, управляющими входами входных ключей, входом синхронизации регистра ввода и управляющими входами выходных ключей коммутатора управляющих сигналов, выходы регистра ввода коммутатора управляющих сигналов соединены с информационныт ш входами входных ключей группы коммутатора управляющих сигналов, выход первого дешифратора адреса коммутатора управляющих сигналов соединен с первыми входами третьего и четвертого элементов И коммутатора уп равляющих сигналов, выходы регистра вывода коммутатора управляющих сигналов подключены к информационным входа выходных ключей группы коммутатора уп равляющих сигналов, выход второго дешифратора адреса коммутатора управ ляющих сигналов соединен с первыми входами первого и второго элементов И коммутатора управляющих сигналов, вы136ходы выходных ключей группы, информационные входы регистра ввода, входы первого дешифратора адреса, второй вход четвертого элемента И, второй вход третьего элемента И, выход первого элемента И каждого коммутатора управляющих сигналов первой группы со единены соответственно с информационными входами ключей второй группы, выходами ключей первой группы, выходами регистра адреса, третьим выходом второй группы выходов распределителя импульсов, четвертым выходом второй группы выходов распределителя импульсов и первым входом второй группы входов распределителя импульсов соответствующего решающего блока исходного шага и суперпозиции, введены N+1 решающих блоков половинного шага, вторая группа из N+1 коМмутаторов управляющих сигналов, N блоков подготовки суперпозиции, третья груп-па и.з N коммутаторов управляющих сиг-. налов, два блока местного управления коммутатор данных, который содержит N узлов коммутации, причем решающий блок половинного шага содержит регистр результата итерации, распределитель импульсов, регистр левой точки, дешифратор команд, регистр коэффициента, сумматор, регистр команд, счетчик команд, регистр правой точки, две группы ключей, две группы элементов И, группу элементов ИЛИ, регистр адреса, узел памяти, причем в каждом решающем блоке половинного шага первый выход первой группы выходов распределителя импульсов соединен с входом синхронизации регистра коэффициента решающего блока половинного шага, второй выход первой группы выходов распределителя импульсов решающего блока половинного шага со счетным входом счетчика команд решающего блока половинного шага, третий выход первой группы выходов распределителя импульсов решающего блока половинного шага - с входом синхронизации регистра адреса решающего блока половинного шага, четвертый выход первой группы выходов распределителя импульсов решающего блока половинного шага - с управляющими входами ключей первой группы решающего блока половинного шага, пятьй выход первой группы выходов распределителя Ю1пульсов решающего блока половинного шага - с первыми входами элементов И первой группы решающего блока половинного шага, шестой выход первой групп выходов распределителя импульсов реш ющего блока половинного шага - с пер выми входами элементов И второй груп пы решающего блока половинного шага, седьмой выход первой группы выходов распределителя импульсов решающего блока половинного шага - с управляющими вхоцат ключей второй группы решающего блока половинного шага, восьмой выход первой группы выходов распределителя, импульсов решающего блока половинного шага - с входом синхронизации регистра команд решающего блока половинного шага, девятый выход первой группы выходов распределителя импульсов решающего блока половинного шага - с входом синхронизации регистра результата итера ции решающего блока половинного шага десятый вызсод первой группы выходов распределителя импульсов решающего блока половинного шага - с входом синхронизации регистра левой точки решающего блока половинного шага, одиннадцатый выход первой группы выходов распределителя импульсов решающего блока половинного шага - с управляющим входом сумматора решающего блока половинного шага, двенадцатый выход первой группы выходов распределителя импульсов решающего блока половинного шага - с входом синхрони зации регистра правой точки решающего блока половинного шага, первая группа входов распределителя импульсов решающего блока половинного шага соединена с выходами дешифратора команд решающего блока половинного шага, входы которого соединены с выходами регистра команд решающего бло ка половинного шага, выходы ключей второй группы решающего блока половинного шага соединены с информацион ньми входами регистра коэффициента, регистра команд, регистра правой точ ки, первьми группами информационных входов регистра результата итерации регистра левой точки решающего блока половинного шага, выходы счетчика команд решающего блока половинного шага соединены с информационными вхо дами регистра адреса решающего блока половинного шага, выходы регистра пр вой точки решающего блока половинного шага соединены с входами правого слагаемого сумматора решающего блока половинного шага, входы второго слаг емого которого соединены с информаци онными выходами регистра левой точки решающего блока половинного шага, выходы сумматора решающего блока половинного шага соединены с второй группой информационных входов регистра результата итерации решающего блока половинного шага, первая группа выходов которого соединена с второй г руппой информационных входов регистра левой точки решающего блока половинного шага, выходы регистра коэффициента решающего блока половинного шага соединена с вторыми входами элементов И первой группы решающего блока половинного шага, вторая группа выходов регистра результата итерации решающего блока половинного шага соединена с вторыми входами элементов И второй группы решающего блока половинного шага, выходы элементов И первой и второй групп решающего блока половинного шага соединены соответственно с первыми и вторыми входами группы элементов ИЛИ, выходы которых соединены с информационными входами ключей первой группы решающего блока половинного шага, первый выход второй группы выходов распределителя импульсов решающего блока половинного шага соединен с входом записи узла памяти решающего блока половинного шага, второй выход второй группы выходов распределителя импульсов решающего блока половинного шага соединен с входом чтения узла памяти решающего блока половинного шага, информационные входы ключей второй группы решающего блока половинного шага соединены с выходами узла памяти решающего блока половинного шага, выходы ключей первой группы решающего блока половинного шага соединены с информационными входами узла памяти решающего блока половинного шага, выходы регистра адреса соединены с адресными входами узла памяти решающего блока половинного шага, решающий блок подготовки суперпозиции содержит регистр результата итерации, распределитель импульсов, регистр левой точки, дешифратор команд, регистр коэффициента, сумматор, регистр команд, счетчик команд, регистр праёой точки, две группы ключей, две группы элементов И, группу элементов ИЛИ, регистр адреса, узел паьшти, причем в блоке подготовки суперпозиции первый выход первой группы выходов распределителя импульсов блока подготовки суперпозиции соединен с входом синхронизации регистра коэффициента блока подготовки суперпозиции, второй выход первой группы выходов распределителя импульсов блока подготовки суперпозиции - с счетным входом счетчика команд блока подготовки суперпозиции, третий выход первой группы выходов распределителя импульсов блока подготовки суперпозиции - с входом синхронизации регистра адреса блока подготовки суперпозиции, четвертый выход первой группы выходов распределителя импульсов блока подготовки суперпозиции - с управляющими входами ключей первой группы блока подготовки суперпозиции, пятый выход первой группы выходов распределителя импульсов блока подготовки суперпозиции с первыми входами элементов И первой группы блока подготовки суперпозиции, шестой выход первой группы выходов распределителя импульсов блока подготовки суперпозиции - с первыми входами элементов И второй группы блока подготовки суперпозиции, седьмой выход первой группы выходов распределителя импульсов блока подготовки супер позиции - с управляющими входами ключей второй группы блока подготовки суперпозиции, восьмой выход первой группы выходов распределителя импульсов блока подготовки суперпозиции с входом синхронизации регистра команд блока подготовки суперпозиции, девятый выход первой группы выходов распределителя импульсов блока подготовки суперпозиции - с входом синхронизации регистра результата итерации подготовки суперпозиции, десятьй выход первой группы выходов распредели теля импульсов блока подготовки суперпозиции - с входом синхронизации регистра левой точки блока подготовки суперпозиции, одиннадцатый выход группы выходов распределителя импульсов блока подготовки суперпозиции - с управляющим входом сумматора блока подготовки суперпозиции, двенадцатый выход первой группы выходов распределителя импульсов блока подготовки суперпозиции - с входом синхронизации регистра правой точки блока подготовки суперпозиции, первая группа входов распределителя импульсов блока подготовки суперпозиции соединена с выходами дешифратора команд блока подготовки суперпозиции, входы которого соединены с выходами регистра команд блока подготокй суперпозиции, выходы ключей второй группы блока подготовки суперпозиции соединены с информационньми входами регистра коэффициента блока подготовки суперпозиции, регистра команд, регистра правой точки, первой группой информационных входов регистра результата итерации и регистра левой точки блока подготовки суперпозиции, выходы счетчика команд блока подготовки суперпозиции соединены с информационными входами регистра адреса блока подготовки суперпозиции, выходы регистра правой точки блока подготовки суперпозиции соединены с входами первого слагаемого сумматора блока подготовки суперпозиции, входы второго слагаемого которого соединены с выходами регистра левой точки блока, подготовки суперпозиции, выходы сумматора блока подготовки суперпозиции . соединены с второй группой информационных входов регистра результата итерации блока подготовки суперпозиции, первая группа выходов которого соединена с второй группой информационных входов регистра левой точки блока подготовки суперпозиции, выходы регистра коэффициента блока подготовки суперпозиции соединены с вторыми входами элементов И первой группы блока подготовки суперпозиции, вторая группа выходов ре.гистра результата итерации блока подготовки суперпозиции соединена с вторыми входами элементов И второй группы блока подготовки суперпозиции, выходы первой и второй групп Элементов И блока подготовки суперпозиции соединены соответственно с первыми и вторыми входами элементов ИЛИ группы блока подготовки суперпозиции, выходы которых соединены с информационными входами ключей первой группы блока подготовки суперпозиции, первьй выход второй группы вьпсодов распределителя импульсов блока подготовки суперпозиции соединен с входом записи узла памяти блока подготовки суперпозиции, второй выход второй группы выходов распределителя импульсов блока подготовки суперпозиции - с входом чтения узла памяти блока подготовки суперпозиции, информационные входы ключей второй группы блока подготовки суперпозиции соединены . с выходами узла памяти подготовки суперпозиции, выходы ключей первой .группы блока 11 подготовки суперпозиции соединены с информационными входами узла памяти блока подготовки суперпозиции, выходы регистра адреса блока подготовки суперпозиции соединены с адресными входами узла памяти блока подготовки суперпозиции, узел коммутации коммутатора данных содержит дешич/ратор адреса, триггер, элемент И, группу информационных ключей, группу адресных ключей, управляющий ключ, выход дешифратора адреса подключен к входу синхронизации триггера узла коммутации коммутатора данных, выход которого соединен с первым входом элемента И узла коммутации коммутато ра данных, выход которого подключен к управляющим входам информационных, адресных и управляющего ключей узла коммутации коммутатора данных, блок управления содержит узел памяти, регистр адреса, две группы ключей, сче чик команд, регистр команд, буферный регистр, дешифратор команд, распреде литель импульсов, причем в блоке управления первый выход первой группы выходов распределителя импульсов соединен с входом синхронизации буферного регистра блока управления-, второй выход первой группы выходов распределителя импульсов блока управления - со счетным входом счетчика команд блока управления, третий выход первой группы выходов распределителя импульсов блока управления - с входом синхронизации регистра адреса блока управления, четвертый выход первой группы выходов распределителя импульсов блока управления - с уп равляющими входами ключей первой группы блока управления, пятый выход первой группы выходов распределителя импульсов блока управления - с управ ляющими входами ключей второй группы блока управления, шестой выход первой группы выходов распределителя импульсов блока управления - с вхо,дом синхронизации регистра команд блока управления, первая группа входов распределителя импульсов блока управления соединена с выходами деши ратора команд блока управления, входы которого соединены с выходами регистра команд блока управления, входы ключей первой группы блока управления соединены с информационными вы ходами буферного регистра блока упра ления , выходы информационных ключей второй группы блока управления соеди 1312 нены с входами регистра команд блока управления и буферного .регистра блокд управления, выходы счетчика команд блока управления соединены с входами регистра адреса блока управления, выходы ключей первой группы блока управления соединены с информа1щонными входами узла памяти блока управления, входы ключей второй группы блока управления соединены с выходами узла памяти блока управления, выходы регистра адреса блока управления соединены с адресными входами узла памяти блока управления, первый выход второй группы выходов распределителя импульсов блока управления соединен с входом записи узла памяти блока управления, второй выход второй группы выходов распределителя импульсов блока управления соединен с входом чтения узла памяти блока управления, блок местного управления содержит узел памяти, регистр адреса, четыре группы ключей, счетчик команд, регистр команд, буферный регистр, дешифратор команд, распределитель импульсов, четыре элемента И, два дешифратора адреса, регистр ввода, регистр вывода, причем в блоке местного управления первьй выход первой группы выходов распределителя импульсов соединен с входом синхронизации буферного регистра блока местного управления, второй выход первой группы выходов распределителя импульсов блока местного управлениясо счетным входом счетчика команд блока местного управления, третий выход первой группы выходов распределителя импульсов блока местного управления - с входом синхронизации регистра адреса блока местного управления, четвертый выход первой группы выходов распределителя импульсов блог ка местного управления - с управляющими .входами ключей первой группы блока местного управления, пятый выход первой группы выходов распределителя импульсов блока местного Управления - с управляющими входами ключей второй группы блока местного управления, щестой выход первой группы выходов распределителя импульсов блока местного управления - с входом синхронизации регистра команд блока местного управления, первая группа входов распределителя импульсов блока местного управления соединена с выходами дешифратора команд блока местного управления, входы которого соединены с выходами регистра команд блока местного управления, информационные входы первой группы блока местного управления соединены с выходами буферного регистра блока местного управления, выходы ключей второй группы блока местного управле ния соединены с информационными входами регистра команд и буферного регистра блрка местного управления, вы ходы счетчика команд блока местного управления соединены с информационными входами регистра адреса блока местного управления, выходы которого соединены с адресными входами- узла памяти блока местного управления, с входами первого дешифратора адреса блока местного управления, первый выход второй группы выходов распределителя импульсов блока местного управления соединен с входом записи узла памяти блока местного управления, второй выход второй группы выходов распределители импульсов блока местного управления соединен с входо чтения узла памяти блока местного управления, третий .выход второй группы выходов распределителя импульсов блока местного управления соединен с первым входом первого элемента И блока местного управления четвертый выход второй группы выходов распределителя импульсов блока местного управления соединен с первы входом второго элемента И блока мест ного управления, первый вход второй группы входов распределителя импульсов блока местного управления соединен с выходом третьего элемента И блока местного управления, информационные входы ключей третьей группы соединены с выходами регистра вывода блока местного управления, выход пер вого дешифратора адреса блока местного управления соединен с вторыми входами первого и второго элементов И блока местного управления, выход второго элемента И блока местного управления соединен с управляющими входами ключей третьей группы блока местного управления, выход первого элемента И блока местного управления соединен с входом синхронизации регистра ввода блока местного управления, выходы регистра ввода блока мес

ного управления соединены с информа-55ционным входам ключей второй группы

ционными входами ключей четвертойблока управления, выходы ключей пергруппы блока местного управления, уп-вой группы блока управления соединены

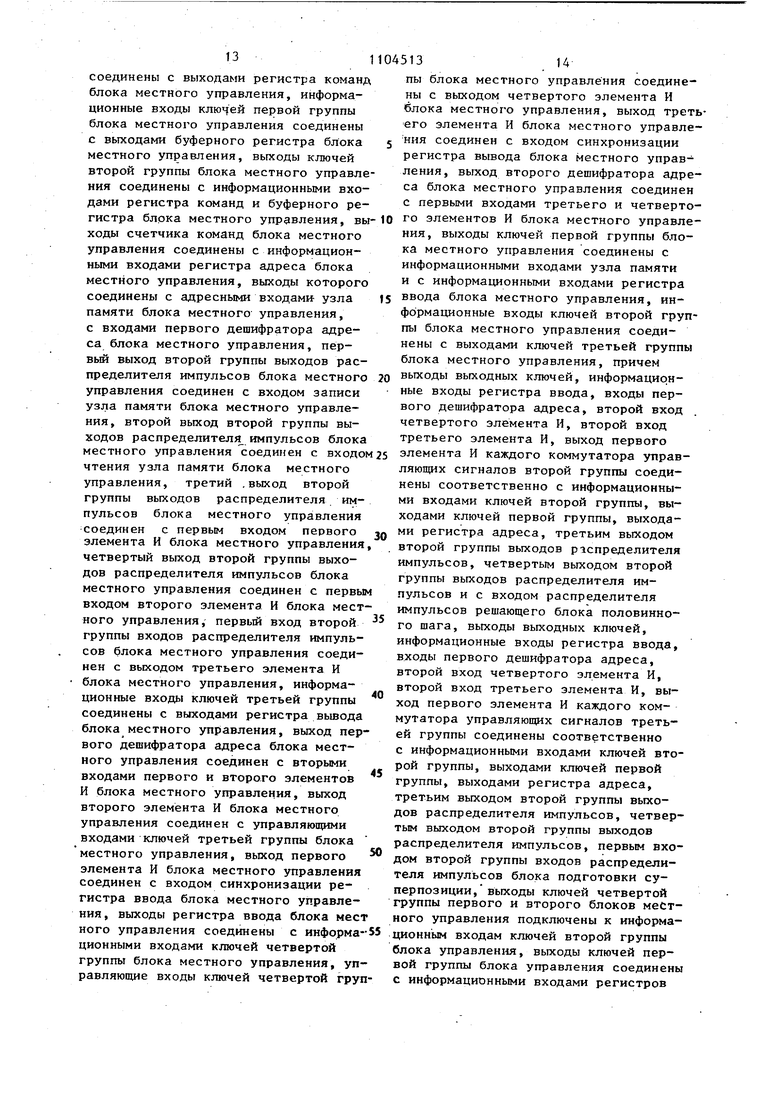

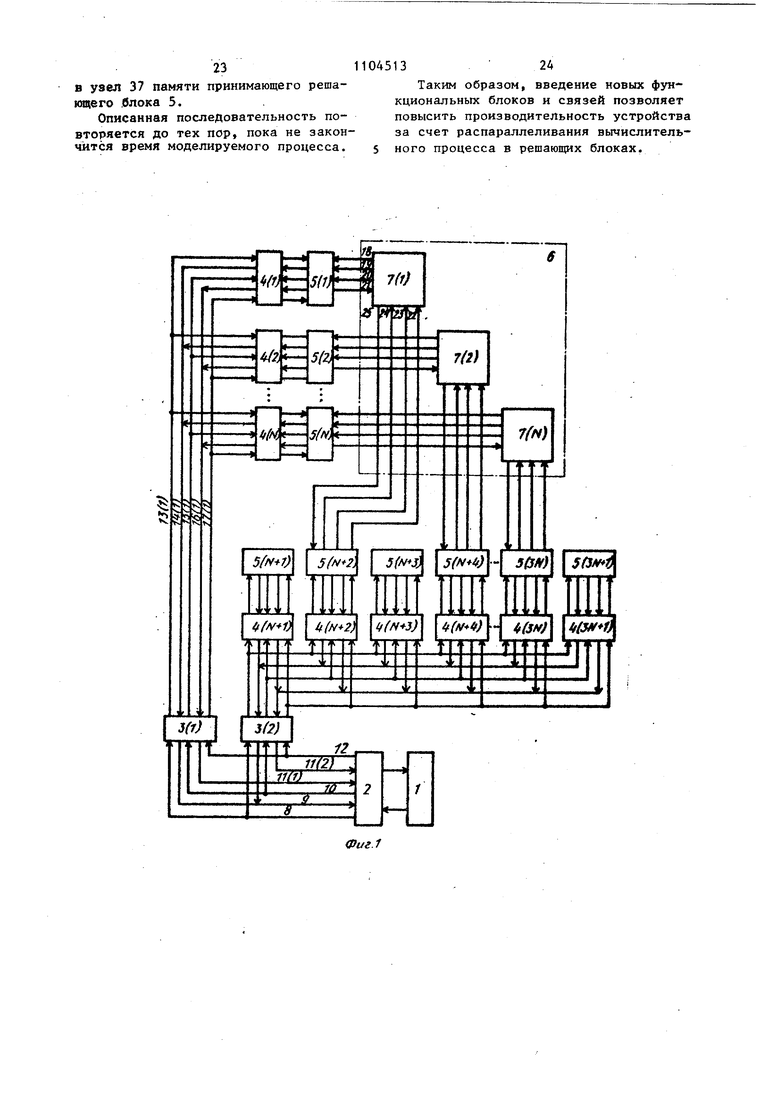

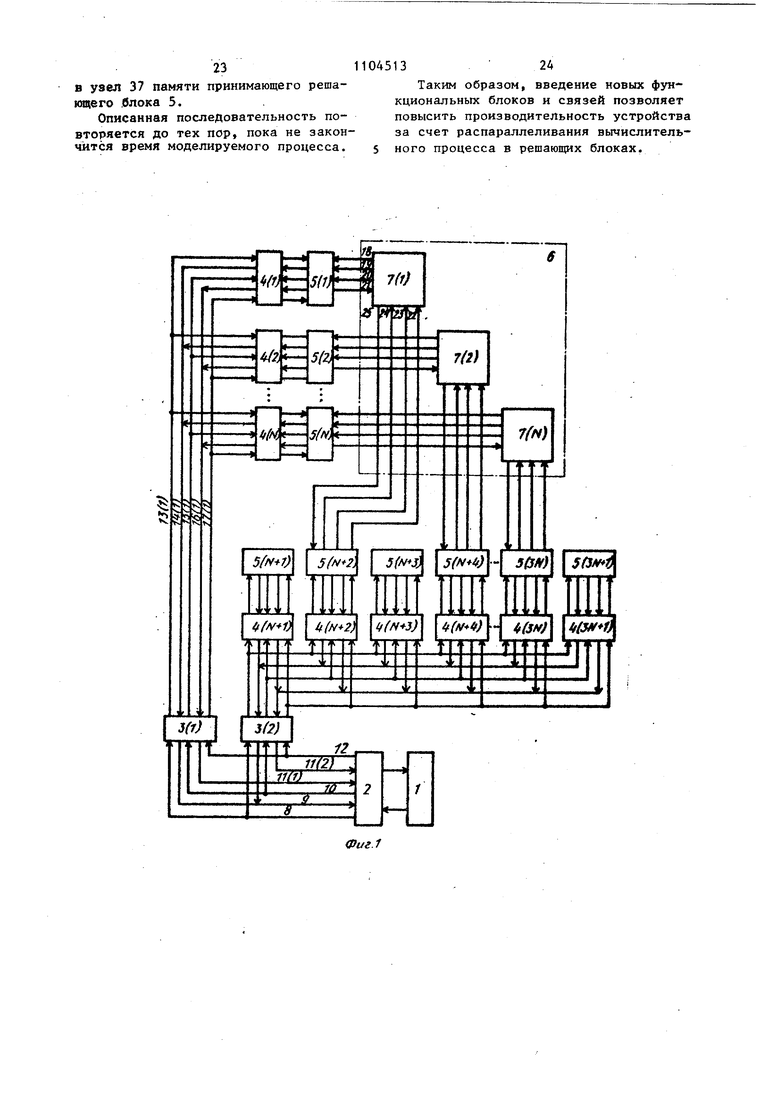

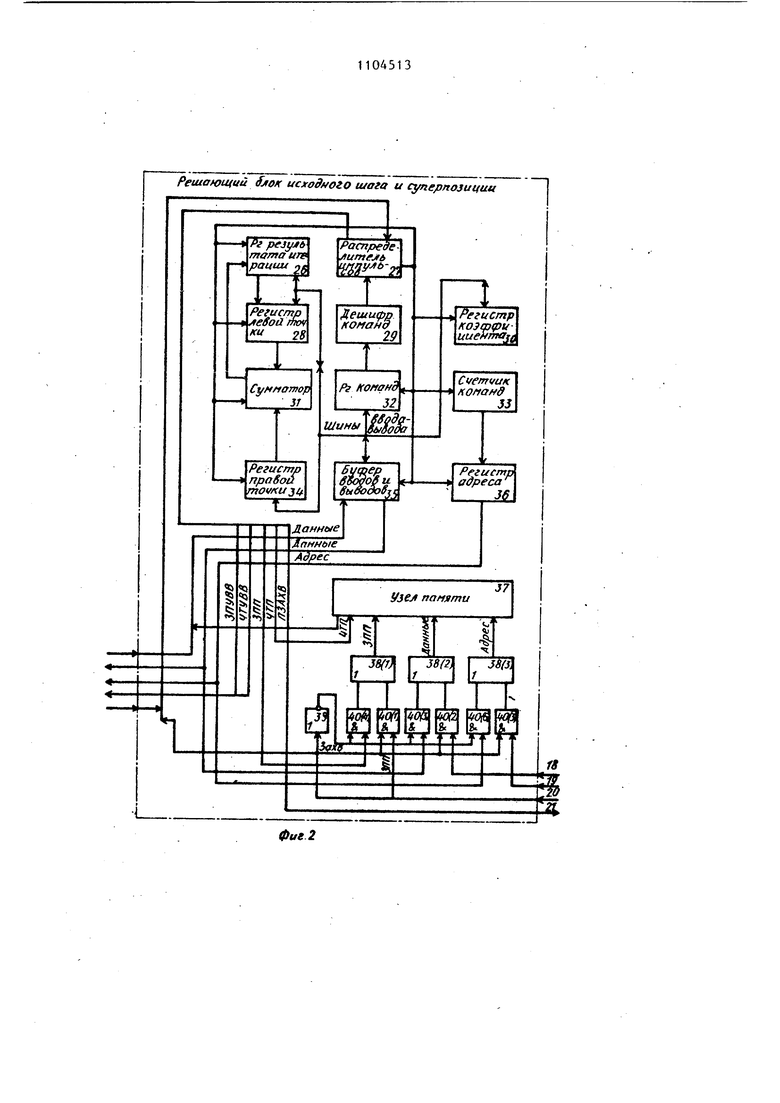

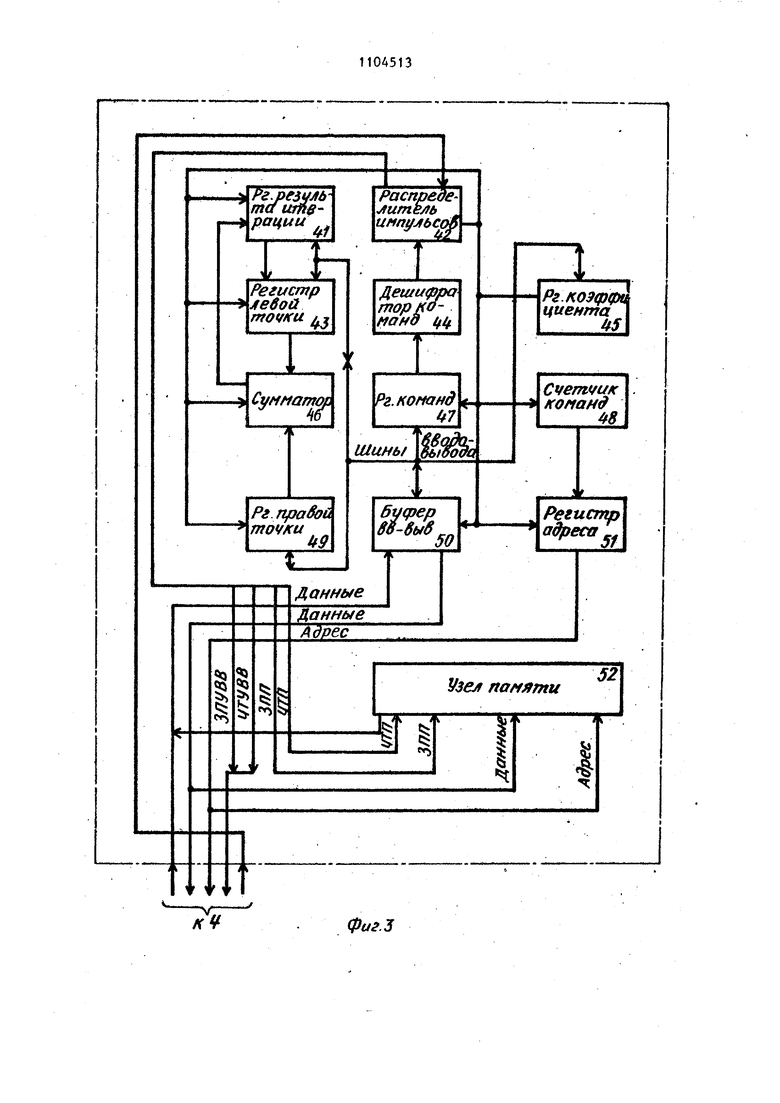

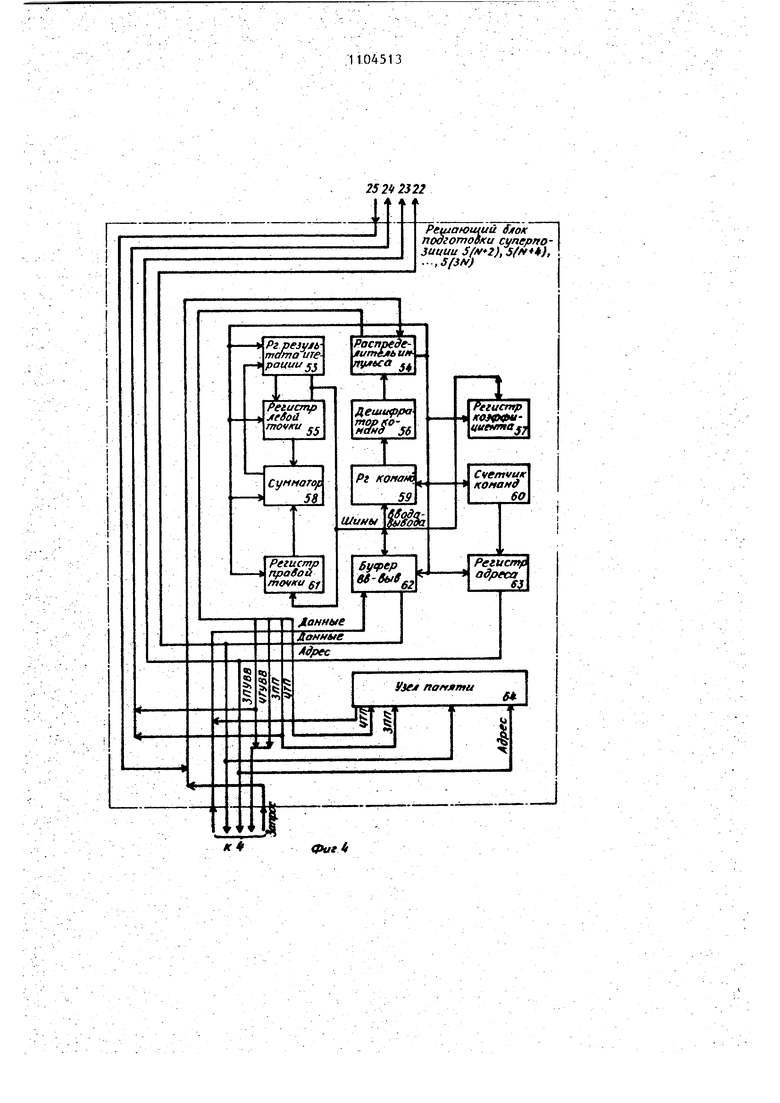

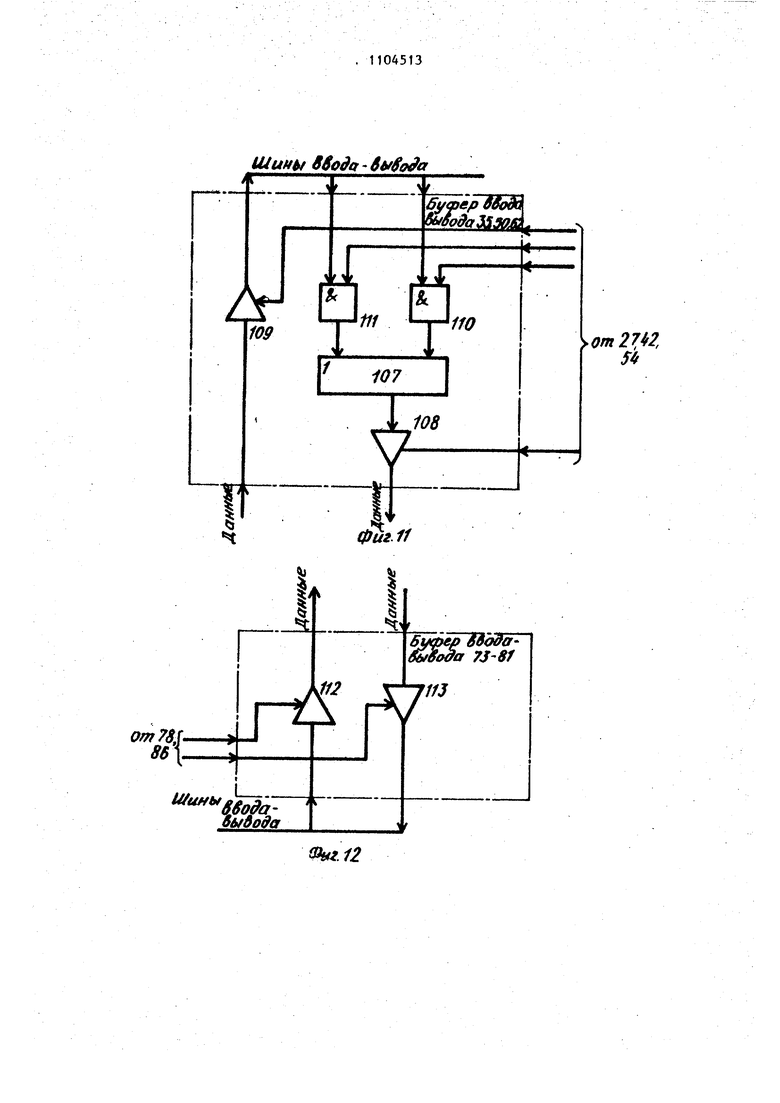

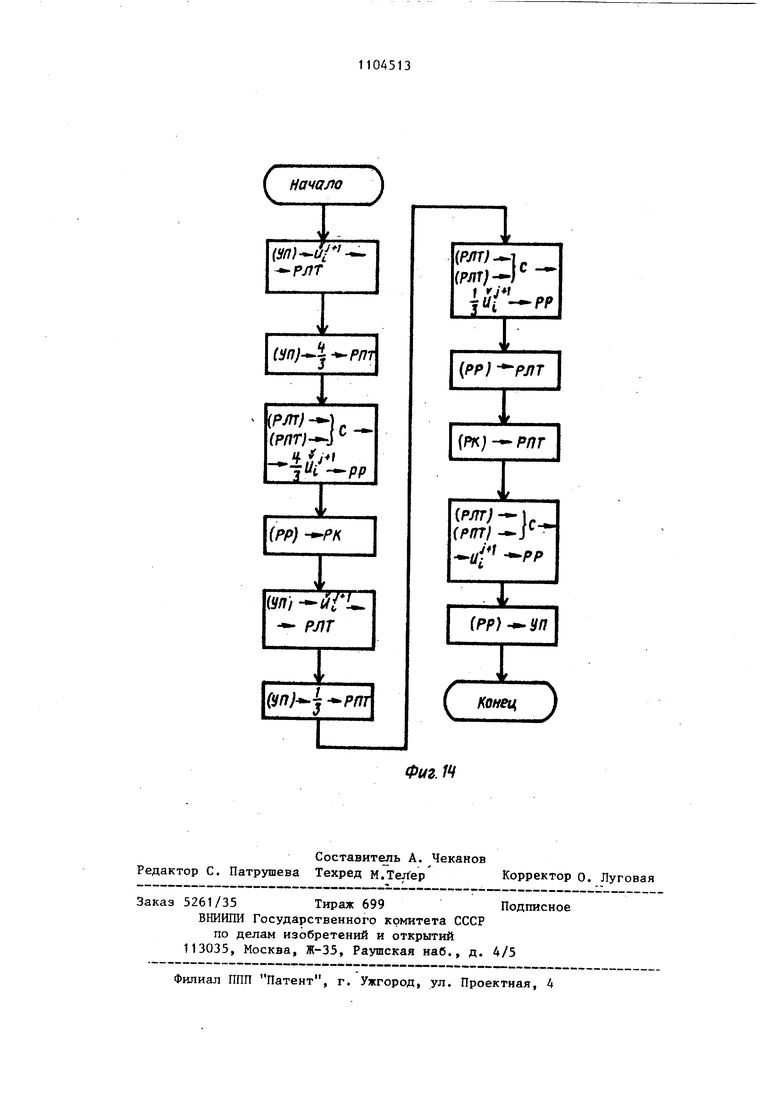

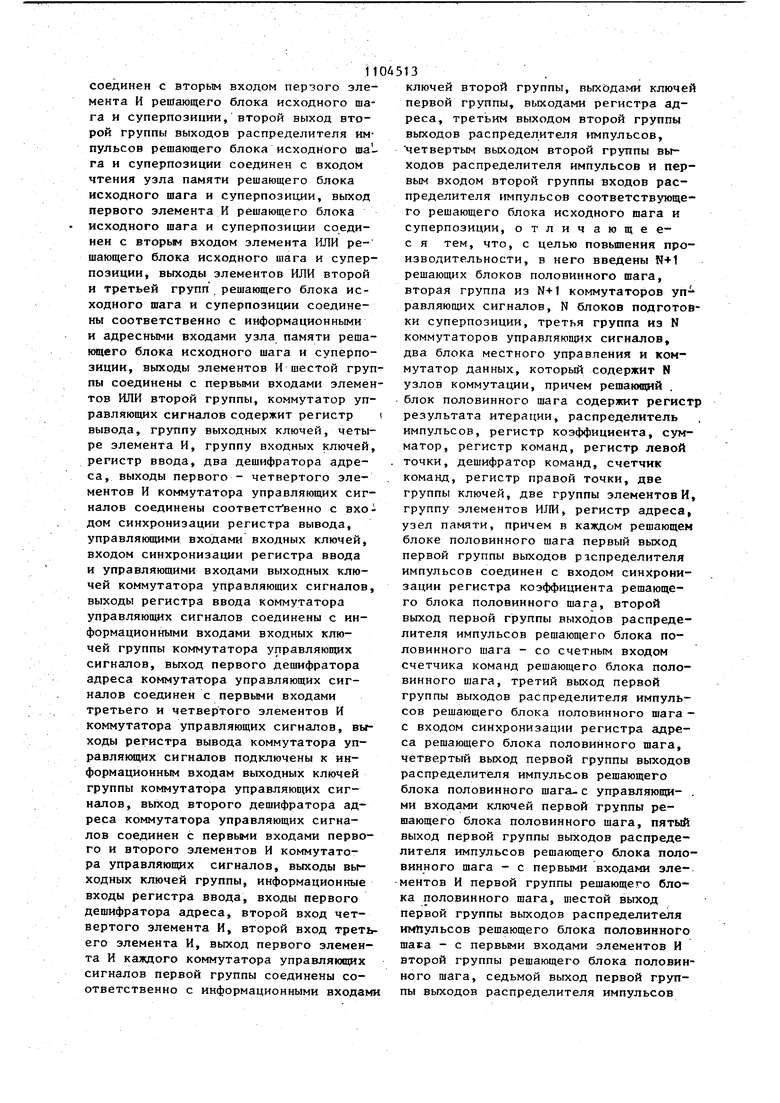

равляющие входы ключей четвертой груп-с информационными входами регистров 1314 пы блока местного управления соединены с выходом четвертого элемента И блока местного управления, выход третьего элемента И блока местного управления соединен с входом синхронизации регистра вывода блока местного управления, выход второго дешифратора адреса блока местного управления соединен с первыми входами третьего и четвертого элементов И блока местного управления, выходы ключей первой группы блока местного управления соединены с информационными входами узла памяти и с информационными входами регистра ввода блока местного управления, информационные входы ключей второй группы блока местного управления соединены с выходами ключей третьей группы блока местного управления, причем выходы выходных ключей, информационные входы регистра ввода, входы первого дешифратора адреса, второй вход четвертого элемента И, второй вход третьего элемента И, выход первого элемента И каждого коммутатора управляющих сигналов второй группы соединены соответственно с информационными входами ключей второй группы, выходами ключей первой группы, выходами регистра адреса, третьим выходом второй группы выходов распределителя импульсов, четвертым выходом второй группы выходов распределителя импульсов и с входом распределителя импульсов решающего блока половинного шага, выходы выходных ключей, информационные входы регистра ввода, входы первого дешифратора адреса, второй вход четвертого элемента И, второй вход третьего элемента И, выход первого элемента И каждого коммутатора управляющих сигналов третьей группы соединены соответственно с информационными входами ключей второй группы, выходами ключей первой группы, выходами регистра адреса, третьим выходом второй группы выходов распределителя импульсов, четвертым выходом второй группы выходов распределителя импульсов, первым входом второй группы входов распределителя импульсов блока подготовки суперпозиции, выходы ключей четвертой группы первого и второго блоков местного управления подключены к информа15 1 вывода первого и второго блоков местного управления, третий и четвертый выходы второй группы выходов распре делителя импульсов блока управления соединены с вторыми входами соответственно третьего и четвертого элементов И первого и второго блоков местного управления, выходы первых элементов И первого и второго блоков местного управления соединены соответственно с первым и вторым входами второй групппы входов распределителя импульсов блока управления, выходы регистра адреса которого соединены с входами вторых дешифраторов адреса первого и второго блоков местного управления, выходы входных ключей каждогр коммутатора управляющих сигналов первой группы подключены к информационным входам ключей второй группы первого блока местного управления выходы ключей первой группы которого соединены с информационными входами регистра вывода каждого коммутатора управляющих сигналов первой группы, третий и четвертый выходы второй группы выходов распределителя импульсов первого блока местного управления соединены с вторыми входами соответственно первого и второго элементов И каждого коммутатора управляющих сигналов первой группы, второй - (Н+1)-й входы второй группы входов распредели теля импульсов первого блока местного управления соединены с выходами треть их элементов И соответствующих коммутаторов управляющих сигналов первой группы, выходы регистров адреса первого блока местного управления .соединены с входами второго дещифратора адреса каждого коммутатора управляюш х сигналов первой группы, выходы входных ключей коммутаторов управляющих сигналов второй и третьей групп подключены к информационным входам ключей второй группы второго блока местногр управления, выходы ключей первой группы которого соединены с информационными регистров вывода каждого коммутатора управляющих сигналов второй и третьей групп третий и четвертый выходы распределителя импульсов второго блока местного управления соединены с вторыми входами соответственно первого и второго элементов И каждого коммутатора управляющих сигналов второй и третьей групп, второй - (2Ы+1)-й входы второй группы входов распределителя импуль3 16 сов второго блока местного управления соединены с выходами третьих элементов И соответствующих коммутаторов управляющих сигналов второй и третьей групп, выходы регистра адреса второго блока местного управления соединены с входами вторых дешифраторов адреса каждого коммутатора управляющих сигналов второй и третьей групп, выходы информационных ключей, выходы адресных ключей, выходы управляющего ключа и выход триггера каждого i-ro (i t, N) узла коммутации коммутатора данных соединены соответственно с вторыми входами элементов И шестой группы, вторыми входами элементов И пятой группы, вторым входом второго элемента И, вторым входом второй группы входов распределителя импульсов, входом элемента НЕ, с первым входом второго элемента И, с первыми входами элементов И -пятой и шестой групп решающего блока исходного шага и суперпозиции, информационные входы информационных ключей, информационные входы адресных ключей, информационный вход управляющего - ключа, управляющий вход дешифратора адреса, информационный вход триггера каждого i-ro узла коммутации коммутатора данных соединены соответственно с выходами ключей первой группы, выходами регистра адреса, с первым выходом второй группы выходов распределителя импульсов, с третьим выходом второй группы выходов распределителя импульсов, с выходами ключей первой груйпы j N-fr2i блока подготовки суперпозиции, пятьй вькод распределителя импульсов каждого решающего блока исходного шага и суперпозиции соединен с вторым входом второй группы входов распределителя импульсов соответствующего блока подготовки суперпозиции. На фиг. 1 представлена структурная схема устройс.твй; на фиг. 2 решающий блок исходного шага и суперпозиции; на фиг. 3 - решающий блок половинного шага; на фиг. 4 - решающий блок подготовки суперпозиции; на фиг. 5 - узел коммутации; на фиг. 6 - блок управления; на фиг.7, 8 - блок местного управления; на фиг. 9 - коммутатор управляющих сигналов; на фиг. 10 - временная диаграмма работы устройства; на фиг. 11 буфер ввода-вывода решаюших блоков; на фиг. 12 - буфер ввода-вывода блоков управления; на фиг. 13 - алгоритм работы решающих блоков (1-3N) для метода простой итерации; на фиг. 14 алгоритм расчета суперпозиции для решающих блоков (1-N). Устройство (фиг. 1) содержит блок ввода-вывода, блок 2 управления, блоки 3, , 32 местного управления, первую группу коммутаторов 4j( управляющи сигналов, вторую группу коммутаторов К + 1 NM кн сигналов, третью группу коммутаторов 4,,2 N+4 М управляющих сигналов, N решающих блоков 5 5yj исходного шага и суперпозиции, N решаюищх блоков 5ц, щ + з м половинного шага, N блоков Зц 5н ..., 5lj подготовки cvпepпoзиции, коммутатор 6 данных, который содержит узлы коммутации 7 - 7ц, системные выходные информационные 8, систе мные входные информационные шины 9, системные выходные управляющие шины 1 системные входные управляющие шины 11,, 11 л системные адресные шины 12 выходные информационные игины 13, 13, входные информационные шины 14, 14, выходные управляющие шины 15, 15,2,.входные управляющие шины 16,, 1 адресные шины 17,, 172. группу выходов 18, группу адресных выходов 19, выходы 20 записи в память и захвата, вход 21 подтверждение захвата, группу входов 22, группу адресных входов 23, входы Z4 записи в память и захвата 24, выход 25 подтверждения захвата узла 7. Решающий блок (фиг.2 и 11) исходного шага и суперпозиции содержит регистр 26 результата итерации, распределитель 27- импульсов, регистр 28 левой точки, дешифратор 29 команд, регистр 30 коэффициента, сум матор 31, регистр 32 команд, счетчик 33 команд, регистр 34 правой точки, буфер 35 ввода-вывода (группу элементов И 35, 352, группу элементов ИЛИ 35, группу ключей 35, 35), регистр 36 адреса, узел 37 памяти, элемент ИЛИ 38j| , группу элементов ИЛИ 382, элемент НЕ 39, элемент И 40, , 40 , группу элементов И 40,-40 Решаюш 1Й блок (фиг. 3 и 11) половинного шага содержит регистр 41 результата итерации, распределитель 42 импульсов, регистр 43 левой точки, дешифратор 4 команд, регистр 45 коэффициента, сумматор 46, регистр 47 команд, счетчик 48 команд, регистр 4 правой точки, буфер 50 ввода-вывода (группу элементов И 50, , 50,, группу элементов ИЛИ 50, группу ключей 50,, 50.-), регистр 51 адреса, узел 52 памяти. Решающий блок (фиг. 4 и 11) подготовки суперпозиции содержит регистр 53 результата итерации, распределитель 54 импульсов, регистр 55 левой точки, дешифратор 56 команд, регистр 57 коэффициента, сумматор 58, регистр 59 команд, счетчик 60 команд, регистр 61 правой точки, буфер 62 ввода-вывода (группу элементов И 62, 62, группу элементов ИЛИ 62-j, группу ключей 624, 62), регистр 63 адреса, узел 64 памяти. Узел 7 коммутации коммутатора данных 6 (фиг. 5) содержит дешифратор 65 адреса, триггер 66, элемент И 67, группу информационных ключей 68, группу адресных ключей 69, управляющий ключ 7СГ. Блок 2 управления (фиг. 6 и 12) содержит узел 71 памяти, регистр. 72 адреса, буфер 73 ввода-выво- . да (группу ключей 73, 732), счетчик 74 команд, регистр 75 команд, буферный регистр 76, дешифратор 77 команд, распределитель 78 импульсов. Блок 3 местного управления (фиг. 7, 8 и 12) содержит узел 79 памяти, ре- гистр 80 адреса, буфер 81 ввода-вывода (группу ключей 81., 81), счетчик 82 команд, регистр 83 команд, буферный регистр 84, дешифратор 85 команд, распределитель 86 импульсов, второй элемент И 87, первый дешифратор 88 адреса, первый элемент И 89, выходные ключи 90, регистр 91 ввода, регистр 92 вьтода,входные ключи 93,четвертый элемент И 94, третий элемент И 95, второй дешифратор 96 адреса. Коммутатор управляющих сигналов 4 (фиг. 9) содержит регистр 97 вывода, группу ВЫХОДНЫХ ключей 98, первый элемент И 99, четвертый элемент И 100, группу входных ключей 101, регистр 102 ввода, второй элемент И 103, первый дешифратор адреса 104, второй дешифратор адреса 105, третий ; элемент И 106. Устройство работает следующим образом. В исходном состоянии устройство подготовлено к работе, т.е. в узел 71 памяти блока 2 управления записаны через устройство 1 ввода управляющие программы, в узел 7У памяти блоков 3, и 32 местного управления, запи саны блоком 2 управления управляющие программы, массивы коэффициентов, начальные и граничные условия, а в уз19лах 37t 52, 64 памяти решающих блоков.5j- 5;}|j+ записаны управляющие программы. Рассмотрим работу устройства на примере решения одновременного ура нения параболического типа зи : ,, 6Гa7 заданного на единичном отрезке (О X 1), аппроксимируемого мето дом конечных разностей: и|;;2игчиг иГ-и Исходную область G(0 и х крываем сеткой cOj,. Расчет на последовательности сеток (0| е W J, иО, позволяет получить в узлах сетки соц решение с требуемой точностью. Суммарное количество узлов в сетке СО,, , чем в сетке (л . и С0и1„ меньше Решение задачи включает следующи этапы. 1). Решение задачи (2) с шагом V. Н (например, методом простой итерации), в результате получаем .2). Решение задачи (2) с шагом V Н/2 (например, методом простой терации), в результате получаем 3). Нахождение суперпозиции полу ченных решений: uKiSr-iu (3) Формулы метода простой итерации И(т40 Ui где m - номер итерации; (WM ,(,„М)1,. CITI+O где с. - невязка. Этапы 1 и 2 выполняются соответственно в первой группе решающих блоков 5к исходного шага и супе позиции и во второй группе решающих блоков -5,,. которая содержит решающие блоки половинного Шага и решаюпще блоки подготовки суперпози ции. Этап 3 выполняется в первой (Группе. 1320 Для реализации описанного алгоритма по командам блока 2 управления блоки 3( и 3 местного управления по собственным программам параллельно загружают исходную информацию (коэффициенты, значения граничных условий) в соответствующую группу; в первый решающий блок 5 - для первой группы и в решающий блок для второй группы. Для этого блок 3 местного управления выдает по шинам 17, 13, 15 соответственно адрес, данные и управляющий сигнал Запись УВВ (ЗП УВВ). В коммутаторе 4 управляющих сигналов, к которому адресуется блок 3 местного управления, срабатывает дешифратор 104 адреса (фиг. 9), с выхода которого активный сигнал совместно с активным сигналом ЗП УВВ поступают на входы элемента И 99. По сигналу с выхода элемента И 99 передаваемая информация с шин 13 записывается в регистр 97 вывода и одновременно через первый выход запроса коммутатора 4 сигнал Запрос поступает в решающий блок 5 (распределитель импульсов) . По сигналу Запрос решающий блок 5 переходит на подпрограмму чтения информации из регистра 97 вывода. Для этого решающий блок 5 выставляет на адресных выходах адрес коммутатора 4 управляющих сигналов, который поступает на вход дешифратора 105 адреса, а по шине ЧТ УВВ - активный сигнал. По совокупности активных сигналов на входе элемента И 100 выходные ключи 98 подключают выходы регистра 97 к информационным входам решающего блока 5 и информация записывается через буфер 35 ввода-вывода в регистр 26 результата итерации, а затем запоминается в узле 37 памяти. Последний командой передаваемого массива блок 3 местного управления запускает решающий блок 5 на вьтолнение функциональной программы по решению одномерной задачи (по формуле 4). Для этого передается в решающий блок 5 код, соответствующий передаче управления, и адрес перехода (подобный алгоритм работы блока 5 приведен на фиг. 13, где УП - узел памяти 37, 52, 64; РЛТ - регистр левой точки 28, 43, 55; РПТ - регистг правой точки 34, 49, 61; РК - регистр коэффициента 30, 45, 57; РР - регист / результата 26, 41, 53; С - сумматор 31, 46, 58). Затем блоки местного управления 3 и 3 гтереключаются соответственно через коммутаторы управляющих сигналов Д и к входам решающих блоков 52 и 5., загружают исходной информацией и передают управление ре шающим блокам 5, которые начинают со ственную программу, а в это время блоки 3,( и 3 местного управления переключаются каждый в своей группе к следующему блоку 5 и, таким образом, все N решающих блоков 5 первой группы со смещением во времени парал лельно выполняют программы первого итерационного цикла. Количество решающих блоков 5 по второй группе (3N+1) - N, поэтому блок местного управления продолжает загружать оставшиеся решающие блоки 5, которые аналогично первой группе выполняют программы первого итерационного цикл После того как выполнено решение в любом из решающих блоков 5 в перво итерационном цикле, решающий блок 5 сообщает об этом блоку местного упра ления. Для этого решающий блок 5 выставляет по адресным шинам адрес ком мутатора А управляющих сигналов, кот рый поступает на вход дешифратора 10 по информационным шинам передает дан ные, которые по управляющему сигналу ЗП УВВ и сигналу с выхода дешифратора 105 записываются в регистр 102, а коммутатор 4 управляющих сигналов формирует сигнал Запрос, который по шине 16 передается в блок 3 местного управления, который переходит на подпрограмму чтения, включающую выдачу по шинам 17 адреса коммутатора 4, который поступает на вход дешифратора 104, и управляющего сигнала ЧТ УВВ по шине 15. По активному сигналу с выхода элемента И 103 информа ция с регистра 102 через ключи 101 поступает по информационным шинам 14 через буфер ввода-вывода 81 в буферный регистр 84 блока 3, а затем записывается в узел 79 памяти. Далее принимаются полученные на первой ите рации значения из остальных блоков 5 Е буферную область памяти блока мест ного управления. Блоки 3, и 3 местного управления не дожидаясь окончания вычисления во всех блоках 5, отслеживают окончание работы соседних блоков 5 и как только результат оказьгоается в буферной области осуществляют перезагрузку 1322 полученной информации и соседние освободившиеся решатощие блоки 5 для выполнения следующей итерации, в то время как остальные блоки 5 заканчивают, текущую итерацию. Таким образом, последовательно оставшиеся блоки 5 переходят к выполнению следующей итерации. Описанный итеративный процесс повторяется в каждой группе до тех пор, пока будут получены искомой функции текущего временного слоя для каждого узла с заранее заданной-точностью (в соответствии с формулой 5). Для нахождения суперпозиции полученных решений значения функции, полученные во второй группе из решающих блоков 5 подготовки суперпозиции. пересылаются в решающие блоки 5 исходного шага и суперпозиции через узлы 7 - 7щ . В решающих блоках 5 т З выполняется программа нахождения суперпозиции по формуле (3). Полученные значения функций в первой группе являются искомыми, а также исходными для расчета поля на следующем временном слое с шагом Н. В то время как выполняется программа нахождения суперпозиции в первой группе (подробно алгоритм расчета суперпозиции приведен на фиг. 14), блок 3 местного управления приступает к расчету поля с шагом Н/2 для следующего временного слоя (фиг. 10). Рассмотрим более подробно передачу информации из решающего блока 5 подготовки суперпозиции (фиг. 5). Передающий блок 5 устанавливает триггер 66 в единицу. Для этого на адресных входах 23 узла 7 выставляется адрес триггера 66, который поступает на вход дешифратора 65 адреса и, кроме того, на стробирующий вход дешифратора 65 поступает с входа 24 узла 7 управляюпщй сигнал ЗП УВВ. Выход триггера 66 формирует сигнал Захват (ЗЛХВ), который через выход 20 узла 7 поступает на вход принимающего блока 5. В случае готовности решающий блок исходного шага и суперпозиции 5, выставляет сигнал Подтверждение захвата (ПЗАХВ). По сигналу ПЗАХВ(выход 25 узла 7) передающий блок 5 из собственного узла 64 памяти через входы 22-24 узла 7, ключи 68-70, которые по сигналу с выхода элемента И 67 переключаются на передачу, выходы 18-20 узла 7 пересылают полученные значения функции

23110451324

в узел 37 памяти принимающего реша- Таким образом, введение новых фунющего блока 5.кциональных блоков и связей позволяет

Описанная последовательность по- повысить производительность устройства вторяется до тех пор, пока не закон- за счет распараллеливания вычислительчится время моделируемого процесса. s ного процесса в решающих блоках.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения дифференциальных уравнений | 1982 |

|

SU1108460A1 |

| Устройство для решения дифференциальных уравнений | 1983 |

|

SU1233148A1 |

| Устройство для решения дифференциальных уравнений | 1985 |

|

SU1348854A1 |

| Устройство для решения дифференциальных уравнений | 1982 |

|

SU1134949A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для решения дифференциальных уравнений | 1983 |

|

SU1233149A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для решения дифференциальных уравнений | 1985 |

|

SU1330635A1 |

| Устройство для решения нелинейных краевых задач | 1987 |

|

SU1683028A1 |

УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ДИФ- . ФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ, содержащее блок управления, N решающих блоков исходного шага и суперпозиции и первую группу из N коммутаторов управляющих сигналов, каждый решающий блок исходного шага и суперпозиции содержит регистр результата итерации, распределитель импульсов, регистр левой точки, дешифратор команд, регистр, коэффициента, сумматор, регистр команд, счетчик команд, регистр правой точки, две группы ключей, шесть групп элементов И, три группы элементов ИЛИ, регистр адреса, узел памяти, элемент ИЛИ, элемент НЕ, два элемента И, причем первый выход первой группы выходов распределителя импульсов решающего блока исходного шага и суперпозиции соединен с входом синхронизации регистра коэффициента решающего блока исходного шага и суперпозиции, второй выход первой группы выходов распределителя импульсов решающего блока исходного шага и суперпозициисо счетным входом счетчика команд решающего блока исходного шага и суперпозиции, третий выход первой группы выходов распределителя импульсов решающего блока исходного шага и суперпозиции - с входом синхронизации р.егистра адреса решающего блока исходного шага и суперпозиции, четвертый выход первой группы выходов распределителя импульсов решающего блока исходного шага и суперпозиции - с управляющими входами ключей первой группы решающего блока исходного шага и суперпозиции, пятый выход первой группы выходов распредели9 теля импульсов решающего блока исходного шага и суперпозиций - с первыми входами элементов И первой группы решающего блока исходного шага и суперпозиции, шестой выход первой группы выходов распределителя импульсов решающего блока исходного шага и суперпозиции - с первыми входами элементов И второй группы решающего блока исходного шага и суперпозиции, седьмой выход первой группы выходов распределителя импульсов решающего блока исходСЛ ного шага и суперпозиции - с управляющими входами ключей второй группы решающего блока исходного шага и 00 суперпозиции, восьмой выход первой группы выходов распределителя импульсов решающего блока исходного шага и суперпозиции - с входом синхронизации регистра команд решающего блока исходного шага и суперпозиции, девятый выход первой группы выходов распределителя импульсов решающего блока исходного шаг-а и суперпозиции с входом синхронизации регистра результата итерации решающего блока ис

I I

Рг-резулд та ит рации

i 1

г

Регистр Jtedou movKu j

CyMMamoL T

Рг. точки tf9

Данные

Данные

Адрес

I

3

Распреде

житель

импульсоб

UZ

Рг Kom0t циента U5

CvemvuK

Рг. команд «7 копана 48

lUuHbt

Регистр адреса 52

Узел поняты

t i

«D

фиг.З

252 2522

Решаюший fjtoff подготооки суперпозиции ), Sfff), , 5f3N)

7 /(Offffymamopa

19

20

-,

70

69

J

68

г

гГ

65

2S

2

puz5

.

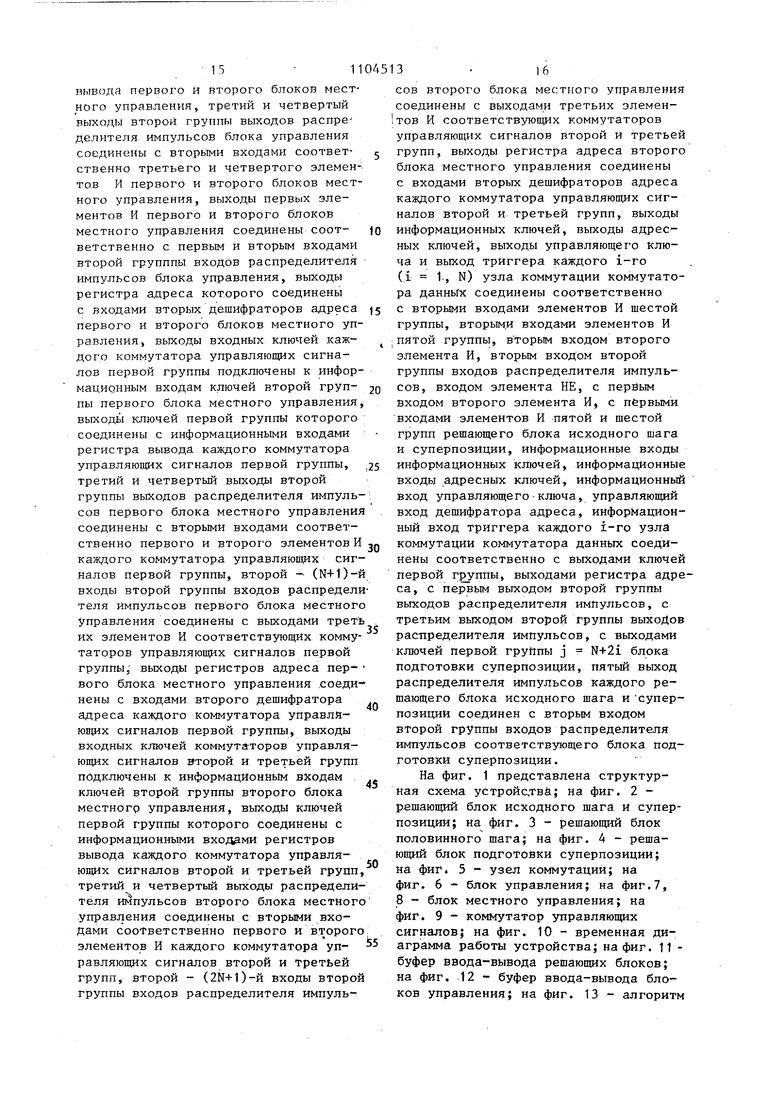

8,

2

2J

фия,6

/J 1 15 W17

ffft/z.

gjntr ittenntoto yi MitteMufS

Лонные

Ш

I Pr Ц

f

т

Pr

т

IS

16 f

lOS

17

&

зпувв

106

Запрос

Фиг. 9

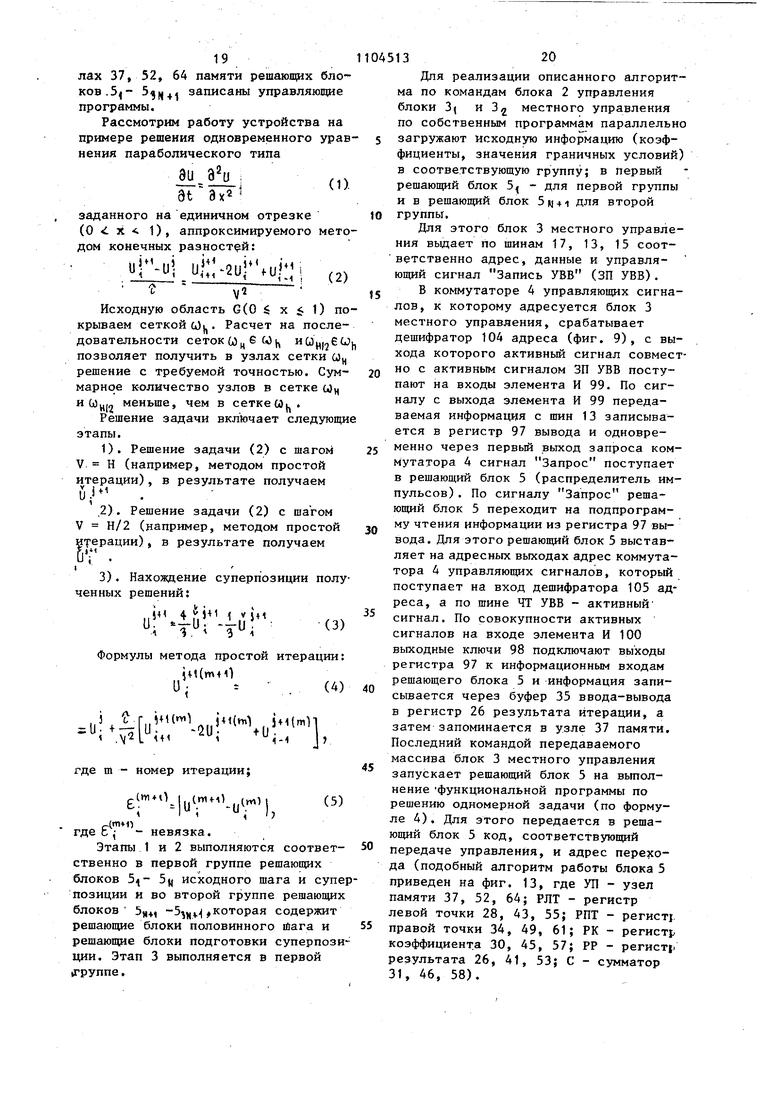

Шины ввода-вь/Ма

I

I Г

ч

Фш.12

буфер oooS(k

ы

&

по

, fff

ъ

108

Фиг11

Фиг. 13

Фиг. 14

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Вычислительная система для решения дифференциальных уравнений | 1975 |

|

SU620980A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Вычислительная система для решения дифференциальных уравнений | 1975 |

|

SU565299A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-23—Публикация

1982-07-15—Подача