1

Изобретение относится к вычислительной техник-е, в частности к за,- .поминающим устройствам (ЗУ) динамического типа, может быть использовано в различных .цифровых вычислительных машинах, системах сбора и обработки данных, системах отображения информации и является усовершенствованием устройства по. основному авт.св. W 1019493,

Цель изобретения - повышение надежности устройства.

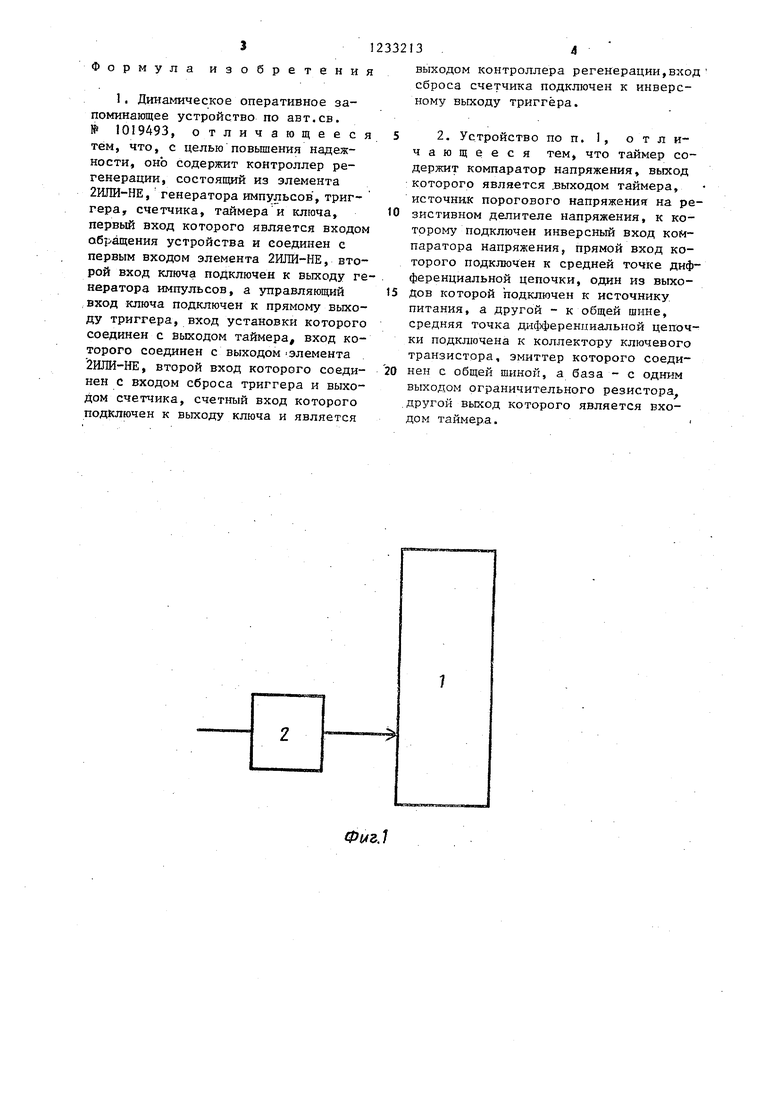

На фиг, 1 изображена структурная схема предлагаемого устройства, на фиг. 2 - структурная схема контроллера регенерации и пример конкретной реализации таймера. .

Устройство содержит динамическое запоминающее устройство (ДЗУ) 1 и контроллер 2 регенерации. Контроллер 2 регенерации сод,ер}кит электронный ключ 3, элемент 2ИЛИ-НЕ 4, гене- ратор 5 импульсов, триггер 6, таймер 7 и счетчцк 8, Таймер 7 представляет собой компаратор на- пряжения, выход которого является выходом таймера. На инверС1ШЙ вход компаратора .подается пороговое напряжение с резистивного делителя 9 напряжения, а на прямой вход - экспоненциально возрастающее напряжение с.о средней точки последовательно включенной RC-цепи, вывод резистора fкоторой подключен к источнику 10 питания, а вывод конденсатора 11 - к общему проводу. Средняя точка этой RC-цепи подключена, кроме того, к коллектору ключевого транзисто ра 12 эмиттер которого подключен к общему проводу, а база через ограничительный резистор 13 к выходу элемента 2ИЛИ-НЕ 4,

В качестве элемента 2ИЛИ-НЕ 4, триггера 6, счетчика 8, генератора 5 могут быть использованы логические элементы интегральных микросхем например, 564 серии, Электроншй ключ 3 легко реализуется на ключах той же серии, Hanpimep 564КТЗ, В качестве таймера 7 может использоватьс интегральный таймер КР1006БИ1 или он может быть реализован с использованием дискретных элементов и компаратора напряжения, например, 521 САЗ Устройство работает следующим образом.

При частоте обращения, удовлетворяющей условию регенерации, т.е. пе

2332132

«

риод обращения в M-N раз меньше периода регенерации (М - число строк накопителя, например, 128 у 565 РУЗ| N - число групп накопителей) при ус5 ловии обращения к данному ЗУ или период обращения в М раз меньше периода регенерации при условии обращения к другим ЗУ, импульсы обращения, про- ходят через элемент 2Ш1И-НЕ 4, открыtO вают транзистор таймера, конденсатор RC-цепи периодически разряжается и напряжение на нем не превышает пороговое, таким образом, таймер 7 не вырабатывает импульс установки триг13 гера 6,, и сигнал с прямого выхода

триггера 6 устанавливает ключ 3 в состояние, при котором импульсы обращения поступают на ДЗУ , и регенерация и обращение к ДЗУ I осуществля20 ется таким же образом, как и в из- BecTHoivf устройстве, ИнверсньШ сигнал с выхода триггер 6 удерживает счет-i чик 8 в нз левом состоянии.

При остановке процессора или в случаях, когда частота поступления сигналов обращения меньше, чем необходимо дпя регенерации, конденсатор таймера 7 успевает зарядиться до по- poroBoi o напряжения, и при превышении порогового напряжения компаратор таймера вырабатывает сигнал, устанав-. ливающк:й триггер б в состояние, со- ответствукадее прохождени о импульсов

с генератора 5 через ключ 3 на ДЗУ I и счетный вход счетчика 8, который в этом случае начинает счет, так как сигнал с инверсного выхода триггера 6 разрешает счет. При поступлении

на вход счетчика 8 необходимого числа импульсов (число импульсов равно числу строк нако;аителя ДЗУ с максимальным чиепом строк) сигнал с выхода счетчика 8 сбрасывает триггер 6

п,. проходя через элемент 2ИЖ-НН; 4 на таймер 7, переводит его в исходное состоя:иие, разрялсая через резистор 2 конденсатор I. Ключ 3 пере- кгаочается и разрешает прохо;кдение на

ДЗУ 1 сигналов обращения, а инверсный сигнал с Егыхода триггера 6 запрещает счет счетчику 8

Таккг-; образом, контроллер регене- рации обеспечивает регенерацию ДЗУ I в pejKi-гмах останова в случаях, когда частота обрапгений ниже допустимой, что повышает надежность устройства.

Формула изобретения

1, Динамическое оперативное запоминающее устройство по авт.св. № 1019493, отличающееся тем, что, с целью повышения надежности, оно содержит контроллер регенерации, состоящий из элемента 2ИЛИ-НЕ, генератора импульсов , триггера, счетчика, таймера и ключа, первый вход которого является входом обращения устройства и соединен с первым входом элемента 2ШШ-НЕ, второй вход ключа подключен к выходу генератора импульсов, а управляющий .вход ключа подключен к прямому выходу триггера, вход установки которого соединен с выходом таймера, вход которого соединен с выходом элемента 2Ш1И-НЕ, второй вход которого соединен с входом сброса триггера и выходом счетчика, счетный вход которого подключен к выходу ключа и является

выходом контроллера регенерации,вход сброса счетчика подключен к инверсному выходу триггера.

2. Устройство по п. 1, отличающееся тем что таймер содержит компаратор напряжения, выход которого является .выходом таймера, источник порогового напряжения на резистивном делителе напряжения, к которому подключен инверсный вход компаратора напряжения, прямой вход которого подключен к средней точке дифференциальной цепочки, один из выхоДов которой подключен к источнику питания, а другой - к общей шине, средняя точка дифференциальной цепочки подключена к коллектору ключевого транзистора, эмиттер которого соедийен с общей тнноп, а база - с одним выходом ограничительного резистора другой выход которого является входом таймера.

0t/IZ.l

.2

Редактор О.Бугир

Составитель В.Гордонова

Техред И.Гайдош Корректор М.Максимишинец

Заказ 2777/54 Тираж 543Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

-----------...

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Цифровой измеритель температуры | 1982 |

|

SU1111038A1 |

| Устройство управления динамической памятью | 1990 |

|

SU1735858A1 |

| Импульсный понижающий стабилизатор постоянного напряжения | 1990 |

|

SU1786477A1 |

| Устройство для динамической балансировки лучом лазера роторов | 1983 |

|

SU1130753A2 |

| ЯЧЕЙКА ПАМЯТИ | 2002 |

|

RU2222100C2 |

| Электропривод | 1990 |

|

SU1830611A1 |

| Устройство для динамической балансировки роторов | 1984 |

|

SU1173214A1 |

| Устройство для управления памятью | 1983 |

|

SU1151975A1 |

| Цифровой генератор синусоидальных колебаний | 1984 |

|

SU1292167A1 |

Изобретение относится к области вычиолительной техники, в частности к запоминающим устройствам динамического типа, и может быть использовано в цифровых вычислительных машинах, системах сбора и обработки данных, системах отображения информации. Целью изобретения является повьшение надежности устройства. Устройство содержит блок памяти и контроллер регенерации, который содержит ключ, элемент 2 ИЖЬНЕ, генератор импульсов, триггер, таймер и счетЧик, Контроллер регенерации обеспечивает ре- генЬрациго динамического запоминающего устройства в случаях, когда частота обращений ниже допустимой. I з.п. ф-лы, 2 ил. ю 00 00 ND 14)

| Динамическое оперативное запоминающее устройство | 1982 |

|

SU1019493A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-05-23—Публикация

1982-10-10—Подача