мент ИЛИ, элемент И-НЕ, причем вход сброса сдвигового регистра подключен к входу запуска формирователя, тактовый ах/од которого подключен к синхровходу регистра сдвига, выходы первого, второго, третьего и четвертого разрядов сдвигового регистра подключены к первому и второму входам эле- , мента ИЛИ и элемента И-НЕ соотве:тственно, выход элемента ИЛИ подключен к входу преобразователя уровней напря1151

75

жения и первому входу элемента И, второй вход которого подключен к выходу элемента И-НЕ и выходу сброса по концу регенерации, группы выходов сигналов внутренней синхронизации формирователя, выходы преобразовате-ля уровней напряжения И элемента И подключены к выходам селектирования и строба адреса группы выходов сигналов внутренней синхронизации формирователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Контроллер динамического оперативного запоминающего устройства | 1987 |

|

SU1442995A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Устройство для отображения информации | 1989 |

|

SU1741123A1 |

| УСТРОЙСТВО ДЛЯ РЕГЕНЕРАЦИИ ИНФОРМАЦИИ ДИНАМИЧЕСКОЙ ПАМЯТИ | 1992 |

|

RU2049363C1 |

| Устройство для отображения информации | 1984 |

|

SU1354182A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ОТЛАДОЧНОЕ УСТРОЙСТВО ДЛЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2016 |

|

RU2634197C1 |

| Устройство для управления динамической памятью | 1987 |

|

SU1524089A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1352477A1 |

| Измеритель частоты | 1989 |

|

SU1691768A1 |

| Микропроцессорная система для программного управления технологическим оборудованием | 1988 |

|

SU1525678A1 |

1. УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПАМЯТЬЮ, содержащее первый и второй элементы ИЛИ, триггер, счетчик адресов регенерации, селектор строк регенерации и формирователь тактовых сигналов, причем первый вход первого элемента ИЛИ подключен к входу сброса устройства, информационный вход триггера подключен к входу синхронизации устройства, выход триггера подключен к первому входу второго элемента ИЛИ, группа выходов счетчика адресов регенерации подключена к первой группе информационных входов селектора строк регенерации, вторая группа информационных входов которого подключена к группе адресных входов устройства, группа выходов селектора строк регенерации подключена к группе адресных выходов устройства, группа выходов формирователя тактовьпс сигналов подключена к группе выходов сигналов внутренней синхронизации устройства, выход сброса по концу регенерации формирователя тактовёгх сигналов подключен к входу сброса триггера, вход запуска Формирователя тактовых сигналов объединен с входом разрешения выдачи счетчика адресов регенерации и управляющим входом селектора строк регенерации, отличающееся тем, что, с целью уменьшения потребляемой мощности, в него введены делитель частоты, элемент И и компаратор, причем вход разрешения делителя частоты подключен к выходу первого элемента ИЛИ, второй вход которого подключен к входу блокировки-готовности устройства, первый тактовый вход делителя частоты подключен к первому тактовому входу устройства, вход сброса делителя частоты подключен к входу .триггера, , к входу синхронизации которого подклю-:2 чен вход управления синхронизацией (О устройства, выход делителя частоты подключен к второму входу второго элемента ИЛИ, выход которого подключен к первому входу элемента И, выход которого подключен к входу разрешения вьщачи счетчика адресов регенерации, вход разрешения вцдачи комсл паратора подключен к выходу триггера, первая группа информационных входов с ы компаратора подключена к группе выходов счетчика адресов регенерации, О1 вторая группа информационных входов компаратора подключена к группе адресных входов устройства, выход компаратора подключен к второму входу . элемента И, синхровход формирователя тактовых сигналов является тактовым входом устройства. 2, Устройство по п. 1, отличающееся тем, что формирователь тактовых сигналов содержит сдвиговый регистр, преобразователь уровней напряжения, элемент И, эле

Изобретение относится к вычислительной технике, а именно к микропроцессорным системам с динамическим ОЗУ и может быть использовано к отладочных микро-ЭВМ с шаговым режимом работы.

Известен автономный контроллер регенерации информации динамического ОЗУ для микропроцессор1ных систем, содержащий таймер, арбитр, селектор адреса строки, счетчик адресов регенерации, формирователь управляющих сигналов, буферы. С приближением момента обязательной регенерации таймер формирует запрос поступающий на арбитр. Б зависимости от занятости ОЗУ запрос удовлетворяется арбитром либо по окончании обращения процессора, либо немедленно. ,Ф1Я этого через селектор адреса строки разрешается прохождение адреса очерёдной регенери.руемой строки, сформированного счетчиком, в соответствующие разряды системной шины адреса. Одновременно формирователь управляющих сигналов обеспечивает подачу к ОЗУ сигналов, необходимых для его регенерации. По окончании цикла регенерации селектор строк восстанавливает связь системной шины адреса с соответствующими адресными разрядами процессора; содер жимое счетчика адресов регенерации инкрементируется ГЛ .

Недостатком автономного контроллера регенерации является необходимость приостановки микропроцессора во время регенерации информации; эта приостановка, приводящая к снижению производительности, производится подачей запрещающего потенциала на линию Готовность микропроцессора.

Наиболее близким к предложенному является неавтономный, контроллер ре-генерации, содержащий селектор адреса строки,- счетчик адресов регенерации, формирователь управляющих сигналов, буферы 3J. Активация неавтономного контроллера регенерации производится по сигналу Синхронизация микропроцессора, стробирующего вьгаод им байта состояния в каждом машинном цикле.Поскольку в это время микропроцессор не может обращаться к ОЗУ , то регенерация очередной строки ОЗУ, производящаяся по сигналу Синхронизация, надежно развязана от конфликта с обращением процессора. Таким образом, сигнал Синхронизация в неавтономном контроллере выполняет роль таймера и арбитра автономного контроллера регенерации, тем самым исключая необходимость приостановки микропроцессора.

В неавтономном контроллере регенерации также предусмотрена резервная активация в случаях отсутствия сигнала Синхронизация, а именно при нахождении микропроцессора i в состоянии Ожидание и при общем сбросе микропроцессорной системы. В этих случаях запускающими являются тактовые синхроимпульсы Ф2 ТТЛ, безусловно генерируемые при наличии питания.

Недостатками неавтономного контроллера регенерации являются избыточная частота регенерации, приводяИ(ая к излишнему расходу мощности. и Невозможность реального использования, контроллера в состоянии Ожидание микропроцессорных систем в том числе при шаговом режиме рабо ты (например, в отладочных микроЭВМ) , Шаговый режим работы микропроцес сорных систем осуществляется посред ством периодической блокировки (подачей отрицательного потенциала) линии Готовность микропроцессора, в результате чего он -переходит в режим Ожидание, вьщавая соответ ствующий сигнал. Наличие сигнала Ожидание приводит к переходу неавтономного конт роллера в резервный режим циклов ре г.енерации, производящихся в каждом такте состояния Ожидание с поступ лением заднего фронта системных сии хроимпульсов Ф2 ТТЛ, инверсных по отношению к системным синхроимпульсам Ф2. Этим же фронтом синхроимпудьсов Ф2 микропроцессор опрашивает линию Готовность в каждом такте состояния Ожидание с тем, чтоб при восстановлении на нем сигнала Готовность возобновить работу .с началом следующего машинного такта ТЗ. Во время такта ТЗ обычно производится обмен информацией между микропроцессором и ОЗУ. Однако очередной цикл регенерации, длитель ность которого равна машинному такту микропроцессора, начинается в конце поеледяего такта состояния Оясидание перед тактом ТЗ и завершается только в конце такта ТЗ. Налицо возникновение конфликтной ситуации, когда обращение микропроцес сора к ОЗУ не может быть реализовано. Дель изобретения - уменьшение расходуемой мощности. Поставленная цель достигается тем, что в устройство для управлени память, содержащее первый и второй элементы ИЛИ, триггер, счетчик адресов регенерации, селектор строк регенерации и формирователь тактовых сигналов, причем первый вход первого элемента ИЛИ подключен к входу сброса устройства, информационный вход триггера подключен .к входу синхронизации устройства, выход триггера подключен к первому входу второго элемента ИЛИ, группа выходов счетчика адресов регенераци подключена к первой группе информационных входов селектора строк регенерации, вторая группа информационных входов которого подключена к группе адресных входов устройства, группа i выходов селектора строк регенерации подключена к группе адресных выходов устройства, группа выходов формирователя тактовых сигналов подключена . к группе выходов сигналов внутренней синхронизации устройства, выход сброса по концу регенерации формирователя тактовых сигналов подключен к входу сброса триггера, вход запуска формирователя тактовых сигналов объединен с входом разрешения вьщачи счетчика адресов регенерации и управлянмцим входом селектора строк регенерации, введены делитель частоты, элемент -И и компаратор, причем вход разрешения делителя частоты подключен к выходу первого элемента ИЛИ, второй вход которого подключен к входу блокировки готовности устройства, первый тактовый вход делителя частоты подключен к первому тактовому входу устройства, вход сброса делителя частоты подключен к входу триггера, к входу синхронизации которого подключен вход управления синхронизацией устройства, выход делителя частоты подключен к второму входу второго элемента ИЛИ, ВЕЛСОД которого подключен к первому входу элемента И, выход которого подключен к входу разрешения вьщачи счетчика адресов регенерации, вход разрешения выдачи компаратора подключен к выходу триггера, первая группа информационных входов компаратора подключена к группе: выходов счетчика адресов регенерации, вторая группа информационных входов компаратора подключена к группе адресных входов устройства, выход компаратора подключен к второму входу элемента И, синхровход формирователя тактовых сигналов является тактовым входом устройства. Кроме того, формирователь тактовых сигналов содержит сдвиговый регистр, преобразователь уровней напряжения, элемент И, элемент ИЛИ, элемент И-НЁ, причем вход сброса сдвигового регистра подключен к входу запуска формирователя, тактовьп1 вход которого подключен к синхровходу регистра сдвига, выходы пеового.

второго, третьего и четвертого разрядов сдвигового регистра подключены к первому и второму входам элемента ИЛИ и элемента И-НЕ соответственно, выход элемента ИЛИ подключен к входу преобразователя уровней напряжения и первому входу элемента И, второй вход которого подключен к выходу элемента И-НЕ и выходу сброса по концу регенерации, группы вьгеодов сигналов внутренней синхронизации .формирователя, выходы преобразователя уровней напряжения и элемента И подключены к выходам селектирования и строба адреса группы выходов сигналов внутренней синхронизации формирователя.

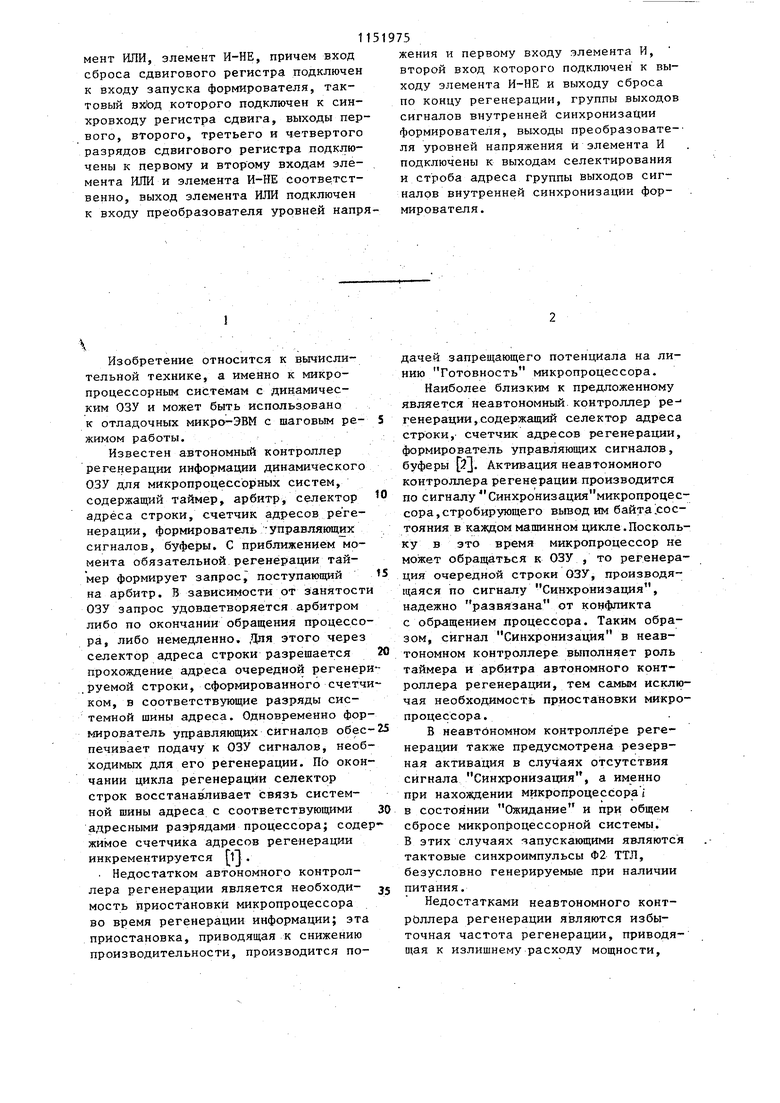

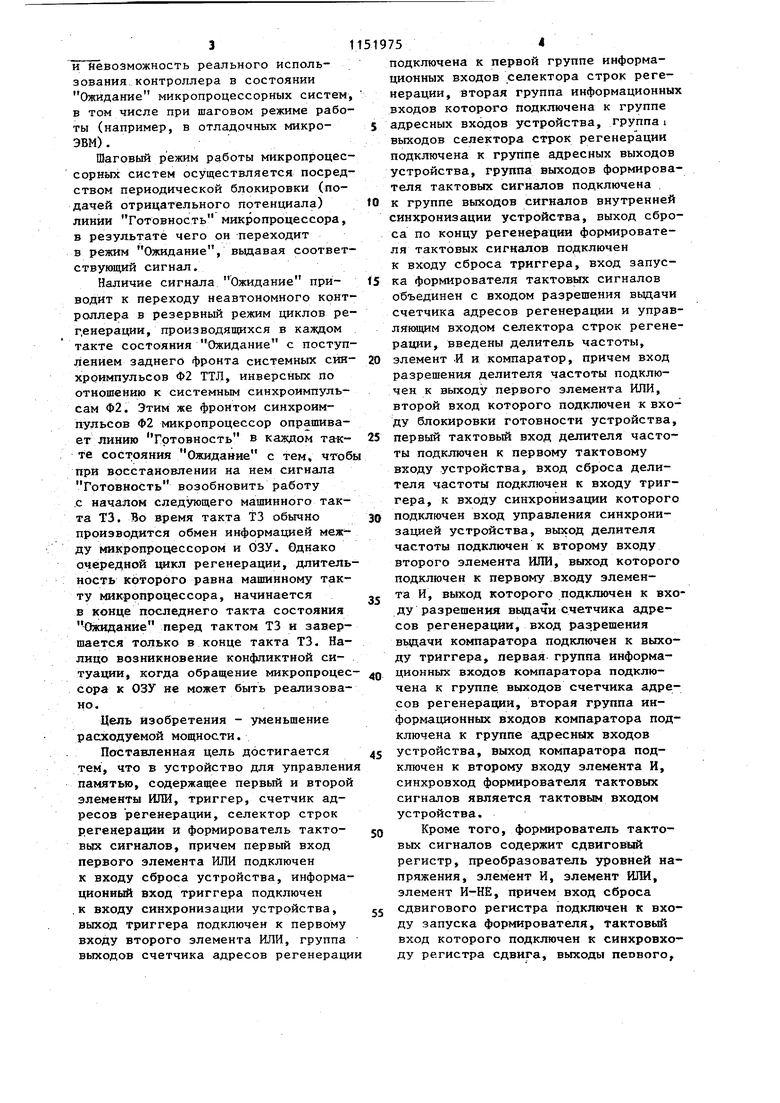

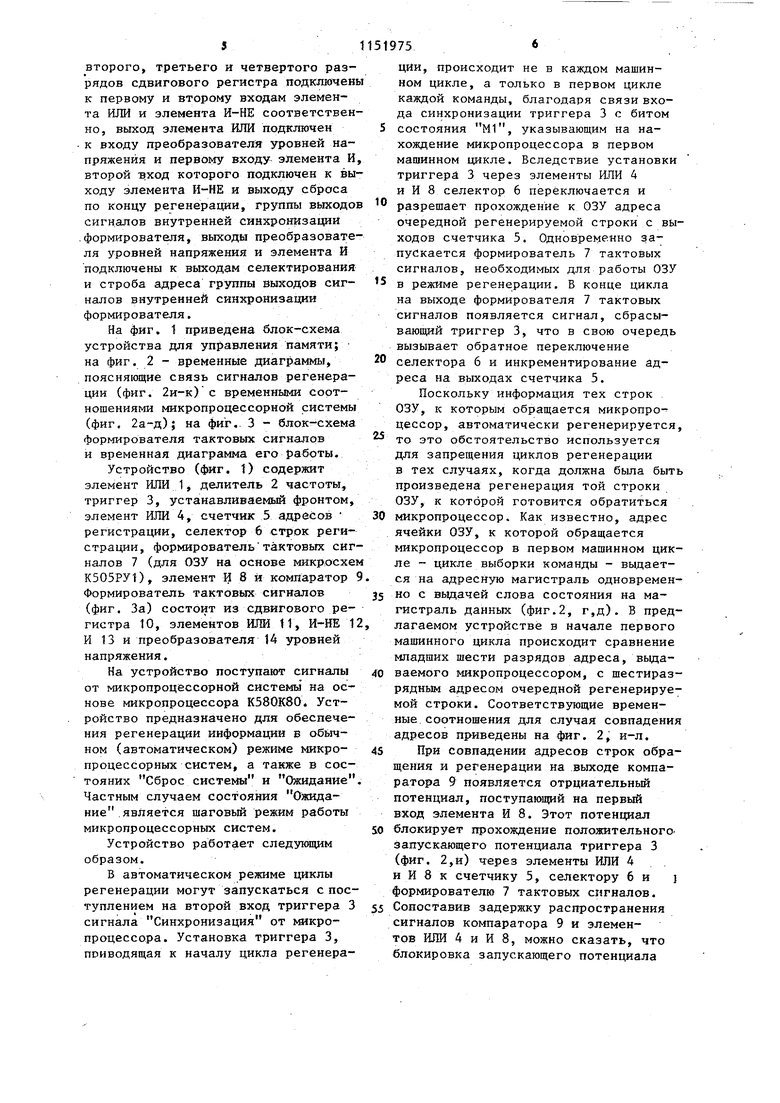

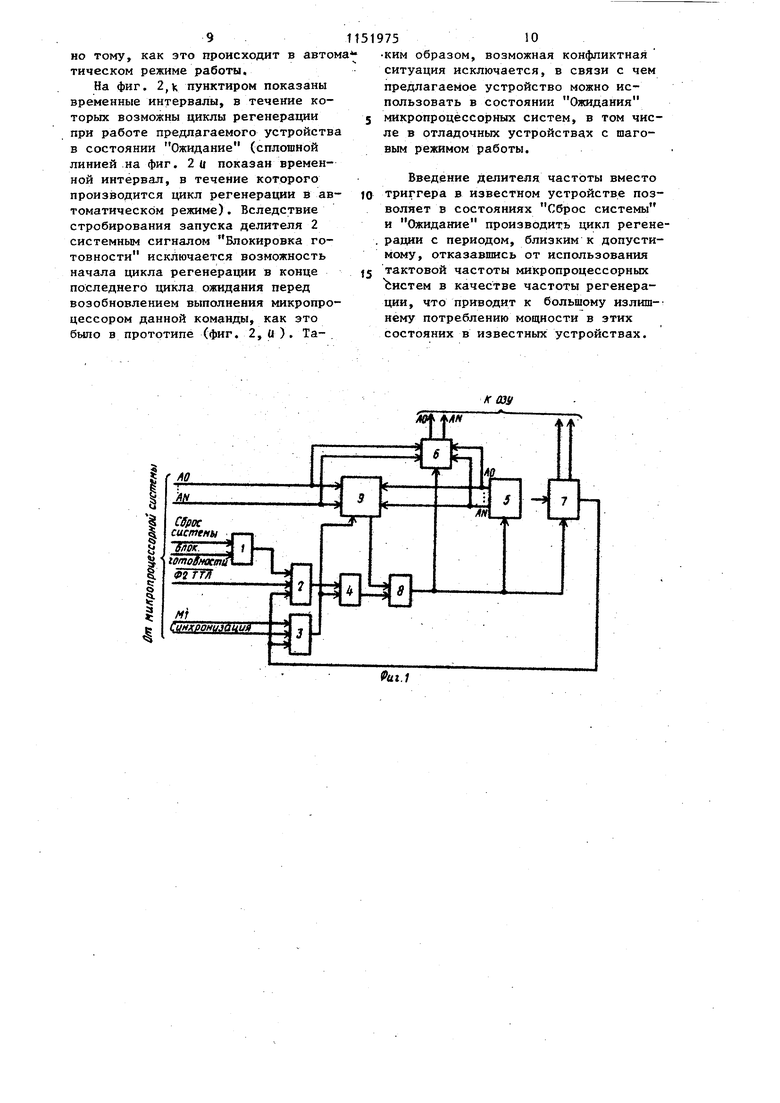

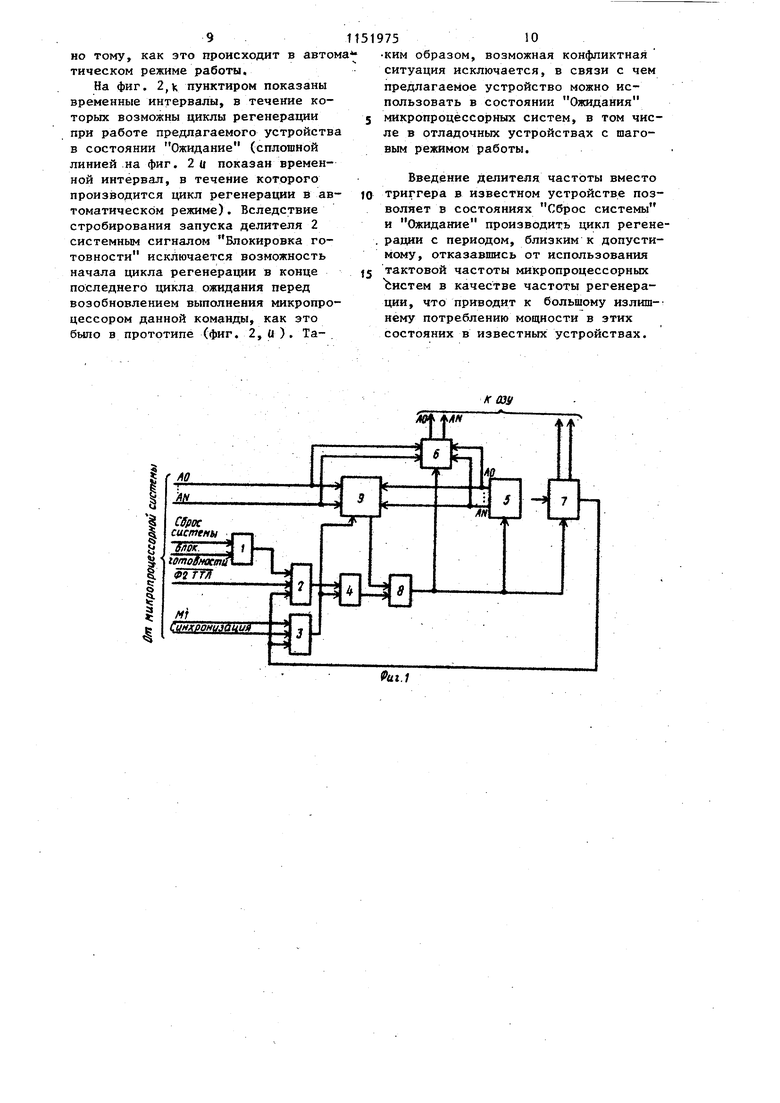

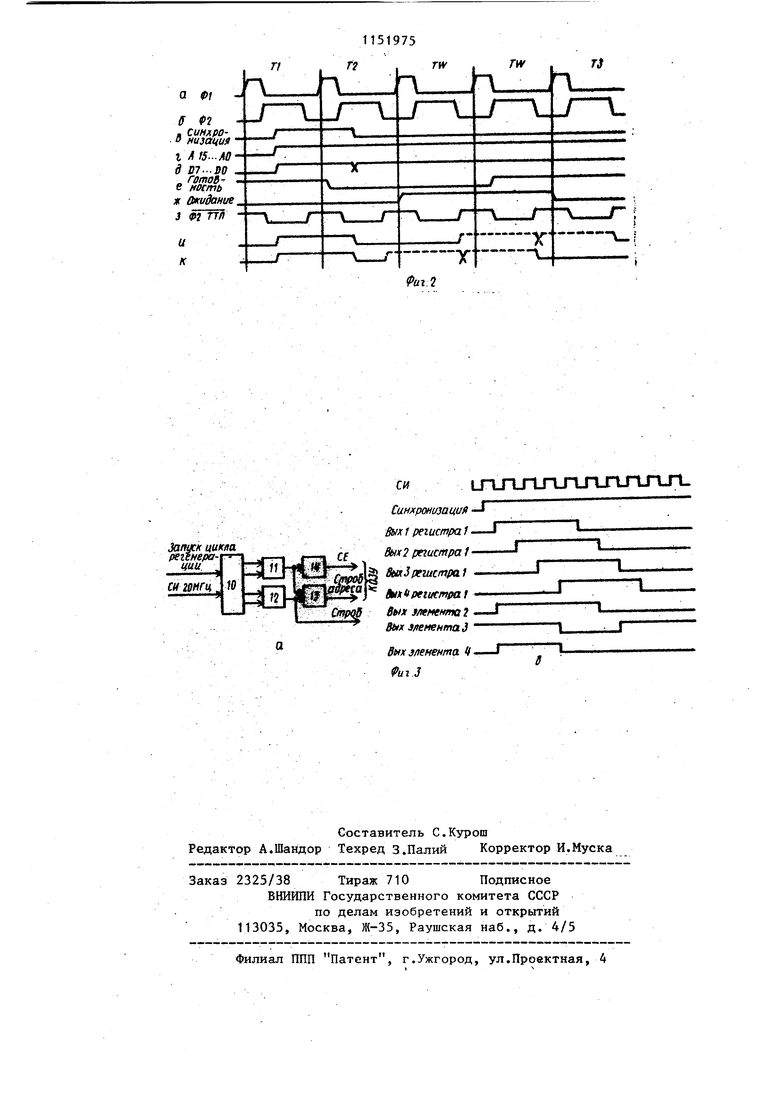

На фиг. 1 приведена блок-схема устройства для управления памяти; на фиг. 2 - временные диаграммы, поясняющие связь сигналов регенерации (фиг. 2и-к) с временными соотношениями микропроцессорной системы (фиг, 2а-д); на фиг.. 3 - блок-схема формирователя тактовых сигналов и временная диаграмма его работы.

Устройство (фиг. I) содержит элемент ИЛИ 1, делитель 2 частоты, триггер 3, устанавливаег лй фронтом, элемент ИЛИ 4, счетчик 5 адресов регистрации, селектор 6 строк регистрации, формировательтактовых сигналов 7 (для ОЗУ на основе микросхем К505РУ1), элемент И 8 и компаратор 9 Формирователь тактовых сигналов (фиг. За) состоит из сдвигового регистра 10, элементов ИЛИ t1, И-НЕ 12 И 13 и преобразователя 14 зФовней напряжения.

На устройство поступают сигналы от микропроцессорной системы на основе микропроцессора К580К80. Устройство предназначено для обеспечения регенерации информации в обычном (автоматическом) режиме микропроцессорных систем, а также в состояних Сброс системы и Ожидание. Частным случаем состояния Ожидание .является шаговый режим работы микропроцессорных систем.

Устройство работает следующим образом.

В автоматическом режиме циклы регенерации могут запускаться с поступлением на второй вход триггера 3 сигнала Синхронизация от кикропроцессора. Установка триггера 3, приводящая к началу цикла регенерации, происходит не в каждом машинном цикле, а только в первом цикле каждой команды, благодаря связи входа синхронизации триггера 3 с битом состояния М1, указывающим на нахождение микропроцессора в первом машинном цикле. Вследствие установки триггера 3 через элементы ИЛИ 4 и И 8 селектор 6 переключается и разрешает прохождение к ОЗУ адреса очередной регенерируемой строки с выходов счетчика 5. Одновременно запускается формирователь 7 тактовых сигналов, необходимых для работы ОЗУ в режиме регенерации. В конце цикла на выходе формирователя 7 тактовых сигналов появляется сигнал, сбрасывающий триггер 3, что в свою очередь вызывает обратное переключение селектора 6 и инкрементирование адреса на выходах счетчика 5.

Поскольку информация тех строк ОЗУ, к которым обращается микропроцессор, автоматически регенерируется то это обстоятельство используется для запрещения циклов регенерации в тех случаях, когда должна была быт произведена регенерация той строки ОЗУ, к которой готовится обратиться микропроцессор. Как известно, адрес ячейки ОЗУ, к которой обращается микропроцессор в первом машинном цикле - цикле выборки команды - выдается на адресную магистраль одновременно с вьщачей слова состояния на магистраль данных (фиг.2, г,д). В предлагаемом устройстве в начале первого машинного цикла происходит сравнение младших шести разрядов адреса, выдаваемого микропроцессором, с щестиразрядным адресом очередной регенерируемой строки. Соответствующие временные соотношения для случая совпадения адресов приведены на фиг. 2, и-л.

При совпадении адресов строк обращения и регенерации на выходе компаратора 9 появляется отрциательный потенциал, поступающий на первый вход элемента И 8. Этот потенциал блокирует прохождение положительного, запускакнцего потенциала триггера 3 (фиг. 2,и) через элементы ИЛИ 4 и И 8 к счетчику 5, селектору 6 и j формирователю 7 тактовых сигналов. Сопоставив задержку распространения сигналов компаратора 9 и элементов ИЛИ 4 и И 8, можно сказать, что блокировка запускающего потенциала несколько запаздывает, вследствие чего на выходе элемента И 8 появляется узкий импульс (фиг. 2, л) вместо полноценного широкого сигнала, образующегося при отсутствии совпаде ния адресов. Появление на выходе элемента И 8 узкого импульса не достаточно для выполнения селектором 6 и формирователем 7 своих функций во время цикла регенерации, поскольку для этого требуется наличие на выходе элемента И 8 нормального широкого сигнала Поэтому готовившийся цикл регенерации не будет осуществлен. По окончании заднего фронта импульса на вькоде элемента И В происходит инкрементирование значения счетчика 5, поэтому адресация строк ОЗУ для регенерации не будет нарушена, и в следующем цикле регенерации будет регенерирована (при отсутствии совпадения адресов) следующая строка. Как известно, для регенерации ОЗУ на основе микросхем К565РУ1 достаточна подача на эти ми росхемы 12-вольтного сигнала разрешения СЕ. При последовательном обращении к всем 64 строкам матрицы микросхемы формирователь 7 тактовых сигналов (фиг. 1) вырабатывает сигнал разрешения и сигнал строба адреса, посредством которого обеспечиваются необходимые временные соот ношения сигнала разрешения и адреса регенерируемой строки, поступающего к ОЗУ с выхода селектора 6 (фиг. 1) С началом цикла регенерации на первый вход (последовательного ввода информации) регистра 10 поступает сигнал логической 1 (с выхода эле мента И 8, фиг. 1). На второй вход (синхро) регистра 10 поступают синхроимпульсы частотой 20 МГц (фиг.Зб Под воздействием этих синхроимпульсов выходы регистра 10 начнут после довательно переключаться в состояни логической 1 (фиг. 36). На выходе элемента И-НЕ 12 образуется отрицательный сигнал сброса, подаваемый на третий вход триггера 3 (и делите ля 2, фиг. 1). Вследствие сброса триггера 3 на первый вход регистра (фиг. За) начнет поступать сигнал логического О (с выхода элемента ИВ,фиг, 1) ивыходы регистра 1 начнут последовательно переключаться в это логическое состояние (фиг.Зб). 758 Выходной сигнал элемента ИЛИ 11, проходя через преобразователь 14, превращается в 12-вольтовый сигнал разрешения СЕ. Выходной сигнал элемента И 13 используется дан временного стробирования адреса регенерируемой строки, поступающего к ОЗУ с выходов селектора 6 (фиг. 1). Запрет специальных циклов регенерации при совпадении адресов обращения и регеиерации приводит к дополнительной экономии потребляемой мощности. Однако основная экономия, обеспечиваемая предлагаемым устройством в автоматическом режиме, достигается благодаря осуществлению циклов регенерации не в каж,1ом машинном цикле, как в известном устройстве, а только в первом машинном цикле каждой команды. Каждая команда микропроцессора К580К80 может содержать от одного до пяти . Конкретная частота регенерации предлагаемого устройства определяется тем, какие команды входят в данную программу. В среднем по сравнению с -автоматическим режимом известного устройства частогРа регенерации снижена примерно в 3 раза. Современные динамические ОЗУ регенерируются за 64, 128 или 256 циклов регенерации. ОЗУ, требующие для полной регенерации 64 цикла, регенерировалась известньм устройством за 0,12-0,15 Vic при допустимом периоде регенерации 2 мс. Предлагаемое устройство в автоматическом режиме работы микропроцессорных систем производит 64 цикла регенерации (при ) за 0,40-0,45 мс, 128 циклов (при ) за 0,8-0,9 we, 256 циклов (при ) за 1,6-1,8-мС, что, обеспечивает существенное снижение потребляемой мощности . Рассмотрим работу предлагаемого устройства для управления памятью Сброс системы и Ожидание. При наличии одного из сигналов Сброс системы или Блокировка готовности (инверсии сигнала Готовность) с поступлением заднего фронта сигнала Ф2 ТТЛ, запускается делитель 2 частоты. Через временной интервал, определяемый коэффициентом деления частоты, на выходе делителя 2 появляется сигнал, запускающий цикл регенерации аналогич9

но тому, как это происходит в автом тическом режиме работы.

На фиг. 2,k пунктиром показаны временные интервалы, в течение которых возможны циклы регенерации при работе предлагаемого устройства в состоянии Ожидание (сплошной линией на фиг. 2u показан временной интервал, в течение которого производится цикл регенерации в автоматическом режиме). Вследствие стробирования запуска делителя 2 системным сигналом Блокировка готовности исключается возможность начала цикла регенерации в конце последнего цикла ожидания перед возобновлением выполнения микропроцессором данной команды, как это было в прототипе (фиг. 2, а). Та7510

КИМ образом, возможная конфликтная ситуация исключается, в связи с чем предлагаемое устройство можно использовать в состоянии Ожидания микропроцессорных систем, в том числе в отладочных устройствах с шаговым режимом работы.

Введение делителя частоты вместо триггера в известном устройстве позволяет в состояниях Сброс системы и Ожидание производить цикл регенерадаи с периодом, близким к допустимому, отказавшись от использования тактовой частоты микропроцессорных Ъистем в качестве частоты регенерации, что приводит к большому излшпнему потреблению мощности в этих состояних в известных устройствах.

а ф1

ff f2 , Синхронизация

г Л 15...АОд D7...SD . „ ГотоЬ , е ность

ж Ожидание . 3 ФГгП

Запуск цикял («гекера- ции

W

Ctf20Hrn

Синхронизации -J вкх 1 регистра J -- Вых 2 регистра f8ыя5 peutcmpu} iHiftt регистра I Вых Л№мента2 8ых э/кнентад

Внхзтнента if, fui3

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Коэевич О.П | |||

| и др | |||

| Применение динамических ОЗУ в микропроцессорных системах | |||

| - Вопросы радиоэлектрони и, сер | |||

| ЭВТ, 198t, вып | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| То же, с | |||

| Способ приготовления сернистого красителя защитного цвета | 1915 |

|

SU63A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-04-23—Публикация

1983-11-29—Подача