ЗРКО

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления динамической памятью | 1990 |

|

SU1777143A2 |

| Устройство для контроля микросхем оперативной памяти | 1983 |

|

SU1149312A1 |

| Устройство для управления динамической памятью | 1987 |

|

SU1524089A1 |

| Устройство сопряжения для контроля блоков памяти | 1991 |

|

SU1836723A3 |

| Устройство для контроля оперативных накопителей | 1989 |

|

SU1705873A1 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

| Устройство для управления регенерацией информации в динамической памяти | 1986 |

|

SU1377909A1 |

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ СИГНАЛОВ УПРАВЛЕНИЯ ДИНАМИЧЕСКОЙ ПАМЯТЬЮ ПРИ ЗАПИСИ ТЕЛЕВИЗИОННОГО СИГНАЛА | 1993 |

|

RU2092893C1 |

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

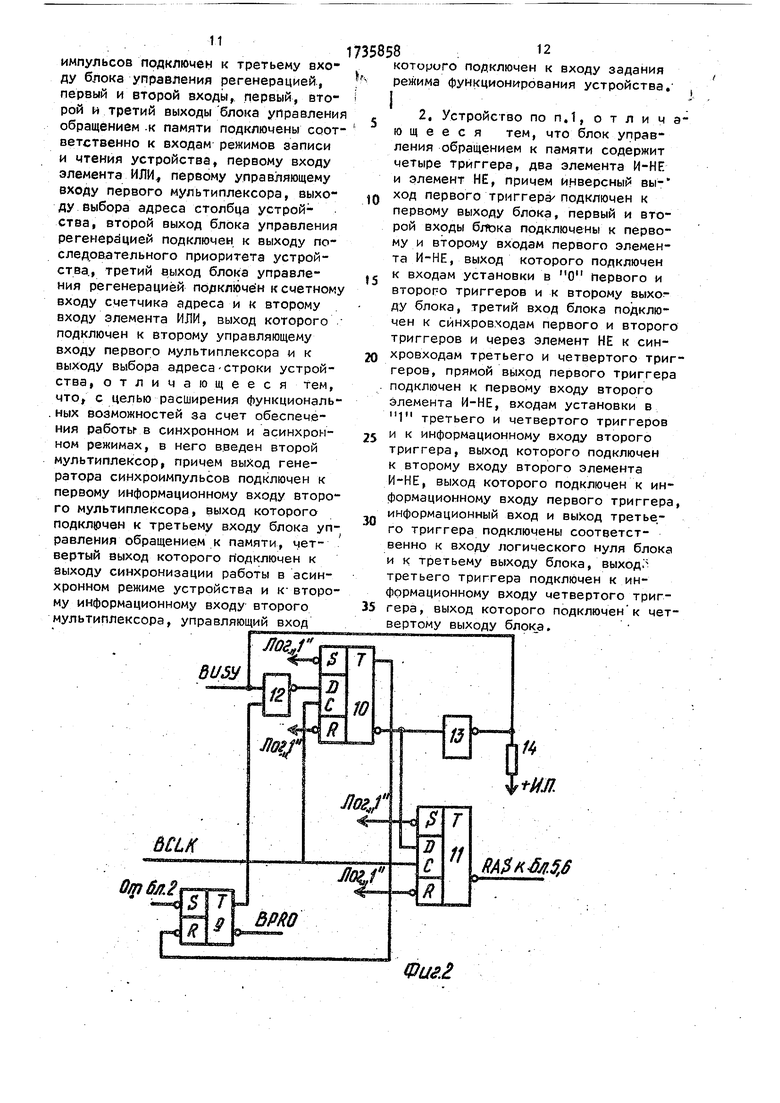

Изобретение относится-к вычислительной технике, в частности к устройствам управления оперативными запоминающими устройствами динамического типа. Цель изобретения - расширение функциональных возможностей. Устройство содержит генератор 1 синхроимпульсов, делитель 2 частоты, счетчик 6 адреса, элемент ИЛИ 5, блок 3 управления регенерацией, блок А управления обращением к памяти, мультиплексоры 7,- 8. Устройство обеспечивает работу как с синхронными, так и асинхронными магистралями, 1 з.п. ф-лы, 6 ил.

vj

00

ел

оо ел

00

ФЫ9.1

Изобретение относится к вычислительной технике и может быть исполь- зовано для управления памятью динамического типа.

Известен контроллер динамической памяти, содержащий счетчик адреса регенерации, подключенный к входу мультиплексора, формирователь управляющих сигналов, подключенный к входам сметчика адреса регенерации, управляющим входам мультиплексора и к выходу контроллера, причем входы формирователя управляющих сигналов, один из входов счетчика адреса регенерации и часть входов мультиплексора являются входами контроллера, а выход мультиплексора и часть выходов формирователя управляющих сигналов являются выходами контроллера.

Недостатками известного контроллера являются ограниченные функциональные возможности из-за отсутствия в контроллере механизма, позволяющег избежать конфликтных ситуаций при одновременном обращении к памяти нескольких активных устройств, низкое быстродействие, так как цикл регенерации и рабочий цикл-занимают равный период времени, хотя при регенерации памяти одним управляющим сигналом время регенерации можно сократить. Контроллер имеет повышенное потребление энергии, ток как регенерация, при которой потребляется- большое количество энергии., производится при отсутствии обращения к памяти не через определенные техническими условиями -интервалы времени, а постоянно с гораздо большей частотой.

Известен контроллер динамической памяти, содержащий тактовый генера-/ тор, подключенный к таймеру регенерации, арбитру запросов, схеме синхронизации, счетчик адреса регенерации, подключенный к выходу таймера регенерации, мультиплексор, подключенный к входу счетчика адреса регенерации, один из входов арбитра запросов подключен к выходу таймера регенерации, а выход - к входу схемы синхрониза- ции, выходы схемы синхронизации подключены к управляющим входам мультиплексора, причем выход и часть входов мультиплексора являются соответственно адресными выходами и входами контроллера, часть входов арбитра запросов является- управляющими входа ми контроллера, а часть выходов схе0

5

0

5

0

5

0

S

(

5

мы синхронизации - управляющими выходами контроллера.

Контроллер имеет ограниченные функциональные возможности, так как не может быть использован при большом числе устройств, напрямую работающих с памятью, из-за отсутствия механизма синхронизации работы устройств,, работающих с памятью, что может привести к потере информации или к конфликтным ситуациям на магистрали, когда несколько устройств одновременно обратятся к памяти.

Другим недостатком устройства является1 низкое быстродействие из-за использования общей схемы синхронизации для формирования сигнала управления памятью как в рабочем режиме, так и в режиме регенерации.

Наиболее близким по технической сущности к предлагаемому является устройство управления динамической памятью, содержащее генератор синхроимпульсов, делитель частоты, счетчик адреса, мультиплексор, блок управления обращением к памяти, блок управления регенерацией и элемент ИЛИ.

Известное устройство имеет ограниченные функциональные возможности из-за того, что управляется сигналами записи и чтения определенной длительности (2,5 или 3 такта), измеренной в тактах синхрочастоты, и не может работать в асинхронных магистралях или в синхронных магистралях, для которых длительности управляющих сигналов отличаются от указанной величины.

Целью изобретения является расширение функциональных возможностей за счет обеспечения работы в синхронном и асинхронном режимах

С этой целью в устройство управления динамической памятью, содержащее генератор синхроимпульсов, делитель частоты, счетчик адреса, элемент ИЛИ, первый мультиплексор, блок управления обращением к памяти и блок управления регенерацией, причем выход генератора синхроимпульсов- подг ключей к входу делителя частоты, первый , второй и третий информационные входы и выход первого мультиплексора подключены-соответственно к выходу счетчика адреса,, входу адреса строки устройства, входу адреса столбца устройства и к выходу устройства, первый

э

выход блока управления регенерацией подключен к входу-выходу признакаа занятости магистрали устройства и к первому входу блока управления регенерацией, второй вход которого подключен к выходу делителя частоты, выход генератора синхроимпульсов подключен к третьему входу блока управления регенерацией,. первый и второй входы, первый, второй и третий выходы блока управления обращением к памяти подключены соответственно к входам режимов записи и чтения устройства, первому входу элемента ИЛИ, первому управляющему входу первого мультиплексора, выходу выбора адреса столбца устройства, второй выход блока управления регенерацией подключен к выходу последовательного приоритета устройства, третий выход блока управления регенерацией подключен к счетному входу счетчика адреса и к второму входу элемента ИЛИ, выход которого подключен к второму управляющему входу первого мультиплексора и выходу выбора адреса строки устройства, введен второй мультиплексор, причем выход генератора синхроимпульсов подключен к первому информационному входу второго Мультиплексора, выход которого подключен к третьему входу блока управления обращением к памяти, четвертый выход которого подключен к выходу синхронизации работы в асинхронном режиме устройства и к второму информационному входу второго мультиплексора, управляющий вход которого подключен к входу задания режима функционирования устройства. Блок управления обращением к памяти содержит четыре триггера, два элемента и элемент НЕ, причем инверсный выход первого триггера подключен к выходу выбора адреса строки устройства, входы режимов записи и чтения устройства - к первому и второму входам первого элемента И-НЕ, выход которого подключен к входам установки в О первого и второго триггеров и к второму выходу блока., третий вход блока-подключен к синхровходам первого и второго триггеров и через элемент HF к синхровходам третьего и четвертого триггеров, прямой выход первого гера подключен к первому входу второго элемента И-НЕ, входам установки в I третьего и четвертого триггеров

358586

и к информационному входу второго триггера, выход которого подключен к второму входу второго элемента И- НЕ, выход которого подключен к информационному входу первого триггера, информационный вход и выход третьего триггера подключены соответственно к входу логического О блока и

JQ к третьему выходу блока, выход третьего триггера подключен к информационному входу четвертого триггера, выход которого подключен к четвертому выходу блока.

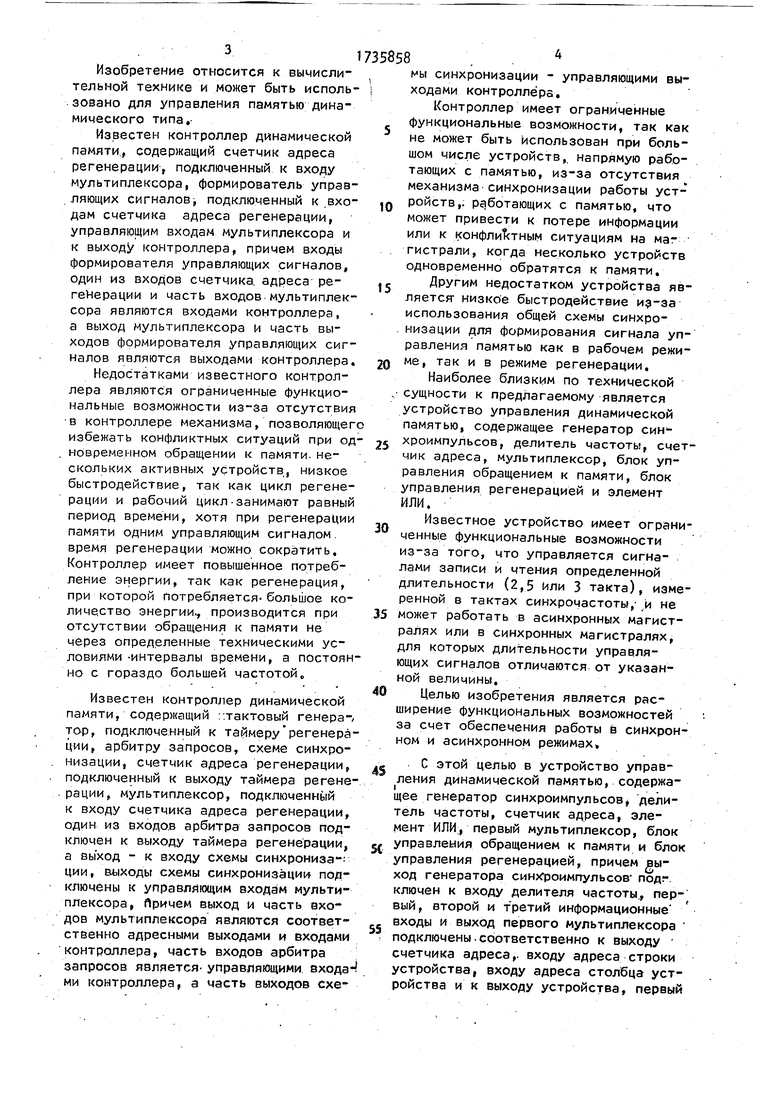

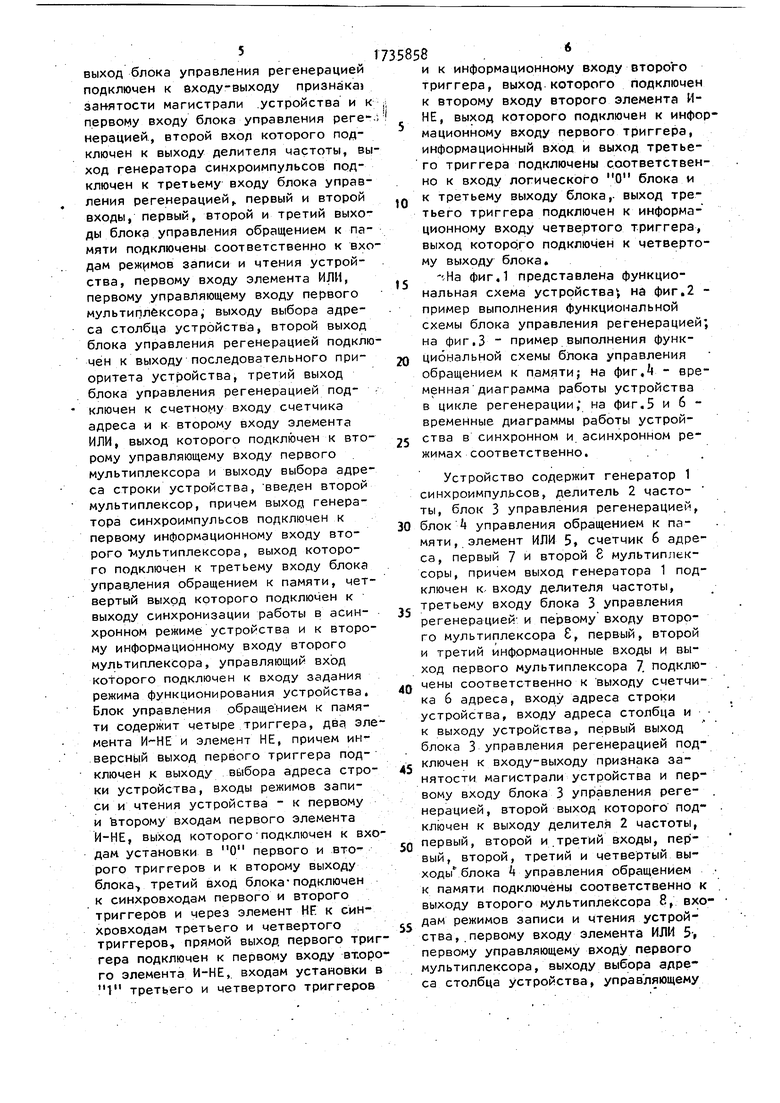

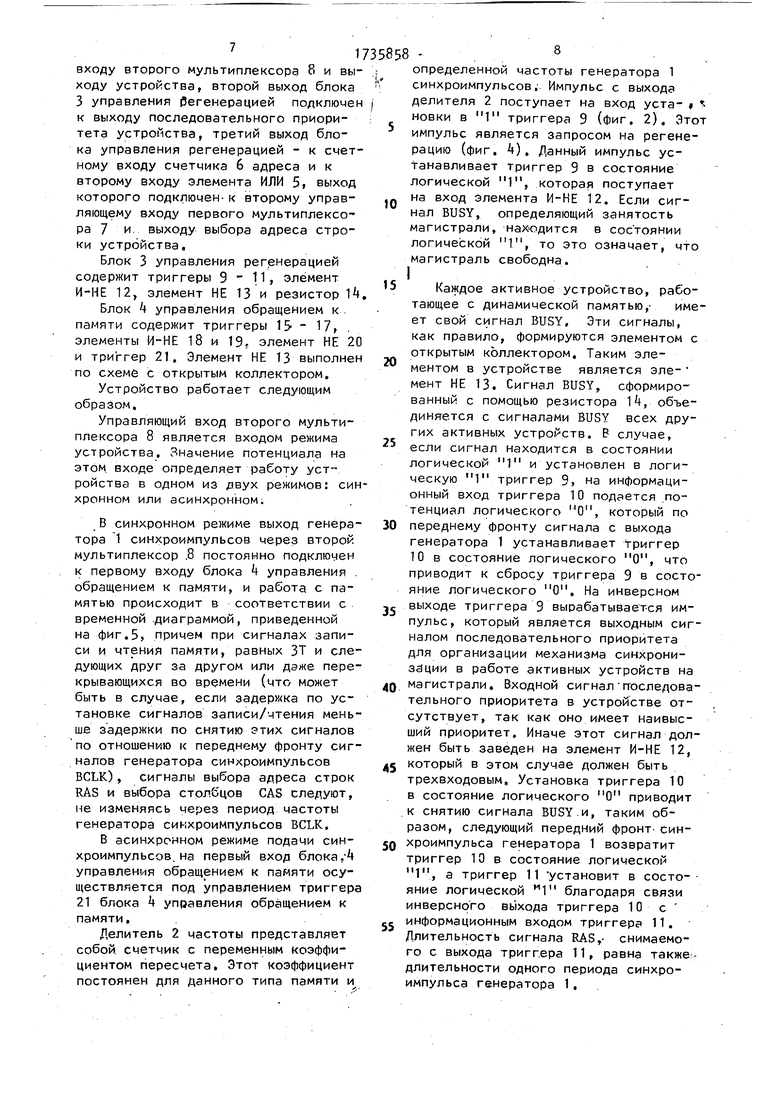

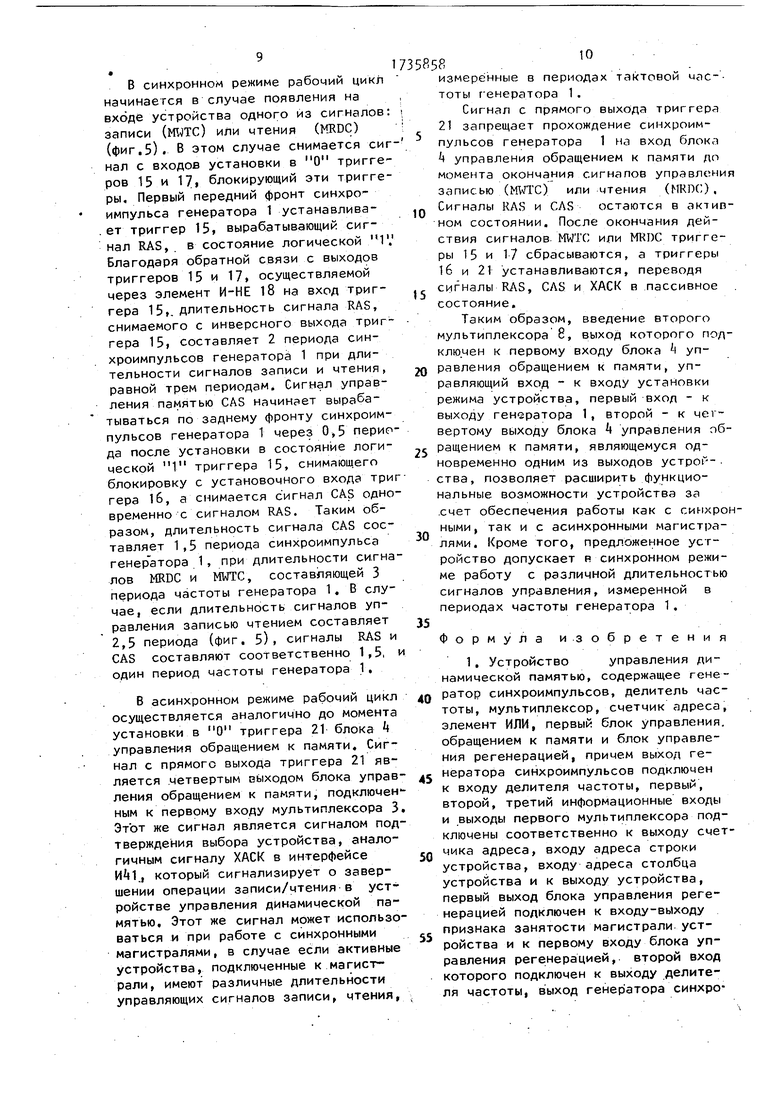

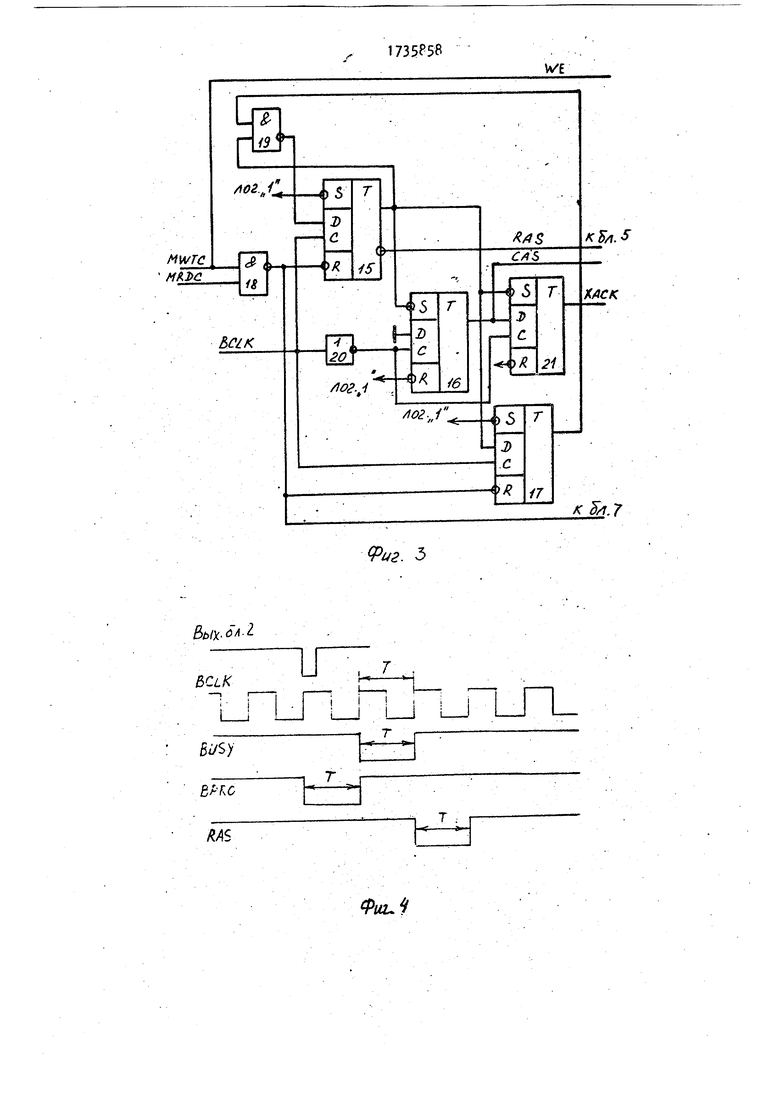

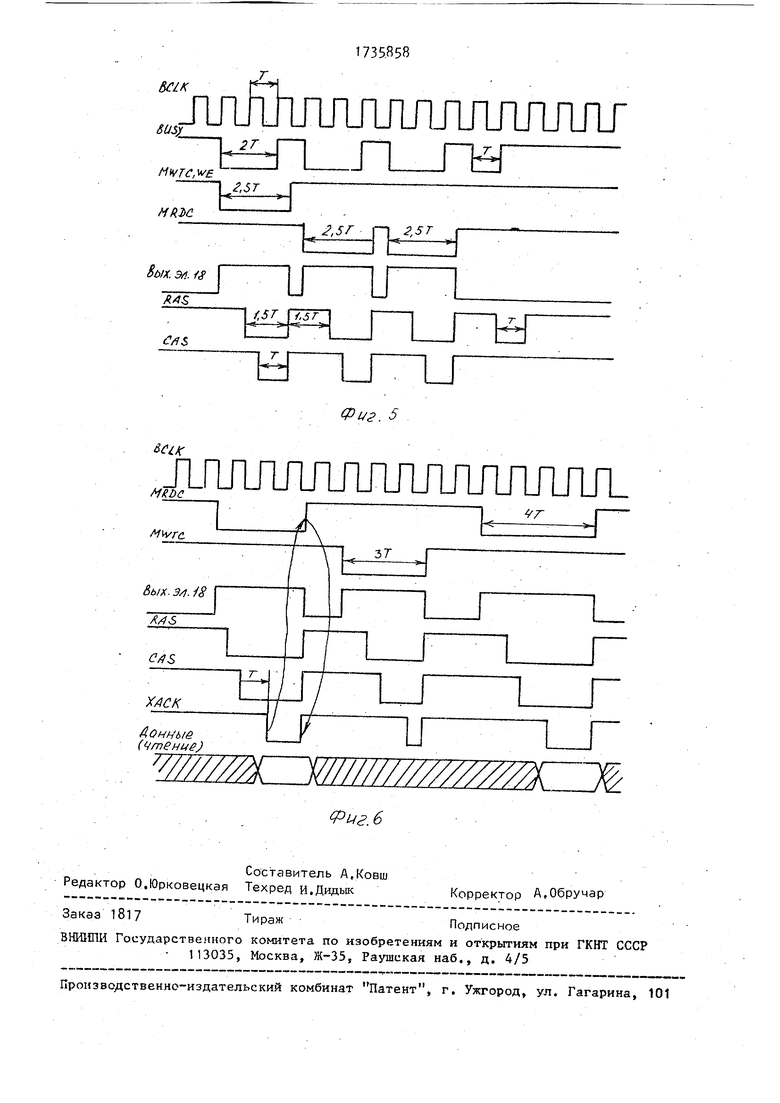

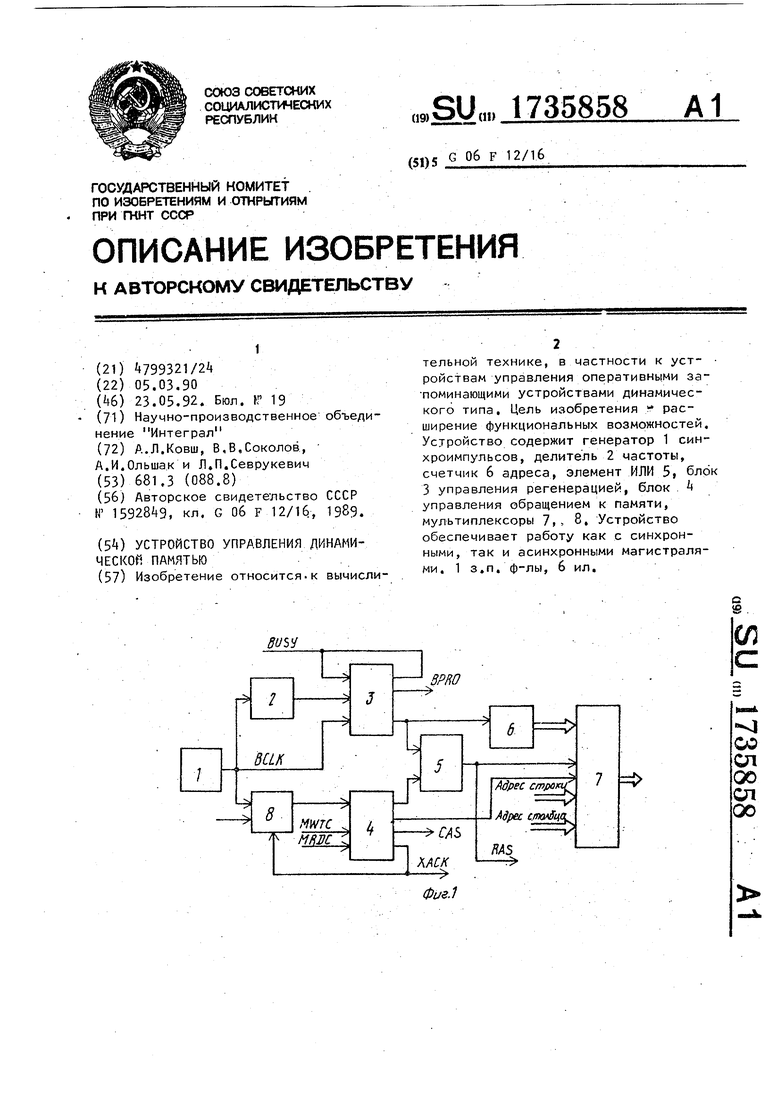

., -На фиг.1 представлена функциональная схема устройства , на фиг.2 - пример выполнения функциональной схемы блока управления регенерацией; на фиг.З - пример выполнения функ20 цибнальной схемы блока управления обращением к памяти; на фиг, - временная диаграмма работы устройства в цикле регенерации; на фиг.5 и б - временные диаграммы работы устрой25 ства в синхронном и асинхронном режимах соответственно.

Устройство содержит генератор 1 синхроимпульсов, делитель 2 часто- ты, блок 3 управления регенерацией,

30 блок управления обращением к памяти, элемент ИЛИ 5, счетчик 6 адреса, первый 7 и второй Б мультиплексоры, причем выход генератора 1 подключен к входу делителя частоты,

,д третьему входу блока 3 управления регенерацией и первому входу второго мультиплексора Ј, первый, второй и третий информационные входы и выход первого мультиплексора 7. подклюд0 чены соответственно к выходу счетчика 6 адреса, входу адреса строки устройства, входу адреса столбца и к выходу устройства, первый выход блока 3 управления регенерацией под.е ключей к входу-выходу признака занятости магистрали устройства и первому входу блока 3 управления реге- . нерацией, второй выход которого подключен к выходу делителя 2 частоты,

5Q первый, второй и третий входы, первый, второй, третий и четвертый выходы блока управления обращением к памяти подключены соответственно к выходу второго мультиплексора 8, вхо-

с дам режимов записи и чтения устройства, первому входу элемента ИЛИ 5, первому управляющему входу первого мультиплексора, выходу выбора адреса столбца устройства, управляющему

717

входу второго мультиплексора 8 и выходу устройства, второй выход блока 3 управления регенерацией подключен к выходу последовательного приори- тета устройства, третий выход блока управления регенерацией - к счетному входу счетчика 6 адреса и к второму входу элемента ИЛИ 5, выход которого подключен к второму управ- ляющему входу первого мультиплексора 7 и выходу выбора адреса строки устройства.

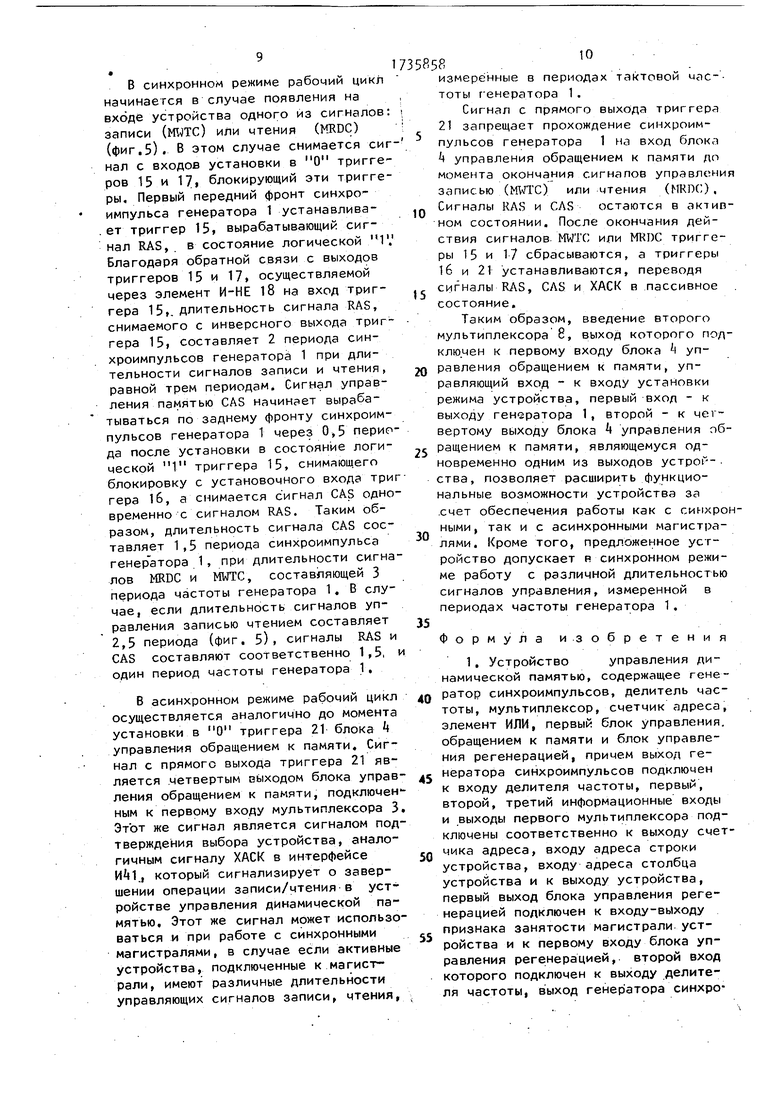

Блок 3 управления регенерацией содержит триггеры 9-11, элемент И-НЕ 12, элемент НЕ 13 и резистор Н

Блок k управления обращением к памяти содержит триггеры 15 - 17, элементы И-НЕ 18 и 19, элемент НЕ 20 и триггер 21, Элемент НЕ 13 выполнен по схеме с открытым коллектором.

Устройство работает следующим образом.

Управляющий вход второго мультиплексора 8 является входом режима устройства. Значение потенциала на этом входе определяет работу устройства в одном из двух режимов: синхронном или асинхронном.

В синхронном режиме выход генера- тора 1 синхроимпульсов через второй мультиплексор 8 постоянно подключен к первому входу блока 4 управления обращением к памяти, и работа с памятью происходит в соответствии с временной диаграммой, приведенной на фиг.5, причем при сигналах записи и чтения памяти, равных ЗТ и следующих друг за другом или даже перекрывающихся во времени (что может быть в случае, если задержка по установке сигналов записи/чтения меньше задержки по снятию этих сигналов по отношению к переднему фронту cni- налов генератора синхроимпульсов BCLK), сигналы выбора адреса строк RAS и выбора столбцов CAS следуют, не изменяясь через период частоты генератора синхроимпульсов BCLK.

В асинхронном режиме подачи син- хроимлульсов на первый вход блока,4 управления обращением к памяти осуществляется под управлением триггера 21 блока 4 управления обращением к памяти.

Делитель 2 частоты представляет собой счетчик с переменным коэффициентом пересчета. Этот коэффициент постоянен для данного типа памяти и

,

5

0 д

Q

5

5

определенной частоты генератора 1 синхроимпульсов. Импульс с выхода делителя 2 поступает на вход уста-« новки в 1 триггера 9 (фиг. 2), Этот импульс является запросом на регенерацию (фиг. 4). Данный импульс устанавливает триггер 9 в состояние логической 1, которая поступает на вход элемента И-НЕ 12. Если сигнал BUSY, определяющий занятость магистрали, находится в состоянии логической 1, то это означает, что магистраль свободна. I

Каждое активное устройство, работающее с динамической памятью, имеет свой сигнал BUSY. Эти сигналы, как правило, формируются элементом с открытым коллектором. Таким элементом в устройстве является эле- мент НЕ 13. Сигнал BUSY, сформированный с помощью резистора 14, объединяется с сигналами BUSY всех других активных устройств. В случае, если сигнал находится в состоянии логической 1 и установлен в логическую 1 триггер 9, на информационный вход триггера 10 подается потенциал логического О, который по переднему фронту сигнала с выхода генератора 1 устанавливает триггер 10 в состояние логического О, что приводит к сбросу триггера 9 в состояние логического О. На инверсном выходе триггера 9 вырабатывается импульс, который является выходным сигналом последовательного приоритета для организации механизма синхронизации в работе активных устройств на магистрали. Входной сигнал ггоследова- тельного приоритета в устройстве отсутствует, так как оно имеет наивысший приоритет. Иначе этот сигнал должен быть заведен на элемент И-НЕ 12, который в этом случае должен быть трехвходовым. Установка триггера 10 в состояние логического 0м приводит к снятию сигнала BUSY и, таким образом, следующий передний фронт синхроимпульса генератора 1 возвратит триггер 10 в состояние логической 1, а триггер 11 установит в состояние логической Т1 благодаря связи инверсного выхода триггера 10 с информационным входом триггера 11. Длительность сигнала RAS, снимаемого с выхода триггера 11, равна также длительности одного периода синхроимпульса генератора 1,

1

В синхронном режиме рабочий цикл начинается в случае появления на входе устройства одного из сигналов: записи (MWTC) или чтения (MRDC) (фиг.5). В этом случае снимается сигнал с входов установки в О триггеров 15 и 17| блокирующий эти триггеры. Первый передний фронт синхроимпульса генератора 1 устанавлива- .ет триггер 15, вырабатывающий сигнал RAS, в состояние логической 11.1 Благодаря обратной связи с выходов триггеров 15 и 17, осуществляемой через элемент И-НЕ 18 на вход триггера 15,. длительность сигнала RAS, снимаемого с инверсного выхода триггера 15, составляет 2 периода синхроимпульсов генератора 1 при длительности сигналов записи и чтения, равной трем периодам. Сигнал управления памятью CAS начинает вырабатываться по заднему фронту синхроимпульсов генератора 1 через 0,5 периода после установки в состояние логической 1 триггера 15, снимающего блокировку с установочного входа триг гера 16, а снимается сигнал CAS одновременно с сигналом RAS. Таким образом, длительность сигнала CAS составляет 1 ,5 периода синхроимпульса генер атора 1 , при длительности сигналов MRDC и MWTC, составляющей 3 периода частоты генератора 1. В случае, если длительность сигналов управления записью чтением составляет 2,5 периода (фиг. 5), сигналы RAS и CAS составляют соответственно 1,5, и один период частоты генератора 1.

В асинхронном режиме рабочий цикл осуществляется аналогично до момента установки в О триггера 21 блока Ь управления обращением к памяти. Сигнал с прямого выхода триггера 21 является четвертым выходом блока управления обращением к памяти, подключен - ным к первому входу мультиплексора 3. Этот же сигнал является сигналом подтверждения выбора устройства, аналогичным сигналу ХАСК в интерфейсе ., который сигнализирует о завершении операции записи/чтения в устройстве управления динамической памятью. Этот же сигнал может использоваться и при работе с синхронными магистралями, в случае если активные устройства, подключенные к магистрали, имеют различные длительности управляющих сигналов записи, чтения,

5

3585810

измеренные в периодах тактовой тоты генератора 1.

Сигнал с прямого выхода триггера 21 запрещает прохождение синхроимпульсов генератора 1 на вход Олокл А управления обращением к памяти до момента окончания сигналов управления записью (MWTC) или чтения (MRDC). JQ Сигналы RAS и GAS остаются в активном состоянии. После окончания действия сигналов MWTC или МКПС триггеры 15 и 17 сбрасываются, а триггеры 16 и 21 устанавливаются, переводя 5 сигналы RAS, CAS и ХАСК в пассивное состояние.

Таким образом, введение второго мультиплексора 8, выход которого подключен к первому входу блока i уп- 20 равления обращением к памяти, управляющий вход - к входу установки режима устройства, первый вход - к выходу генератора 1, второй - к четвертому выходу блока управления об- 25 ращением к памяти, являющемуся одновременно одним из выходов устройства, позволяет расширить функциональные возможности устройства за счет обеспечения работы как с синхронными, так и с асинхронными магистралями. Кроме того, предложенное устройство допускает Р синхронном режиме работу с различной длительностью сигналов управления, измеренной в периодах частоты генератора 1. 35

Формула изобретения

импульсов подключен к третьему входу блока управления регенерацией, первый и второй входы, первый, вто- рой и третий выходы блока управления обращением .к памяти подключены COOT- ветственно к входам режимов записи и чтения устройства, первому входу элемента ИЛИ, первому управляющему входу первого мультиплексора, выхо- ду выбора адреса столбца устройства, второй выход блока управления регенерацией подключен к выходу последовательного приоритета устройства, третий выход блока управления регенерацией подключён к сметному входу счетчика адреса и к второму входу элемента ИЛИ, выход которого подключен к второму управляющему входу первого мультиплексора и к выходу выбора адреса-строки устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения работы- в синхронном и асинхрои- ном режимах, в него введен второй мультиплексор, причем выход генератора синхроимпульсов подключен к первому информационному входу второго мультиплексора, выход которого подключен к третьему входу блока управления обращением к памяти, четвертый выход которого подключен к выходу синхронизации работы в асинхронном режиме устройства и к-второму информационному входу второго мультиплексора, управляющий вход

f

5

. JQ 20 25 35

30

которого подключен к входу задания режима функционирования устройства. (

i

&ЫУ..ОЛ Z

BCLK

BUS)

Фиг. 3

Фкг.

ШК

6U3L

Т

лҐ1Ш1;шлшшгшши1г

2Т

МУГС,ЫЕ

2,5Т

MWC

2,5 Г

Вых. э0. (У

MS

и и

Фиг. 5

,JlГLfШЛЯЛJlГLШlПЛШlГL

,

А

гт

Вых. э/1. i8

X/ICK

Аоиныб (чтение)

7

U

Фиг. 6

fb

2,5Т

чг

37

U

| Видоизменение печи, охарактеризованной в патенте № 1573 | 1929 |

|

SU15928A1 |

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

| ( УСТРОЙСТВО УПРАВЛЕНИЯ ДИНАМИЧЕСКОЙ ПАМЯТЬЮ | |||

Авторы

Даты

1992-05-23—Публикация

1990-03-05—Подача