1чЭ

со

4 00 ел

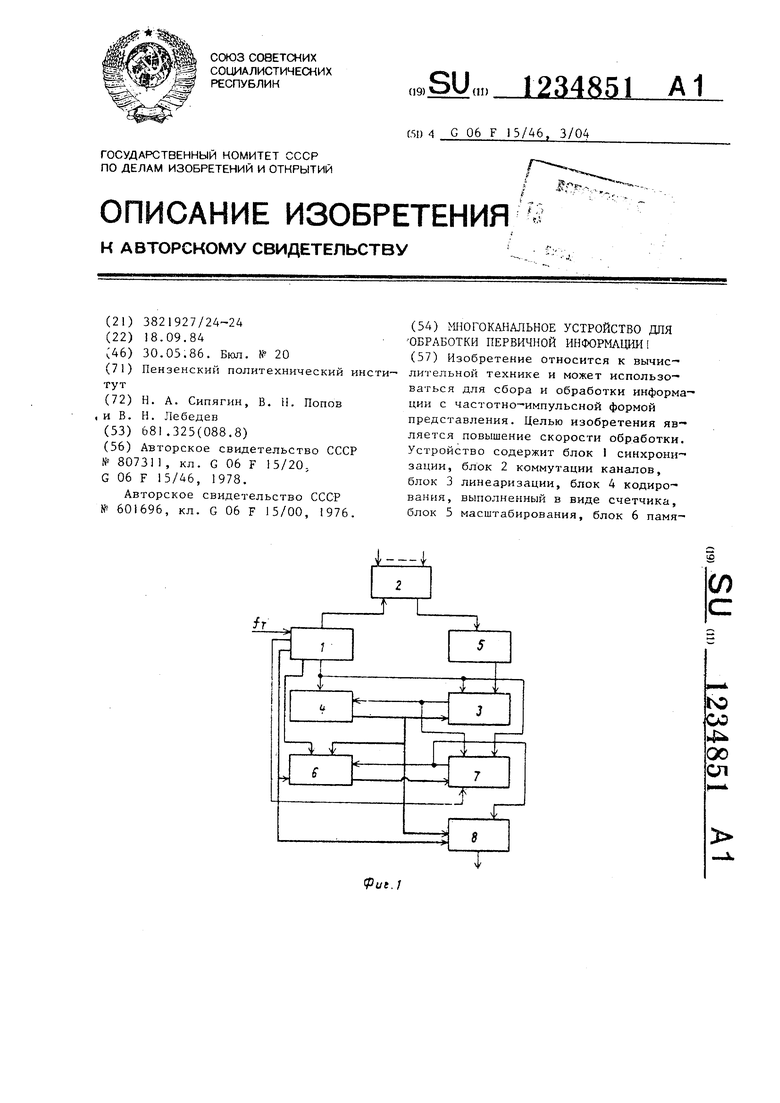

ти, блок 7 сравнения, блок 8 вывода. Входы блока 2 коммутации каналов подключены к входу устройства, управляющий вход блока 2 соединен с выходом блока 1 синхронизации, другой выход которого подключен к управляющему входу блока А кодирования, к управляющему входу блока 3 линеаризации и к управляющему входу блока 7 сравнения. Блок синхронизации соединен с блоком 6 памяти и с блоком 7 сравнения, выход .которого подключен к управляющему входу блока 8 вывода и к входу блока 6 памяти, информационный выход

Изобретение относится к вычислительной технике и предназначено для сбора и предварительной обработки информации с частотно-импульсной формой представления.

Целью изобретения является повышение быстродействия.

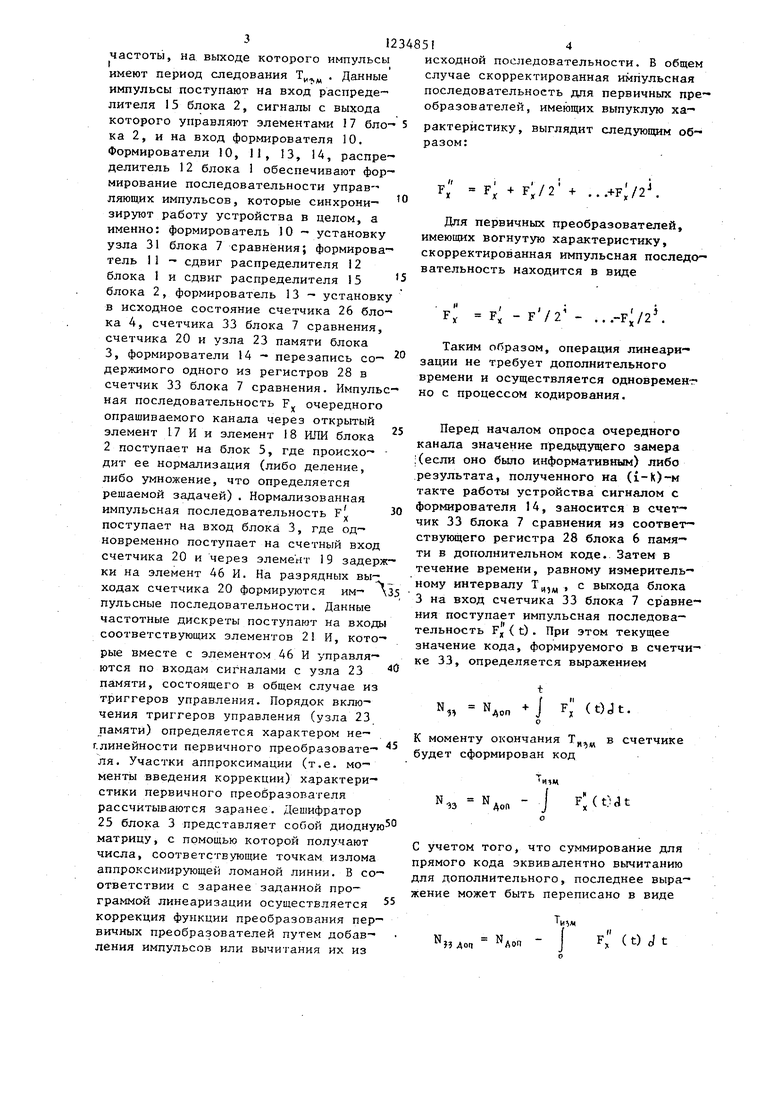

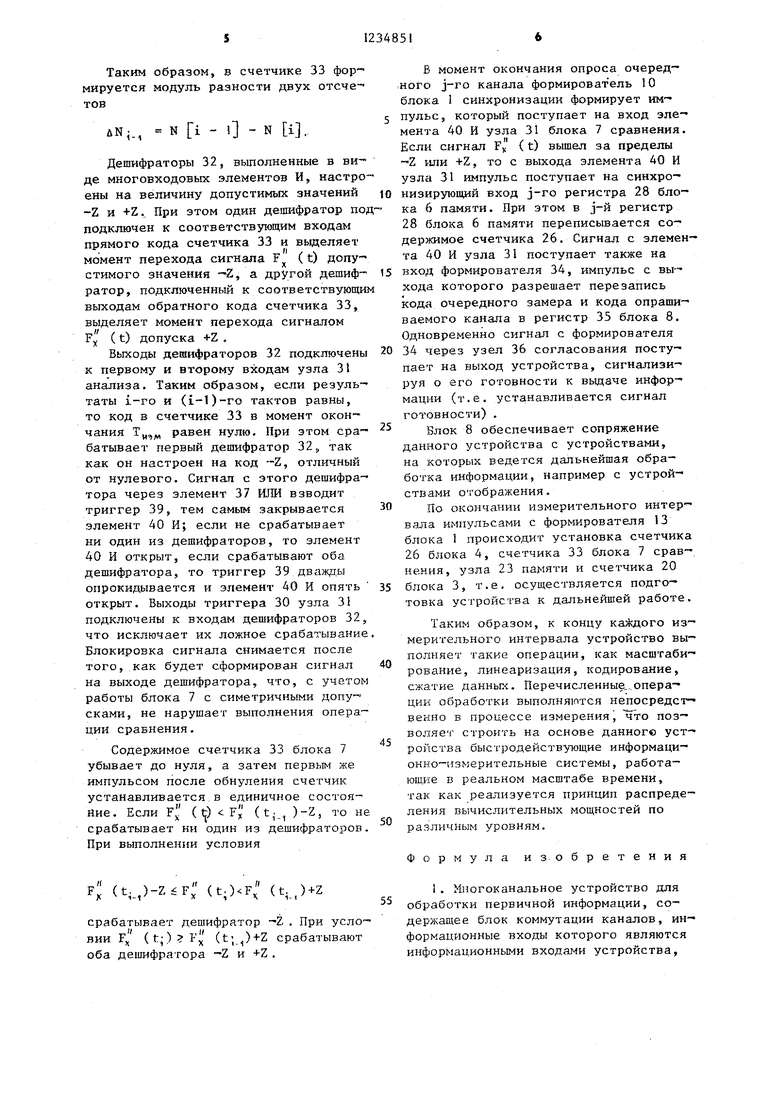

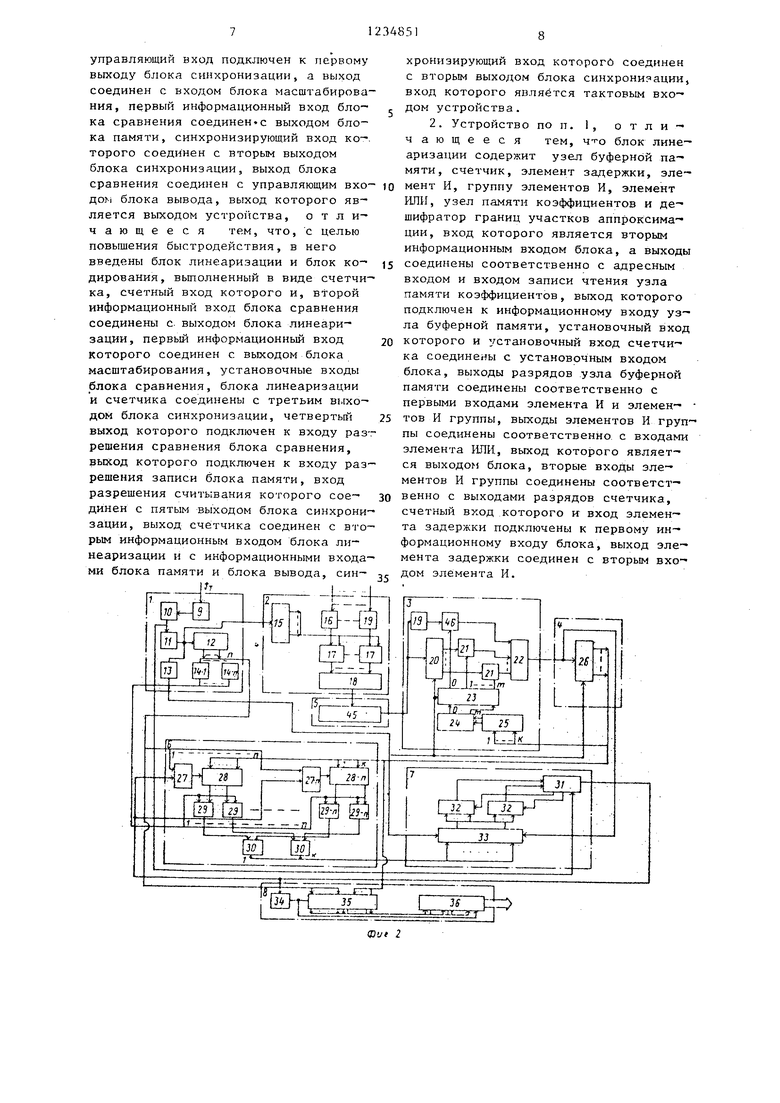

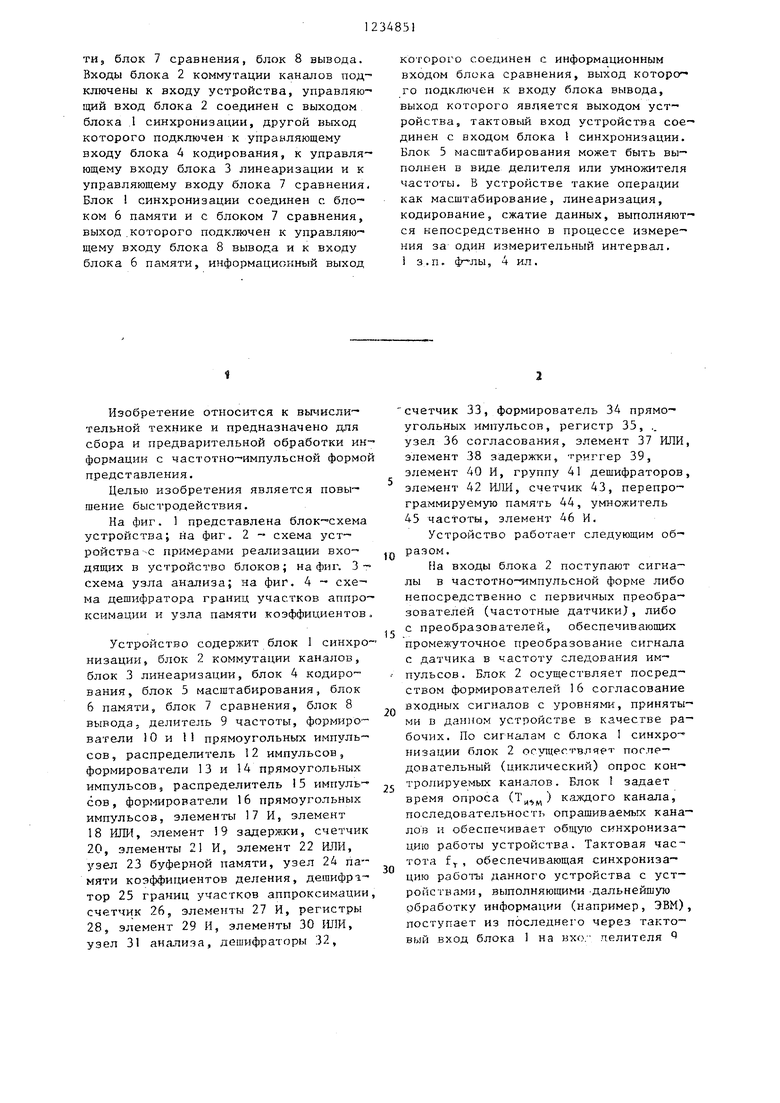

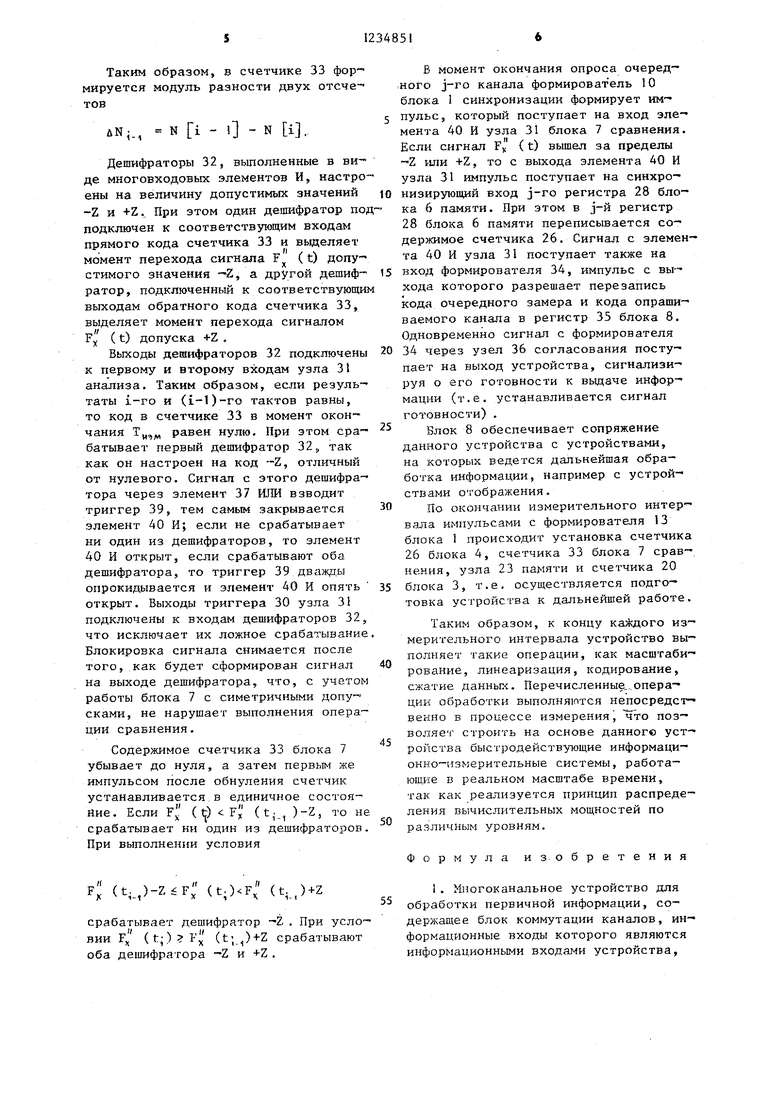

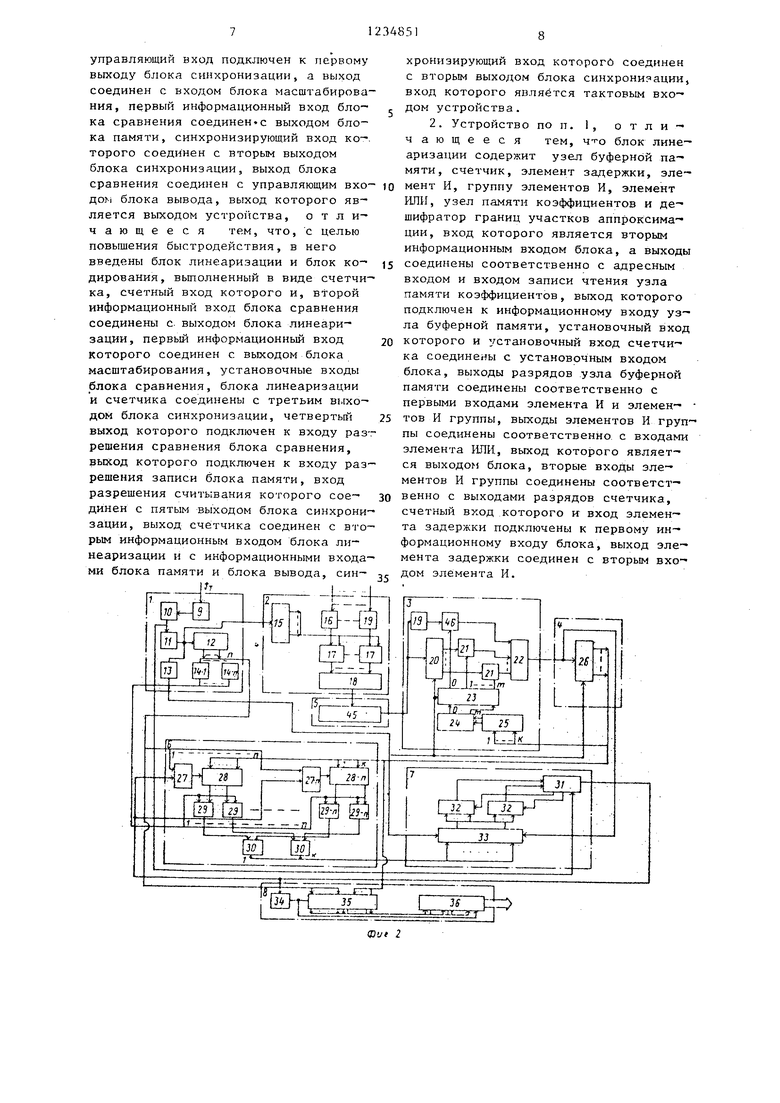

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - схема устройств а -с примерами реализации входящих в устройство блоков; на фиг. 3 схема узла анализа; на фиг. 4 - схема дешифратора границ участков аппроксимации и узла памяти коэффициентов.

Устройство содержит блок 1 синхронизации, блок 2 коммутации каналов, блок 3 линеаризации, блок 4 кодирования, блок 5 масштабирования, блок 6 памяти, блок 7 сравнения, блок 8 вывода, делитель 9 частоты, формирователи 10 и 1 прямоугольных импульсов, распределитель 12 импульсов, формирователи 13 и 14 прямоугольных импульсов, распределитель 15 импуль- сов, формирователи 16 прямоугольных импульсов, элементы 17 И, элемент 18 ИЛИ, элемент 19 задержки, счетчик 20, элементы 21 И, элемент 22 ИЛИ, узел 23 буферной памяти, узел 24 па- мяти коэффициентов деления, дешифратор 25 границ участков аппроксимации счетчик 26, элементы 27 И, регистры 28, элемент 29 И, элементы 30 ИЛИ, узел 31 анализа, дешифраторы 32,

которого соединен с информационным входом блока сравнения, выход которо- го подключен к входу блока вывода, выход которого является выходом устройства, тактовый вход устройства соединен с входом блока 1 синхронизации. Блок 5 масштабирования может быть выполнен в виде делителя или умножителя частоты. В устройстве такие операции как масштабирование, линеаризация, кодирование, сжатие данных, выполняются непосредственно в процессе измерения за один измерительный интервал. 3.п. , 4 ил.

0

5

0

,

счетчик 33, формирователь 34 прямоугольных импульсов, регистр 35, .. узел 36 согласования, элемент 37 ИЛИ, элемент 38 задержки, триггер 39, элемент 40 И, группу 41 дешифраторов, элемент 42 Р11Ш, счетчик 43, перепро- граммируемуто память 44, умножитель 45 частоты, элемент 46 И.

Устройство работает следующим образом.

На входы блока 2 поступают сигналы в частотно-импульсной форме либо непосредственно с первичных преобразователей (частотные датчики), либо с преобразователей., обеспечивающих промежуточное преобразование сигнала с датчика в частоту следования импульсов. Блок 2 осуществляет посредством формирователей 16 согласование входных сигналов с уровнями, принятыми в данном устройстве в качестве рабочих. По сигналам с блока синхро- низации блок 2 осуществляет последовательный (циклический) опрос контролируемых каналов. Блок 1 задает время опроса (Т,,,,) каждого канала, последовательность опрашиваемых каналов и обеспечивает общую синхронизацию работы устройства. Тактовая частота f, обеспечивающая синхронизацию работы данного устройства с устройствами, выполняющими -дальнейшую обработку информации (например, ЭВМ), поступает из последнего через тактовый вход блока 1 на вхог пелителя Ч

частоты, на выходе которого импульсы имеют период следования Т,, . Данные импульсы поступают на вход распределителя 15 блока 2, сигналы с выхода которого управляют элементами 17 бло- ка 2, и на вход формирователя 10. Формирователи 10, 11, 13, 14, распре- делитель 12 блока обеспечивают формирование последовательности управляющих импульсов, которые синхрони- зируют работу устройства в целом, а именно: формирователь 10 - установку узла 31 блока 7 сравнения; формирователь I1 - сдвиг распределителя I2 блока 1 и сдвиг распределителя 15 блока 2, формирователь 13 - установку в исходное состояние счетчика 26 блока 4, счетчика 33 блока 7 сравнения, счетчика 20 и узла 23 памяти блока 3, формирователи 14 - перезапись со- держимого одного из регистров 28 в счетчик 33 блока 7 сравнения. Импульсная последовательность Т очередного опрашиваемого канала через открытый элемент 17 И и элемент 18 ИЛИ блока 2 поступает на блок 5, где происхо- - дит ее нормализация (либо деление, либо умножение, что определяется решаемой задачей) . Нормализованная импульсная последовательность р поступает на вход блока 3, где одновременно поступает на счетный вход счетчика 20 и через элемент 19 задержки на элемент 46 И. На разрядных выходах счетчика 20 формируются им- пульсные последовательности. Данные частотные дискреты поступают на входы соответствующих элементов 21 И, которые вместе с элементом 46 И управляются по входам сигналами с узла 23 памяти, состоящего в общем случае из триггеров управления. Порядок включения триггеров управления (узла 23 памяти) определяется характером не- г.линейности первичного преобразовате- ля. Участки аппроксимации (т.е. моменты введения коррекции) характеристики первичного преобразователя рассчитываются заранее. Дешифратор 25 блока 3 представляет собой диодную матрицу, с помощью которой получают числа, соответствующие точкам излома аппроксимирующей ломаной линии. В соответствии с заранее заданной программой линеаризации осуществляется коррекция функции преобразования первичных преобразователей путем добавления импульсов или вычитания их из

исходной последовательности. В общем случае скорректированная импульсная последовательность дпя первичных преобразователей, имеющих выпуклую характеристику, выглядит следующим образом:

F; F; 4 г;/2 + ...-ьр;/2

Для первичных преобразователей, имеющих вогнутую характеристику, скорректированная импульсная последовательность находится в виде

F F - F /2 - ...

Таким образом, операция линеаризации не требует дополнительного времени и осуществляется одновременно с процессом кодирования.

Перед началом опроса очередного канала значение предьщущего замера :(если оно было информативным) либо результата, полученного на (i-K)-M такте работы устройства сигналом с формирователя 14, заносится в счетчик 33 блока 7 сравнения из соответствующего регистра 28 блока 6 памяти в дополнительном коде. Затем в течение времени, равному измерительному интервалу 1, , с выхода блока 3 на вход счетчика 33 блока 7 сравнения поступает импульсная последовательность F,, ( t) . При этом текущее значение кода, формируемого в счетчике 33, определяется выражением

«я - J (t)Jt.

о

моменту окончания Т, будет сформирован код

К моменту окончания Т., в счетчике

N

Доп

ч 7

- F:(t)jt

с учетом того, что суммирование для прямого кода эквивалентно вычитанию для дополнительного, последнее выражение может быть переписано в виде

Nj5 ДОП д,.

F; (t) j t

Таким образом, в счетчике 33 формируется модуль разности двух отсчетов

uNj., N i - l - N i.

Дешифраторы 32, выполненные в виде многовходовых элементов И, настро ены на величину допустимых значений -Z и +Z, При этом один дешифратор по подключен к соответствующим входам прямого кода счетчика 33 и выделяет момент перехода сигнала F (t) допу стимого значения -Z, а другой дешиф- ратор, подключенный к соответствующи выходам обратного кода счетчика 33, выделяет момент перехода сигналом F (t) допуска +Z ,

Выходы дешифраторов 32 подключены к первому и второму входам узла 31 анализа. Таким образом, если результаты i-ro и (L-l)-ro тактов равны, то код в счетчике 33 в момент окончания Tj,, равен нулю. При этом ера™ батывает первый дешифратор 32, так как он настроен на код -Z, отличный от нулевого. Сигнал с этого дешифратора через элемент 37 ИЛИ взводит триггер 39, тем самым закрывается элемент 40 И; если не срабатывает ни один из дешифраторов, то элемент 40 И открыт, если срабатывают оба дешифратора, то триггер 39 дважды опрокидывается и элемент 40 И опять открыт. Выходы триггера 30 узла 31 подключены к входам дешифраторов 32, что исключает их ложное срабатывание Блокировка сигнала снимается после того, как будет сформирован сигнал на выходе дешифратора, что, с учетом работы блока 7 с симетричными допу сками, не нарушает выполнения опера- ПИИ сравнения.

Содержимое счетчика 33 блока 7 убывает до нуля, а затем первым же импульсом после обнуления счетчик устанавливается в единичное состоя- ние. Если F (tf)F; (t,., )-Z, то не

срабатывает ни один из дешифраторов. При выполнении условия

р; (Ч, (t.)F; (t..,)z

срабатывает дешифратор -2, . При условии Г (t;)F (t;)+Z срабатывают оба дешифратора -Z и +Z.

to 15

20 30 5 0

0

5

В момент окончания опроса очеред- ,ного j-ro канала формироват ель 10 блока 1 синхронизации формирует импульс, который поступает на вход элемента 40 И узла 31 блока 7 сравнения. Если сигнал F (t) вышел за пределы -Z или +Z, то с выхода элемента 40 И узла 31 импульс поступает на синхро- низируюш нй вход j-ro регистра 28 блока 6 памяти. При этом в j-й регистр 28 блока 6 памяти переписывается содержимое счетчика 26. Сигнал с элемента 40 И узла 31 поступает также на вход формирователя 34, импульс с выхода которого разрешает перезапись кода очередного замера и кода опрашиваемого канала в регистр 35 блока 8. Одновременно сигнал с формирователя 34 через узел 36 согласования поступает на выход устройства, сигнализируя о его готовности к выдаче информации (т.е. устанавливается сигнал готовности) .

Блок 8 обеспечивает сопряжение данного устройства с устройствами, на которых ведется дальнейшая обработка информации, например с устройствами отображения.

По окончании измерительного интервала импульсами с формирователя 13 блока 1 происходит установка счетчика 26 блока 4, счетчика 33 блока 7 срав-. нения, узла 23 памяти и счетчика 20 блока 3, т.е. осуществляется подготовка устройства к дальнейшей работе.

Таким образом, к концу каждого измерительного интервала устройство выполняет такие операции, как масштабирование, линеаризация, кодирование, сжатие данных. Перечисленные,..операции обработки выполняются непосредственно в процессе измеренияj позволяет строить на основе данногс устройства быстродействующие информационно-измерительные системы, работающие в реальном масштабе времени, так как реализуется принцип распределения вычислительных мощностей по различным уровням.

Формула изобретения

1. Многоканальное устройство для обработки первичной информации, со- блок коммутации каналов, информационные входы которого являются информационными входами устройства,

управляющий вход подключен к первому выходу блока синхронизации, а выход соединен с входом блока масштабирования, первый информационный вход бло- ка сравнения соединен.с выходом блока памяти, синхронизирующий вход ко-, торого соединен с вторым выходом блока синхронизации, выход блока сравнения соединен с управляющим вхо- до блока вывода, выход которого является выходом устройства, о т л и- чающееся тем, что, с целью повышения быстродействия, в него введены блок линеаризации и блок ко- дирования, вьшолненный в виде счетчика, счетный вход которого и, второй информационный вход блока сравнения соединены с. выходом блока линеаризации, первый информационный вход которого соединен с выходом блока масштабирования, установочные входы блока сравнения, блока линеаризации и счетчика соединены с третьим выходом блока синхронизации, четвертьш выход которого подключен к входу раз решения сравнения блока сравнения, выход которого подключен к входу разрешения записи блока памяти, вход разрешения считывания которого сое- динен с пятым выходом блока синхронизации, выход счётчика соединен с вторым информационнь м входом блока ли неаризации и с информационными входами блока памяти и блока вывода, син-

„U.

хронизирующий вход которого соединен с вторым выходом блока синхронизации, вход которого является тактовым входом устройства.

2. Устройство по п. 1, отличающееся тем, что блок линеаризации содержит узел буфернЬй памяти, счетчик, элемент задержки, элемент И, группу элементов И, элемент ИЛИ, узел памяти коэффициентов и дешифратор границ участков аппроксимации, вход которого является вторым информационным входом блока, а выходы соединены соответственно с адресным входом и входом записи чтения узла памяти коэффициентов, выход которого подключен к информационному входу узла буферной памяти, установочный вход которого и установочный вход счетчика соединены с установочным входом блока, выходы разрядов узла буферной памяти соединены соответственно с первыми входами элемента И и элемен- тов И группы, выходы элементов И груп пы соединены соответственно с входами элемента ИЛИ, выход которого является выходом блока, вторые входы элементов И группы соединены соответственно с выходами разрядов счетчика, счетный вход которого и вход элемента задержки подключены к первому информационному входу блока, выход элемента задержки соединен с вторым входом элемента И.

Г

(риг.З

От 26

Составитель А. Жеренов Редактор М. Цнткина Техред М.Ходаннч Корректор А. Тяско

Заказ 2987/52 Тираж 671Подписное

BFIHHflH Г осударственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфиче(:кое предприятие, г. Ужт ород, ул. Проектная, А

| название | год | авторы | номер документа |

|---|---|---|---|

| Сеточная модель | 1984 |

|

SU1260981A1 |

| Число-импульсное линеаризирующее устройство с масштабированием | 1984 |

|

SU1201847A1 |

| Умножитель частоты | 1988 |

|

SU1562908A1 |

| Устройство для умножения частоты следования импульсов | 1986 |

|

SU1410027A1 |

| Устройство для отображения информации на экране электроннолучевой трубки | 1984 |

|

SU1257635A1 |

| Умножитель частоты | 1987 |

|

SU1499341A1 |

| Устройство для программного управления | 1984 |

|

SU1198461A1 |

| Устройство для вычисления непрерывно-логических функций | 1989 |

|

SU1695289A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Умножитель частоты | 1989 |

|

SU1649538A1 |

Изобретение относится к вычислительной технике и может использоваться для сбора и обработки информации с частотно-импульсной формой представления. Целью изобретения является повышение скорости обработки. Устройство содержит блок I синхронизации, блок 2 коммутации каналов, блок 3 линеаризации, блок 4 кодирования, выполненный в виде счетчика, блок 5 масштабирования, блок 6 памя- fr I- -I (Л

| Устройство для обработки измеритель-НОй иНфОРМАции | 1978 |

|

SU807311A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для предварительной обработки информации | 1976 |

|

SU601696A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-30—Публикация

1984-09-18—Подача