рования (БИ)8, блок управления 9, (N+ 1) блоков памяти 10, пороговый блок 11, компаратор 12, триггер 13, элемент И 14, распределитель импульсов (РИ) 15 и дешифратор информационных сигналов (ДИС) 16, На пере- даняцей стороне формируется требуемая кодовая комбинация, поступающая в электрическую сеть. Информация из сети поступает на приемную сторону, где в БИ 8 накапливается сигнал /с выхода вед 6 в течение п периодов сети, затем в течение одного периода сети считьшается и сбрасьгаается на

Изобретение относится к радиосвд- зи и может быть использовано в системах передачи информации по электрическим сетям в тонажном диапазоне частот

Цельк изобретения является повышение помехозащиценности и быстродействия.

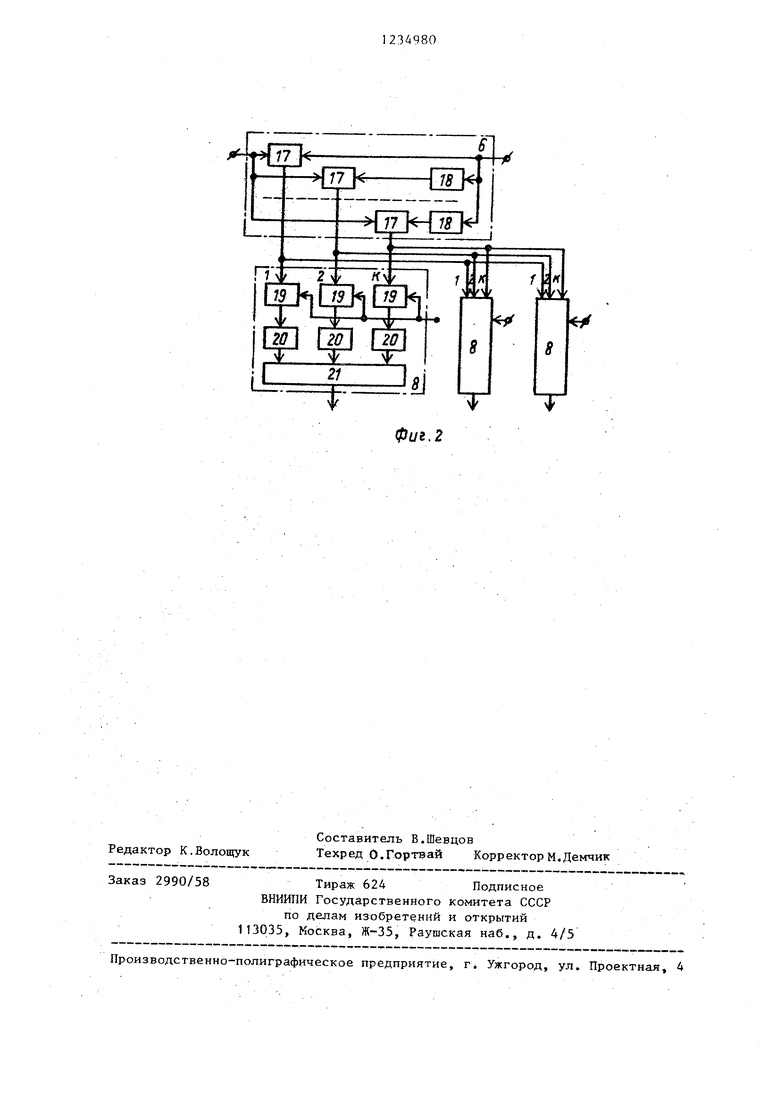

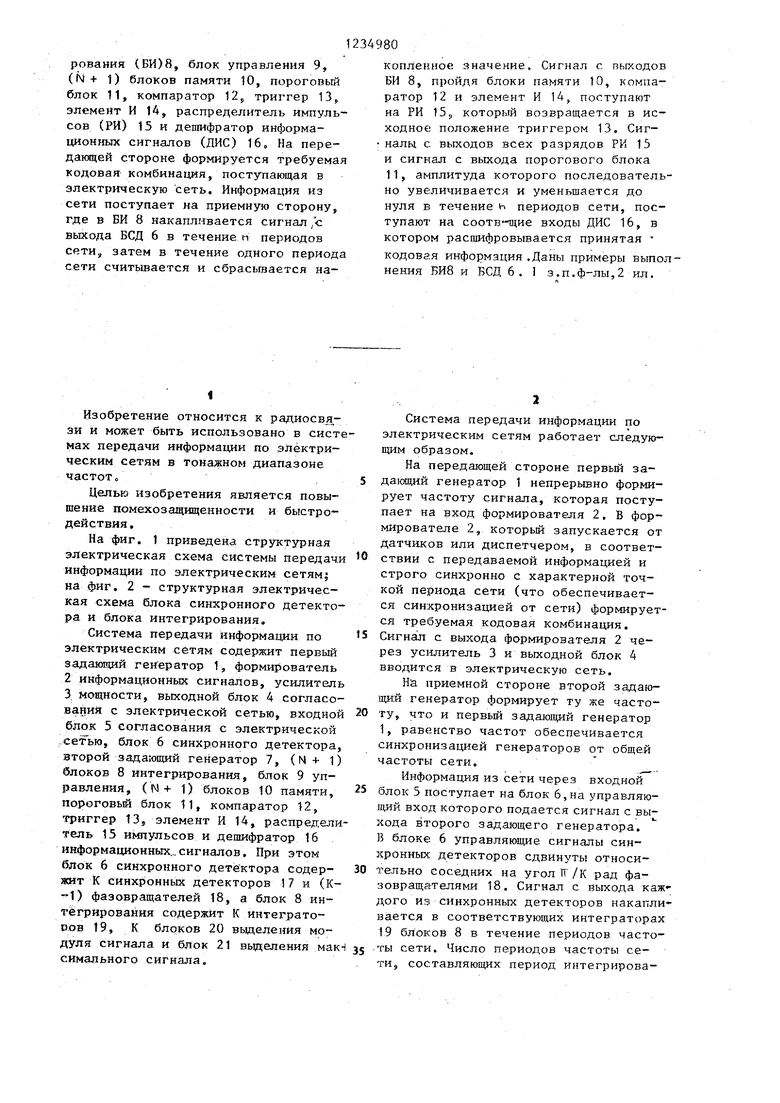

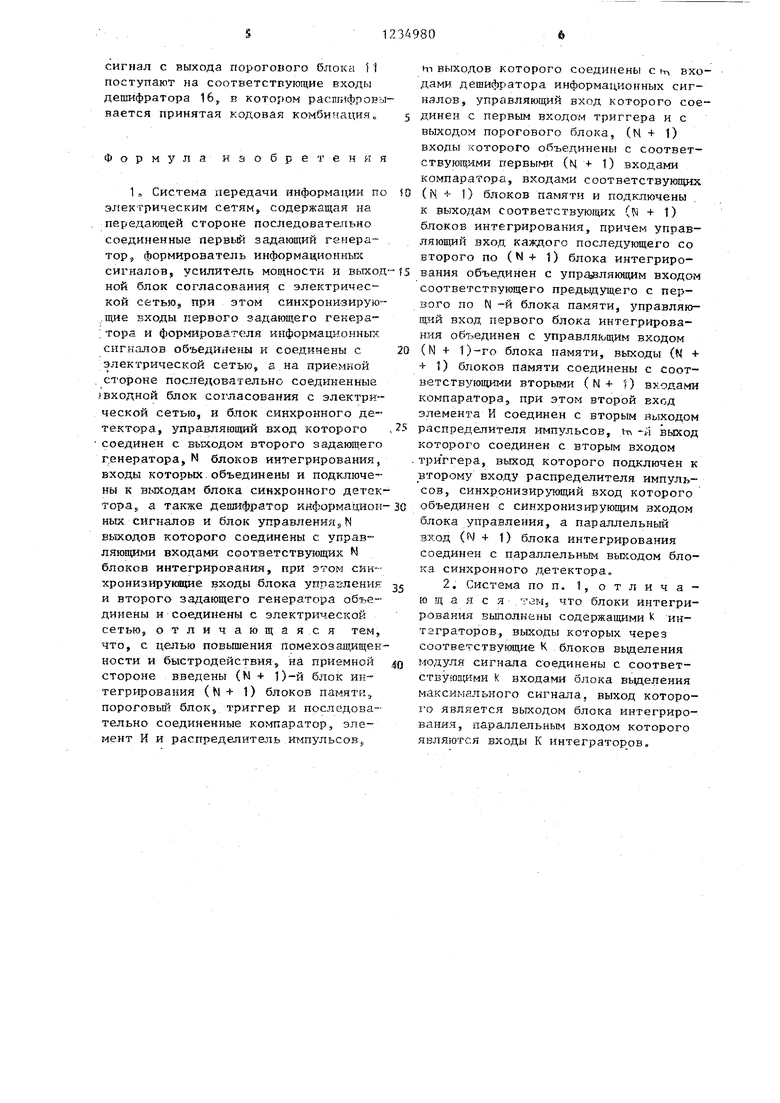

На фиг. 1 приведена структурная электрическая схема системы передачи информации по электрическим сетям| на фиг, 2 - структурная электрическая схема блока синхронного детектора и блока интегрирования.

Система передачи информации по электрическим сетям содержит первый задающий генератор 1, формирователь

2информационных сигналов, усилитель

3мощности, выходной блок 4 согласования с электрической сетью, входной блок 5 согласования с электрической

.сетью, блок 6 синхронного детектора, второй задающий генератор 7, (N 1) блоков 8 интегрирования, блок 9 управления, (N+ 1) блоков 10 памяти, пороговый блок 11, компаратор 12, чциггер 13, элемент И 14, распределитель 15 импульсов и дешифратор 16 информационных...сигналов. При этом блок 6 синхронного детектора содержит К синхронных детекторов 17 и (К- 1) фазовращателей 18, а блок 8 интегрирования содержит К интеграторов 19, К блоков 20 выделения модуля сигнала и блок 21 выделения мак симального сигнала.

,й

234980

копленное значение. Сигнал с выходов БИ 8, пройдя блоки памяти 10, компаратор 12 и элемент И 14, поступают на РИ 15,, который возвращается в исходное положение триггером 13, Сиг- налы с выходов всех разрядов РИ 15 и сигнал с выхода порогового блока 11, амплитуда которого последовательно увеличивается и уменьшается до нуля в течение н периодов сети, поступают на соотв-щие входы ДИС 16, в котором расшифровывается принятая кодовая информация .Даны примеры выполнения БИ8 и БСД 6. 1 з.п.ф-лы,2 ил.

5

5

0

5

0

Система передачи информации по электрическим сетям работает следующим образом.

На передающей стороне первый за- дакящй генератор 1 непрерьшно формирует частоту сигнала, которая поступает на вход формирователя 2, В формирователе 2, который запускается от датчиков или диспетчером, в соответствии с передаваемой информацией и строго синхронно с характерной точкой периода сети (что обеспечивается синхронизацией от сети) формируется требуемая кодовая комбинация. Сигнал с выхода формирователя 2 через усилитель 3 и выходной блок 4 вводится в электрическую сеть.

На приемной стороне второй задающий генератор формирует ту же частоту, что и первый задающий генератор 1, равенство частот обеспечивается синхронизацией генераторов от общей частоты сети.

Информация из сети через входной блок 5 поступает на блок 6,на управляю- 1ЦИЙ вход которого подается сигнал с выхода второго задающего генератора, В блоке 6 управляющие сигналы синхронных: детекторов сдвинуты относительно соседних на угол П /К рад фазовращателями 18. Сигнал с йыхода каж доге из синхронных детекторов накапли- зается в соответствующих интеграторах 19 блоков 8 в течение периодов часто- .ты сети. Число периодов частоты сети, составляющих период интегрирова ния определяется по условию отстройки от сетевых помех. Начало интегрирования, общее для всех К интеграторов одного блока интегрирования, сдвинуто по сравнению с соседними блоками интегрирования на один перио частоты сети. Сигналы с выходов интеграторов 19 в каждом из блоков 8 поступают на входы блока 21. На выход блока 21 проходит сигнал с того из К каналов блока 6, для которого минимальна разность фаз входного сигнала и управляющего сигнала синхронного детектора 17. Выполненные таким образом блоки 6 и 8 позволяют вьщел1ить сигнал при произвольной его фазе на входе приемника.

Каждьй из блоков 8 накапливает сигнал с выхода блока 6 синхронного детектора в течение п периодов сети, затем в течение одного периода сети происходит считывание и сброс накопленного значения. Амплитуда выходного импульса блока 8 пропорциональна накопленному значению сигнала. В блоке 9, вьшолнениом на основе кольцевого распределителя, формируются последовательности импульсов для управления накоплением, считыванием fi сбросом информации для каждого из блоков 8 интегрирования. Сигналы с выходов всех блоков интегрирования поступают на входы порогового блока 1 1 .

При появлении сигнала на входе приемного устройства через каждый период сети на входе порогового блока 11 появляется импульс, амплитуда которого равна значению сигнала, накопленного в том блоке 8 ий- тегрирования, с выхода которого в данный момент поступает сигнал. В течение п периодов сети амплитуды импульсов на входе порогового блока 11 будут последовательно нарастать, увеличиваясь с каждым шагом. Через время, равное н периодам сети, амплтуды импульсов на входе порогового блока 11 станут равными вплоть до ммента исчезновения сигнала на входе приемного устройства, а затем будут последовательно уменьшаться до нуля в течение н периодов сети.

Сигналы с выходов блоков 8 посту- пают также на входы компаратора 12, на одни входы непосредственно, а на другие - через блоки 10. Сброс ин

5

0

5

формации в кажд,ом из блоков 10 осуществляется одновременно со сбросом информзцни следующего блока 8 интегрирования. Таким образом,, в течение каждого периода сети в компараторе 12 происходит сравнение сигнала, поступившего с блоков интегрирования 8 в текущий период, с сигналом, поступившим в предшествующий период. Сигнал на выходе компаратора 12 появляется в том случае, когда текущее значение сигнала больше предыдущего, т.е. сигнал на выходе компаратора 12 будет появляться в течение h периодов сети, начиная с момента появления сигнала на входе приемного устройства, вплоть до появления установившегося значения сигнала на выходах блоков 8.

При первом срабатьгеании порогового блока 11 триггер 13 переходит из нулевого состояния в 1 и сигнал с выхода триггера 13 дает разрешение на запуск распределителя 15, число разрядов которого соответствует числу элементов кодовой комбинации. При появлении тактового импульса, кото- рьгй формируется из напряжения сети, распределитель 15 переходит в первое положение. При приходе следующего тактового импульса через период сети распределитель 15 переходит во второе положение, но при наличии в этот момент сигнала на выходе компаратора 12, которьй свидетельствует о том, что установившееся значение сигнала на выходах блоков интегрирования 8 еще не достигнуто, распределитель 15 через элемент И 14 вновь возвращается в первое положение. Распределитель 15 будет возвращаться в первое положение до тех пор, пока не исчезнет сигнал на выходе компаратора 12, что соответствует фиксированному сдвигу на h периодов сети относительно момента появления сигнала на входе приемного устройства. После этого с приходом каждого следующего тактового импульса распределитель 15 будет переходить в новое положение. Сигнал с последнего разряда распределителя 15, соответствующий последнему элементу кодовой комбинации сигнала, устанавливает триггер 13 в нулевое состояние и тем самым возвращает распределитель 15 в исходное положение. Сигналы с выходов всех разрядов распределителя 15 и

сигнал с выхода порогового блока 11 поступают на соответствующие входы дешифратора I6j, в котором расшифровывается принятая кодовая комбинация„ 5

Формула изобретения

1 ., Система передачи информации по iO электрическим сетяМ} содержащая на передающей стороне последоватепьно соединенные первьй задающий генера-- . торэ формирователь информационньк сигналов, усилитехсь мощности и выход-f5 ной блок согласования с электрической сетью, при этом синхрони-зирую- щие входы первого задающего генератора и формирователя информационньга сигналов объединены и соединены с 20 электрической сетью, а.на приемкой

стороне последовательно соединенные

входной блок со1 ласования с электрической сетью, и блок синхронного детектора, управляющий вход которого ,25

соединен с выходом второго задающего генератора,N блоков интегрирования, входы которьЕХ. объединены и подключены к выходам блока синхронного детектора., а также дешифратор информациои-30 них сигналов и блок управления., N выходов которого соединены с управляющими входами соответствутещих N блоков интегрирования, при этом син- хронизгфукшще входы блока управления и второго задающего генератора объединены и соединены с электрической сетью, отлич ающа я. с. я тем, что, с целью повышения помехозащищенности и быстродействия5 на приемной 40 стороне введены (N + |)-й блок интегрирования (Н+ 1) блоков памяти. пороговьй блокS, триггер и последовательно соединенные компаратор, элемент И и распределитель импульсов,

m выходов которого соединены с ил входами дешифратора информационных сиг- няло В, управляющий вход которого соединен с первым входом триггера и с выходом порогового блока, (N + 1) входы которого объединены с соответствующими первыми (Ы 1) входами компаратора, входами соответствующих (Н 1) блоков памяти и подключены к выхо/ ам соответствуюгцих ( + 1) блоков интегрирования, причем управ- хшющий вход каждого последующего со второго по (М+ 1) блока интегрирования объединен с управляющим входом соответствующего предыдущего с первого по N -и блока памяти, управляю- щ:яй вход первого блока интегрирования объединен с управляющим входом (N + 1)-го блока памяти, выходы (N + i) блоков памяти соединены с соот- ветствующи1 1И вторыми (N+ I) входами компаратора, при этом второй вход элемента И соединен с вторым выходом распределителя импульсов, tn -и выход которого соединен с вторым входом три ггера, выход которого подключен к второму входу распределителя импульсов, синхронизирующий вход которого объединен с синхронизирующим входом блока управления, а параллельный вход (N + 1) блока интегрирования соединен с п.араллельным выходом блока синхронного детектора.

2. Система поп, 1, отличающаяся, там, что блоки интегрирования вьшолнены содержащими К ин- тэ-граторов, выходы которых через соответствующие К ,блоков выделения модуля сигнала соединены с соответ- ствуюаснми К входами блока выделения наксимгшьного сигнала, выход которого является выходом блока интегрирования, параллельным входом которого являются входы К интеграторов.

Редактор К.Волощук

Составитель Б.Шевцов

Техред О.Гортвай Корректор М.Демяик

Заказ 2990/58

Тираж 624Подписное

ВНИИТШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Система передачи информации по электрическим сетям | 1984 |

|

SU1279076A1 |

| Система передачи информации по электрическим сетям | 1978 |

|

SU692100A1 |

| Синтезатор частот | 1988 |

|

SU1656680A1 |

| Устройство синхронизации электроразведочных приемников | 1987 |

|

SU1449961A1 |

| Система связи с относительной фазовой и фазоимпульсной модуляцией | 1987 |

|

SU1559421A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ МОТОРНЫМИ ПРИВОДАМИ РАЗЪЕДИНИТЕЛЕЙ КОНТАКТНОЙ СЕТИ | 2004 |

|

RU2274904C2 |

| Устройство для приема и передачи сигналов контроля от датчиков | 1987 |

|

SU1418793A1 |

| Система передачи данных по одножильному кабелю | 1985 |

|

SU1298937A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| УСТРОЙСТВО ПОИСКА ПСЕВДОШУМОВЫХ РАДИОСИГНАЛОВ | 1990 |

|

RU2012138C1 |

Изобретение относится к радиосвязи. Повьшается помехозащищенность и быстродействие. Устр-во содержит на передающей стороне задаюпщй генератор 1, формирователь информационных сигналов 2, усилитель мощности 3 и выходной блок согласования 4 с электрической сетью, а на приемной стороне - входной блок согласования 5 с электрической сетью, блок синхронного детектора (БСД)6, задающий генератор 7 (N4- 1) блоков интегри(Л с ю СО 00 J У иг. 1

| Система телесигнализации с использованием наложенных .частот то- нажного диапазона, - Электрические станции, 1975, № 5, с | |||

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Система передачи информации по электрическим сетям | 1978 |

|

SU692100A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-05-30—Публикация

1984-12-29—Подача