зон допускаемых значений фаз сигналов в соответствующих каналах. В ПЗУ 16 хранятся коды внутренних углов, образуемых границами зон допустимых значений фаз сигналов в соответствующих каналах. При этом

Изобретение относится к измерителной технике и может быть использован в измерительных приборах и системах

Цель изобретения - расширение функциональных возможностей.

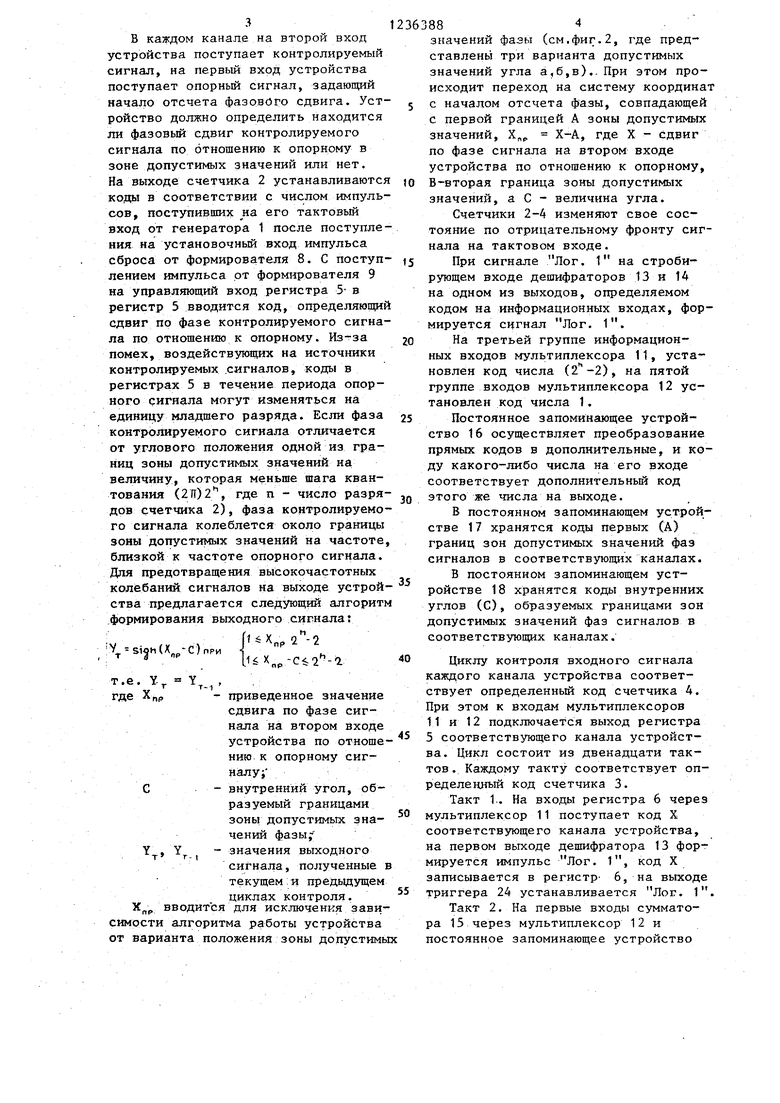

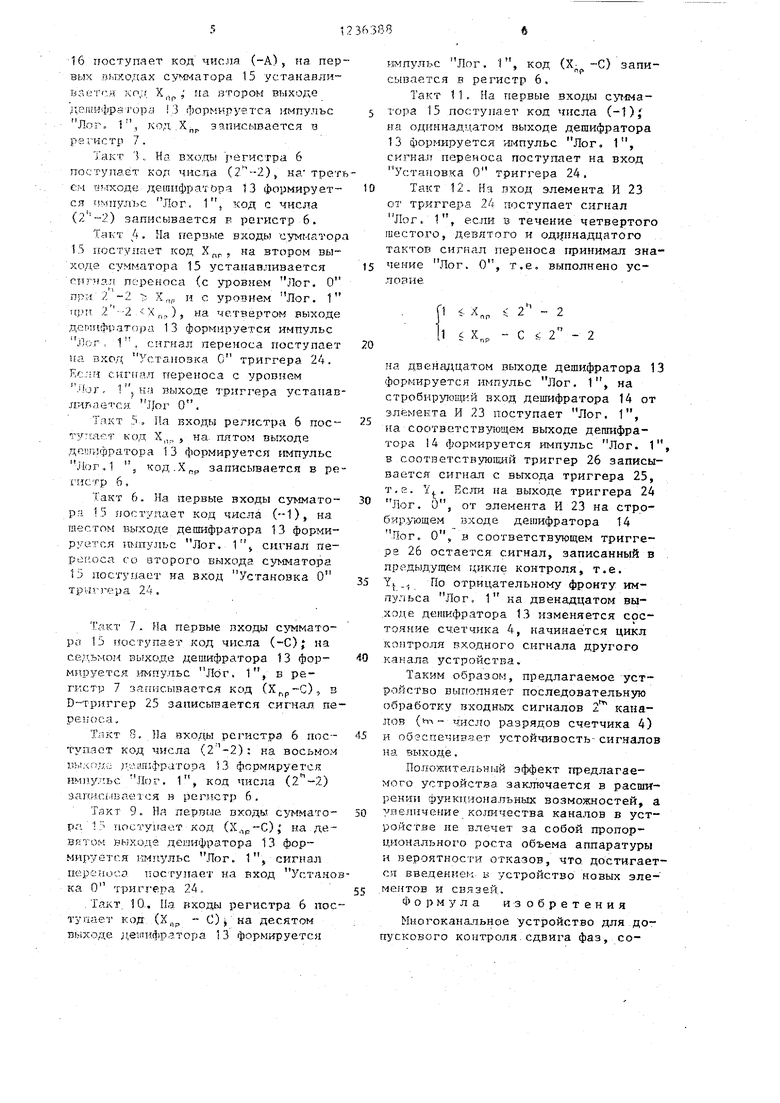

На фиг.1 представлена структурная схема многоканального устройства для допускового контроля сдвига фаз, на фиг.2 - временные диаграммы работы устройства-.

Устройство содержит генератор 1 импульсов, счет.чики 2-4 импульсов, регистры 5-7, формирователи 8 и 9 импульсов, мультиплексоры 10-12, дешифраторы 13 и 14, сумматор 15, постоянные запоминающие устройства 16-18, элементы ИЛИ : 19-21, элементы И 22 и 23, RS-триггер 24 и D-триггеры 25 и 26,при этом первые входы сумматора 15 соединены с выхо- дами первого постоянного запоминающего устройства 16, тактовый вход счетчика 2 импульсов соединен с генератором 1 импульсов, установочный вход соединен с выходом формирователя 8 импульсов, соединенного первым входом с первым входом устройства, информационные входы регистров 5 соединены с выходами счетчика 2 им- ,пульсов, первые входы формировате- лей 9 импульсов соединены с вторыми входами устройства, информационные входы мультиплексора 10 соединены с выходами регистров 5, а выходы соединены с первыми группами информа- ционных входов мультиплексоров 11 и 12, управляющие входы которых соединены с информационными входами дешифратора 13 и подключены к выходам счетчика 3 импульсов, соединен- кого входом с стробирующим входом дшифратора 13 и подключенного к генератору 1 импульсов, выходы мультиплексора 11 соединены с информацион

увеличение количества каналов в устройстве не влечет за собой пропорционального роста объема аппаратуры и вероятности отказов, что дос- тигае тся введением в устройство указанных новых элементов. 2 ил.

0 0 , 0

5

ными входами регистра 6, выходы которого соединены с второй группой входов сумматора 15, соединенного первой группой выходов с информационными входами регистра 7, выходы которого соединены с вторыми группами входов мультиплексоров 11 и 12, второй выход сумматора соединен с информационным входом D-триггера 25 и через элемент И 22 - с входом Установка О RS-триггера 24, вход Ус- тановка t которого соединен с первым выходом дешифратора 13, а выход через элемент 23 соединен со стробирующим входом де иифратора 14, информационные входы которого соединены с управляющими входами мультиплексора 10 и выходами счетчика 4 импульсов непосредственно, а через запоминающие устройства 17 и 18 - с третьей и четвертой группами информационных входов мультиплексора 12, соединенного выходами с входами запоминающего устройства 16, выходы дешифратора 14 соединены с тактовыми входами D-триггеров 26, выходы которых являются выходами устройства, тактовый вход регистра 6 через элемент ИЛИ 19 соединен с первым, третьим, пятым, восьмым и десятым выходами дешифратора 13, второй вход элемента И 22 через элемент ИЛИ 20 соединен с четвертым, шестым, девя- и одиннадцатым выходами дешифратора 13, тактовый вход регистра 7 через элемент ИЛИ 21 соединен с вто- рьм и седьмым выходами дешифратора 13, двенадцатый выход которого соединен с входом счетчика 4 импульсов и вторым входом элемента И 23, а .седьмой выход соединен с тактовым .входом D-триггера 25,

Устройство работает следующим образом.

3

В каждом канале на второй вход устройства поступает контролируемый сигнал, на первый вход устройства поступает опорньй сигнал, задающий начало отсчета фазового сдвига. Уст- ройство должно определить находится ли фазовый сдвиг контролируемого сигнала по отношению к опорному в зоне допустимых значений или нет. На выходе счетчика 2 устанавливаются коды в соответствии с числом импульсов, поступивших на его тактовый вход от генератора 1 после поступления на установочный вход импульса сброса от формирователя 8. С поступ- лением импульса от формирователя 9 на управляющий вход регистра 5- в регистр 5 вводится код, определяющий сдвиг по фазе контролируемого сигнала по отношению к опорному. Из-за помех, воздействующих на источники контролируемых .сигналов, коды в регистрах 5 в течение периода опорного сигнала могут изменяться на единицу младшего разряда. Если фаза контролируемого сигнала отличается от углового положения одной из границ зоны допустимых значений на величину, которая меньше шага квантования (2ТГ)2, где п - число разря- дон счетчика 2), фаза контролируемого сигнала колеблется около границы зоны допустимых значений на частоте, близкой к частоте опорного сигнала. Для предотвращения высокочастотных колебаний сигналов на выходе устрой- ства предлагается следующий алгоритм формирования выходного сигнала:

fts :У 51|и()пРи 1

)пр2 -2

T.e.Y, Y,,

где ЛПР - приведенное значение сдвига по фазе сигнала на втором входе устройства по отношению к опорному сиг- Hsmy-f

е - внутренний угол, образуемый границами зоны допустимых значений фазы;- Y, Y - значения выходного

сигнала, полученные в текущем:я предыдущем

циклах контроля. вводится для исключения зависимости алгоритма работы устройства от варианта положения зоны допустимы

j )о 5 о 5 ..

0

5

значений фазы (см,фиг.2, где представлены три варианта допустимых значений угла а,б,в).. При этом происходит переход на систему координат с началом отсчета фазы, совпадающей с первой границей А зоны допустимых значений, Х„р Х-А, где X - сдвиг по фазе сигнала на втором входе устройства по отношению к опорному, В-вторая граница зоны допустимых значений, а С - величина угла.

Счетчики 2-4 изменяют свое сос тояние по отрицательному фронту сигнала на тактовом входе.

При сигнале Лог. 1 на строби- рующем входе дешифраторов 13 и 14 на одном из выходов, определяемом кодом на информационных входах, формируется сигнал Лог. 1.

На третьей группе информационных входов мультиплексора 11, установлен код числа (), на пятой группе входов мультиплексора 12 установлен код числа 1.

Постоянное запоминающее устройство 16 осуществляет преобразование прямых кодов в дополнительные, и коду какого-либо числа на его входе соответствует дополнительный код этого же числа на выходе.

В постоянном запоминающем устройстве 17 хранятся коды первых (А) границ зон допустимых значений фаз сигналов в соответствующих каналах.

В постоянном запоминающем устройстве 18 хранятся коды внутренних углов (С), образуемых границами зон допустимых значений фаз сигналов в соответствующих каналах.

Циклу контроля входного сигнала каждого канала устройства соответствует определенный код счетчика 4. При этом к входам мультиплексоров 11 и 12 подключается выход регистра 5 соответствующего канала устройства. Цикл состоит из двенадцати тактов . Каждому такту соответствует определенный код счетчика 3.

Такт 1.. На входы регистра 6 через мультиплексор 11 поступает код X соответствукмцего канала устройства, на первом выходе дешифратора 13 формируется импульс Лог. 1, код X записывается в регистр 6, на выходе триггера 24 устанавливается Лог. 1.

Такт 2. На первые входы сумматора 15 через мультиплексор 12 и постоянное запоминающее устройство

16 поступает код числа (-А), на первых вь.кодах сумматора 15 устанавли- вяетг.я ко,ь Х,,, на втором выходе Гцбигифра ора 3 формируется импульс Лог 1, код .Х|,р записывается в регистр 7,

Такт „ На входы регистра 6 поступает код числа ), на третем яыхоце дешифратора 13 формирует- ся чмпульс Лог, код с числа (2-2) записывается F регистр 6.

Такт 4. На ггервые входы сумматор 15 поступает код X. на втором выходе сумматора 15 устанавливается сигнал переносгг (с уровнем Лог, О при 2 -2 ХГ,Р и с уровнем Лог, 1 гфк Хг,.,), на четвертом рыходе дештЕфратора 13 формируется ннпульс .Пог , сигнал переноса поступает на вход З стаповка О триггера 24. сигнал переноса с уровнем . Тог, 1 j ка выходе триггера устанавливается Jlor О.

Такт 5, ila входы регистра 6 пос- ту гаст код X,,., , на. пятом выходе дешифратора 13 формируется ямпульс ,Uor,1 ; код.Хг,р записывается в ре гнстр 6.

Такт 6. }1а первые входы сз ммато- р.ч 1.5 поступает код числа (-1), на шестом Г5ьгходе дешифратора 13 формируется гшпульс Лог. Г си.гнал пе- pet -oca со второго выхода сумматора 15 поступает на вход Установка О триггера 24,

Такт 7 . На первые пходы сумматора 13 поступает код числа (-С); на се,, выходе дешифратора 13 фор- мируется 1шпу.пьс Лог. 1, в ре- п .стр 7 заггнсывастся код ()., s В трнггер 25 записываетс.я сигнал пере.; оса.

Такт 8, Ila входы регистра 6 нос- тупаст код числа (2-2): ка восьмом г,).г,-сг; яц я;,лш.1фратора 3 формируется HMjiyjJbc .Лог, 1, код числа (2 -2) записьшается в регистр 6.

Такт 9. На перпые входы суммато- ра 1. поступает код (Х.р-С), на девятом выходе деиифратора 13 формируется импульс Лог. Г сигнал переноса поступает на вход 5 станока О триггера 24.

.Такт. 10., Па входы регистра 6 поступает код (X,,., С) на десятом выходе ;.ге:вифратора 13 формируется

рзлшульс Лог, 1, код ( -С) записывается в регистр 6.

Та.кт 11. На первые входы т ора 15 поступа.ет код числа (-1) на одиннадцатом выходе дешифратора 13 формируется импульс Лог. 1, сигнал переноса поступает на вход Установка О триггера 24,

Такт 12. На пход элемента И 23 от триггера 2fi поступает сигнал Лог. 1, ес.пи в течение четвертого шестого, девятого и одфгнадцатого тактов сигнал переноса гфинимал значение Лог. О, т,е выполнено условие

1 Х„, 2-2

1 .. Х„, -- С 2 - 2

на двенадцатом выходе дешифратора 13 фор.чируется импульс Лог, 1, на стробирую1г.1ий вход дешифратора 14 от элемекта И 23 поступает Лог, 1, па соответствующем выходе дешифратора 14 формируется импульс Лог. 1, в соответствующи} триггер 26 записывается сигнап с выхода триггера 25, т.е. Y, Если lia выходе триггера 24 Лог. О, от элемента И 23 на стро- бир.ующем входе дешифратора 14 Лог. О, в соответствующем триггере 26 остается сигнал, записанный в предыдущем цикле контроля, т.е.

Y.

По отрицательному фронту им

пульса Лог, 1 на двенадцатом вы- ,ходе дешифратора 13 изменяется срс- то.яние счетчика 4, начинается цикл контроля Б.ходного сигнала другого кака.па устройства.

Таким образом, предлагаемое устройство выполняет последовательную обработку входных сигналов 2 каналов (ьл число разрядов счетчика 4) и обеспечивает устойчивость- сигналов на выходе.

.По.гюжительный эффект предлагаемого устройства заключается в расширении функциональных возможностей, а увеличение количества каналов в уст- ро.йстве не влечет за собой пропорционального роста объема аппаратуры и вероятности отказов, что. достигается вве.цениек в устройство новых эле- ментов и связей.

Формула изобретения

Многоканальное устройство для.до- пускового контроля.сдвига фаз, содержащее сумматор, первые входы которого соединены с выходами первого постоянного запоминающего устройства, генератор импульсов, соединенный с тактовым входом первого счетчика импульсов, ус ановочный вход которого соединен с выходом первого формирователя импульсов, соединенного первьм входом с первым входом устройства, и в каждом канале первы регистр, информадионные входы которого соединены с.выходами первого счетчика импульсов, второй формирователь импульсов, первый вход которого соединен с вторьм входом устройства, второй вход - с вторым входо первого формирователя импульсо в и генератором импульсов, а выход - с тактовым входом первого регистра, о тл и ч а ющ ее с я тем, что, с целью расширения функциональных возможностей, в него введены второй и третий счетчики импульсов, второй и третий регистры, дешифраторы, элементы ИЛИ, элементы И, мультиплексоры, RS-триггер, D-триггеры, второй и третий постоянные запоминающие устройства, причем информационные входы первого мультиплексора соединены с выходами первых регистров, а выходы - с первыми группами информационных входов второго и третьего мультиплексоров, управляющие входы которых соединены с информационными входами первого дешифратора и подключены к выходам второго счетчика Импульсов, соединенного входом со стробирующим входом первого дешифратора и подключенного к генератору импульсов, выходы второго мультиплексора соединены с информационными входами второго регистра, выходы которого соединены с второй группой входов сумматора, соединенного пер10

ts

20

2363888

вой группой выходов с информационными входами третьего регистра, выходы которого соединены с вторыми группами входов второго и третьего мультиплексоров , второй выход сумматора соединен с информационным входом первого D-триггера и через первый элемент И - с входом Установка О RS-триггера, вход Установка 1 которого соединен с первым выходом первого дешифратора, а выход через второй элемент И соединен со стробирующим входом второго дешифратора, информационные входы которого соединены с управляющими входами первого мультиплексора и выходами третьего счетчика импульсов непосредственно, а через второе и третье постоянные запоминающие устройства - с третьей и четвертой соответственно группами информационных входов третьего мультиплексора, соединенного выходами с входами первого запоминающего устройства, выходы второго дешифратора соединены с .тактовыми входами вторых D-триггеров, выходы которых являются выходами устройства, тактовый вход второго .регистра через первый элемент ИЛИ соединен с первым, третьим, пятым, восьмь1м и десятым выходами первого дешифратора, второй вход первого элемента И через второй элемент ИЛИ соединен с четвертым, шестым, девятым и одиннадцатым выходами первого дешифратора, тактовый вход третьего регистра через третий элемент ИЛИ соединен с вторым и седьмым выходами первого дешифратора, двенадцатый выход которого соединен с входом третьего счетчика импульсов и вторым входом второго элемента И, а седьмой выход первого деш11фратора соединен с тактовым входом первого D-триггера.

25

30

5

0

а

А

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для определения знака разности фаз | 1984 |

|

SU1250980A1 |

| Цифровой измеритель угловой скорости | 1985 |

|

SU1275292A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Коррелятор | 1983 |

|

SU1130874A1 |

| Формирователь импульсных последовательностей для контроля запоминающих модулей на цилиндрических магнитных доменах | 1987 |

|

SU1513514A1 |

| УНИВЕРСАЛЬНЫЙ ГЕНЕРАТОР СИГНАЛОВ ПРОИЗВОЛЬНОЙ ФОРМЫ | 1994 |

|

RU2060536C1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Устройство для моделирования дискретных систем | 1985 |

|

SU1295411A1 |

| Многоканальное устройство тестового контроля логических узлов | 1990 |

|

SU1837295A1 |

Изобретение относится к измерительной технике и может быть использовано в измерительных приборах и системах. Целью изобретения является расширение функциональных возможностей устройства. Для достижения цели в устройство введены счетчики 3 и 4, регистры 6 и 7, мультиплексоры 10, 11 и 12, дешифраторы 13 и 14, элементы ИЛИ 19, 20 и 21, элементы И 22 и 23, RS-триггер 24 и D-триггеры 25 и 26. Устройство также содержит генератор 1 импульсов, счетчик 2, регистр 5, формирователи 8 и 9 импульсов, сумматор 15, постоянные запоминаюшрие устройства (ПЗУ) 16, 18. При этом ПЗУ 16 осуществляет преобразование прямых кодов в дополнительные. В ПЗУ 17 хранятся коды первых границ с 1йТ Т1Ю 00 О со 00 00 Лиг (fauif

Фиг.

Редактор С. Патрушева Заказ 3085А7

Составитель В. Шубин

Техред Г.Гербер Корректор А. Обручар

Тираж 728 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

1Й оизводственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,А

| Устройство для определения знака разности фаз | 1982 |

|

SU1065785A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для определения знака разности фаз | 1983 |

|

SU1167524A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-06-07—Публикация

1984-12-10—Подача