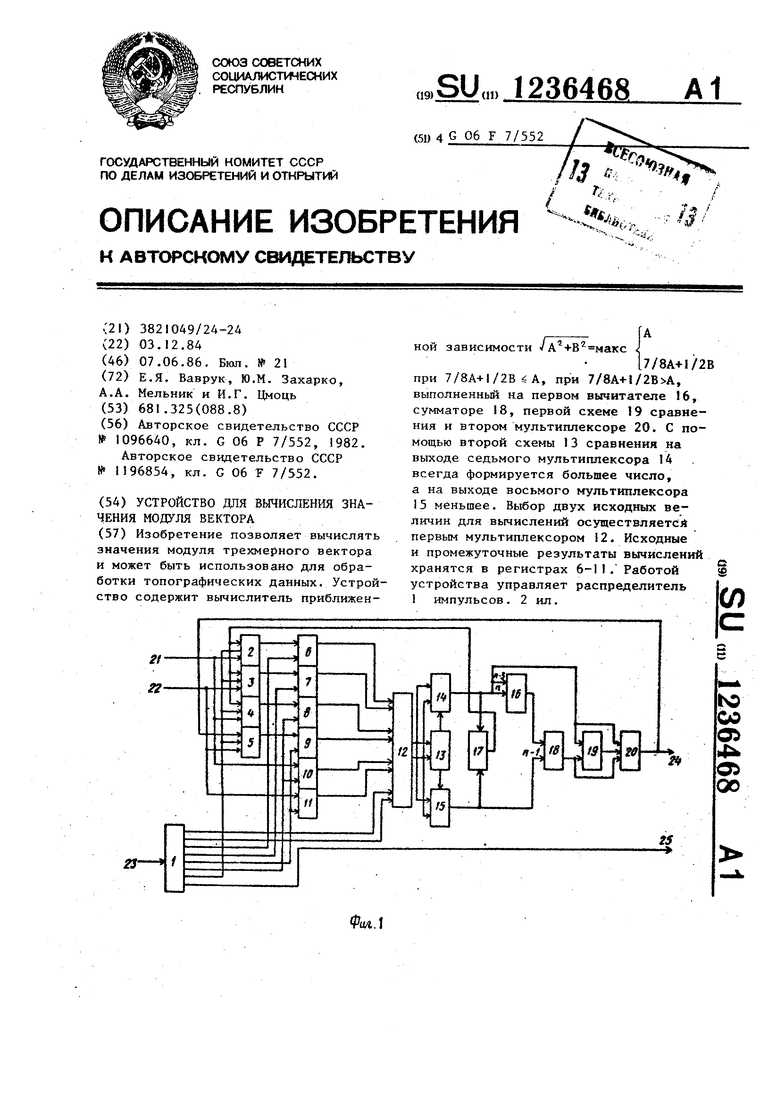

Изобретение относится к автоматике и вычислительной технике и может быть использовано для создания автоматизированных систем обработки топографических данных.

Целью изобретения является расширение класса решаемых задач.

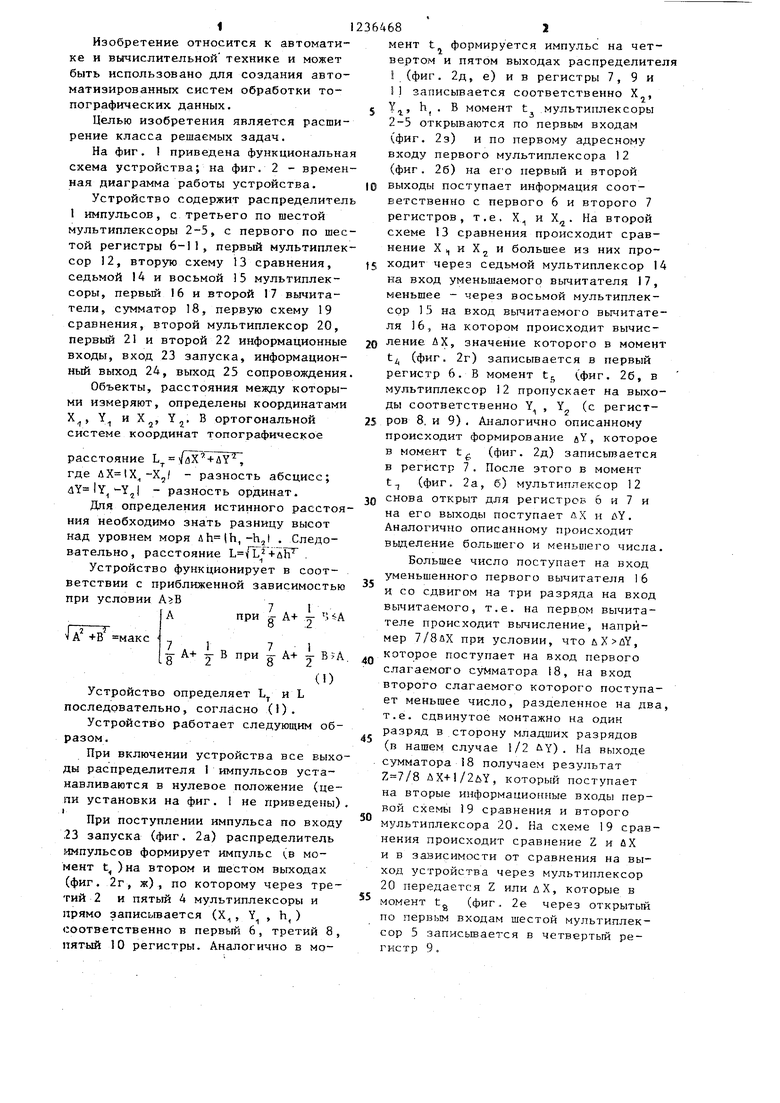

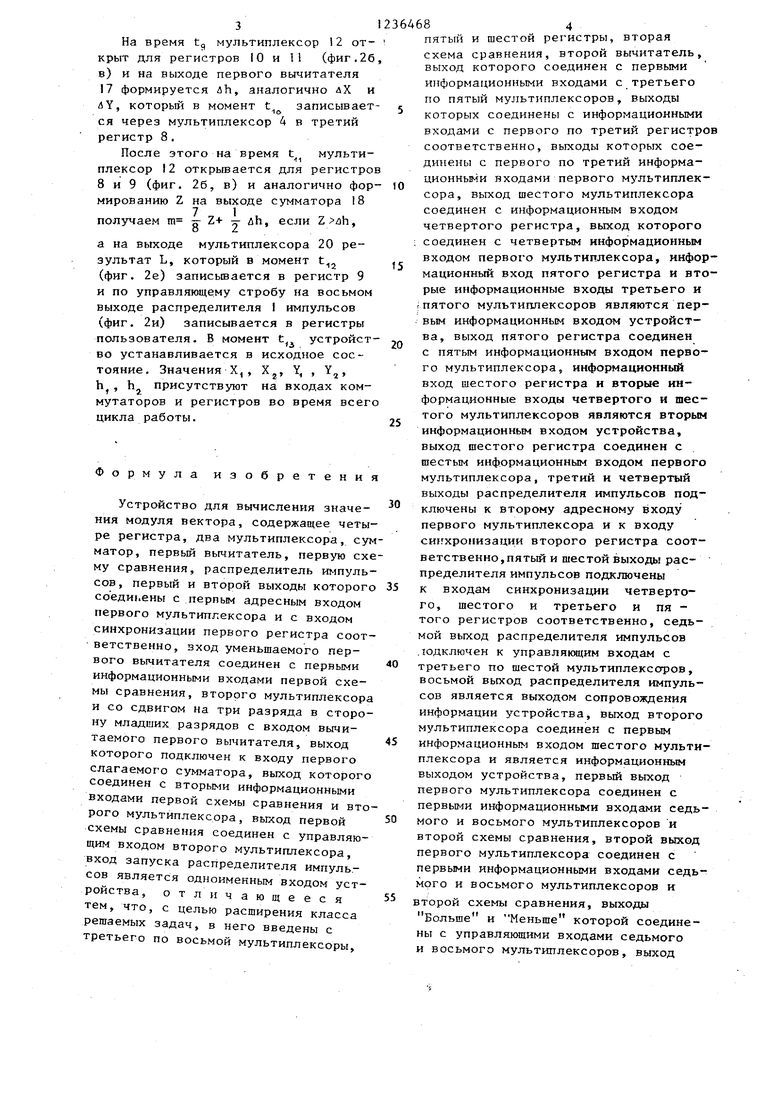

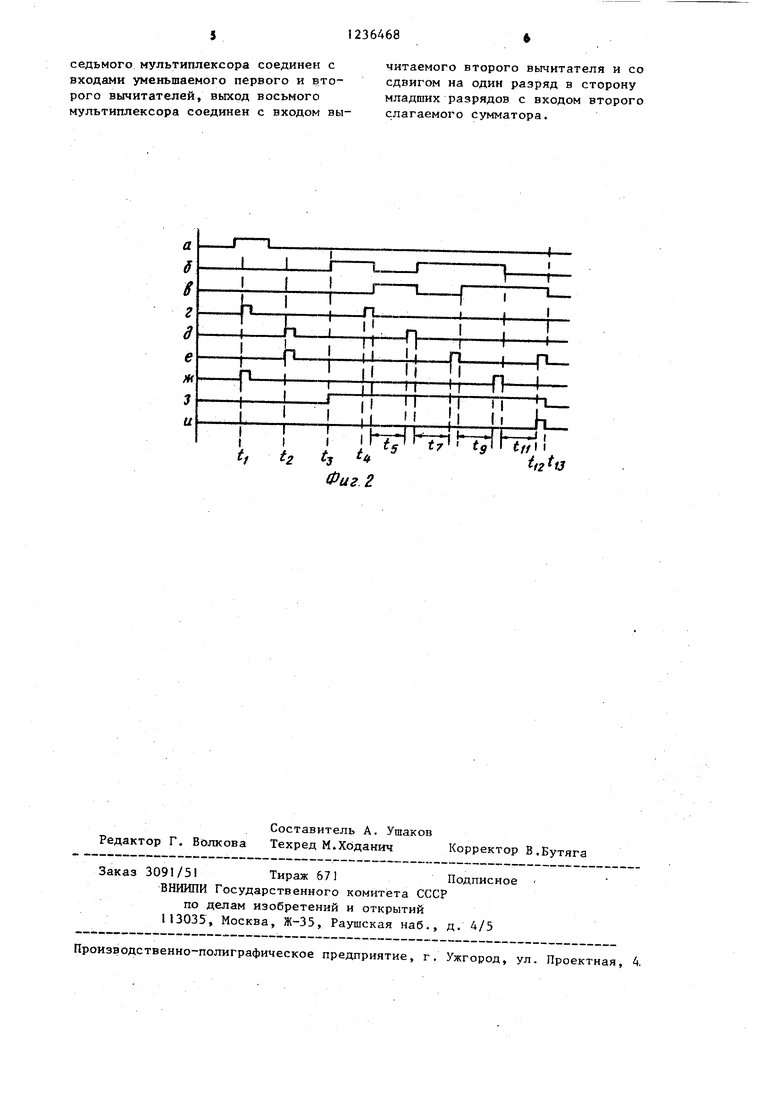

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - временная диаграмма работы устройства.

Устройство содержит распределитель 1 импульсов, с третьего по шестой мультиплексоры 2-5, с первого по шестой регистры 6-11, первый мультиплексор 12, вторую схему 13 сравнения, седьмой 14 и восьмой 15 мультиплексоры, первый 16 и второй 17 вычита- тели, сумматор 18, первую схему 19 сравнения, второй мультиплексор 20, первый 21 и второй 22 информационные входы, вход 23 запуска, информационный выход 24, выход 25 сопровождения.

Объекты, расстояния между которыми измеряют, определены координатами Х, Y и Х,, Y. В ортогональной системе координат топографическое

расстояние Ц /aX + flY

где ,j| - разность абсцисс;

- разность ординат.

Для определения истинного расстояния необходимо знать разницу высот над уровнем моря ,-h, . Следовательно, расстояние + &W .

Устройство функционирует в соответствии с приближенной зависимостью при условии А

при д- А+ .- UA о

макс

1

Q- А+ 7г В при А+ :

1- о Zо С

(О

Устройство определяет Ц и L последовательно, согласно (J).

Устройство работает следующим образом.

При включении устройства все выходы распределителя 1 импульсов устанавливаются в нулевое положение (цепи установки на фиг. I не приведены), 1

При поступлении импульса по входу

.23 запуска (фиг. 2а) распределитель 11мпульсов формирует импульс (в момент t ) на втором и шестом выходах (фиг. 2г, ж), по которому через третий 2 и пятый 4 мультиплексоры и прямо записьгеается (X,, Y , h) соответственно в первый 6, третий 8, пятый 10 регистры. Аналогично в мо

мент t формируется импульс на четвертом и пятом выходах распределителя I (фиг. 2д, е) и в регистры 7, 9 и И записывается соответственно Х.,

Y,, h.

В момент t .мультиплексоры

s

0

$

0

5

0

5

0

5

2-5 открываются по первым входам (фиг. 2з) и по первому адресному входу первого мультиплексора 12 (фиг. 2б) на ег о первый и второй выходы поступает информация соответственно с первого 6 и второго 7 регистров, т.е. Х и Х. На второй схеме 13 сравнения происходит сравнение X ,, и Х и большее из них проходит через седьмой мультиплексор 14 на вход уменьшаемого вьгчитателя 17, меньшее - через восьмой мультиплексор 15 на вход вычитаемого вьгчитателя 16, на котором происходит вычисление ДХ, знач€;ние которого в момент t (фиг. 2г) записывается в первый регистр 6. В момент t (фиг. 26, в мультиплексор 12 пропускает на выходы соответственно Y , Y (с регистров 8. и 9) , Аналогично описанному происходит формирование лУ, которое в момент t (фиг. 2д) записьгеается в регистр 7. После этого в момент t-j (фиг, 2а, б) мультиплексор 12 снова открыт для регистров 6 и 7 и на его выходы поступает ДХ и . Аналогично описанному происходит вьщеление большего и меньшего числа.

Большее число поступает на вход уменьшенного первого вычитателя 16 И со сдвигом на три разряда на вход вычитаемого, т.е. на первом вычита- теле происходит вычисление, например 7/8лХ при условии, что , которое поступает на вход первого слагаемого сумматора 18, на вход второго слагаемого которого поступает меньшее число, разделенное на два, т.е. сдвинутое монтажно на один разряд в сторону младших разрядов (в нашем случае 1/2 UY). На выходе сумматора 18 получаем результат , который поступает на вторые информационные входы первой схемы 19 сравнения и второго мультиплексора 20. На схеме 19 сравнения происходит сравнение Z и йХ и в зависимости от сравнения на выход устройства через мультиплексор 20 передается Z или дХ, которые в момент tg (фиг. 2е через открытый по первым входам шестой мультиплексор 5 записьшается в четвертый регистр 9.

3

На время t мультиплексор 2 открыт для регистров 10 и 11 (фиг.2б в) и на выходе первого вычитателя 17 формируется лЬ, аналогично дХ и йУ, который в момент t записывается через мультиплексор 4 в третий регистр 8.

После этого на время t мультиплексор 12 открывается для регистров 8 и 9 (фиг. 2б, в) и аналогично формированию Z на выходе сумматора 18

получаем т Z+ - &h, если , о /

а на выходе мультиплексора 20 результат L, который в момент t (фиг. 2е) записывается в регистр 9 и по управляющему стробу на восьмом выходе распределителя I импульсов (фиг. 2и) записывается в регистры пользователя. В момент t устройство устанавливается в исходное состояние. Значения X, , Х, Y, , Y, h , h присутствуют на входах коммутаторов и регистров во время всего цикла работы.

Формула изобретения

Устройство для вычисления значения модуля вектора, содержащее четыре регистра, два мультиплексора, сумматор, первый вычитатель, первую схему сравнения, распределитель импульсов , первый и второй выходы которого соедиьены с первым адресным входом первого мультиплексора и с входом синхронизации первого регистра соответственно, вход уменьшаемого первого вычитателя соединен с первыми информационнь ми входами первой схемы сравнения, второго мультиплексора и со сдвигом на три разряда в сторону младших разрядов с входом вычитаемого первого вычитателя, выход которого подключен к входу первого слагаемого сумматора, выход которого соединен с вторыми информационными входами первой схемы сравнения и ВТОРОГО мультиплексора, вьгход первой схемы сравнения соединен с управляющим входом второго мультиплексора вход запуска распределителя импульсов является одноименным входом устройства, отличающееся тем, что, с целью расширения класса решаемых задач, в него введены с третьего по восьмой мультиплексоры.

10

15

20

25

364684

пятый и шестой регистры, вторая схема сравнения, второй вычитатель, выход которого соединен с первыми информационными входами с третьего по пятый мультиплексоров, выходы которых соединены с информационными входами с первого по третий регистров соответственно, выходы которых соединены с первого по третий информа- ционньЫи входами первого мультиплексора, выход шестого мультиплексора соединен с информационнь м входом четвертого регистра, выход, которого ; соединен с четвертым информационным входом первого мультиплексора, информационный вход пятого регистра и вторые информационные входы третьего и пятого мультиплексоров являются первым информационньм входом устройства, выход пятого регистра соединен с пятым информационным входом первого мультиплексора, информационный вход шестого регистра и вторые информационные входы четвертого и шестого мультиплексоров являются вторым информационным входом устройства, выход шестого регистра соединен с шестым информационным входом первого мультиплексора, третий и четвертый выходы распределителя импульсов под ключены к второму адресному входу первого мультиплексора и к входу сиггхронизации второго регистра соответственно, пятый и шестой выходы распределителя импульсов подключены

5 к входам синхронизации четвертого, шестого и третьего и пятого регистров соответственно, седьмой вьгход распределителя импульсов лодключен к управлякщим входам с

0 третьего по шестой мультиплексоров, восьмой вьгход распределителя импульсов является выходом сопровождения информации устройства, выход второго мультиплексора соединен с первым

5 информационным входом шестого мультиплексора и является информационным выходом устройства, первый выход первого мультиплексора соединен с первыми информационными входами седь0 мого и восьмого мультиплексоров и

второй схемы сравнения, второй выход первого мультиплексора соединен с первыми информационными входами седьмого и восьмого мультиплексоров и

второй схемы сравнения, выходы

Больше и Меньше которой соединены с управляющими входами седьмого и восьмого мультиплексоров, выход

седьмого мультиплексора соединен с входами уменьшаемого первого и второго вычитателей, выход восьмого мультиплексора соединен с входом вычитаемого второго вычитателя и со сдвигом на один разряд в сторону младших разрядов с входом второго слагаемого сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Процессор для обработки массивов данных | 1985 |

|

SU1293737A1 |

| Устройство для вычисления координат | 1989 |

|

SU1635178A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Устройство для определения заданной ординаты корреляционной функции | 1990 |

|

SU1777152A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ТЕЛЕВИЗИОННОГО ИЗОБРАЖЕНИЯ С ИЗМЕНЕНИЕМ МАСШТАБА УПРАВЛЯЕМОГО ФРАГМЕНТА | 1993 |

|

RU2065206C1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| Вычислительное устройство для поворота вектора | 1987 |

|

SU1520511A1 |

| Цифровой квадратичный интерполятор | 1985 |

|

SU1290354A1 |

Изобретение позволяет вычислять значения модуля трехмерного вектора и может быть использовано для обработки топографических данных. Устройство содержит вычислитель приближенной зависимости 1 17/8A-H/2B при 7/8А+1/2ВёА, при 7/8А-И/2В А, выполненньй ка первом вычитателе 16, сумматоре 18, первой схеме 19 сравнения и втором мультиплексоре 20. С помощью второй схемы 13 сравнения на выходе седьмого мультиплексора 14 всегда формируется большее число, а на выходе восьмого мультиплексора 15 меньшее. Выбор двух исходных величин для вычислений осуществляетсА первым мультиплексором 12. Исходные и промежуточные результаты вычислений хранятся в регистрах 6-1 I . Работой устройства управляет распределитель 1 импульсов. 2 ил. сл 23- ю со О) 4 О) 00

| Вычислительное устройство | 1982 |

|

SU1096640A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Метод получения 4-фенил-4-метил-1,3диоксана | 1950 |

|

SU96854A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-07—Публикация

1984-12-03—Подача