Изобретение относится к вычислительной технике, в частности к регистровым запоминающим устройствам.

Цель изобретения - раси ирение области применения устройства за счет возможности записи информации в произвольном порядке.

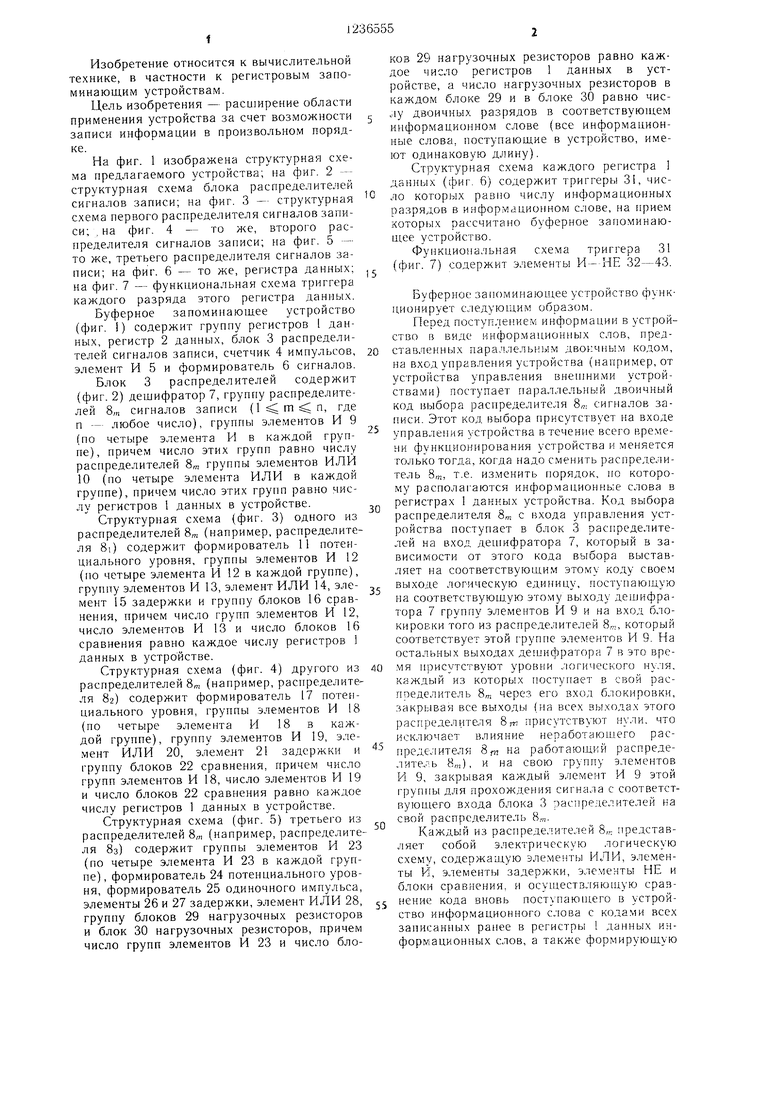

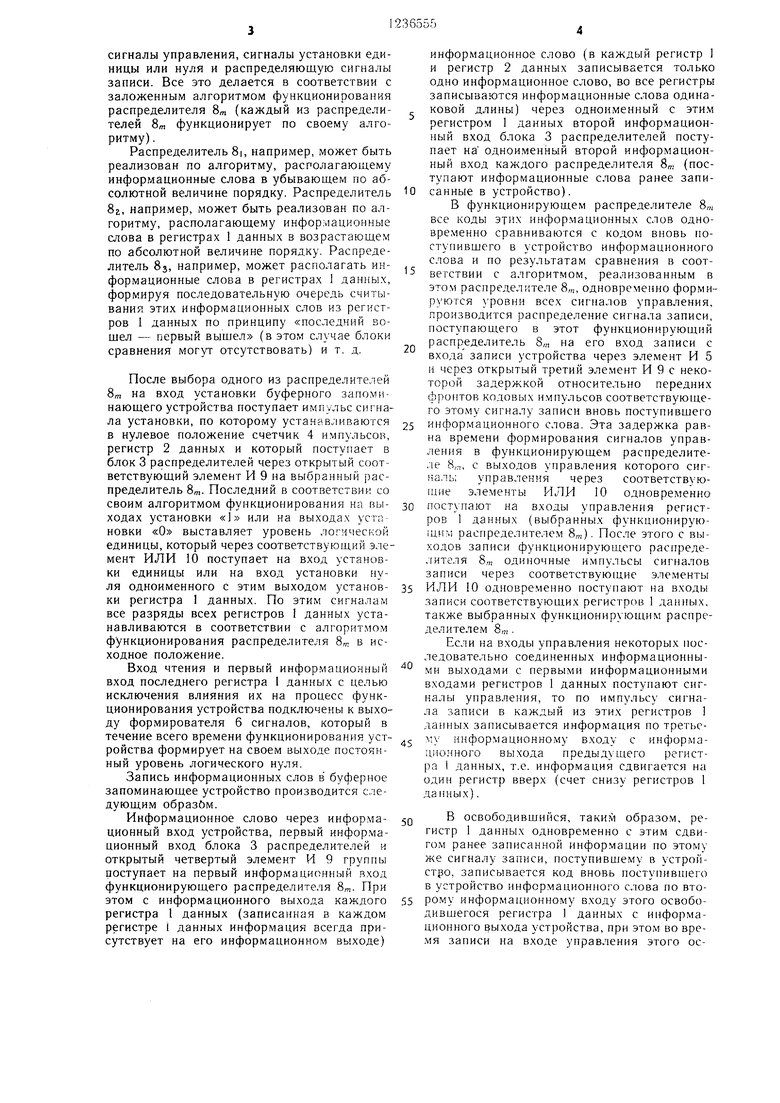

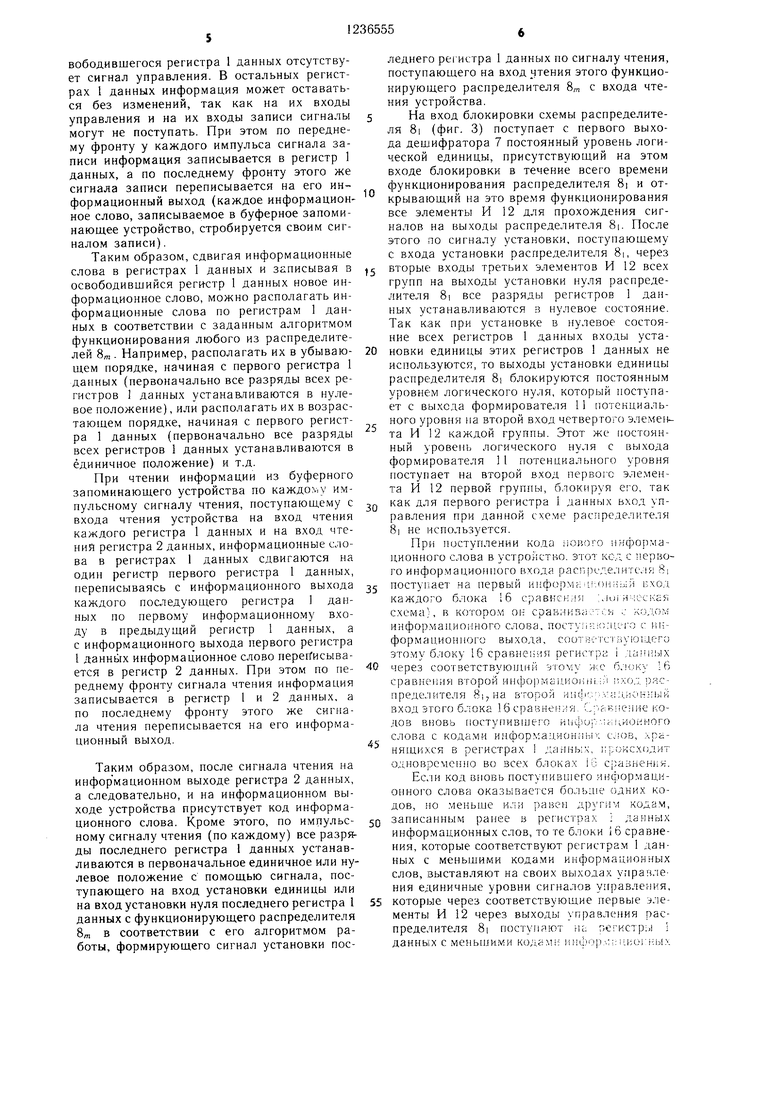

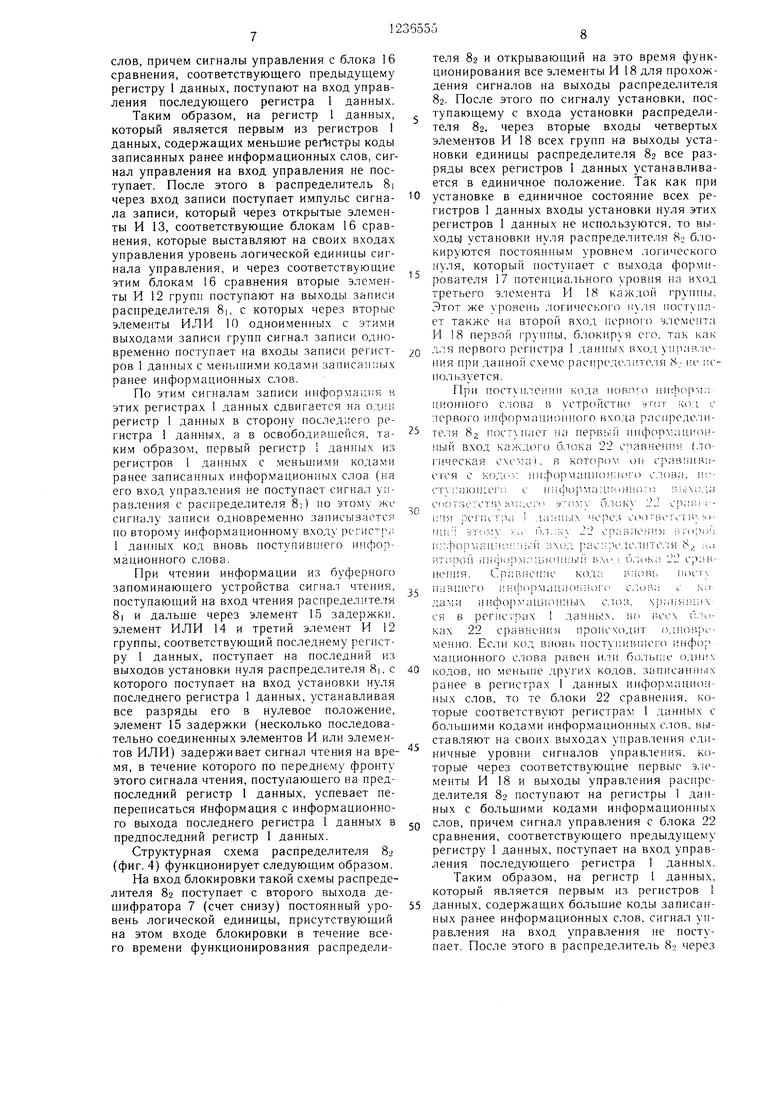

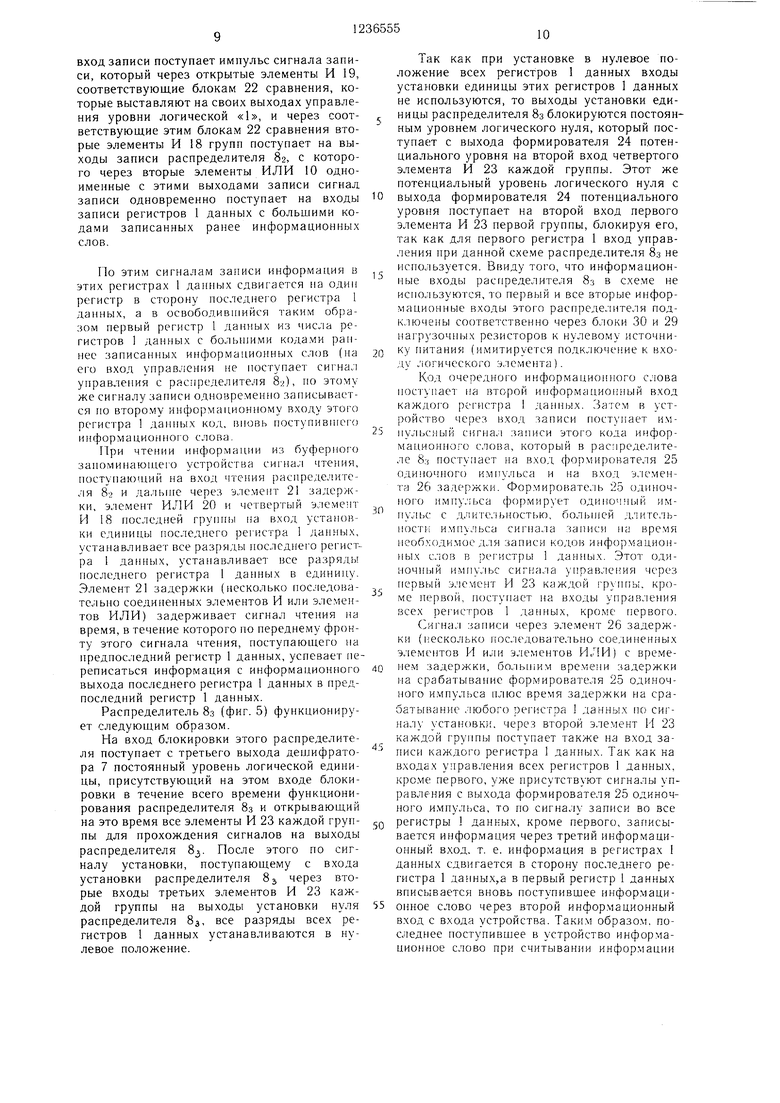

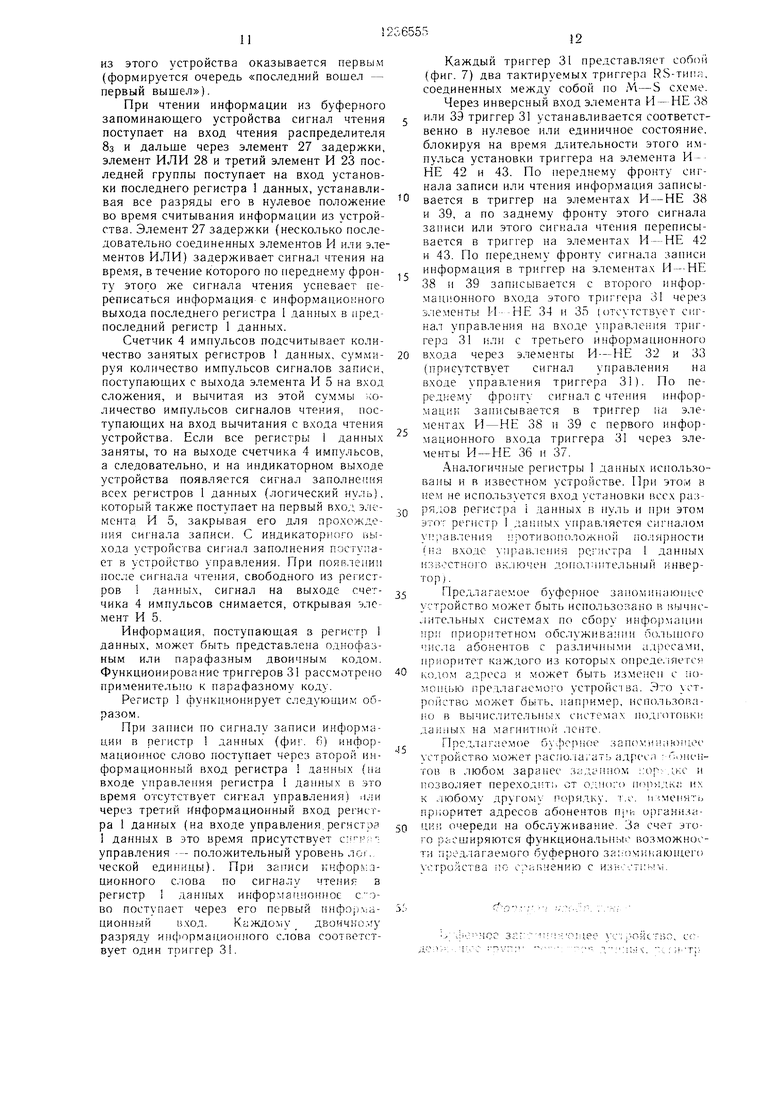

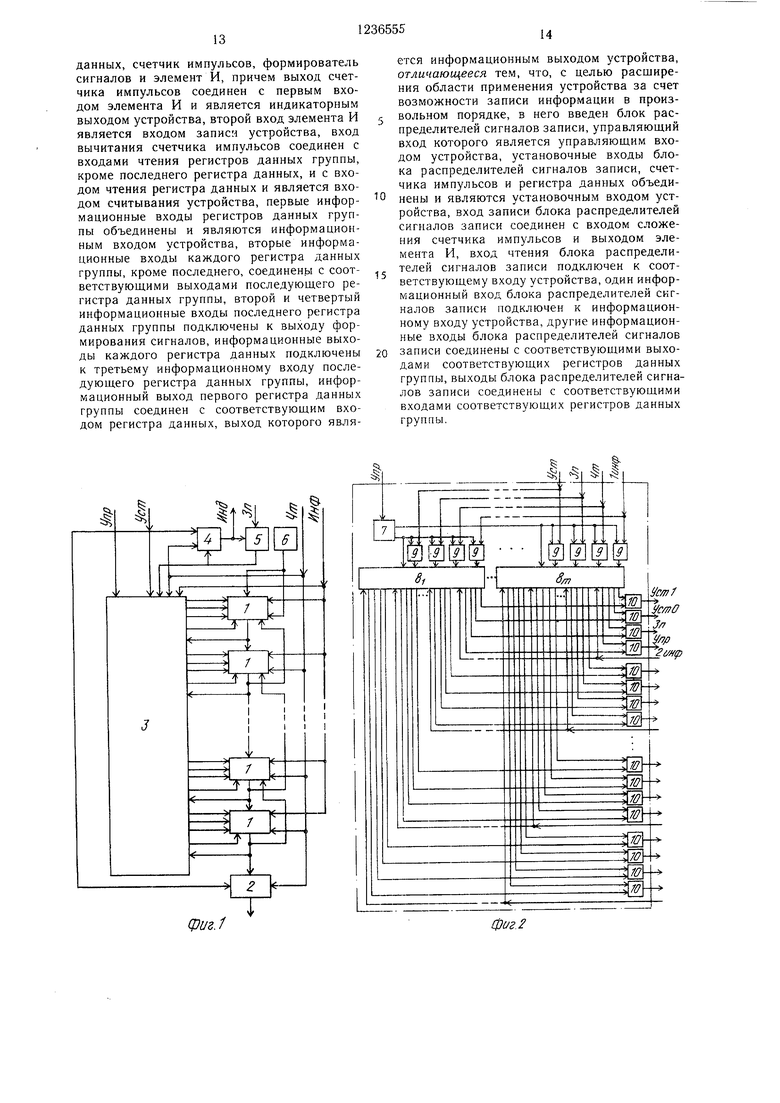

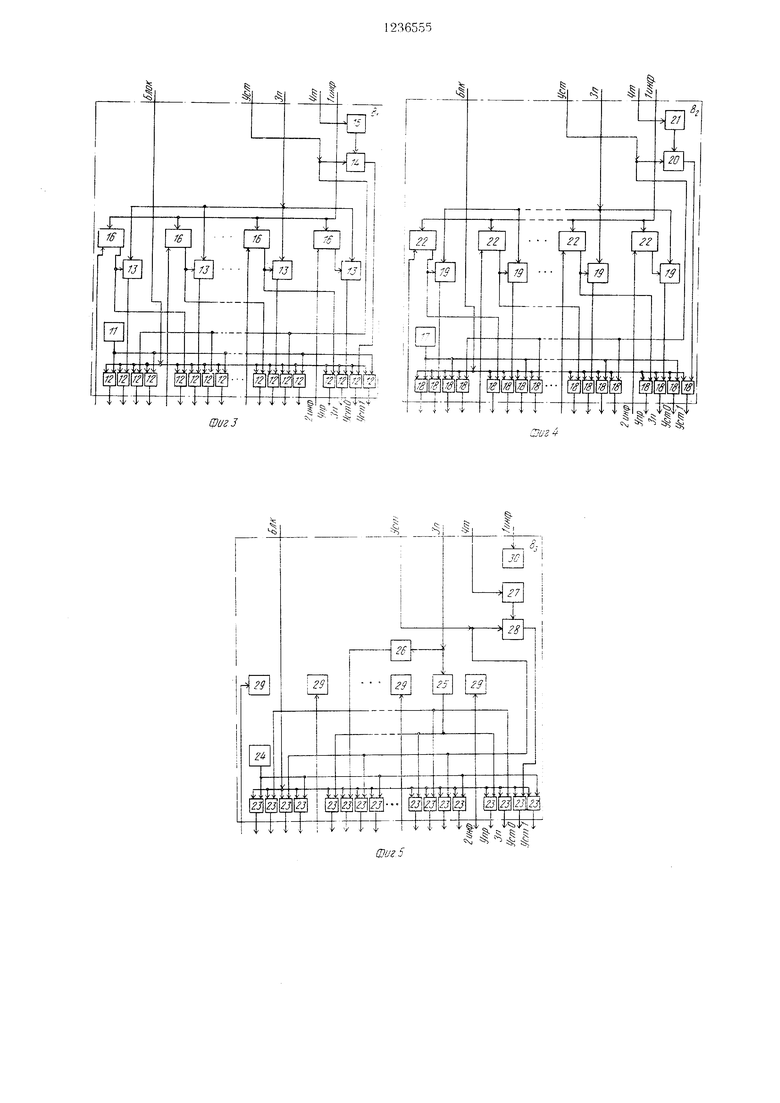

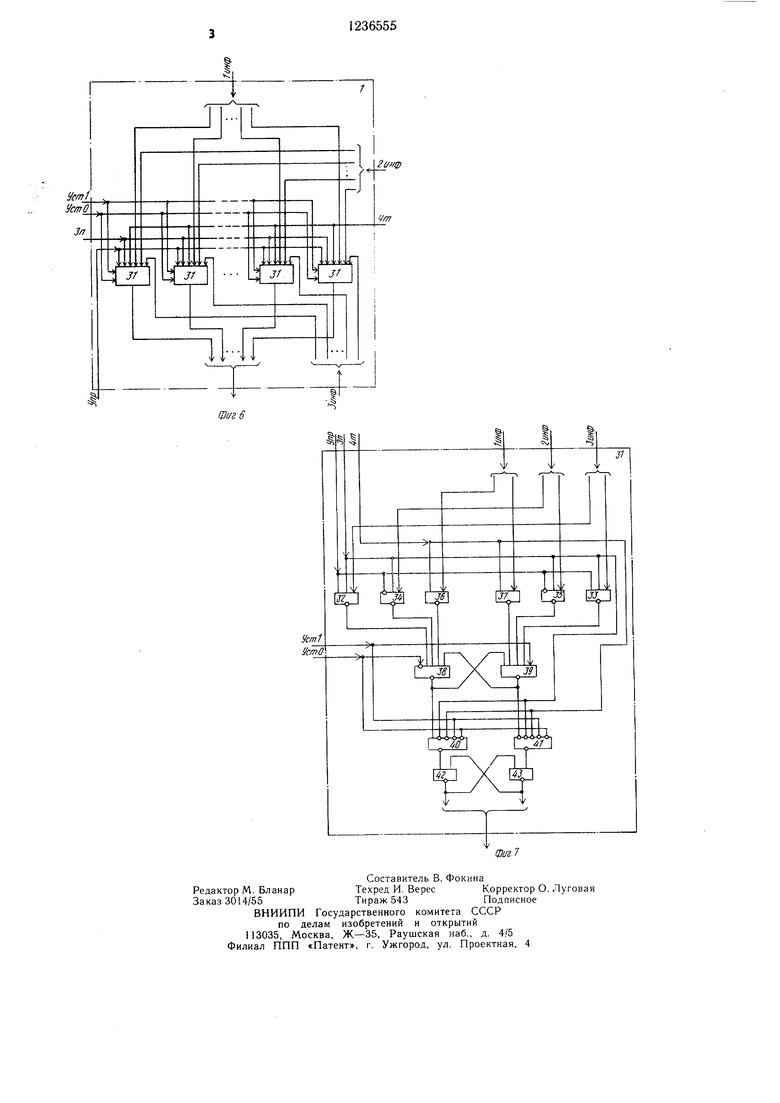

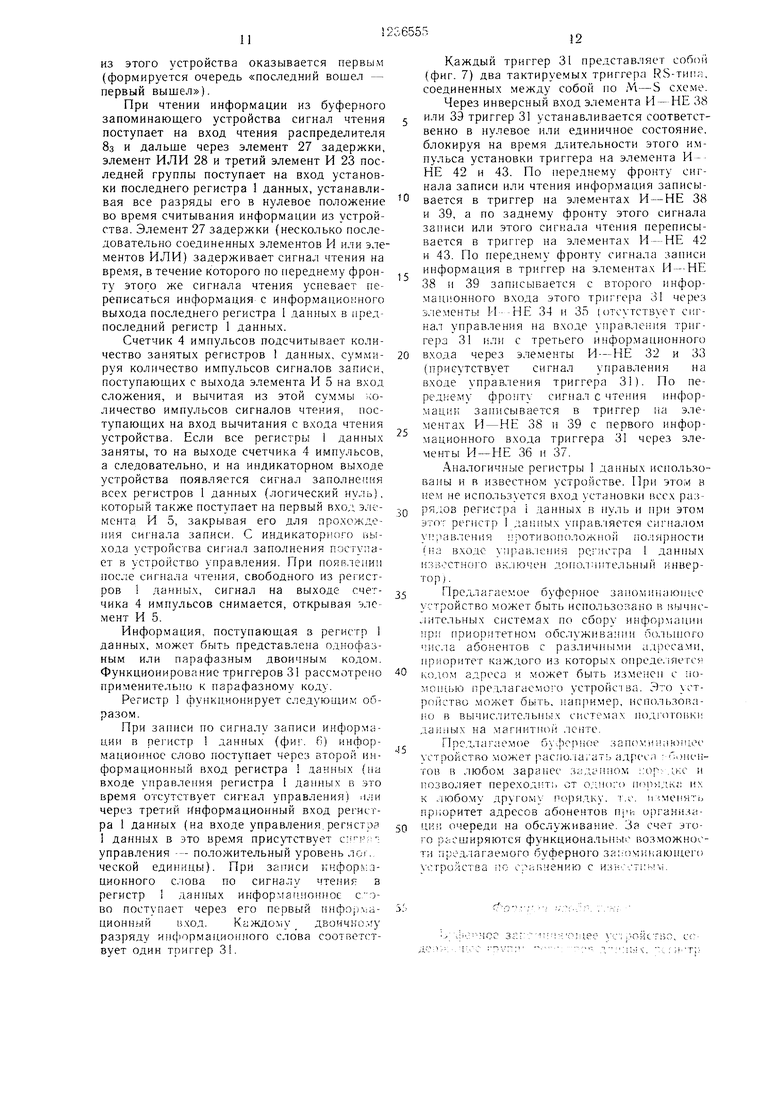

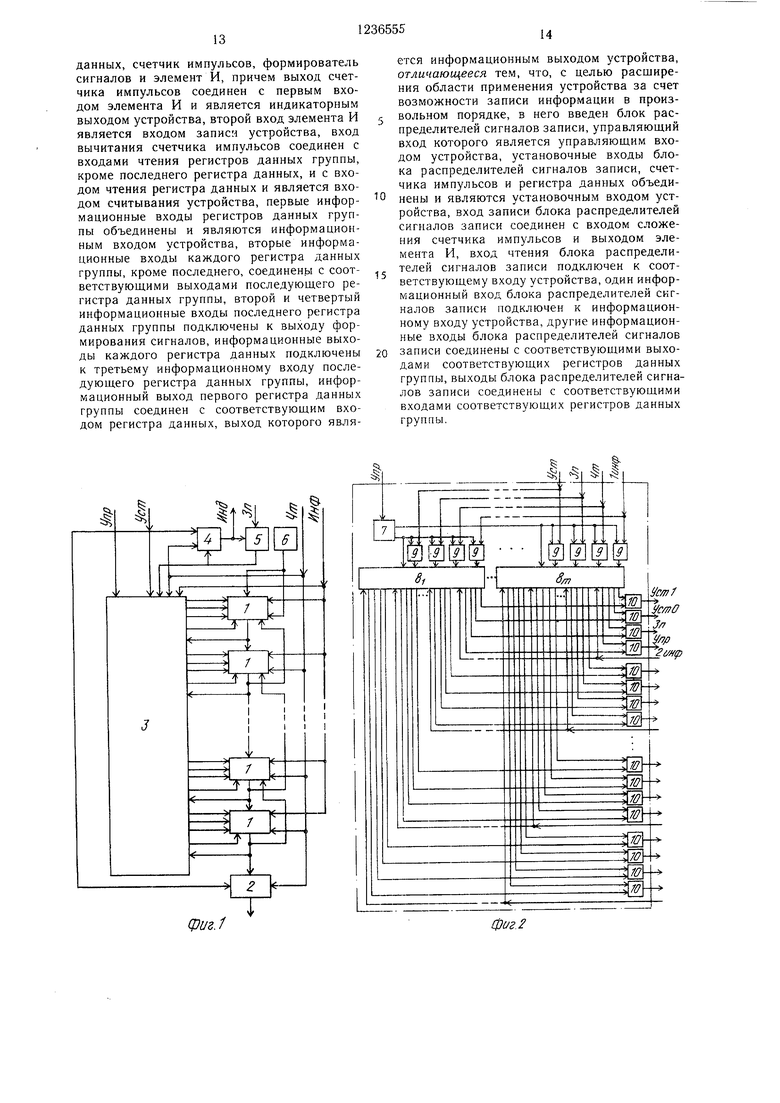

На фиг. 1 изображена структурная схема предлагаемого устройства; на фиг. 2 -- структурная схема блока распределителей сигналов записи; на фиг. 3 - структурная схема первого распределителя сигналов записи; .на фиг. 4 - то же, второго распределителя сигналов записи; на фиг. 5 - то же, третьего распределителя сигналов записи; на фиг. 6 - то же, регистра данных; на фиг. 7 - функциональная схема триггера каждого разряда этого регистра данных.

Буферное запоминающее устройство (фиг. ) содержит группу регистров i данных, регистр 2 данных, блок 3 распределителей сигналов записи, счетчик 4 импульсов, элемент И 5 и формирователь 6 сигналов.

Блок 3 распределителей содержит (фиг. 2) дещифратор 7, группу распределителей 8,„ сигналов записи (1 г m п, где п - любое число), группы элементов И 9 (по четыре элемента И в каждой группе), причем число этих групп равно числу распределителей 8т группы элементов ИЛИ 10 (по четыре элемента ИЛИ в каждой группе), причем число этих групп равно числу регистров 1 данных в устройстве.

Структурная схема (фиг. 3) одного из распределителей 8т (например, распределителя 8i) содержит формирователь 1 потенциального уровня, группы элементов И 12 (по четыре элемента И 12 в каждой группе), группу элементов И 13, элемент ИЛИ 14, эле- мент 15 задержки и группу блоков 16 сравнения, причем число групп элементов И 12, число элементов И 13 и число блоков 16 сравнения равно каждое числу регистров 1 данных в устройстве.

Структурная схема (фиг. 4) другого из распределителей 8т (например,распределителя 82) содержит формирователь 17 потенциального уровня, группы элементов И 18 (по четыре элемента И 18 в каждой группе), группу элементов И 19, элемент ИЛИ 20, элемент 21 задержки и группу блоков 22 сравнения, причем число групп элементов И 18, число элементов И 19 и число блоков 22 сравнения равно каждое числу регистров 1 данных в устройстве.

Структурная схема (фиг. 5) третьего из распределителей 8,„ (например, распределителя 8з) содержит группы элементов И 23 (по четыре элемента И 23 в каждой группе), формирователь 24 потенциального уровня, формирователь 25 одиночного импульса, элементы 26 и 27 задержки, элемент ИЛИ 28, группу блоков 29 нагрузочных резисторов и блок 30 нагрузочных резисторов, причем число групп элементов И 23 и число бло5

0

„

j

0

ков 29 нагрузочных резисторов равно каждое число регистров 1 данных в устройстве, а число нагрузочных резисторов в каждом блоке 29 и в блоке 30 равно числу двоичных разрядов в соответствуюихем информационном слове (все информационные слова, поступающие в устройство, имеют одинаковую длину).

Структурная схема каждого регистра данных (фиг. 6) содержит триггеры 3, число которых равно числу информационных разрядов в информационном слове, на прием которых рассчитано буферное запоминающее устройство.

Функциональная схема триггера 31 (фиг. 7) содержит элементы И---НЕ 32-43.

Буферное запоминающее устройство функционирует следующим образом.

Перед поступлением информации в устройство в виде информационных слов, представленных парал;1елы-П)м двоичным кодом, на вход управления устройства (например, от устройства управления устройствами) поступает параллельный двоичный код выбора распределителя 8„, сигналов записи. Этот код выбора присутствует на входе управления устройства в течение всего вре.ме- ни функционирования устройства и меняется только тогда, когда надо сменить распределитель 8т, т.е. изменить порядок, но которому располагаются информационные слова в регистрах 1 данных устройства. Код выбора распределителя 8 с входа управления устройства поступает в блок 3 распределителей на вход дешифратора 7, который в зависимости от этого кода выбора выставляет на соответствующим этому коду своем выходе логическую единицу, поступающую на соответствующую этому выходу дешифратора 7 группу элементов И 9 и на вход блокировки того из распределителей 8,,,, который соответствует этой группе элементов И 9. На остальных выходах дешифратора 7 в это вре- .мя присутствуют уровни логического ну;1я, каждый из которых р.остунает в свой распределитель 8т через его вход блокировки, .закрывая все выходы (на всех выходах этого распределителя Вгл присутствуют нули, что исключает влияние неработающего распределителя 8гл на работаюпдий распреде- 8,,;), и на свою группу элементов И 9, закрывая каждый элемент И 9 этой rpyrnibi для прохождения сигнала с соответствующего входа блока 3 распределителей на свой распределитель 8,„.

Каждый из распределителей 8„: представляет собой электрическую логическую схему, содержащую элементы ИЛИ, элементы И, элементы задержки, элементы НЕ и блоки сравнения, и осун1естБляющую сравнение кода вновь поступаюп1его в устройство информационного с. юва с кодами всех записанных ранее в регистры 1 данных информационных слов, а также формирующую

сигналы управления, сигналы установки единицы или нуля и распределяющую сигналы записи. Все это делается в соответствии с заложенным алгоритмом функционирования распределителя 8т (каждый из распределителей 8т функционирует по своему алгоритму) .

Распределитель 8i, например, может быть реализован по алгоритму, располагающему информационные слова в убывающем по абсолютной величине порядку. Распределитель 8г, например, может быть реализован по алгоритму, располагающему информационные слова в регистрах 1 данных в возрастающем по абсолютной величине порядку. Распределитель 8з, например, может располагать информационные слова в регистрах 1 данных, формируя последовательную очередь считывания этих информационных слов из регистров 1 данных по принципу «последний во- щел - первый выщел (в этом случае блоки сравнения могут отсутствовать) и т. д.

После выбора одного из распределителей 8т на вход установки буферного запоминающего устройства поступает импульс сигнала установки, по которому устанавливаются в нулевое положение счетчик 4 импульсов, регистр 2 данных и который поступает в блок 3 распределителей через открытый соответствующий элемент И 9 на выбранный распределитель 8т. Последний в соответствии со своим алгоритмом функционирования на выходах установки «1 или на выходах установки «О выставляет уровень логической единицы, который через соответствующий элемент ИЛИ 10 поступает на вход установки единицы или на вход установки fiy- ля одноименного с этим выходом установки регистра 1 данных. По этим сигналам все разряды всех регистров 1 данных устанавливаются в соответствии с алгоритмом функционирования распределителя 8; в исходное положение.

Вход чтения и первый инфор.мационный вход последнего регистра I данных с целью исключения влияния их на процесс функционирования устройства подключены к выходу формирователя 6 сигналов, который в течение всего времени функционирования устройства формирует на своем выходе постоянный уровень логического нуля.

Запись информационных слов в буферное запоминающее устройство производится сле- дующи.м образйм.

Информационное слово через информационный вход устройства, первый информационный вход блока 3 распределителей и открытый четвертый элемент И 9 группы поступает на первый информационный вход функционирующего распределителя 8т. При этом с информационного выхода каждого регистра 1 данных (записанная в каждом регистре 1 данных информация всегда присутствует на его информационном выходе)

0

информационное слово (в каждый регистр 1 и регистр 2 данных записывается только одно информационное слово, во все регистры записываются информационные слова одинаковой длины) через одноименный с этим регистром I данных второй информационный вход блока 3 распределителей поступает на однои.менный второй информационный вход каждого распределителя 8т (поступают информационные слова ранее запи0 санные в устройство).

В функционирующем распределителе 8„, все коды этих информационных слов одновременно сравниваются с кодом вновь по- ступивщего в устройство информационного слова и по результатам сравнения в соот5 вегствии с алгоритмом, реализованным в этом распределителе 8,,,, одновременно формируются уровни всех сигналов управления, производится распределение сигнала записи, поступающего в этот функционирующий распределитель 8ш на его вход записи с входа записи устройства через элемент И 5 и через открытый третий элемент И 9 с некоторой задержкой относительно передних фронтов кодовых импульсов соответствуюи1.е- го этому сигналу записи вновь поступивщего

5 инфopгvlaциoннoгo слова. Эта задержка равна времени формирования сигналов управления в функционирующем распределите- .ле 8,;,, с выходов управления которого сиг- ь:аль: управления через соответствующие элементы ИЛИ 10 одновременно

0 поступают на входы управления регистров 1 данных (выбранных функционирующим распределителем 8,„). После этого с выходов записи функционирующего распределителя 8т одиночные и.мпульсы сигналов записи через соответствующие элементы

5 ИЛИ 10 одновременно поступают на входы записи соответствующих регистров 1 данных, также выбранных функционируюн1им распределителем 8,,,.

Если на входы управления некоторых последовательно соединенных информационны ми выходами с первыми информационными входами регистров 1 данных поступают сигналы управления, то по импульсу сигнала записи в каждый из этих регистров 1 данных записывается информация по третье5 му информационному входу с информа- цмонного выхода предыдущего регистра 1 данных, т.е. информация сдвигается на один регистр вверх (счет снизу регистров 1 данных).

QВ освободивщийся, таким образом, регистр 1 данных одновременно с этим сдвигом ранее записанной информации по этому же сигналу записи, поступивщему в устрой- CTJ30, записывается код вновь поступивн1его в устройство информационного слова по вто5 рому информационному входу этого освобо- дивщегося регистра 1 данных с информационного выхода устройства, при этом во вре- .мя записи на входе управления этого освободившегося регистра 1 данных отсутствует сигнал управления. В остальных регистрах 1 данных информация может оставаться без изменений, так как на их входы управления и на их входы записи сигналы могут не поступать. При этом по переднему фронту у каждого импульса сигнала записи информация записывается в регистр 1 данных, а по последнему фронту этого же сигнала записи переписывается на его информационный выход (каждое информационное слово, записываемое в буферное запоминающее устройство, стробируется своим сигналом записи).

Таким образом, сдвигая информационные слова в регистрах 1 данных и записывая в освободившийся регистр 1 данных новое информационное слово, можно располагать информационные слова по регистрам 1 данных в соответствии с заданным алгоритмом функционирования любого из распределителей 8т . Например, располагать их в убывающем порядке, начиная с первого регистра 1 данных (первоначально все разряды всех регистров 1 данных устанавливаются в нулевое положение), или располагать их в возрастающем порядке, начиная с первого регистра 1 данных (первоначально все разряды всех регистров 1 данных устанавливаются в единичное положение) и т.д.

При чтении информации из буферного запоминающего устройства по каждо,у импульсному сигналу чтения, поступающему с входа чтения устройства на вход чтения каждого регистра 1 данных и на вход чтения регистра 2 данных, информационные слова в регистрах 1 данных сдвигаются на один регистр первого регистра 1 данных, 1ереписываясь с информационного выхода каждого последующего регистра 1 данных по первому информационному входу в предыдущий регистр 1 данных, а с информационного выхода первого регистра 1 даннь1х информационное слово перегТисыва- ется в регистр 2 данных. При этом по переднему фронту сигнала чтения информация записывается в регистр 1 и 2 данных, а по последнему фронту этого же сигнала чтения переписывается на его информационный выход.

Таким образом, после сигнала чтения на инфор мационном выходе регистра 2 данных, а следовательно, и на информационном выходе устройства присутствует код информационного слова. Кроме этого, по импульсному сигналу чтения (по каждому) все разряды последнего регистра 1 данных устанавливаются в первоначальное единичное или нулевое положение с помощью сигнала, поступающего на вход установки единицы или на вход установки нуля последнего регистра 1 данных с функционирующего распределителя 8т в соответствии с его алгоритмом работы, формирующего сигнал установки последнего регистра 1 данных по сигналу чтения, поступающего на вход чтения этого функционирующего распределителя 8, с входа чтения устройства.

На вход блокировки схемы распределителя 8i (фиг. 3) поступает с первого выхода дешифратора 7 постоянный уровень логической единицы, присутствующий на этом входе блокировки в течение всего времени функционирования распределителя 8i и открывающий на это время функционирования все элементы И 12 для прохождения сигналов на выходы распределителя 8|. После этого по сигналу установки, поступающему с входа установки распределителя 8i, через

5 вторые входы третьих элементов И 12 всех групп на выходы установки нуля распределителя 8i все разряды регистров 1 данных устанавливаются з нулевое состояние. Так как при установке в нулевое состояние всех регистров 1 данных входы уста0 новки единицы этих регистров 1 данных не используются, то выходы установки единицы распределителя 8i блокируются постоянным уровнем логического нуля, который поступает с выхода формирователя 11 потенциального уровня на второй вход четвертого элеме11- та И 12 каждой группы. Этот же постоянный уровень логического нуля с Г5ыхода формирователя 11 потенциального уровня поступает на второй вход первого элемента И 12 первой группы, блокируя его, так

Q как для первого регистра данных вход управления при данной схеме расгфе.аелителя 8| не используется.

При поступлении кода ноиого 1|нформа- ционного слова в устройство, этот код с первого инфор.мациорпюго входа рас11|1слелитс. 1и 8i

J поступает на первый И1 фоплимгпипи:й вход каждого б.чока 16 сравкскля ini ическая схема), в котором ок срав:- ИБ;к Т;; - .; ко;;,ом информап.иомного слова, поступ:;;;;л1его с И1 форм анионного выхода, соотнс Тств |О цегс) этому блоку 16 сравне1И1я регистра i ./laiiHijix

0 через соответствующий этому же O.IOKV 16 сравнения второй информанионн :; I .xo::. рас- преде.1ителя второй ииф .::-.,ионный вход этого блока 16 сравнения. Срг;кпе; не кодов вновь ноступившег о йн4юр-.;;;ииоиного слова с кодами инфop ;aциoн iьn; слов, хранящихся в регистрах даннь;х, 1;роксх ;дит о.;аювроменно во всех блоках 16 с|;азнени ;. Если код вновь постунивн1его информащ - ОПН01Х) слова оказывается болыне (JAHHX кодов, но .меньше или равен другиг-л кодам,

Q записанным ранее в регнстр.ях ; данных информационных слов, то те блоки 16 сравнения, которые соответствуют регистрам 1 данных с меньшими кодами информационных слов, выставляют на своих выходах управления единичные уровни сигналов управления,

5 которые через соответствующие первые э.че- менты И 12 через выходы управления распределителя 8i поступают иг погистры i

данных с MeHBHJHMH КОЛЙЛП; ИНи)Орл:;:иИ01 Н1 1Х

5

слов, причем сигналы управления с блока 16 сравнения, соответствующего предыдущему регистру 1 данных, поступают на вход управления последующего регистра 1 данных.

Таким образом, на регистр 1 данных, который является первым из регистров 1 данных, содержащих меньщие регистры коды записанных ранее информационных слов, сигнал управления на вход управления не поступает. После этого в распределитель 8i через вход записи поступает импульс сигнала записи, который через открытые элементы И 13, соответствующие блокам 16 сравнения, которые выставляют на своих входах управления уровень логической единицы сигнала управления, и через соответствующие этим блокам 16 сравнения вторые элементы И 12 групп поступают на выходы записи распределителя Si, с которых через вторые элементы ИЛИ 10 одноименных с этими выходами записи групп сигнал записи одновременно поступает на входы записи регистров 1 данных с меньшими кодами записань ых ранее информационных слов.

По этим сигналам записи информаиия н этих регистрах 1 данных сдвигается на о;ии регистр 1 данных в сторону последнего регистра 1 данных, а в освободившейся, таким образом, первый регистр 1 данных из регистров 1 данных с меньшими кодами ранее записанных информационных слов (на его вход управления не поступает сигнал управления с распределителя 8i) но этому же- сигналу записи одновре.менно записыз.аотся по второму информационному входу регист-г-,1 1 данпых код вновь поступившего информационного слова.

При чтении информации из буферного запоминающего устройства сигнал чтения, поступающий на вход чтения распредел теля 8| и дальше через элемент 15 задержки, элемент ИЛИ 14 и третий элемент И 12 группы, соответствующий последнему регистру 1 данных, поступает на последний из выходов установки нуля распределителя 8i, с которого поступает на вход установки нуля последнего регистра 1 данных, устанавливая все разряды его в нулевое положение, элемент 15 задержки (несколько последовательно соединенных элементов И или элементов ИЛИ) задерживает сигнал чтения на время, в течение которого по переднему фронту этого сигнала чтения, поступающего на прелТ,- последний регистр 1 данных, успевает пе- переписаться информация с информационного выхода последнего регистра 1 данных в предпоследний регистр 1 данных.

Структурная схе.ма распределителя 8- (фиг. 4) функционирует следующим образом.

На вход блокировки такой схемы распределителя 82 поступает с второго выхода дешифратора 7 (счет снизу) постоянный уровень логической единицы, присутствующий на этом входе блокировки в течение всего времени функционирования распредели0

5

О

теля 82 и открывающий на это время функционирования все элементы И 18 для прохождения сигналов на выходы распределителя 82. После этого по сигналу установки, поступающему с входа установки распределителя 82, через вторые входы четвертых элементов И 18 всех групп на выходы установки единицы распределителя 82 все разряды всех регистров 1 данных устанавливается в единичное положение. Так как при установке в единичное состояние всех регистров 1 данных входы установки нуля этих регистров 1 данных не используются, то выходы установки нуля распределителя 8 блокируются постоянным уровнем логического нуля, который иостунает с выхода формирователя 17 потенциального уровня на вход третьего элемента И 18 каждой группы. Этот же уровень .чогического нуля поступает также на второй вход (iopiioro элемента И 18 первой группы, б.юкируя ci o. так как для перво1-о регистра 1 данных вход yunai.io- ния при данно схеме рас11ре,1,с. 1| те. 8;. lu используется.

11ри поступлении кода iioRiV o ин:Ь(Н1м:; ционного слова в устройство ч гот код с lepBOiXT И1 формацио111 ого входа Пспродс. те, 1Я 8 поступает на первь пый вход каждо1 о блока 22 o laBiJeniis; (ло гяческая схол;;:), в котором ori cpawnim; - ется с KO;UM: ипформапионпо Ч) C,IOB;I. п;-- CT ;;;oKjii;s4 ;: с инцюрмп цн ишоуо .ui

лами инфор. ационных с я в perHcrptix 1 . X. ках 22 сравнения происходит о,чног.{ч - меняо. Если код внов1 rioCTyr.MBiiicro иифор мационного слова равен или болыне одш х кодов, но меньпге других кодов, записанных ранее в регистрах 1 данных информапио - ных слов, то те блоки 22 сравнения, которые соответствуют регистрам I даннь1х с большими кодами информационных слов, выставляют на своих выходах управления единичные уровни сигналов управления, которые через соответствующие первые s.ie- менты И 18 и выходы управления распределителя 82 поступают на регистры 1 данных с большими кодами информационных слов, причем сигнал управления с блока 22 сравнения, соответствующего предыдущему регистру 1 данных, поступает на вход управления последующего регистра 1 данных. Таким образом, на регистр 1 данных, который является первым из регистров 1 данных, содержащих большие коды записанных ранее информационных слов, сигнал управления на вход управления не поступает. После этого в распределитель 82 через

вход записи поступает импульс сигнала записи, который через открытые элементы И 19, соответствующие блокам 22 сравнения, которые выставляют на своих выходах управления уровни логической «1, и через соответствующие этим блокам 22 сравнения вторые элементы И 18 групп поступает на выходы записи распределителя 82, с которого через вторые элементы ИЛИ 10 одноименные с этими выходами записи сигнал записи одновременно поступает на входы записи регистров 1 данных с большими кодами записанных ранее информационных слов.

По этим сигналам записи информация в этих регистрах 1 данных сдвигается на один регистр в сторону последнего регистра 1 данных, а в освободившийся таким образом первый регистр 1 данных из чис;1а регистров 1 данных с большими кодами раннее записанных информационных слов (на ei o вход управления не поступает сигна; управления с распределителя 8:), по этому же сигналу записи одновременно записывается по второму информационному входу этого регистра 1 данных код, вновь ноступивнгего информационного слова.

При чтении информации из буферного заноминаюн1е1 О устройства си1Ч1ал чтения, поступаю ций на вход чтения распределителя 8 и дальше через элемент 21 задержки, элемент ИЛИ 20 и четвертый элеме гг И 18 носледней гругни на вход установки единицы последнего регистра 1 данных, устанавливает все разряды последнего регистра 1 данных, устанавливает все разряды последнего регистра 1 данных в единицу. Элемент 21 задержки (несколько последовательно соединенных элементов И или элементов ИЛИ) задерживает сигнал чтения на время, в течение которого но нереднему фронту этого сигнала чтения, поступающего на предпос;1едний регистр 1 данных, успевает переписаться информация с информационного выхода последнего регистра 1 данных в предпоследний регистр 1 данных.

Распределитель 8з (фиг. 5) функционирует следующим образом.

На вход блокировки этого распределителя поступает с третьего выхода дешифратора 7 постоянный уровень логической единицы, присутствующий на этом входе блокировки в течение всего времени функционирования распределителя 8з и открывающий на это время все элементы И 23 каждой группы для прохождения сигналов на выходы распределителя 8j. После этого по сигналу установки, поступающему с входа установки распределителя 8 через вторые входы третьих элементов И 23 каждой группы на выходы установки нуля распределителя 83, все разряды всех регистров 1 данных устанавливаются в нулевое ноложение.

0

5

0

5

Так как при установке в нулевое положение всех регистров 1 данных входы установки единицы этих регистров 1 данных не используются, то выходы установки единицы распределителя 8з блокируются постоянным уровнем логического нуля, который поступает с выхода формирователя 24 потенциального уровня на второй вход четвертого элемента И 23 каждой группы. Этот же потенциальный уровень логического нуля с выхода формирователя 24 потенциального уровня поступает на второй вход первого элемента И 23 первой группы, блокируя его, так как для первого регистра 1 вход управления при данной схе.ме распределителя 8з не используется. Ввиду того, что информационные входы распределителя 8з в схе.ме не используются, то первый и все вторые информационные входы этого распределителя подключены соответственно через блоки 30 и 29 нагрузочных резисторов к нулевому источнику питания (имитируется подк.чючение к входу логического элемента).

Код очередного информационного слова поступает на второй информацио| иый вход каждог о регистра I данных. Затем в устройство через вход гшписи поступает н,- иульсный сигнал записи этого кода информационного слова, который в распределителе 8;j поступает ня вход формирователя 25 одиночного импульса и на вход э. 1емен- та 26 задержки. Формировате.ль 25 одиночного импу„ :ьса формирует одипоч 1ый импульс с д.аительностью, бол1зП1ей длитель- nocTii импульса сигнала запис.и на время яеобходи.мое для записи кодов информационных слов в регистры 1 данных. Этот одиночный импульс сигнала управле1шя через первый элемент И 23 каждой rpvnrib, кроме П(РБОЙ, поступает па входы управ:1ения всех ре1 истров 1 данных, кроме первого.

С лг1ии записи через элемент 26 задержки (несколько последовательно соединенных э,лементов И или элементов И/1И) с временем задержки, больптм вре.меии задержки иа срабатыва1П1е формирователя 25 одиночного импульса плюс время задержки на срабатывание любого регистра данных по сигналу установки, чере.- второй элемент 1-1 23 каждой группы поступает также на вход записи каждого регистра 1 данных. Так как на входах управления всех регистров 1 данных, кро.ме первого, уже присутствуют сигналы управления с выхода формирователя 25 одиноч- }joro импульса, то по сигналу записи во все регистры 1 данных, кроме первого, записывается информация через третий информационный вход. т. е. информация в регистрах 1 данных сдвигается в сторону последнего регистра 1 данных,а в первый регистр 1 данных вписывается вновь поступившее инфор.маци- онпое слово через второй информационный вход с входа устройства. Таким образом, последнее поступившее в устройство информационное слово при считывании информации

данных, сигнал на выходе счет

11

из этого устройства оказывается первым (формируется очередь «последний вошел - первый вышел).

При чтении информации из буферного запоминающего устройства сигнал чтения поступает на вход чтения распределителя 8з и дальше через элемент 27 задержки, элемент ИЛИ 28 и третий элемент И 23 последней группы поступает на вход установки последнего регистра 1 данных, устанавливая все разряды его в нулевое положение во время считывания информации из устройства. Элемент 27 задержки (несколько последовательно соединенных элементов И или элементов ИЛИ) задерживает сигнал чтения на время, в течение которого по переднему фрон- ту этого же сигнала чтения успевает переписаться информация с информационного выхода последнего регистра 1 данных в предпоследний регистр 1 данных.

Счетчик 4 импульсов подсчитывает количество занятых регистров 1 данных, сумми- руя количество импульсов сигналов записи, поступающих с выхода элемента И 5 на вход сложения, и вычитая из этой сум.мы количество импульсов сигналов чтения, поступающих на вход вычитания с входа чтения устройства. Если все регистры 1 данных заняты, то на выходе счетчика 4 импульсов, а следовательно, и на индикаторном выходе устройства появляется сигнал заполнения всех регистров 1 данных (логический нуль), который также поступает на первый BXO;I эл-с- мента И 5, закрывая его для прохожде- н ия сигнала записи. С индикаторного иы- хода устройства сигнал заполнения поступает в устройство управления. При появлении после сигр1ала чтения, свободного из регистров

чика 4 импульсов снимается, открывая элемент И 5.

Информация, поступающая з регистр 1 данных, может быть представлена однофазным или парафазным двоичным кодом. Функционирование триггеров 31 рассмотрено применительно к парафазному коду.

Регистр 1 функционирует следующим образом.

При записи по сигналу записи информации в регистр 1 данных (фиг . б) информационное слово поступает через второй информационный вход регистра 1 данных (на входе управлении регистра 1 данных в это время отсутствует сигнал управления) или через третий информационный вход регистра 1 данных (на входе управления.регистра 1 данных в это время прис тствует с:; - - ; -; управления -- положительный уровень ло. ческой единицы). При записи ннфор: ;а- ционного с. юва по сигналу чтения в регистр данных инфop auнoннoe во поступает через его первый инфп;) ционный вход. Каждо. двоичко;.гу разряду ипс||ормацио11ного слова соответствует один триггер 31.

o

5

0

Q

52

Каждый триггер 31 представляет собой (фиг. 7) два тактируемых триггера RS-Tui;;, соединенных между собой по М-S схеме.

Через инверсный вход элемента И - НЕ 38 или ЗЭ триггер 31 устанавливается соответственно в нулевое или единичное состояние, блокируя на время длительности этого импульса установки триггера на элемента И- НЕ 42 и 43. По переднему фронту сигнала записи или чтения информация записывается в триггер на элементах И - НЕ 38 и 39, а по заднему фронту этого сигнала записи или этого сигнала чтения переписывается в триггер на элементах И - НЕ 42 и 43. По переднему фронту сигнала за1И1си информация в триггер на элементах И--НЕ 38 и 39 записывается с второго инфор- .машюнного входа этого триггера 31 через эле.менты I-l--Hf- 34 и 35 (отсутствует сигнал управления на входе управления триггера 31 или с третьего информационного входа через элементы И - НЕ 32 и 33 (присутствует сигнал управления на входе управления триггера 31). По переднему фронту сигнал с чтения пнфор- .мации записывается в триггер lia элементах И-НЕ 38 и 39 с первого информационного входа триггера 31 через элементы И -НЕ 36 и 37.

Аналогичные регистры 1 данных использованы и в известном устройстве. При этом в нем не используется вход установки всех разрядов регистра i данных в пуль и при этом этот регистр 1 да1;мых управ.чяется сигнало.м управления противоположной по.-1ярности (и: входе управ, ieiiii i pe.i iiCTpa 1 данных ii3i50CTHoro вк:1Ю.;еп дог ол:|пте,. 1ьный инвертор) .

Предлагаемое буферное запоминаюпк С устройство может быть использовано н вычис- ,1ительных системах по сбору инфop iaunи при приоритетном обс.П жнвапии 6(nbnjoro М сла абонентов с различп11|ми а.чоесами, пp iopитeт каждого из которых опреде. 1легся ко,том адреса и .может быть изменеп с по- предлагс емо Х) устройства. Это устройство .может быть, например, испо.чьзова- 1(0 в вычпс, 1ительн)Х систе.мах по;и ято1и 1 дан.чых на .магпитиой ленте.

устройство люжет распо. шгать адресл : :..)центов в любом заранее .ча;и 1)ом ::ор:-.1кс и позволяет переход ;т1 от о. июг ,) поря;1к;; их

к любому другому ПОрЯ.ТКу. т.о. и IMCHHTrj

приоритет адресов абонентов niui органи.ча- Ц1-:. ; очереди на обслуживание. За счет этого расширяются функциональны возможности предлагаемого буферного зд;|)Мг;иающег() стройства с; а 1ненкю с H:-iiv; ,-Ti;wM.

-;1ПС 3;:Г

13

данных, счетчик импульсов, формирователь сигналов и элемент И, причем выход счетчика импульсов соединен с первым входом элемента И и является индикаторным выходом устройства, второй вход элемента И является входом записи устройства, вход вычитания счетчика импульсов соединен с входами чтения регистров данных группы, кроме последнего регистра данных, и с входом чтения регистра данных и является входом считывания устройства, первые информационные входы регистров данных группы объединены и являются информационным входом устройства, вторые информационные входы каждого регистра данных группы, кроме последнего, соединены с соответствующими выходами последующего регистра данных группы, второй и четвертый информационные входы последнего регистра данных группы подключены к выходу формирования сигналов, информационные выходы каждого регистра данных подключены к третьему информационному входу последующего регистра данных группы, информационный выход первого регистра данных группы соединен с соответствующим входом регистра данных, выход которого явля1236555

14

ется информационным выходом устройства, отличающееся тем, что, с целью расширения области применения устройства за счет возможности записи информации в произвольном порядке, в него введен блок распределителей сигналов записи, управляющий вход которого является управляющим входом устройства, установочные входы блока распределителей сигналов записи, счетчика импульсов и регистра данных объединены и являются установочным входом устройства, вход записи блока распределителей сигналов записи соединен с входом сложения счетчика импульсов и выходом элемента И, вход чтения блока распределителей сигналов записи подключен к соответствующему входу устройства, один информационный вход блока распределителей сигналов записи подключен к информационному входу устройства, другие информационные входы блока распределителей сигналов

записи соединены с соответствующими выходами соответствующих регистров данных группы, выходы блока распределителей сигналов записи соединены с соответствующими входами соответствующих регистров данных группы.

Фиг.

фиг. 2

ШигЗ

.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления | 1984 |

|

SU1171790A1 |

| Устройство для программного управления технологическим оборудованием | 1988 |

|

SU1638707A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ | 1991 |

|

RU2018970C1 |

| Устройство управления | 1986 |

|

SU1339559A2 |

| Устройство для вычисления полиномиальной функции от аналогового аргумента | 1990 |

|

SU1737444A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Запоминающее устройство | 1985 |

|

SU1305772A1 |

| Запоминающее устройство | 1987 |

|

SU1481865A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1983 |

|

SU1140125A1 |

Изобретение относится к вычислительной технике, в частности к регистровым запоминающим устройствам. Целью изобретения является расширение области при.мене- ния устройства за счет возможности записи информации в произвольном порядке. Устройство содержит группу регистров данных, регистр данных, блок распределителей сигналов записи, счетчик импульсов, элемент И и формирователь сигналов. Устройство может быть использовано в вычислительных системах по сбору информации при приоритетном обслуживании большого числа абонентов с различными адресами, приоритет каждого из которых определяется кодом адреса и может быть изменен с помошью данного устройства. Устройство может располагать адреса абонентов в любом заранее заданном порядке и позволяет переходить от одного порядка расположения их к другому порядку, т.е. изменять приоритет адресов абонентов, при организации очереди на обслуживание. 7 ил. со ГчЭ оэ а СП сд О

фиг Л

Составитель В. Фокина

Редактор М. БланарТехред И. ВересКорректор О. Луговая

Заказ 3014/55Тираж 543Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений н открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП «Патент, г. Ужгород, ул. Проектная, 4

| Буферное запоминающее устройство | 1974 |

|

SU487422A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1030855A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-06-07—Публикация

1984-12-17—Подача