Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах повышенной надежности.

Цель изобретения - упрощение устройства.

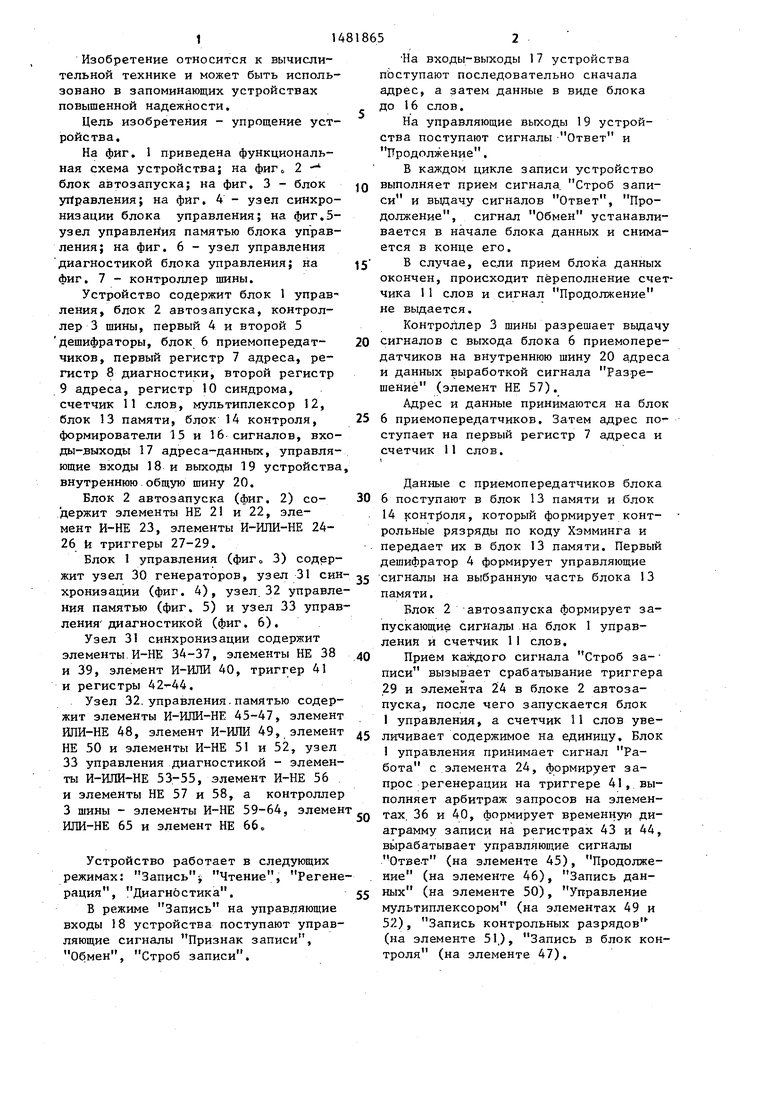

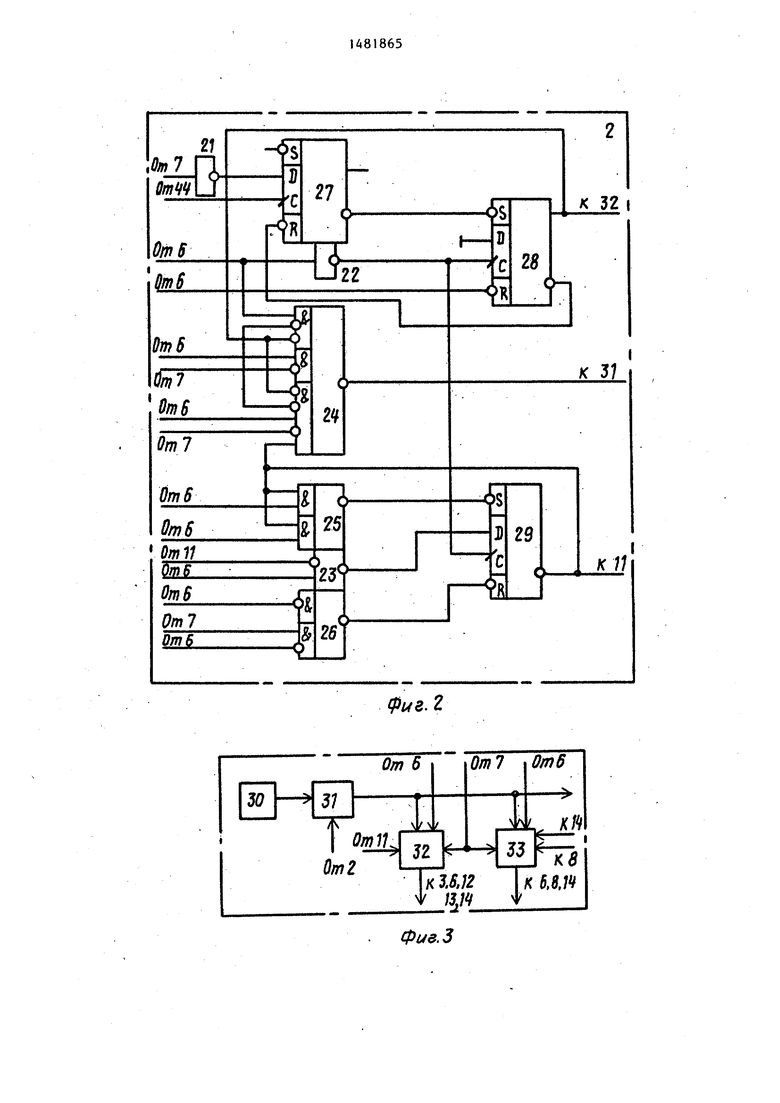

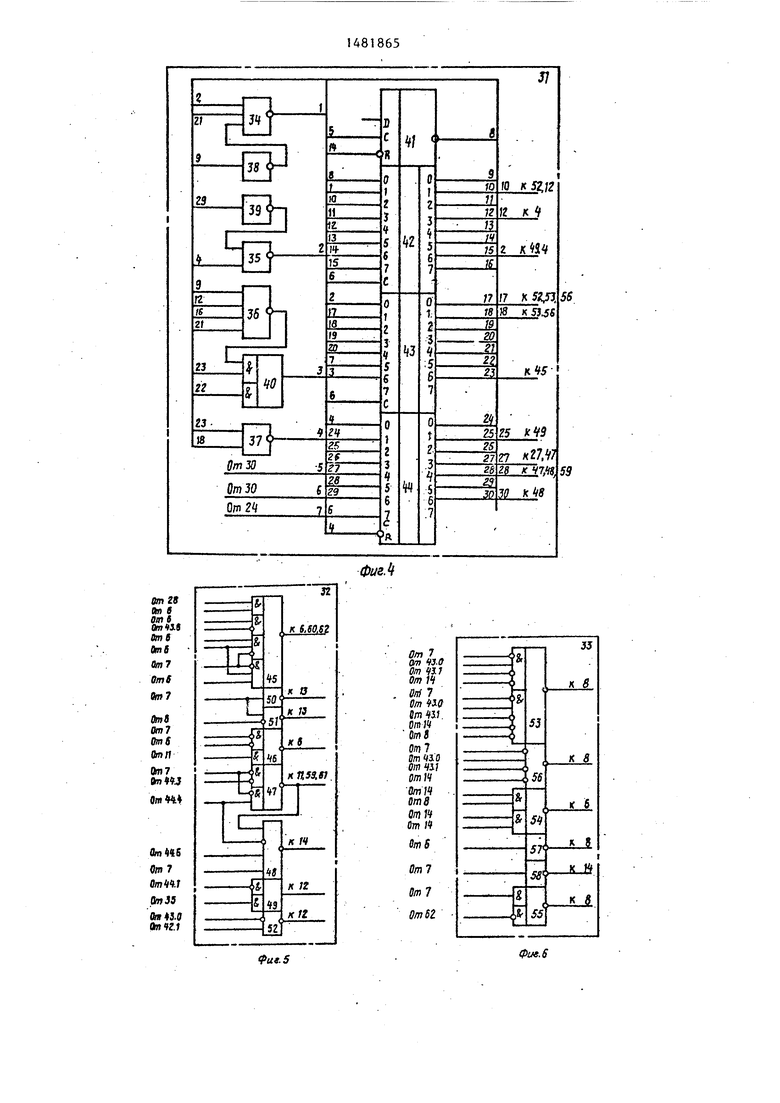

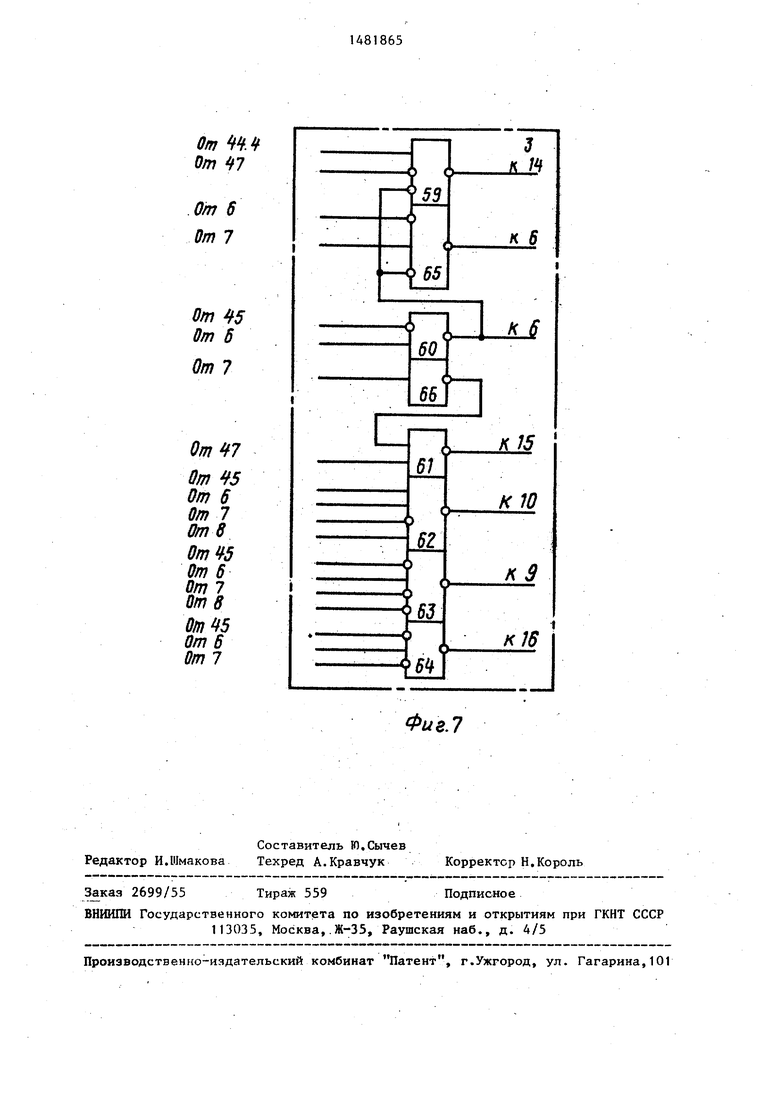

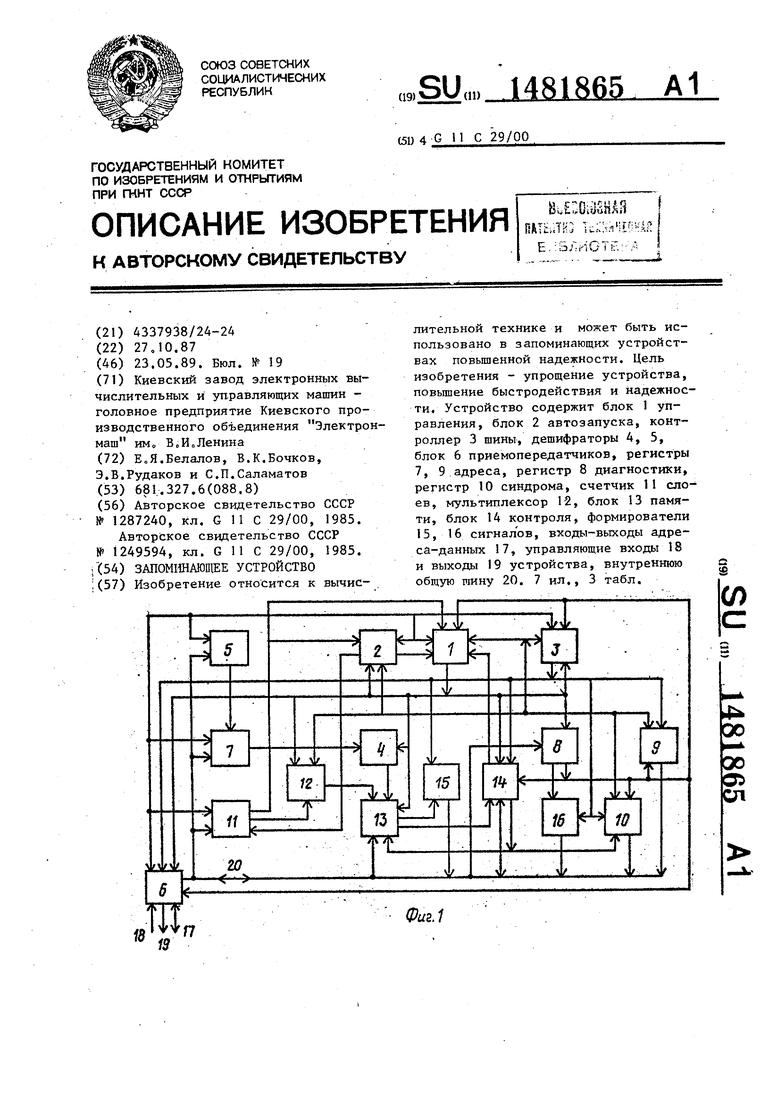

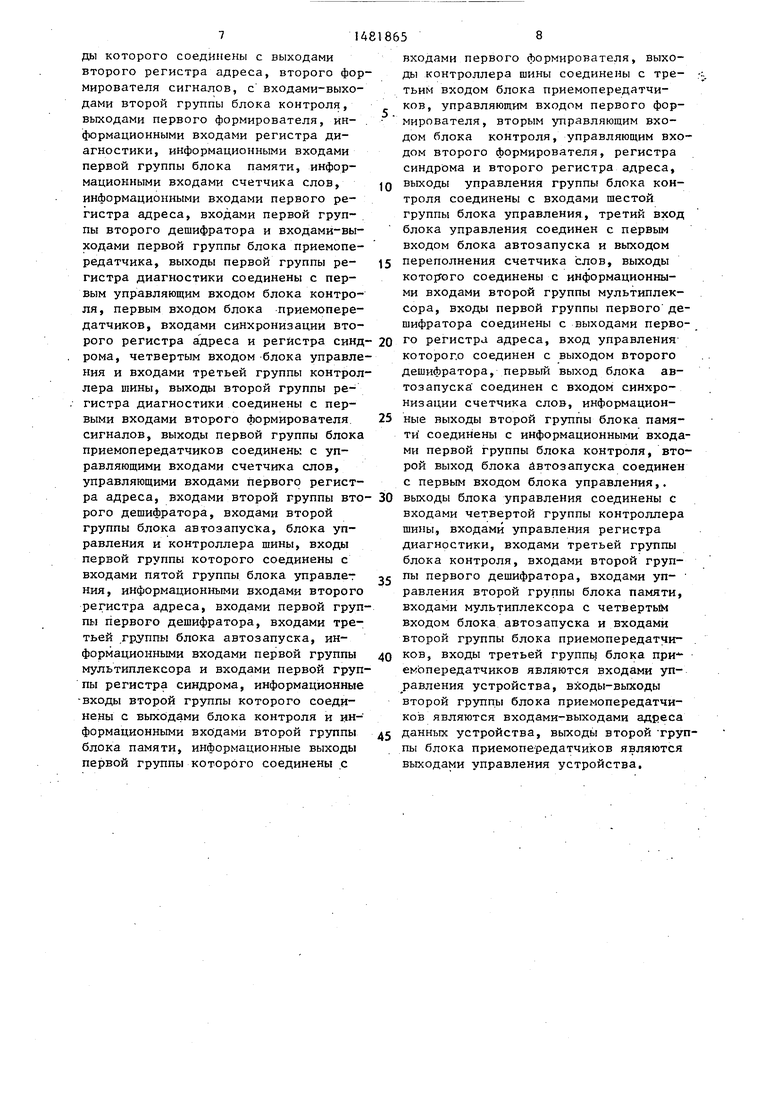

На фиг. 1 приведена функциональная схема устройства; на фиг 2 - блок автозапуска; на фиг. 3 - блок управления; на фиг. 4 - узел синхронизации блока управления; на фиг.5- узел управления памятью блока управления; на фиг. 6 - узел управления диагностикой блока управления; на фиг. 7 - контроллер шины.

Устройство содержит блок 1 управ- ления, блок 2 автозапуска, контроллер 3 шины, первый 4 и второй 5 дешифраторы, блок 6 приемопередатчиков, первый регистр 7 адреса, регистр 8 диагностики, второй регистр 9 адреса, регистр 10 синдрома, счетчик 11 слов, мультиплексор 12, блок 13 памяти, блок 14 контроля, формирователи 15 и 16 сигналов, входы-выходы 17 адреса-данных, управляющие входы 18 и выходы 19 устройства внутреннюю общую шину 20.

Блок 2 автозапуска (фиг. 2) содержит элементы НЕ 21 и 22, элемент И-НЕ 23, элементы И-ИЛИ-НЕ 24- 26 и триггеры 27-29.

Блок 1 управления (фиг„ 3) содержит узел 30 генераторов, узел 31 синхронизации (фиг. 4), узел 32 управления памятью (фиг. 5) и узел 33 управления диагностикой (фиг. 6) .

Узел 31 синхронизации содержит элементы И-НЕ 34-37, элементы НЕ 38 и 39, элемент И-ИЛИ 40, триггер 41 и регистры 42-44.

Узел 32, управления.памятью содержит элементы И-ИЛИ-НЕ 45-47, элемент ИЛИ-НЕ 48, элемент И-ИЛИ 49, элемент НЕ 50 и элементы И-НЕ 51 и 52, узел 33 управления диагностикой - элементы И-ИЛИ-НЕ 53-55, элемент И-НЕ 56 и элементы НЕ 57 и 58, а контроллер 3 шины - элементы И-НЕ 59-64, элемен ИЛИ-НЕ 65 и элемент НЕ 66.

Устройство работает в следующих режимах: Запись -, Чтение, Регенерация, Диагностика.55

В режиме Запись на управляющие входы 18 устройства поступают управляющие сигналы Признак записи, Обмен, Строб записи.

0

5

0

5

0

5

0

5

0

5

На входы-выходы 17 устройства поступают последовательно сначала адрес, а затем данные в виде блока до I6 слов.

На управляющие выходы 19 устройства поступают сигналы Ответ и Продолжение.

В каждом цикле записи устройство выполняет прием сигнала Строб записи и выдачу сигналов Ответ, Продолжение, сигнал Обмен устанавливается в начале блока данных и снимается в конце его.

В случае, если прием блока данных окончен, происходит переполнение счетчика 11 слов и сигнал Продолжение не выдается.

Контроллер 3 шины разрешает выдачу сигналов с выхода блока 6 приемопередатчиков на внутреннюю шину 20 адреса и данных выработкой сигнала Разрешение (элемент НЕ 57).

Адрес и данные принимаются на блок 6 приемопередатчиков. Затем адрес поступает на первый регистр 7 адреса и

счетчик 11 слов.

1

Данные с приемопередатчиков блока 6 поступают в блок 13 памяти и блок 14 контроля, который формирует контрольные рязряды по коду Хэмминга и передает их в блок 13 памяти. Первый дешифратор 4 формирует управляющие сигналы на выбранную часть блока 13 памяти.

Блок 2 автозапуска формирует запускающие сигналы на блок 1 управления и счетчик 11 слов.

Прием каждого сигнала Строб за- писи вызывает срабатывание триггера 29 и элемента 24 в блоке 2 автозапуска, после чего запускается блок 1 управления, а счетчик 11 слов увеличивает содержимое на единицу. Блок 1 управления принимает сигнал Работа с элемента 24, формирует запрос регенерации на триггере 41, выполняет арбитраж запросов на элементах 36 и 40, формирует временную диаграмму записи на регистрах 43 и 44, вырабатывает управляющие сигналы Отве.т (на элементе 45), Продолжение (на элементе 46), Запись данных (на элементе 50), Управление мультиплексором (на элементах 49 и 52), Запись контрольных разрядов 1 (на элементе 51,), Запись в блок контроля (на элементе 47),

3U

В режиме Чтение на вход устройства поступают управляющие сигналы Блок, Обмен Строб чтения.

Двунаправленные приемопередатчики блока 6 сначала принимают адрес, затем переходят в режим передачи и выдают считанные данные на входы-выходы 17 устройства в виде блока данных до 16 слов.

На управляющие выходы 19 устрой

ства поступают сигналы Ответ и Продолжение.

В каждом цикле чтения устройство принимает сигнал Строб чтения и выдает сигналы Ответ, Продолжение а сигналы Обмен и Блок устанавливаются в начале блока данных и снимаются в конце его.

Последнее слово в блоке выдается без сигнала Продолжение, что означает конец блока данных.

Контроллер 3 шины выдает сигналы Разрешение (на элементе 65) и Передача (на элементе 60) в блок 6, сигналы Разрешение выдачи (на элементе 61) на формирователь 15 и Чтение блока контроля (на элементе 59) на блок 14.

Такая последовательность сигналов обеспечивает выдачу адреса с блока 6 на блоки 5, 7 и 11, затем выдачу данных с формирователя 15 на блок 14 контроля и выдачу данных с блока 14 на блок 6, причем все потоки адреса и данных идут через внутреннюю общую шину 20

Считанные данные с блока 13 памяти поступают на формирователь 15, а затем в блок 14 контроля, а контрольные разряды - в блок 14 контроля Последний выявляет двойные ошибки или осуществляет коррекцию одиночных ошибок и выполняет выдачу данных на внутреннюю общую тайну 20 и выдачу сигналов одиночной или двойной ошибки, а также синдрома ошибки .

Блок 2 автозапуска принимает с блока 6 сигналы Обмен, Блок, Строб чтения, со счетчика 11 - сигнал Конец блока.

Блок 2 вырабатывает сигналы Коне цикла (на элементе 28), Автозапуск (на элементе 29), Работа (на элементе 24).

Сигнал Конец цикла означает, чт внутренний цикл окончен, устройство свободно и можно начинать новый цикл. Сигнал Автозапуск означает,

0

0

5

0

5

0

5

что цикл обмена через интерфейс окончен и можно начинать автозапуск нового цикла чтения. Сигнал с выхода элемента 29 блока 2 запускает счетчик 11 слов, а сигнал Работа с выхода элемента 24 запускает блок 1 управления.

Блок 1 управления выполняет арбитраж запросов на элементах 36 и 40, формирует временную диаграмму, вырабатывает управляющие сигналы Ответ, Продолжение, Запись в блок контроля, Управление мультиплексором, 5 Контроль. При наличии-ошибок блок 1 вырабатывает строб одиночной ошибки или строб двойной ошибки и сигнал Ошибка. При этом взводится триггер одиночной или двойной ошибки ре- гистра 8 диагностики.

При двойной ошибке старшие разряды адреса запоминаются на втором регистре 9 адреса,, а при одиночной ошибке синдром и два старших разряда адреса запоминаются на регистре 10 синдрома.

В режиме Регенерация генератор формирует последовательность импульсов, которая устанавливает триггер

41запроса регенерации. На элементах 36 и 40 выполняется выбор режима: Работа или Регенерация. Регистр

42формирует временную диаграмму регенерации.

Адрес регенерации задается счетчиком, встроенным в микросхемы памяти.

В режиме диагностики могут выполняться следующие операции: Запись регистра, Чтение регистра, Отмена коррекции, Отмена записи -контрольных разрядов1-1, Маскирование ошибки.

При операции Запись регистра выполняется обмен внешними сигналами, но при этом передаются не блоки

данных, а отдельные слова.

Сигнал Блок используется в качестве признака обращения к регистрам, а сигнал Продолжение не используется.

Второй дешифратор 5 выполняет дешифрацию адреса регистра. Результат дешифрации, признак записи и признак обращения к регистрам запоминаются в регистре 7.

Блок 1 управления вырабатывает сигнал Запись в регистр.

51

Контроллер 3 шины вырабатывает сигнал Разрешение, а блок 6 обеспечивает прием адреса и данных на внутреннюю общую шину„

Данные заносятся на регистр 84 Формат регистра 8 приведен в табл. 1.

Т а б л и ц а 1

6

Т а

б л и ц а 3

Разряды регистра 10

Назначение

0...5

6,7

Синдром одиночной ошибки

Старшие разряды адреса одиночной ошибки

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между ЭВМ и периферийным устройством | 1987 |

|

SU1605240A1 |

| Устройство сопряжения для контроля блоков памяти | 1987 |

|

SU1481864A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Устройство для обмена информацией с общей шиной | 1984 |

|

SU1322301A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1988 |

|

SU1667075A1 |

| Устройство для обмена информацией между персональной ЭВМ и управляющим вычислительным комплексом | 1991 |

|

SU1838819A3 |

| Устройство для сопряжения процессора с периферийным устройством | 1984 |

|

SU1246102A1 |

| Запоминающее устройство | 1985 |

|

SU1249594A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах повышенной надежности. Цель изобретения - упрощение устройства, повышение быстродействия и надежности. Устройство содержит блок 1 управления, блок 2 автозапуска, контроллер 3 шины, дешифраторы 4, 5, блок 6 приемопередатчиков, регистры 7, 9 адреса, регистр 8 диагностики, регистр 10 синдрома, счетчик 11 слов, мультиплексор 12, блок 13 памяти, блок 14 контроля, формирователи 15,16 сигналов, входы- выходы адреса- данных 17, управляющие входы 18 и выходы 19 устройства, внутреннюю общую шину 20. 7 ил., 3 табл.

Разряды регистра 8

Назначение

Маска ошибки Отмена коррекции ошибок

Отмена записи контрольных разрядов Признак чтения регистра 10

Признак одиночной ошибки

Признак двойной ошибки

При операции Чтение регистра выполняется обмен внешними сигналами но передаются не блоки данных, а слова, сигнал Блок используется в качестве признака обращения к регистрам, а сигнал Продолжение не выдается ,

Дешифратор 5 определяет адрес регистра.

Контроллер 3 шины вырабатывает сигналы Разрешение (на элементе 64), Чтение адреса (на элементе 63) или Чтение синдрома (на элементе 62) в зависимости от второго бита регистра 10.

При этом выполняется прием адреса, выдача содержимого регистра 8 и регистра 9 или 10„

Таким образом, можно произвести чтение регистра диагностики, адреса двойной ошибки, синдрома одиночной ошибки, адреса одиночной ошибки.

Форматы регистров 9 и 10 приведены в табл. 2 и 3.

0...7

Старшие разряды адреса двойной ошибки

Адрес двойной ошибки может использоваться для программного обхода поврежденных ячеек, а синдром и адрес одиночной ошибки - для тестирования, техобслуживания и ремонта.

При операции Отмена коррекции в первый разряд регистра 8 записывается единица. В этом случае при чтении памяти блок 14 контроля обнаруживает одиночные ошибки, но не корректирует их, а блок 1 управления вырабатывает сигнал Ошибка (на элементе 54). Остальные действия

выполняются как при обычном чтении. При операции Отмена записи контрольных разрядов во второй бит регистра 8 записывается единица. Блок 1 управления при этом отменяет выработку сигнала Запись контрольных

разрядов- (на элементе 51). Осталь- ные действия выполняются как при обвге- ной записи.

Таким образом, можно записывать

любые коды с неправильной четностью для тестирования блока контроля.

При операции Маскирование ошибки записывается единица в нулевой бит регистра 8. При наличии сигнала

Маска ошибки система игнорирует сигнал Ошибка.

w

Формула изобретения Запоминающее устройство, содержащее блок памяти, управляющие входы первой группы и адресные входы которого соединены соответственно с выходами первого дешифратора и мультиплексора, блок контроля, первый и

второй формирователи сигналов, регистр диагностики, первый регистр адреса, блок управления, блок приемопередатчиков, отличающее с я тем, что, с целью упрощения устройства, повышения быстродействия и надежности, в него введены счетчик слов, блок автозапуска, контроллер шины, второй дешифратор, второй регистр адреса, регистр синдрома, выходы которого соединены с выходами второго регистра адреса, второго формирователя сигналов, с входами-выходами второй группы блока контроля, выходами первого формирователя, информационными входами регистра диагностики, информационными входами первой группы блока памяти, информационными входами счетчика слов, информационными входами первого регистра адреса, входами первой группы второго дешифратора и входами-выходами первой группы блока приемопередатчика, выходы первой группы регистра диагностики соединены с первым управляющим входом блока контроля, первым входом блока приемопередатчиков, входами синхронизации второго регистра адреса и регистра синдрома, четвертым входом блока управления и входами третьей группы контроллера шины, выходы второй группы регистра диагностики соединены с первыми входами второго формирователя сигналов, выходы первой группы блока приемопередатчиков соединены с управляющими входами счетчика слов, управляющими входами первого регистра адреса, входами второй группы второго дешифратора, входами второй группы блока автозапуска, блока управления и контроллера шины, входы первой группы которого соединены с входами пятой группы блока управления, информационными входами второго регистра адреса, входами первой группы первого дешифратора, входами третьей группы блока автозапуска, информационными входами первой группы мультиплексора и входами первой группы регистра синдрома, информационные входы второй группы которого соединены с выходами блока контроля и информационными входами второй группы блока памяти, информационные выходы первой группы которого соединены с

входами первого формирователя, выходы контроллера шины соединены с третьим входом блока приемопередатчиков, управляющим входом первого формирователя, вторым управляющим входом блока контроля, управляющим входом второго формирователя, регистра синдрома и второго регистра адреса,

выходы управления группы блока контроля соединены с входами шестой группы блока управления, третий вход блока управления соединен с первым входом блока автозапуска и выходом

переполнения счетчика слов, выходы которого соединены с информационными входами второй группы мультиплексора, входы первой группы первого дешифратора соединены с выходами первого регистра адреса, вход управления которого соединен с выходом второго дешифратора, первый выход блока автозапуска соединен с входом синхронизации счетчика слов, информационные выходы второй группы блока памяти соединены с информационными входами первой группы блока контроля, второй выход блока автозапуска соединен с первым входом блока управления,.

выходы блока управления соединены с входами четвертой группы контроллера шины, входами управления регистра диагностики, входами третьей группы блока контроля, входами второй группы первого дешифратора, входами управления второй группы блока памяти, входами мультиплексора с четвертым входом блока автозапуска и входами второй группы блока приемопередатчи-

ков, входы третьей группы блока приемопередатчиков являются входами управления устройства, входы-выходы второй группы блока приемопередатчиков являются входами-выходами адреса

данных устройства, выходы второй группы блока приемопередатчиков являются выходами управления устройства.

Фиг. 2

фие.З

Фив. 5

gЈ«

От «7 От 11

Orri 7 От «ff 8т W От От 8

0/n 7 0/пчаО От 411 ОтН

От 14 От 8 От 14 От II

Qm$ От 7 От 7 Вт 62

фие.6

От tt. 4 От 47

От 6 От 7

От 45 От 6

От 7

От 47

От 45 От 6 От 7 От в

От 15 От 6 От 7 От 8

От 45 От 6 От 7

Фие.7

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1287240A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство | 1985 |

|

SU1249594A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1989-05-23—Публикация

1987-10-27—Подача