Изобретение относится к аналоговой технике и может быть использовано для запоминания выборочных значений аналогового сигнала.

Цель изобретения - повышение быстродействия аналогового устройства.

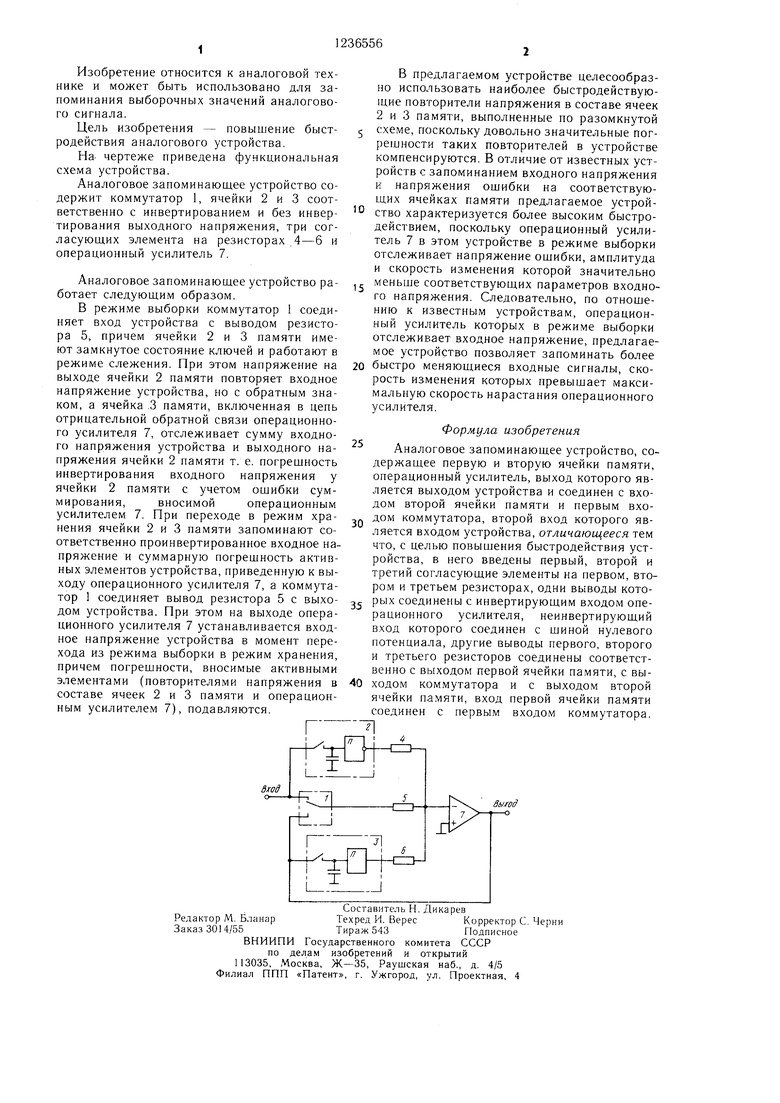

На- чертеже приведена функциональная схема устройства.

Аналоговое запоминающее устройство содержит коммутатор 1, ячейки 2 и 3 соответственно с инвертированием и без инвертирования выходного напряжения, три согласующих элемента на резисторах 4-6 и операционньЕЙ усилитель 7.

Аналоговое запоминающее устройство работает следующим образом.

В режиме выборки коммутатор 1 соединяет вход устройства с выводом резистора 5, причем ячейки 2 и 3 памяти имеют замкнутое состояние ключей и работают в режиме слежения. При этом напряжение на выходе ячейки 2 памяти повторяет входное напряжение устройства, но с обратным знаком, а ячейка .3 памяти, включенная в цепь отрицательной обратной связи операционного усилителя 7, отслеживает сумму входного напряжения устройства и выходного напряжения ячейки 2 памяти т. е. погрещность инвертирования входного напряжения у ячейки 2 памяти с учетом ощибки суммирования, вносимой операционным усилителем 7. При переходе в режим хранения ячейки 2 и 3 памяти запоминают соответственно проинвертированное входное на.- пряжение и суммарную погрешность активных элементов устройства, приведенную к выходу операционного усилителя 7, а коммутатор 1 соединяет вывод резистора 5 с выходом устройства. При этом на выходе операционного усилителя 7 устанавливается входное напряжение устройства в момент перехода из режима выборки в режим хранения, причем погрещности, вносимые активными элементами (повторителями напряжения в составе ячеек 2 и 3 памяти и операционным усилителем 7), подавляются.

В предлагаемом устройстве целесообразно использовать наиболее быстродействующие повторители напряжения в составе ячеек 2 и 3 памяти, выполненные по разомкнутой

схеме, поскольку довольно значительные погрещности таких повторителей в устройстве компенсируются. В отличие от известных устройств с запоминанием входного напряжения и напряжения ошибки на соответствующих ячейках памяти предлагаемое устройство характеризуется более высоким быстродействием, поскольку операционный усилитель 7 в этом устройстве в режиме выборки отслеживает напряжение ощибки, амплитуда и скорость изменения которой значительно

меньще соответствующих параметров входного напряжения. Следовательно, по отношению к известным устройствам, операционный усилитель которых в режиме выборки отслеживает входное напряжение, предлагаемое устройство позволяет запоминать более

быстро меняющиеся входные сигналы, скорость изменения которых превыщает максимальную скорость нарастания операционного усилителя.

Формула изобретения

Аналоговое запоминающее устройство, содержащее первую и вторую ячейки памяти, операционный усилитель, выход которого является выходом устройства и соединен с входом второй ячейки памяти и первым входом коммутатора, второй вход которого является входом устройства, отличающееся тем что, с целью повышения быстродействия устройства, в него введены первый, второй и третий согласующие элементы на первом, втором и третьем резисторах, одни выводы которых соединены с инвертирующим входом операционного усилителя, неинвертирующий вход которого соединен с шиной нулевого потенциала, другие выводы первого, второго и третьего резисторов соединены соответственно с выходом первой ячейки памяти, с выходом коммутатора и с выходом второй ячейки памяти, вход первой ячейки памяти соединен с первым входом ко.ммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1981 |

|

SU1012348A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU966750A1 |

| Ячейка аналоговой памяти | 1978 |

|

SU729643A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU936031A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU957275A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU966749A1 |

| Аналоговое запоминающее устройство | 1982 |

|

SU1104585A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU920843A1 |

| Устройство для определения моментов времени квантования сигналов | 1984 |

|

SU1167731A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU926720A1 |

Изобретение относится к вычислительной и контрольно-измерительной технике Цель изобретения - повышение быстродействия аналогового запоминающего устройства. Устройство содержит коммутатор, первую и вторую ячейки памяти соответственно с инвертированием и без инвертирования выходного напряжения, три резистора и операционный усилитель (ОУ). В режиме выборки первая ячейка памяти повторяет входное напряжение устройства, инвертируя его знак, а вторая ячейка памяти, включенная в цепь отрицательной обратной связи ОУ, запоминает напряжение ошибки, вносимой первой ячейкой памяти и ОУ. В режиме хранения погрешности активных элементов в составе ячеек памяти и ОУ компенсируются. В отличие от известных устройств с запоминанием вход ного напряжения и напряжения ошибки на соответствующих ячейках памяти предлагаемое устройство характеризуется более высоким быстродействием, поскольку в нем ОУ в режиме выборки отслеживает напряжение ошибки, амплитуда и скорость изменения которой значительно меньше соответствующих параметров входного напряжения. 1 ил. сл N5 СА:) 05 ел С71 ot

| Аналоговое запоминающее устройство | 1979 |

|

SU858114A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU881868A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-06-07—Публикация

1981-10-26—Подача