f

Изобретение относится к вычислительной технике и может быть использовано в управляющих, моделирующих и вычислительных машинах и устройствах, работающих в избыточной двоичной системе счисления с цифрами 1, 0,1.

Цель изобретения - повьшение быстродействия в случае задания постоянным одного из операндов.

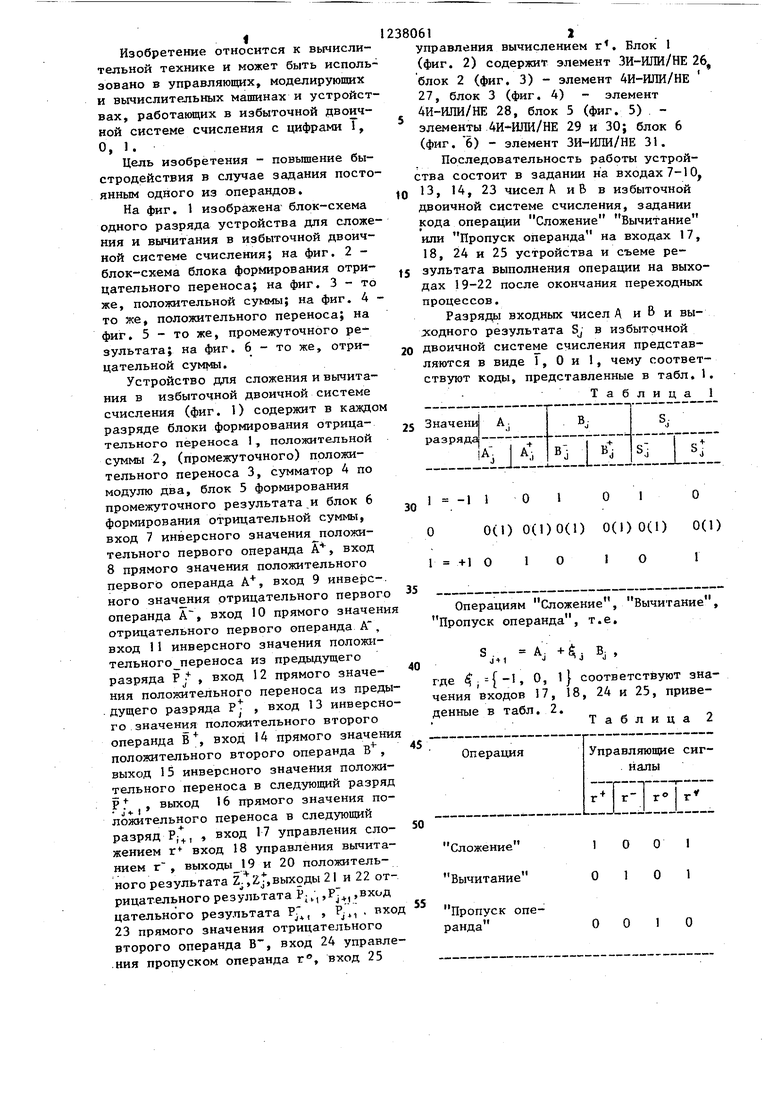

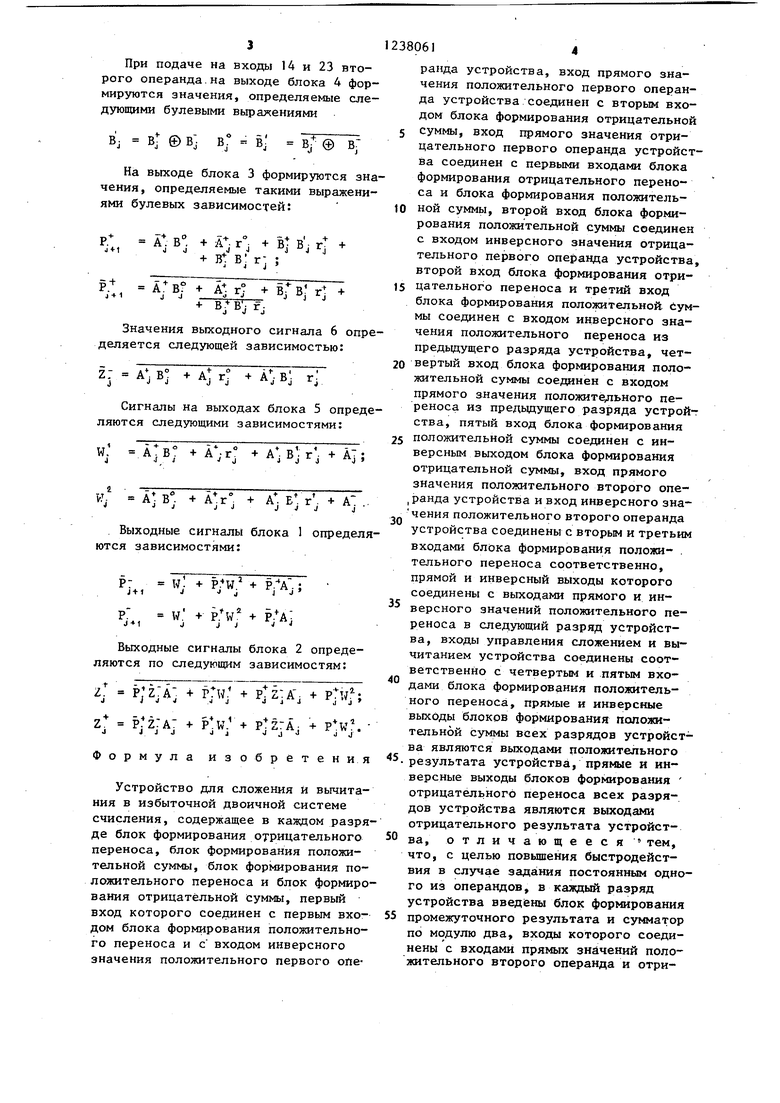

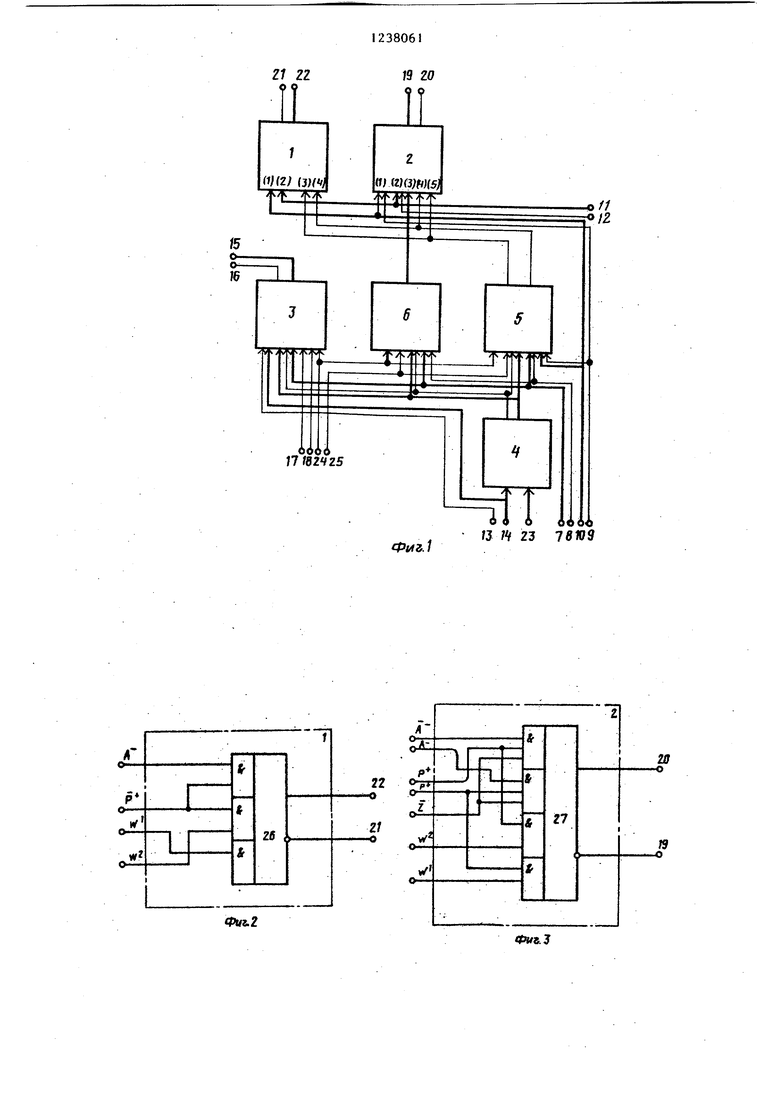

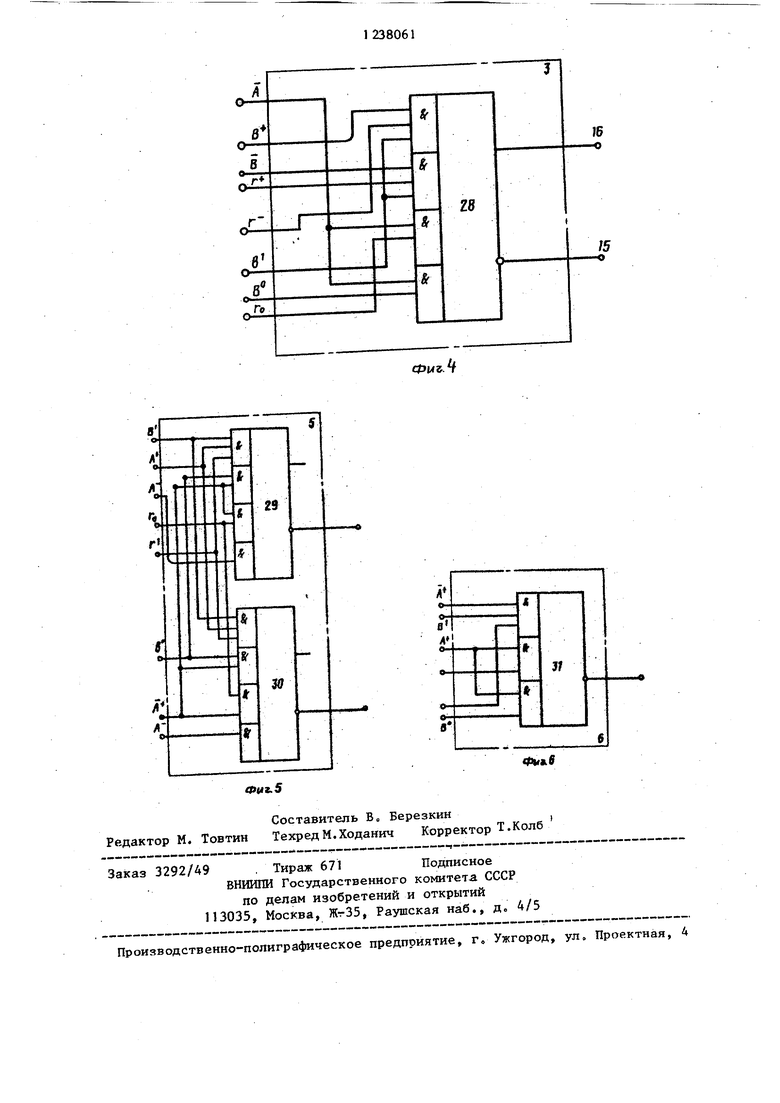

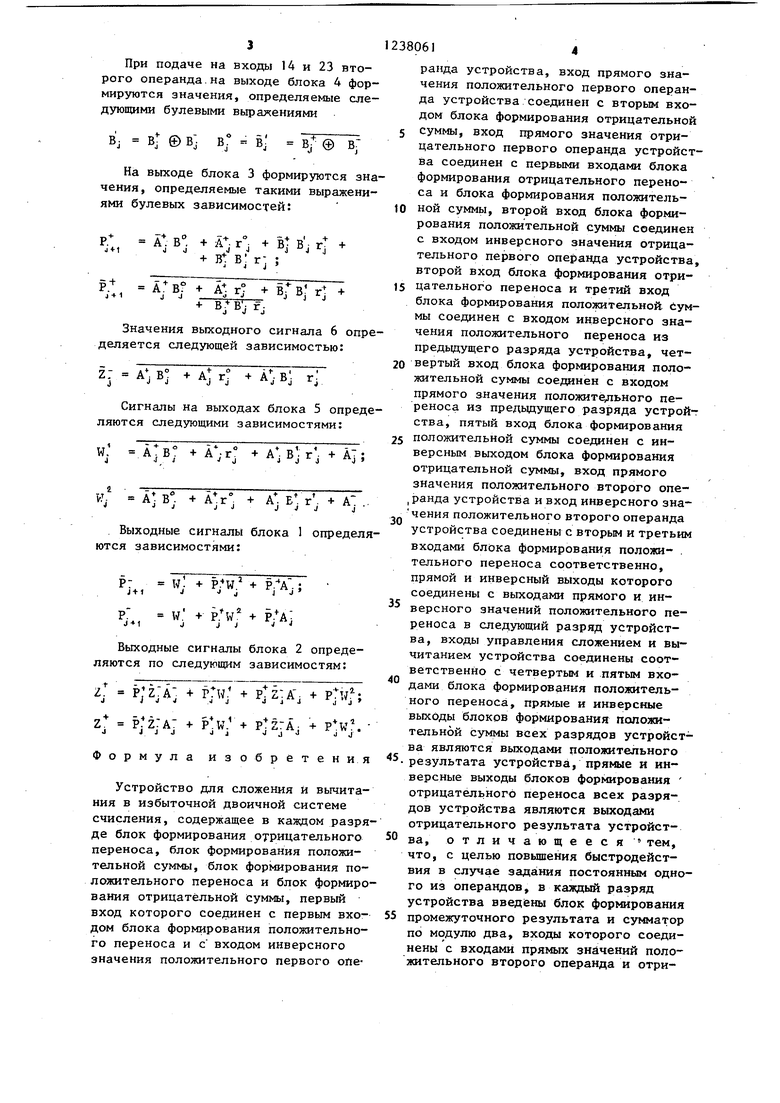

На фиг. 1 изображена блок-схема одного разряда устройства для сложения и вычитания в избыточной двоичной системе счисления; на фиг. 2 - блок-схема блока формирования отрицательного переноса; на фиг. 3 - то же, положительной суммы; на фиг. 4 - то же, положительного переноса; на фиг. 5 - то же, промежуточного результата; на фиг. 6 - то же, отрицательной суммы.

Устройство для сложения и вычитания в избыточной двоичной системе счисления (фиг. 1) содержит в каждом разряде блоки формирования отрицательного переноса 1, положительной суммы 2, (промежуточного) положительного переноса 3, сумматор А по модулю два, блок 5 формирования промежуточного результата,и блок 6 формирования отрицательной суммы, вход 7 инверсного значения положительного первого операнда А, вход 8 прямого значения положительного первого операнда А, вход 9 инверс-. ного значения отрицательного первого операнда А, вход Ю прямого значени отрицательного первого операнда А , вход 11 инверсного значения положительного переноса из предьщущего разряда Р , вход 12 прямого значения положительного переноса из предыдущего разряда Р| , вход 13 инверсного значения положительного второго операнда В , вход 14 прямого значени положительного второго операнда В , выход 15 инверсного значения положительного переноса в следующий разряд

Р Г , выход 16 прямого значения по J - I

ложительного переноса в следующий

разряд Pj, , вход 17 управления сложением г вход 18 управления вычитанием г, выходы 19 и 20 положительного результата Z,2;|,выходы 21 и 22 отрицательного результата ;,+, вход цательного результата Pj, , Р, , вхо 23 прямого значения отрицательного второго операнда В, вход 24 управле .ния пропуском операнда г, вход 25

380612

управления вычислением г. Блок I (фиг. 2) содержит элемент ЗИ-ИЛИ/НЕ 26, блок 2 (фиг. 3) - элемент 4И-ИЛИ/НЕ 27, блок 3 (фиг. 4) - элемент J 4И-ИЛИ/НЕ 28, блок 5 (фиг. 5) - элементы 4И-ИЛИ/НЕ 29 и 30; блок 6 (фиг. 6) - элемент ЗИ-ИЛИ/НЕ 31.

Последовательность работы устройства состоит в задании на входах 7-10. o 3, 14, 23 чисел Л иВ в избыточной двоичной системе счисления, задании кода операции Сложение Вычитание или Пропуск операнда на входах 17, 18, 24 и 25 устройства и съеме ре- 5 зультата выполнения операции на выходах 19-22 после окончания переходных процессов.

Разряда. входных чисел А и В и выходного результата Sj в избыточной 20 двоичной системе счисления представляются в виде 1, О и 1, чему соответствуют коды, представленные в табл. 1.

Таблица 1

30

1 -1 1 О 1О 1о

00(1) 0(1)0(1) 0(1) 0(1) 0(1)

1 +1 о 10 I о1

35

Операциям Сложение, Вычитание, Пропуск операнда, т.е.

-1

где Oj 1} соответствуют значения входов 17, 18, 24 и 25, приведенные в табл. 2.

Таблица2

50

Сложение Вычитание

Пропуск операнда

1001 0101

0010

При подаче на входы 14 и 23 второго операнда.на выходе блока 4 формируются значения, определяемые следующими булевыми выражениями

Bj Bj © В в; в

Bj ® в

VJ

На выходе блока 3 формируются значения, определяемые такими выражениями булевых зависимостей:

Р. А: в, + Г. Г° + в) в ; Г| +

J -1JJ- JJJ

+ в в; г- ;

Д. АГвг . в;в; B/Bjf,

Значения выходного сигнала 6 определяется следующей зависимостью:

z: А, в° + At rt -f AU г :

J j

j j

j S

Сигналы на выходах блока 5 определяются следующими зависимостями:

w; А;В; -ь + А:;В}Г:. + А-;

W, А В. + + А. Б г . -I- А: .. J JJ jjjjj J

. Выходные сигналы блока 1 определяются зависимостями:

Р: w + p.. + р-Х-;

j-HJJ JJ J

РГ w + P.W + P.A- J J

Выходные сигналы блока 2 определяются по следующим зависимостям:

j P;Z;A: - p;w; , -

z + . + + pЧ - J jjj jj ij-i J J

Формула изобретения

Устройство для сложения и вычитания в избыточной двоичной системе счисления, содержащее в каждом разряде блок формирования отрицательного переноса, блок формирования положительной суммы, блок формирования положительного переноса и блок формирования отрицательной суммы, первый вход которого соединен с первым входом блока формирования положительного переноса и с входом инверсного значения положительного первого операнда устройства, вход прямого значения положительного первого операнда устройства соединен с вторым входом блока формирования отрицательной

суммы, вход прямого значения отрицательного первого операнда устройства соединен с первыми входагв блока формирования отрицательного переноса и блока формирования положительной суммы, второй вход блока формирования положительной суммы соединен с входом инверсного значения отрицательного первого операнда устройства, второй вход блока формирования отрицательного переноса и третий вход

блока формирования положительной суммы соединен с входом инверсного значения положительного переноса из предыдущего разряда устройства, чет0 вертый вход блока формирования положительной суммы соединен с входом прямого значения положительного переноса из предьщущего разряда устроит ства, пятый вход блока формирования

5 положительной суммы соединен с инверсным выходом блока формирования отрицательной суммы, вход прямого значения положительного второго опе- , ранда устройства и вход инверсного зна- . чения положительного второго операнда устройства соединены с вторым и третьим входами блока формирования положи- . тельного переноса соответственно, прямой и инверсный выходы которого соединены с выходами прямого и инвареного значений положительного переноса в следующий разряд устройства, входы управления сложением и вычитанием устройства соединены соответственно с четвертым и пятым входами блока формирования положительного переноса, прямые и инверсные выходы блоков формирования положительной суммы всех разрядов устройства являются выходами положительного

- результата устройства, прямые и инверсные выходы блоков формирования отрицательного переноса всех разрядов устройства являются выходами отрицательного результата устройсто ва, отличающееся тем, что, с целью повышения быстродействия в случае задания постоянным одного из операндов, в каждый разряд устройства введ1ены блок формирования

5 промежуточного результата и сумматор по модулю два, входы которого соединены с входами прямых значений положительного второго операнда и отридательного второго операнда, прямой и инверсный выходы сумматора по модулю два соединены соответственно с шестым и седьмым входами блока фор- мирования положительного переноса, с третьим и четвертым входами блока формирования отрицательной суммы, ; с первым и вторым входами блока формирования промежуточного результата, третий и четвертый входы которого соединены соответственно с входами прямого и инверсного значений положительного первого операнда устрой ства, пятый и шестой входы блока фор мирования промежуточного результата соединены соответственно с входами прямого и инверсного значений отрицательного первого операнда устройства, вход управления пропуском one- ранда устройства соединен с восьмым входом блока формирования положительного переноса, пятым входом блока формирования отрицательной суммы и седьмым входом блока формирования . промежуточного результата, вход управления вычислением устройства соединен с шестым входом блока формирования отрицательной суммы и вось№)1м входом блока формирования промежуточ ного результата, первый выхо,а. которого соединен с третьим входом блока формирования отрицательного переноса и шестым входом блока формирования положительной суммы, второй выход блока формирования промежуточного ре аультата соединен с четвертым входом блока формирования отрицательного переноса и седьмым входом блока фор мирования положительной суммы, при этом блок формирования отрицательног переноса содержит элемент ЗИ-ИЛИ/НЕ, прямой и инверсный выходы которого соединены с прямым и инверсным выходами блока, первая группа входов со- единена с первым и вторым входами блока, вторая группа входов с вторым и четвертым входами блока, третья группа входов соединена с третьим входом блока, блок формирования поло жительной сумьы содержит элемент 4И-ИЛИ/НЕ, прямой и инверсный выходы которого соединены с прямым и инверсным выходами блока, первая группа входов соединена с вторым, третьим и

пятым входами блока, вторая группа входов соединена с первым, четвертым и пятым входами блока, третья группа входов соединена с третьим и седьмым входами блока, четвертая группа входов соединена с четвертым и шестым входами блока, блок формирования положительного переноса содержит элемент АИ-ИЛИ/НЕ, прямой и инверсный выходы которого соединены с прямьм и инверсным выходами блока первая группа входов соединена с вторым, пятым и шестым входами блока, вторая группа входов соединена с третьим, четвертым и шестым входами блока, третья группа входов соединена с первым и восьмым входами блока, четвертая группа входов соединена с первым и седьмым входами блока, блок формирования промежуточного результата содержит два элемента АИ-ИЛИ/НЕ, инверсные выходы которых соединены с первым и вторым выходами блока, первая группа входов первого элемента АИ-ИЛИ/НЕ соединена с вторым, третьим и восьмым входами блока, вторая группа входов первого элемента АИ-Ш1:1/НЕ соединена с первым и четвертым входами блока, третья группа входов первого элемента АИ-ИЛИ/НЕ соединена с четвертым и седьмым входами блока, четвертая группа входов первого элемента АИ-ИЛИ/НЕ соединена с шестым входом блока, первая группа входов второго элемента АИ-ШШ/НЕ соединена с вторым, третьим и восьмым входами блока, вторая группа входов второго элемента АИ-ИЛИ/НЕ соединена с первым и четвертым входами блока, третья группа входов второго элемента АИ-ИЛИ/НЕ соединена с седьмым и четвертым входами блока, четвертая группа входов второго элемента АИ-ИЛИ/НЕ соединена с пятым входом блока, блок формирования отрицательной суммы содержит элемент ЗИ-Ш1И/НЕ, инверсный выход которого соединен с инверсным выходом блока, первая группа входов соединена с первым, третьим и шестым входами блока, вторая группа входов соединена с вторым и пятым входами блока, третья группа входов соединена с вторым и четвертым входами блока.

Фиг.2

Составитель В, Березкин Редактор М. Товтин ТехредМ.Ходанич Корректор Т.Колб

Заказ 3292/49 . Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Жг35, Раушская наб,, д 4/5

Производственно-полиграфическое предприятие, г Ужгород, ул. Проектная, 4

Ф1лгМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательное устройство для сложения в избыточной двоичной системе счисления | 1980 |

|

SU968807A1 |

| Устройство для сложения и вычитания в избыточной двоичной системе счисления | 1980 |

|

SU1015371A1 |

| Многовходовой знакоразрядный сумматор | 1982 |

|

SU1027716A1 |

| Преобразователь целых комплексных чисел в двоичный код | 1980 |

|

SU962914A1 |

| Устройство для сложения и вычитания | 1980 |

|

SU922730A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Устройство для алгебраического сложения в избыточной двоичной системе счисления | 1981 |

|

SU1003073A1 |

| Сумматор-вычитатель | 1988 |

|

SU1536373A1 |

| Арифметическое устройство | 1984 |

|

SU1236473A1 |

| Последовательный сумматор в избыточной двоичной системе счисления | 1988 |

|

SU1619251A1 |

Изобретение относится к области вычислительной техники и может быть использовано в управляющих, моделирующих и вычислительных машинах и устройствах, работающих в избыточной двоичной системе счисления с цифрами 1,0, I . Цель изобретения - повьппе- ние быстродействия в случае задания постоянным одного из операндов. Сущ,ность изобретения заключается в том, что в устройство, содержащее в каждом разряде блок формирования отрицательного переноса, блок формирования положительной суммы, блок формирования положительного переноса и блок формирования отрицательной суммы, дополнительно введены блок формирования промежуточного результата и сумматор по модулю два, включенные таким образом, что при операциях Сложение, Вычитание или пропуск операнда блок формирования положительного переноса, блок формирования отрицательного переноса и блок формирования положительной cyMffljj формируют коды сигналов, соответствующих названиям блоков о Наличие операции Пропуск операнда позволяет сделать данное устройство прозрачным для одного из операндов путем умножения на ноль второго. Таким образом, устройство реализует операцию вида Sj AJ + + j В;,., где. {-1, о,. 1}; Aj и Bj - операнды, S,, - результат. Использование предлагаемого устройства целесообразно в быстродействующих арифметических процессорах, специализированных вычислителях, так как ограниченная глубина распространения переноса увеличивает скорость выполнения операций, что позволяет организовать ряд цифровых устройств комбинационного типа, а также безыте- рационных структур для вычисления неявных соотношений. 6 ил., 2 табл. § (Л ю ОО 00 о О5

| Устройство для сложения и вычитания в избыточной двоичной системе счисления | 1980 |

|

SU1015371A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| 1971 |

|

SU453691A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-15—Публикация

1984-07-25—Подача