§

V

| название | год | авторы | номер документа |

|---|---|---|---|

| Многовходовой знакоразрядный сумматор | 1982 |

|

SU1027716A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Устройство для сложения и вычитания в избыточной двоичной системе счисления | 1984 |

|

SU1238061A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU864278A1 |

| Интегроарифметическое устройство | 1990 |

|

SU1784975A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| Накапливающий сумматор | 1984 |

|

SU1174921A1 |

| Преобразователь целых комплексных чисел в двоичный код | 1980 |

|

SU962914A1 |

| Устройство для умножения | 1987 |

|

SU1411733A1 |

| Устройство для сложения в избыточнойдВОичНОй СиСТЕМЕ СчиСлЕНия | 1979 |

|

SU824201A1 |

Изобретение относится к вычислительной технике и может быть использовано в вычислительных устройствах, работающих в избыточной двоичной системе счисления. Целью изобретения является повышение точности. Сумматор содержит блок 3 формирования отрицательной суммы, блок 14 формирования положительной суммы, блок 11 формирования положительного переноса, блок 15 формирования результата, элемент ИЛИ-НЕ 7, элементы 4,8,16 задержки. 2 ил., 2 табл.

Фиг.

Изобретение относится к вычислительной технике и может быть использовано в вычислительных устройствах, работающих в избыточной двоичной системе счисления.

Целью изобретения является повышение точности.

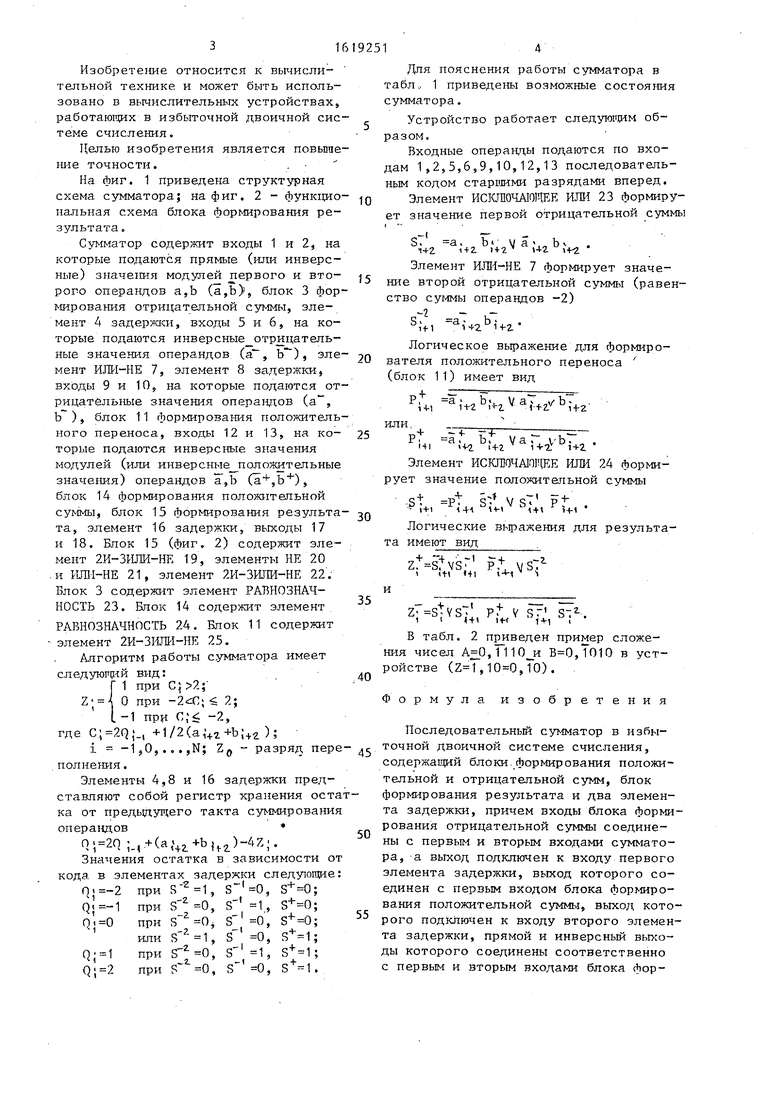

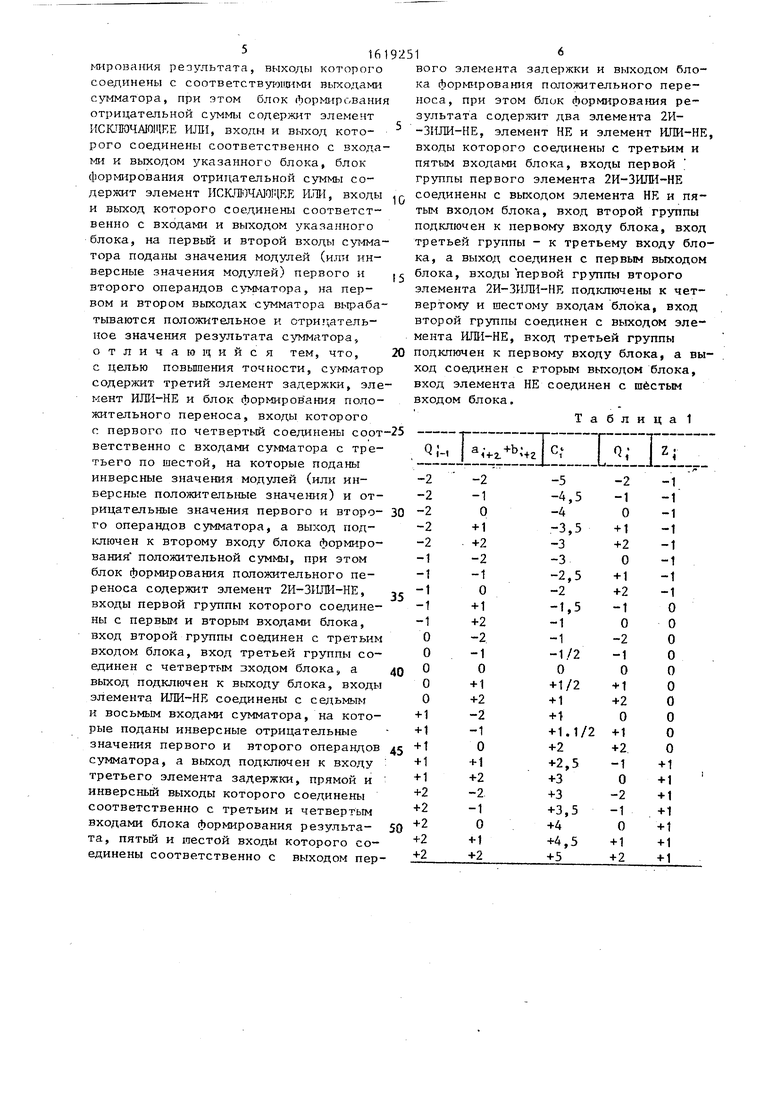

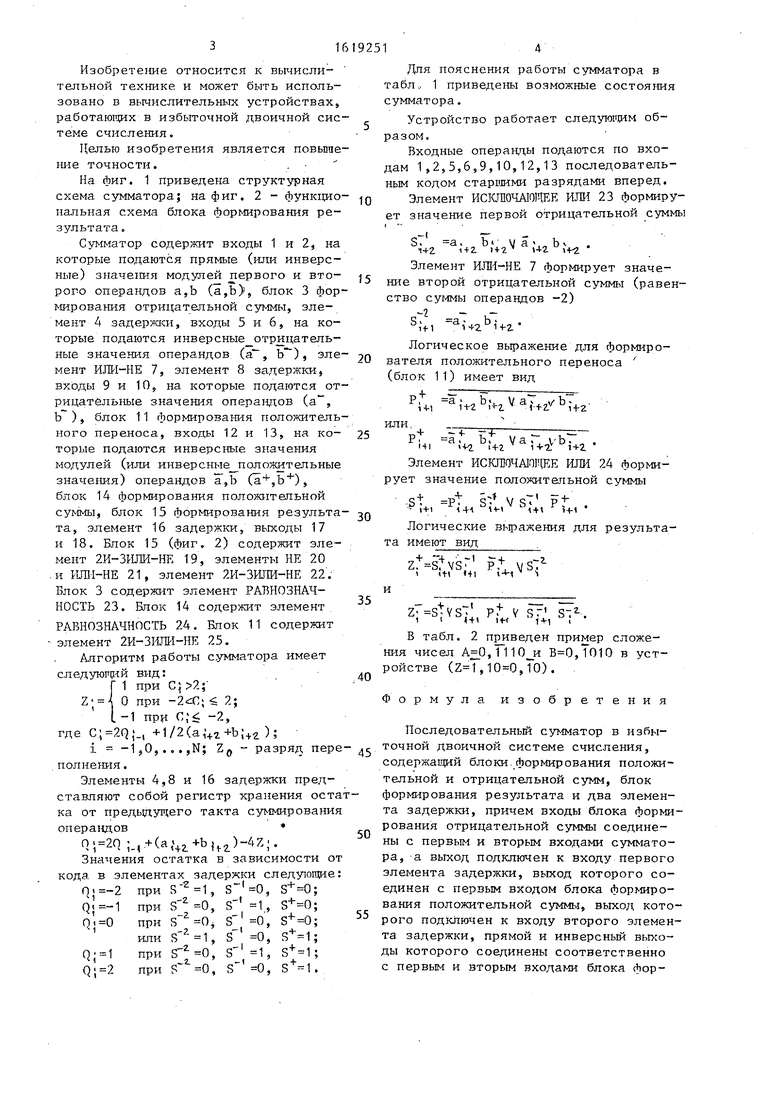

На фиг. 1 приведена структурная схема сумматора; на фиг. 2 - функциональная схема блока формирования результата .

Сумматор содержит входы 1 и 2, на которые подаются прямые (или инверсные) значения модулей первого и второго операндов a,b (a,b)s блок 3 формирования отрицательной суммы, элемент 4 задержки, входы 5 и 6, на которые подаются инверсные отрицатель- ные значения операндов (а, Ь), элемент ИЛИ-НЕ 7, элемент 8 задержки, входы 9 и 10, на которые подаются отрицательные значения операндов (а, tT ), блок 11 формирования положительного переноса, входы 12 и 13, на которые подаются инверсные значения модулей (или инверснне положительные значения) операндов a,b (), блок 14 формирования положительной суммы, блок 15 формирования результата, элемент 16 задержки, выходы 17 и 18. Блок 15 (фиг. 2) содержит элемент 2И-ЗИЛИ-НЕ 19, элементы НЕ 20 и ИЛИ-НЕ 21, элемент 2И-ЗИЛИ-НЕ 22. Блок 3 содержит элемент РАВНОЗНАЧНОСТЬ 23. Блок 14 содержит элемент РАВНОЗНАЧНОСТЬ 24. Блок 11 содержит элемент 2И-ЗИЛИ-НЕ 25.

Алгоритм работы сумматора имеет

следующий вид:

(1 при О при 2; -1 при С, -2, где , +1/2(а1 +г+ъ;+г);

i -1,0,...,N; Z0 - разряд переполнения .

Элементы 4,8 и 16 задержки представляют собой регистр хранения остака от предыдущего такта суммирования операндов

Qr2( ;-«+ а Чг+ьНг)-421- Значения остатка в зависимости от

кода в элементах задержки следующие: q.-2 при , ,

ф -1приS Z 0, 1,

Q.0приS , 0,

илиS - 1,S 0,

Q; 1приS 0,,S+ 1;

Q; 2приS 0,S 0,S 1.

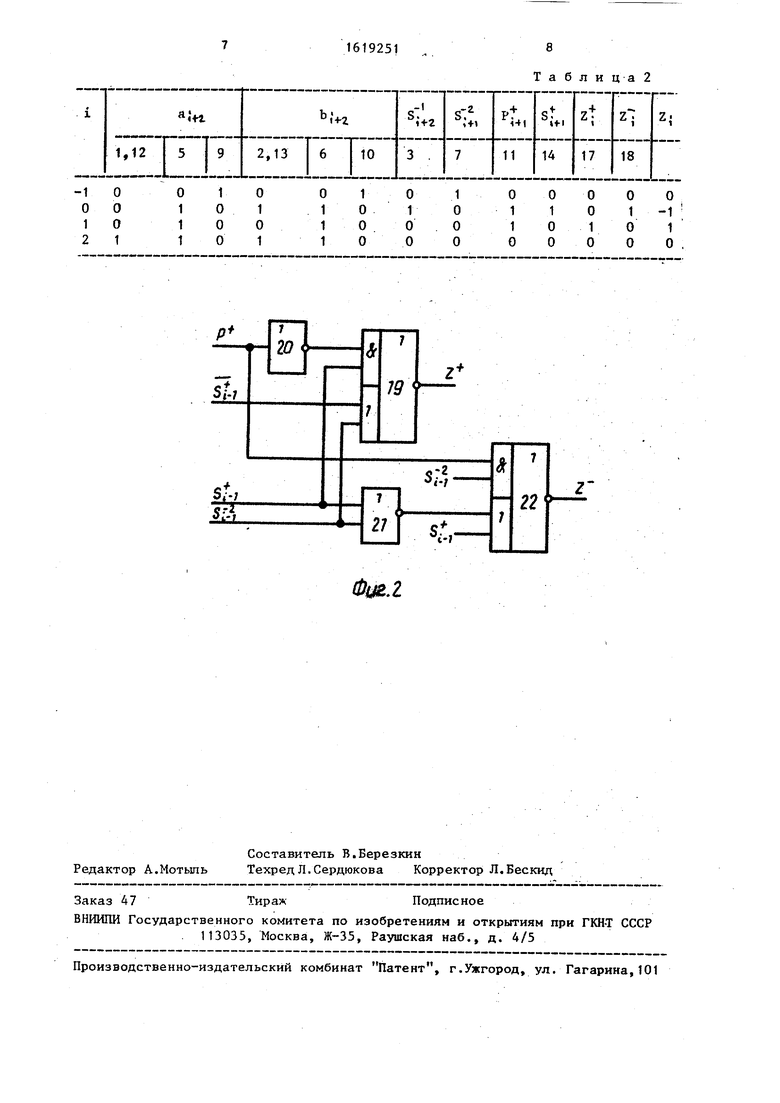

Для пояснения работы сумматора в табл 1 приведены возможные состояния сумматора.

Устройство работает следующим образом.

Входные операнды подаются по входам 1,2,5,6,9,10,12,13 последовательным кодом старшими разрядами вперед.

Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 23 формирует значение первой отрицательной суммы

I

,42V5;42b)W.

Элемент ИЛИ-НЕ 7 формирует значение второй отрицательной суммы (равенство суммы операндов -2)

„-2

И-1

a,42bUz

Логическое выражение для формирователя положительного переноса (блок 11) имеет вид

р,ч, amb nva7«/b7+z

или

р+

HI

a 4ibr«Vai4zvbi4Z

Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 24 формирует значение положительной суммы

st pt V чТ1

;-и .м

Логические выражения для результата имеют вид

P.+, i it( i+i t-H ч

35

, ,

В табл. 2 приведен пример сложения чисел АдО.ТИО и ,1010 в устройстве (,,То).

Формула изобретения

Последовательньй сумматор в избы- точной двоичной системе счисления, содержащий блоки формирования положительной и отрицательной сумм, блок формирования результата и два элемента задержки, причем входы блока формирования отрицательной суммы соединены с первым и вторым входами сумматора, а выход подключен к входу первого элемента задержки, выход которого соединен с первым входом блока формирования положительной суммы, выход которого подключен к входу второго элемента задержки, прямой и инверсный выходы которого соединены соответственно с первым и вторым входами блока фор516192516

мирования результата, выходы которогового элемента задержки и выходом бло- соединены с соответствующими выходамика формирования положительного пересумматора, при -этом блок Нормированияноса, при этом блок формирования ре- отрицательной суммы содержит элементзультата содержит два элемента 2И- ИСКЛЮЧАЮЩЕЕ ИЛИ, входы и выход кото- 5-ЗИЛИ-НЕ, элемент НЕ и элемент ИЛИ-НЕ, рого соединены соответственно с входа-входы которого соединены с третьим и ми к выходом указанного блока, блокпятым входами блока, входы первой формирования отрицательной суммы со-группы первого элемента 2И-ЗИЛИ-НЕ держит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, входы соединены с выходом элемента НЕ и пя- и выход которого соединены соответст-тым входом блока, вход второй группы венно с входами и выходом указанногоподключен к первому входу блока, вход блока, на первый и второй входы сумма-третьей группы - к третьему входу бло- тора поданы значения модулей (или ин-ка, а выход соединен с первым выходом версные значения модулей) первого и | блока, входы первой группы второго второго операндов сумматора, на пер-элемента 2И-ЗИЛИ-НЕ подключены к чет- вом и втором выходах сумматора выраба-вертому и шестому входам блока, вход тываются положительное и отрицатель-второй группы соединен с выходом эле- ное значения результата сумматора,мента ИЛИ-НЕ, вход третьей группы отличающийся тем, что, 20подключен к первому входу блока, а вы- с целью повышения точности, сумматорход соединен с вторым выходом блока, содержит третий элемент задержки, эле-вход элемента НЕ соединен с шестым кент ИЛИ-НЕ и блок формирования поло-входом блока.

жительного переноса, входы которогоТаблица 1

с первого по четвертый соединены соот-25 ветственно с входами сумматора с третьего по шестой, на которые поданы

инверсные значения модулей (или ин--2-2-5-2-1

версные положительные значения) и от--2-1 4,5 -1 -1

рицательные значения первого и второ- 30 20-40-1

го операндов сумматора, а выход под--2+1 3,5 +1 -1

ключей к второму входу блока формиро--2+2-3+2 -1

вания положительной суммы, при этом-1-2-30-1

блок формирования положительного пе--1-1 2,5 +1 -1

реноса содержит элемент 2И-ЗИЛИ-НЕ, ,,-10-2+2-1

входы первой группы которого соедине--1+1 1 5 -1О

ны с первым и вторым входами блока,-1+2-100

вход второй группы соединен с третьим0-2-1-2О

входом блока, вход третьей группы со-0-1-1/2 -1О

единен с четвертым входом блока, а ДО

выход подключен к выходу блока, входы0+1+1/2 +1О

элемента ИЛИ-НЕ соединены с седьмым0+2+1+20

и восьмым входами сумматора, на кото-+1-2-И00

рые поданы инверсные отрицательные -+1 1+1.1/2 +1О

значения первого и второго операндов

сумматора, а выход подключен к входу+1+1+2,5 -1+1

третьего элемента задержки, прямой и+1+2+30+1

инверсный выходы которого соединены+2-2+3-2 +1

соответственно с третьим и четвертым+ 1+3,5 -1 +1

входами блока формирования результа-

та, пятый и шестой входы которого со-+ + +4,5 +1+1

единены соответственно с выходом пер-+ i +5+2 +1

.±l iti±±2ti jiJLiL

Таблица

.±l iti±±2ti jiJLiL

Таблица2

##г.2

| Устройство для сложения в избыточной двоичной системе | 1977 |

|

SU717763A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-01-07—Публикация

1988-06-20—Подача