Изобретение относится к микропроцессорной технике и может быть использовано при построении средств контроля микропроцессоров.

Цель изобретения - повышение опе- .ративности контроля.

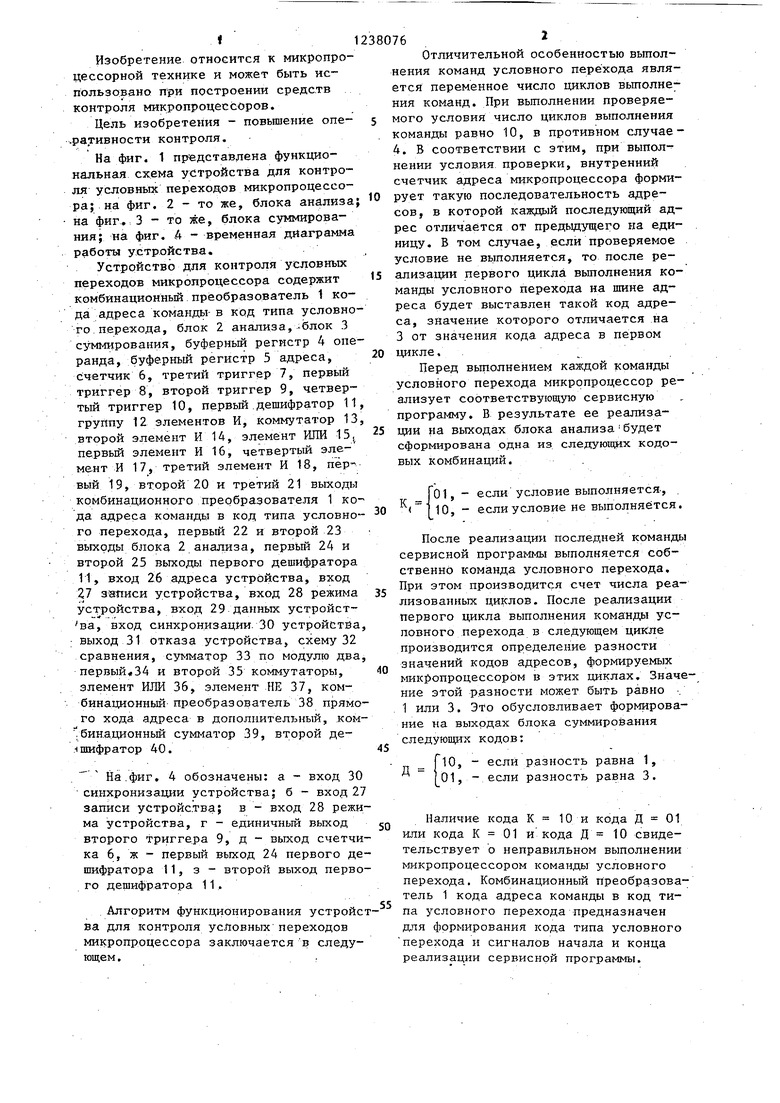

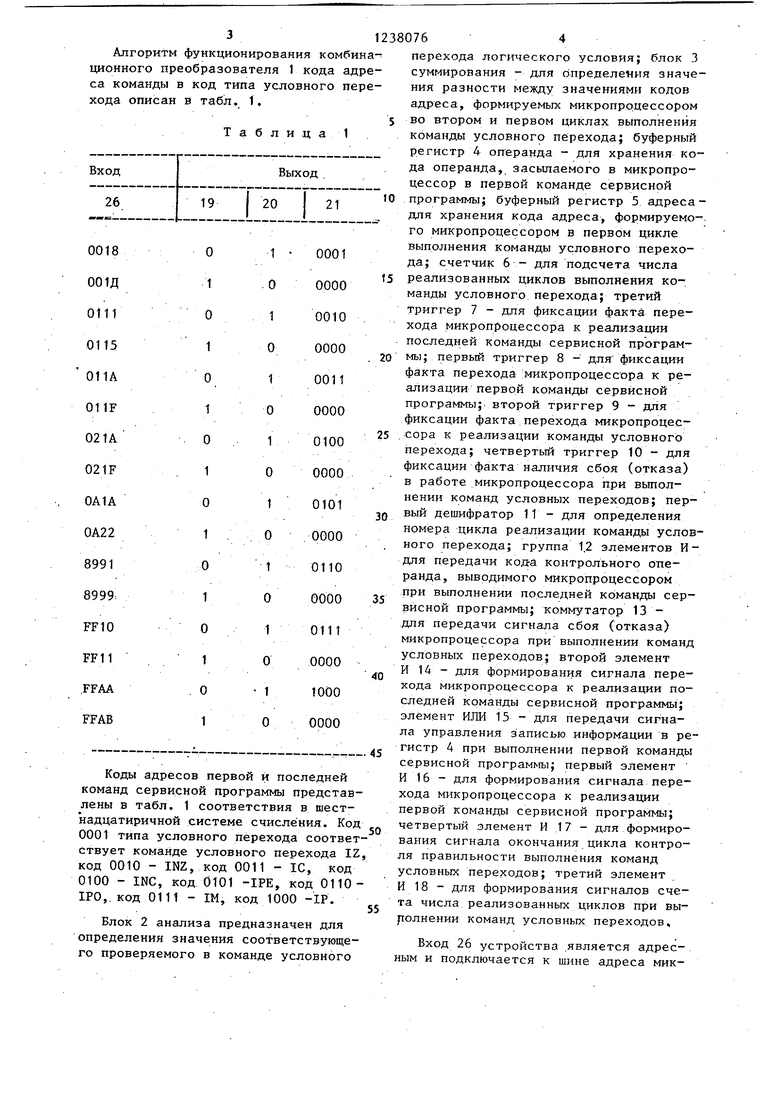

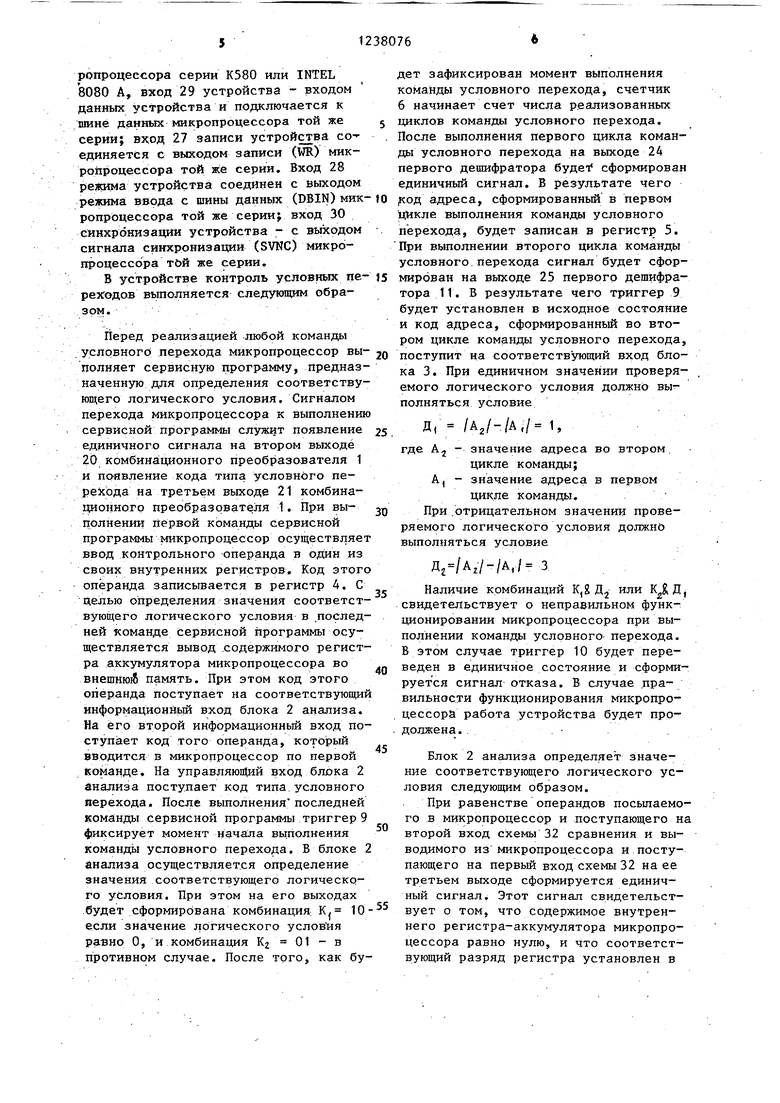

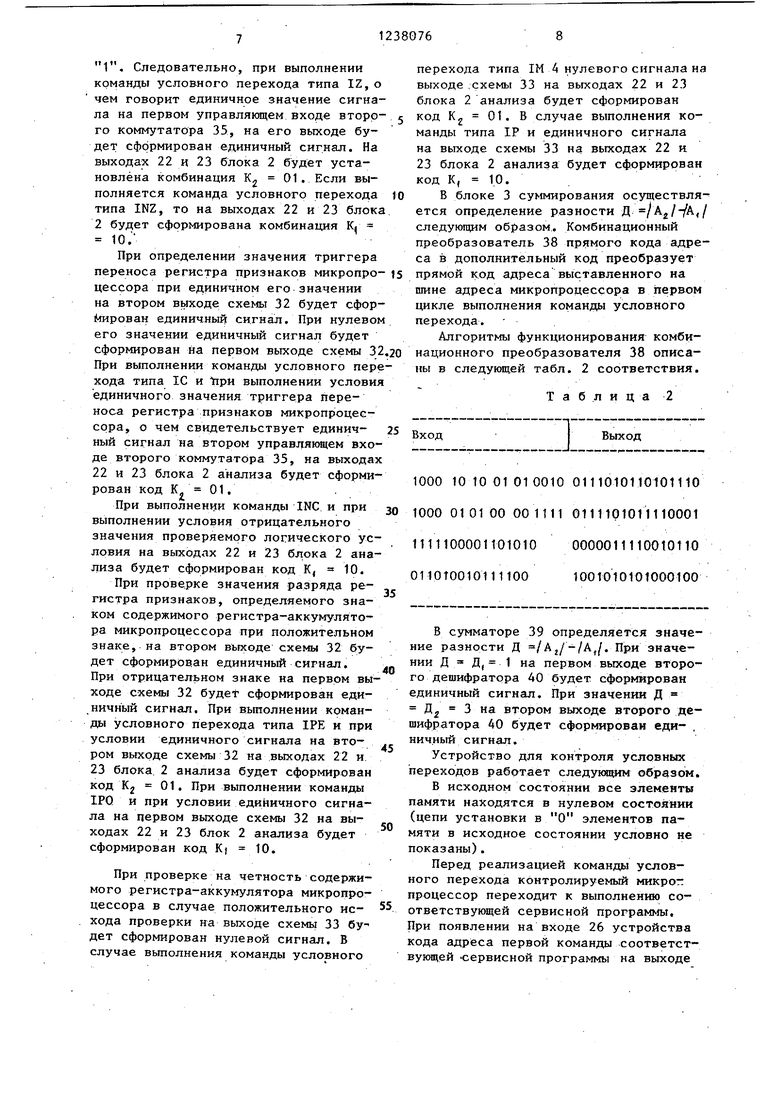

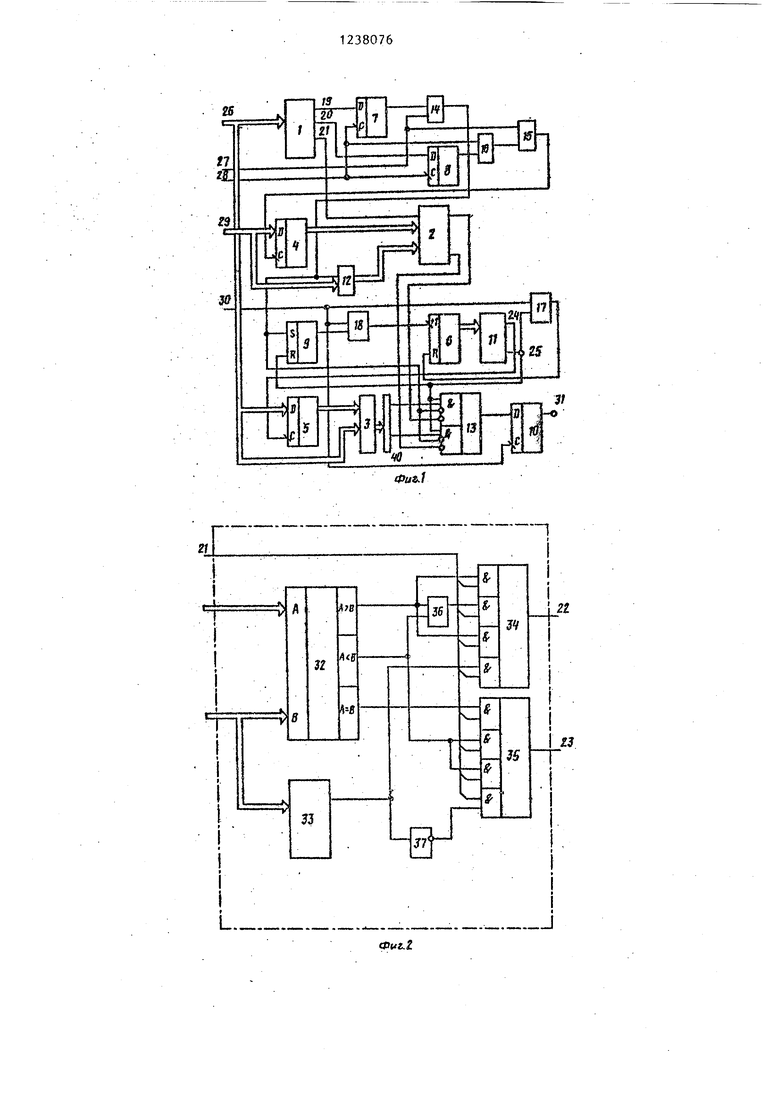

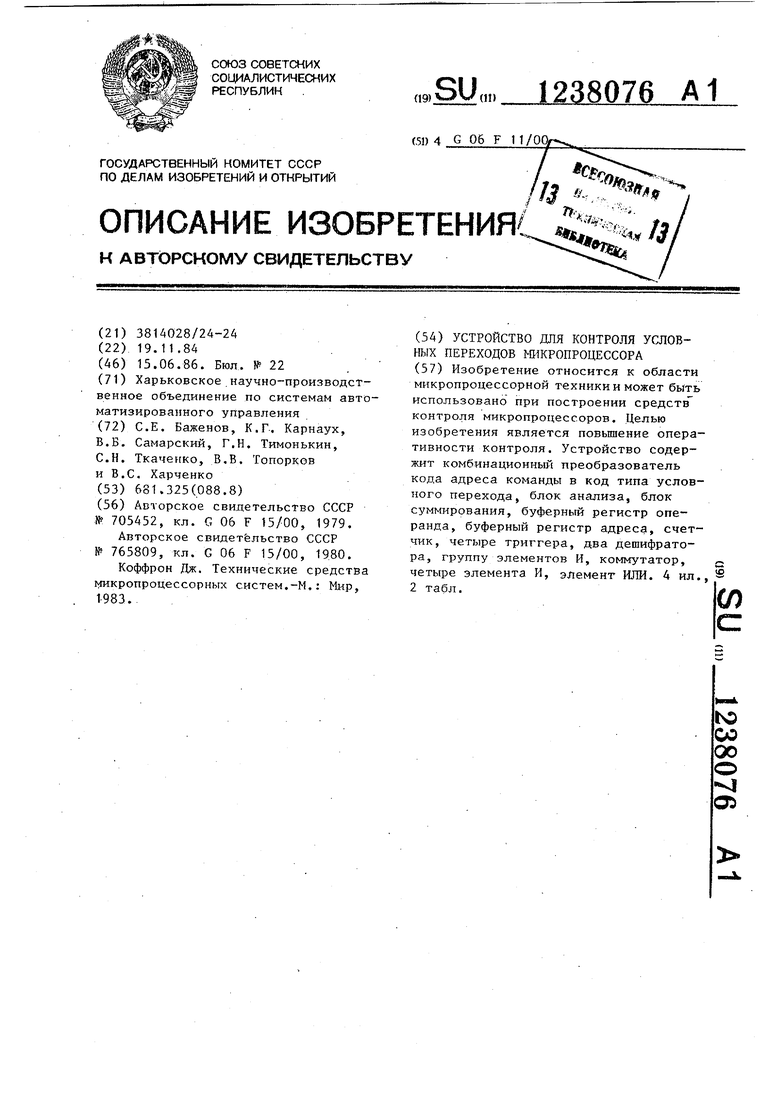

На фиг. 1 представлена функциональная схема устройства для контроля условных переходов микропроцессора; на фиг. 2 - то же, блока анализа; на фиг.,. 3 - то же, блока суммирования; на фиг. А - временная диаграмма работы устройства.

Устройство для контроля условных переходов микропроцессора содержит комбинационньш преобразователь 1 кода адреса команды- в код типа условного перехода, блок 2 анализа,-блок 3 суммирования, буферный регистр 4 операнда, буферный регистр 5 адреса, с:четчик 6, третий триггер 7, первый триггер 8, второй триггер 9, четвертый триггер 10, первый.дешифратор 11, группу 12 элементов И, коммутатор 13, второй элемент И 14, элемент ИЛИ 15 первый элемент И 16, четвертый элемент И 17, третий элемент И 18, первый 19, второй 20 и третий 21 выходы комбинационного преобразователя 1 ко-- да адреса команды в код типа условного перехода, первый 22 и второй 23 выходы блока 2 анализа, первьш 24 и второй 25 вьпсоды первого дешифратора 11, вход 26 адреса устройства, вход 27 згшиси устройства, вход 28 режима устройства, вход 29 данных устройст- ва, вход синхронизации. 30 устройства, : выход 31 отказа устройства, схему 32 сравнения, сумматор 33 по модулю два, первый,34 и второй 35 коммутаторы, элемент ИЛИ 36, элемент НЕ 37, комбинационный преобразователь 38 прямо- го хода адреса в дополнительный, ком- :бинадионный сумматор 39, второй де- 1шифратор 40.

На.фиг. 4 обозначены: а - вход 30 синхронизации устройства; б - вход 27 записи устройству; в - вход 28 режима устройства, г - единичный выход второго триггера 9, д - выход счетчика 6, ж - первый выход 24 первого дешифратора 11, э - второй выход первого дешифратора 11,

10

15

20

25

30

35

40

45

50

Отличительной особенностью выполнения команд условного перехода является переменное число циклов выполнения команд. При выполнении проверяемого условия число циклов выполнения команды равно 10, в противном случае- 4. В соответствии с этим, при выпол- нении условия проверки, внутренний счетчик адреса микропроцессора формирует такую последовательность адресов, в которой каждый последующий адрес отличается от предьщущего на единицу. В том случав, если проверяемое условие не выполняется, то после реализации первого цикла, вьшолнения команды условного перехода на шине адреса будет выставлен такой код адреса, значение которого отличается на 3 от значения кода адреса в первом цикле.

Перед выполнением каждой команды условного перехода микропроцессор реализует соответствующую сервисную программу. В результате ее реализации на выходах блока анализа будет сформирована одна из следую1цих кодовых комбинаций.

{01, - если условие выполняется., . 10, - если условие не выполняется.

После реализации последней команды сервисной программы выполняется собственно команда условного перехода. При этом производится счет числа реализованных циклов. После реализации Первого цикла выполнения команды условного перехода в следующем цикле производится определение разности значений кодов адресов, формируемых микропроцессором в этих циклах. Значение этой р.азности может быть равно .. 1 или 3. Это обусловливает формирование на выходах блока суммирования следующих кодов:

По, - если разность равна 1, (01, - если разность равна 3.

Наличие кода К 10 и кода Д 01 или кода К 01 и кода Д 10 свидетельствует о неправильном выполнении микропроцессором команды условного перехода. Комбинационный преобразователь 1 кода адреса команды в код ти- Алгоритм функционирования устройст- па условного перехода предназначен

для формирования кода типа условного перехода и сигналов начала и конца реализации сервисной программы.

ва для контроля условных переходов микропроцессора заключается в следующем .

5

0

5

0

5

0

5

Отличительной особенностью выполнения команд условного перехода является переменное число циклов выполнения команд. При выполнении проверяемого условия число циклов выполнения команды равно 10, в противном случае- 4. В соответствии с этим, при выпол- нении условия проверки, внутренний счетчик адреса микропроцессора формирует такую последовательность адресов, в которой каждый последующий адрес отличается от предьщущего на единицу. В том случав, если проверяемое условие не выполняется, то после реализации первого цикла, вьшолнения команды условного перехода на шине адреса будет выставлен такой код адреса, значение которого отличается на 3 от значения кода адреса в первом цикле.

Перед выполнением каждой команды условного перехода микропроцессор реализует соответствующую сервисную программу. В результате ее реализации на выходах блока анализа будет сформирована одна из следую1цих кодовых комбинаций.

{01, - если условие выполняется., . 10, - если условие не выполняется.

После реализации последней команды сервисной программы выполняется собственно команда условного перехода. При этом производится счет числа реализованных циклов. После реализации Первого цикла выполнения команды условного перехода в следующем цикле производится определение разности значений кодов адресов, формируемых микропроцессором в этих циклах. Значение этой р.азности может быть равно .. 1 или 3. Это обусловливает формирование на выходах блока суммирования следующих кодов:

По, - если разность равна 1, (01, - если разность равна 3.

Наличие кода К 10 и кода Д 01 или кода К 01 и кода Д 10 свидетельствует о неправильном выполнении микропроцессором команды условного перехода. Комбинационный преобразоваАлгоритм функционирования комбина- ционного преобразователя 1 кода адреса команды в код типа условного перехода описан в табл. 1.

Т а б л и ц а 1

Коды адресов первой и последней команд сервисной программы представлены в табл. 1 соответствия в шестнадцатиричной системе счисления. Код 0001 типа условного перехода соответствует команде условного перехода IZ, код 0010 - INZ, код 0011 - 1C, код 0100 - INC, код 0101 -IPE, код 0110- IPO,. код 0111 - га, код 1000 -IP.

Блок 2 анализа предназначен для определения значения соответствующего проверяемого в команде условного

10

t5

0

5

0

5

0

5

перехода логического условия; блок 3 суммирования - для определения значения разности между значениями кодов адреса, формируемых микропроцессором во втором и первом циклах выполнения команды условного перехода; буферный регистр 4 операнда - для хранения кода операнда, засылаемого в микропроцессор в первой команде сервисной программы; буферный регистр 5 адреса- для хранения кода адреса, формируемо- го микропроцессором в первом цикле выполнения команды условного перехода; счетчик 6 - для подсчета числа реализованных циклов выполнения команды условного перехода; третий триггер 7 - для фиксации факта перехода микропроцессора к реализации последней команды сервисной программы; первый триггер 8 - для фиксации факта перехода :микропроцесс ора к реализации первой команды сервисной программы;- второй триггер 9 - для фиксации факта перехода микропроцессора к реализации команды условного перехода; четвертый триггер 10 - для фиксации факта наличия сбоя (отказа) в работе микропроцессора при вьтол- нении команд условных переходов; первый дешифратор 11 - для определения номера цикла реализации команды условного перехода; группа 1.2 злементов И- для передачи код-а контрольного операнда, выводимого микропроцессором при выполнении последней команды сервисной программы; коммутатор 13 - для передачи сигнала сбоя (отказа) микропроцессора при выполнении команд условных переходов; второй элемент И 14 - для формирования сигнала перехода микропроцессора к реализации последней команды сервисной программы; элемент ИЛИ 15 - для передачи сигнала управления записью информации в регистр 4 при выполнении первой команды сервисной программы; первый элемент И 16 - для формирования сигнала перехода микропроцессора к реализации первой команды сервисной программы; четвертый элемент И 17 - для формирования сигнала окончания цикла контроля правильности выполнения команд условных переходов; третий элемент И 18 - для формирования сигналов счета числа реализованных циклов при вы- ролнении команд условных переходов.

Вход 26 устройства .является адресным и подключается к шине адреса микопроцеесора серии К580 или INTEL 080 А, вход 29 устройства - входом анных устройства и подключается к ине данных микропроцессора той же 5 ерии; вход 27 записи устройс1;ва со- диняется с выходом записи (WR) микопроцессора той же серии. Вход 28 еясима устройства соединен с выходом ежима ввода с шины данньпс (DBIN) мик- to ропроцеесора той же серии; вход 30 синхронизации устройства - с выходом сигнала синхронизации (SVNC) микропроцессора т&й же серии,

В устройстве контроль условных пе- 15 резсодов выполняется следующим образом.

Перед реализацией любой команды условного перехода микропроцессор вы- 2о цолняет сервисную программу, предназначенную для определения соответствующего логического условия. Сигналом перехода микропроцессора к выполнению сервисной программы служит появление 25 единичного сигнала на втором выходе 20 комбина;ционного преобразователя 1 и появление кода типа условного пе- на третьем выходе 21 комбинационного преобразователя 1, При вы- о полнении первой команды сервисной программы микропроцессор осуществляет ввод контрольного операнда в один из своих внутренних регистров. Код этого операнда записывается в регистр 4, С целью определения значения соответствующего логического условия в последней команде сервисной программы осуществляется вывод .содержимого регистра аккумулятора микропроцессора во внешнюй память. При этом код этого операнда поступает на соответствующий информационйьй вход блока 2 анализа, На его второй информационньга вход поступает код того операнда, который вводится в микропроцессор по первой команде. На управляющий вход блока 2 анализа поступает код типа.условного перехода. После выполнения последней кома;нды сервисной программы триггер 9 фиксирует момент начала выполнения командь условного перехода. В блоке 2 анализа осуществляется определение значения соответствующего логического условия. При этом на его выходах .будет сформирована комбинация. К. 10- если значение логического услов ия равно О, и комбинация К 01 - в противном случае. После того, как бу35

40

дет зафиксирован момент выполнения команды условного перехода, счетчик 6 начинает счет числа реализованных циклов команды условного перехода. После выполнения первого цикла команды условного перехода на выходе 24 первого дешифратора бyдef сформирован единичный сигнал, В результате чего ;сод адреса, сформированный в первом цикле выполнения команды условного перехода, будет записан в регистр 5, При выполнении второго цикла команды условного.перехода сигнал будет сформирован на выходе 25 первого дешифратора 11, В результате чего триггер 9 будет установлен в исходное состояние и код адреса, сформированный во втором цикле команды условного перехода, поступит на соответствующий вход блока 3, При единичном значении проверяемого логического условия должно вы полняться условие

Д, /А2/-/А,/ 1,

где Aj - значение адреса во втором.

цикле команды; А, - значение адреса в первом

цикле команды.

При .отрицательном значении проверяемого логического условия должно выполняться условие

,7-/А,/ 3

Наличие комбинаций К,Х Д или К&Д, свидетельствует о неправильном функционировании микропроцессора при выполнении команды условного перехода, В этом случае триггер 10 будет переведен в единичное состояние и сформируется сигнал отказа. В случае .правильности функционирования микропроцессора работа устройства будет продолжена, .

Блок 2 анализа определяет значение соответствующего логического условия следующим образом.

При равенстве операндов посылаемого в микропроцессор и поступающего на второй вход схемы 32 сравнения и выводимого из микропроцессора и поступающего на первый вход схемы 32 на ее третьем выходе сформируется единичный сигнал. Этот сигнал свидетельствует о том, что содержимое внутреннего регистра-аккумулятора микропроцессора равно нулю, и что соответствующий разряд регистра установлен в

1. Следовательно, при выполнении команды условного перехода типа IZ,о чем говорит единичное значение сигнала на первом управляющем входе вторр- го коммутатора 35, на его выходе будет сформирован единичный сигнал. На выходах 22 и 23 блока 2 будет установлена комбинация У. 01. Если выполняется команда условного перехода типа INZ, то на выходах 22 и 23 блока 2 будет сформирована комбинация К( 10/

При определении значения триггера переноса регистра признаков микропро- цессора при единичном его значении на втором выходе схемы 32 будет сфор- йирован единичный сигнал. При нулевом его значении единичный сигнал будет сформирован на первом выходе схемы 32 При выполнении команды условного перехода типа 1C и При выполнении условия единичного значения триггера переноса регистра признаков микропроцессора, о чем свидетельствует единич- ный сигнал на втором управляющем входе второго коммутатора 35, на выходах

22и 23 блока 2 анализа будет сформирован код К- 01..

При выполнении команды INC и при выполнении условия отрицательного значения проверяемого логического условия на выходах 22 и 23 блока 2 анализа будет сформирован код К, 10.

При проверке значения разряда регистра признаков, определяемого знаком содержимого регистра-аккумулятора микропроцессора при положительном знаке, на втором выходе схемы 32 будет сформирован единичный сигнал. При отрицательном знаке на первом выходе схемы 32 будет сформирован еди- ничный сигнал. При выполнении коман- да.1 условного перехода типа 1РЕ и при условии единичного сигнала на втором выходе схемы 32 на выходах 22 и

23блока 2 анализа будет сформирован код К 01. При выполнении команды IPQ и при условии единичного сигнала на первом выходе схемы 32 на выходах 22 и 23 блок 2 анализа будет сформирован код К) 10.

При проверке на четность содержимого регистра-аккумулятора микропроцессора в случае положительного ис- хода проверки на выходе схемы 33 будет сформирован нулевой сигнал. В случае вьтолнения команды условного

перехода типа IM 4 нулевого сигнала на выходе.схемы 33 на выходах 22 и 23 блока 2 анализа будет сформирован код К 01. В случае выполнения команды типа IP и единичного сигнала на выходе схемы 33 на выходах 22 и 23 блока 2 анализа будет сформирован код К, 10.

В блоке 3 суммирования осуществляется определение разности Д /A2/YA,/ следующим образом.. Комбинационный преобразователь 38 прямого кода адреса в дополнительный код преобразует прямой код адреса выставленного на шине адреса микропроцессора в первом цикле выполнения команды условного перехода.

Алгоритмы функционирования комбинационного преобразователя 38 описаны в следующей табл. 2 соответствия.

Т а

блица 2

Вход

I

Выход

1000 10 10 01 01 00100111010110101110

1000 01 01 00 00 11110111101011110001

11111000011010100000011110010110

0110Т00101111001001010101000100

в сумматоре 39 определяется значение разности Д /Aj/-/А,(f. При значении Д Д, 1 на первом вьтходе второго дешифратора 40 будет сформирован единичный сигнал. При значении Д Д 3 на втором выходе второго дешифратора 40 будет сформирован еди- , ничный сигнал.

Устройство для контроля условных переходов работает следукхцим обрезом.

В исходном состоянии все элементы памяти находятся в нулевом состоянии (цепи установки в О элементов памяти в исходное состоянии условно не показаны).

Перед реализацией команды условного перехода контролируемый микрог процессор переходит к выполнению соответствующей сервисной программы. При появлении на входе 26 устройства кода адреса первой команды соответствующей Сервисной программы на выходе

20 преобразователя 1 будет установен единичный сигнал, свидетельствуюий о выполнении первой команды сервисной программы, а на его выходе 21 будет установлен код типа команды усовного перехода. При появлении единичного сигнала DBIN, который выс- тавляется микропроцессором на входе 28 устройства, в первом цикле выполнения первой команды сервисной программы триггер 8 .будет установлен в единичное состояние. Во втором цикле выполнения команды, когда в микропроцессор вводится контрольный операнд, по появлению такого же сигнала DBIN на входе 28 устройства на выходе элемента И 16 будет установлен единичный сигнал, который поступит через элемент ИЛИ 15 на вход,синхронизации регистра А, По заднему фронту этого сигнала код контрольного операнда, посыпаемого в микропроцессор, будет записан в регистр А, При выполнении последней команды сервисной программы после выставления на шине адреса кода адреса последней команды и пос- .туплении этого кода на вход 26 уст- ройства на выходе 19 преобразователя 1 будет установлен единичный Сигнал. Пр и кътолиенин первого цикла этой команды при поступленрп .единичного сиг- нала DBIN на вход 28 устройства триггер 7 будет установлен в единичное состояние. Во втором цикле вы полнения последней команды сервисной

програ мы при появлении единичного сигнала Щ на входе -27 устройства единичный сигнал с выхода элемента И 14 поступит на управляющий вход блока 12 элементов И. Код-операнда, выводимого микропроцессором, поступит с входа 29 устройства.через открытый блок 12 элементов И на первый информационный вход блока 2 анал;иза. Кроме того, при этом триггер 9 переходит в единичное состояние и открывает элемент И 18. Следущая команда, которую выполняет микропроцессор, яв ляется командой условного перехода. В.первом цикле ее выполнения единичный сигнал SYNC поступает на вход 30 устройства и на второй вход элемента

И 18. Единичный сигнал с выхода элемента,- И 18 поступает на счетный вход счетчика 6 и формирует в нем код 01,

При этом на выходе 24 первого дешифратора 11 будет установлен единичный сигнал, который поступит на вход син

л

хронизации регистра 5. В регистр 5 будет записан код адерса первого байта команды условного перехода. Во втором цикле выполнения команды условного перехода в счетчик 6 по единичному сигнапу SYNC на входе 30 уст ройства будет установлен код 10. В результате этого на выходе 25 первого дешифратора 11 будет установлен единичный сигнал, который поступит на второй вход элемента И 17, на первый и второй управляющие входы коммутатора 13 и установит триггер- 9 в ис-.

ходное состояние. На выходах 22 и 23 блока ,2 в зависимости от результатов анализа будет установлен код Kj 10 или К 01. Па выходах второго дешифратора 40 в зависимости от результата определения разности Д, будет выставлен код d 10 или d 01. При условии выставления кодов , или У. d на выходе коммутатора 13 будет установлен единичный сигнал.

При .поступлении очередного единичного сигнала SYNC на вход 30 устройства счетчик 6 перейдет .в исходное... (нуленое) состояние, а триггер 10 перейдет в единичное состояние. При -отсутствии сбоя (отказа) триггер 10

не изменит своего состояния и работа . устройства будет продолжена.

35

Формула изобретения

5

Устройство для - контроля условных переходов микропроцессора, содержащее счетчик, первый, второй и третий триггеры, первый, второй, третий и четвертый элементы И-и элемент ИЛИ, причем единичный выход первого триггера соединен с первым входом .первого элемента ii, выход которого соединен с первым входом элемента ИЛИ, выход второго элемента И соединен с S-входом второго триггера, единичный . которого соединен с первым входом третьего элемента И, о т л и - ч а ю щ е е- с я тем, что, с целью повьпиения оперативности контроля, устройство дополнительно содержит комбинационньп-i преобразователь кода адреса команды в код типа условного перехода, блок анализа, блок суммирования, буферный.регистр операнда, бу- ферн,1Й регистр адреса, коммутатор, четвер.тый триггер, группу элементов И, первый и второй дешифраторы, при0

5

чем первый выход комбинационного преобразователя кода адреса команды в код типа условного перехода соединен с D-входом третьего триггера, единичный выход которого соединен с первым входом второго элемента И, выход второго элемента И соединен с управляющими входами элементов И группы, с первым и с вторым информационными входами коммутатора, выходы элементов И группы соединены с первым информационным входом блока анализа, второй выход комбинационного преобразователя кода адреса команды в код типа условного перехода соединен с D-BKO- дом первого триггера, третий выход комбинационного преобразователя кода адреса команда в код типа условного перехода соединен с управляющим в:.о- дом блока анализа, первый выход которого соединен с третьим информационным входом коммутатора, выход буферного регистра операнда соединен с вторым информационным входом блока анализа, второй выход которого соединен с четвертым информационньм входом коммутатора, вход записи устройства соединен с вторыми входами, элемента ИЛИ и второго элемента И, вход режима устройства соединен с С-входа- ми первого и третьего триггеров и вторым входом первого элемента И, вход синхронизации устройства соединен с первым входом четвертого элемента И, вторым входом третьего элемента И и с С-входом четвертого, триггера, вход данных устройства соединен с информационными входами буферного регистра операнда и элементов И группы, вход адреса устройства соединен с входом комбинационного преобразователя кода адреса кома.нды в код типа условного перехода, информационным входом буферного регистра адреса и первым информационным входом блока суммирования, выход буферного регистра адреса соединен с вторым информационным входом блока суммирования, выход которого соединен с входом вто- jporo дешифратора i первьй и второй выходы которого соединены с и Шестым информационными входами к.омму0

5

0

5

0

5

0

5

0

татора соответственно, выход третьего элемента И соединен со счетным входом счетчика, выход которого соединен с входом первого дешифратора, первый выход первого дешифратора соединен с входом, синхронизации буферного регистра адреса, второй выход первого дешифратора соединен с вторым входом четвертого элемента И, R-BXO- дон второго триггера и первым и вторым управляющими входами коммутатора, выход коммутатора сое1динен с D-входом четвертого триггера, единичный выход которого соединен с выходом отказа устройства, выход четвертого элемента И соединен с.входом сброса счетчика, выход элемента ИЛИ соединен с входом синхронизации буферного .регистра операнда, причем блок анализа содержит схему сравнения, сумматор по модулю два, два коммутатора, элемент 1-ШИ и элемент НЕ, причем первый информационный вход блока анализа соединен с первым входом схемы сравнения и входом сумматора по модулю два, второй информационный вход блока анализа соединен с вторь1м входом схемы сравнеггия, выход Больше которой соединен с первым входом элемента ИЛИ, первым и вторым информационными входами первого коммутатора, выход Меньше схемы сравнения соединен с вторым входом элемента ИЛИ и первым и вторым информационными входами второго коммутатора, выход Равно схемы сравнения соединен с третьим информационным входом второго коммутатора, выход сумматора по модулю два соединен с третьим информационным входом первого коммутатора и через элемент НЕ с четвертым информационным входом второго коммутатора, выход элемента ИЛИ соединен с четвер- тым информационным входом первого коммутатора, первый, второй, третий и четвертый входы первого и второго коммутаторов соединены с управляюпщм входом блока анализа, выход первого коммутатора соединен с первым выходом блока анализа, выход второго коммутатора соединен с вторым выходом блока анализа.

I

a

Jl-Jl-J - ru... JA-Jl-Jb. t

- JT-/V-A -/l-.-A.-y.A

IXIDCDC

/

/-V

Редактор М. Товтин

Составитель Д. Ванюхин. .,,

Техред Л.Сердгокова Корректор Г. Решетник

Заказ 3293/50 . Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

39

ffff

r

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микропроцессорной системы | 1985 |

|

SU1287161A1 |

| Микропроцессорная система с контролем | 1984 |

|

SU1242976A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Устройство для отладки программ | 1982 |

|

SU1100627A1 |

| Устройство для контроля последовательности выполнения программ | 1987 |

|

SU1536389A1 |

| Микропроцессор | 1982 |

|

SU1037263A1 |

| Микро-ЭВМ | 1982 |

|

SU1124316A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

Изобретение относится к области микропроцессорной техники и может быть использовано при построении средств контроля микропроцессоров. Целью изобретения является повышение оперативности контроля. Устройство содержит комбинационный преобразователь кода адреса команды в код типа условного перехода, блок анализа, блок суммирования, буферный регистр операнда, буферный регистр адреса, счетчик, четыре триггера, два дешифратора, группу элементов И, коммутатор, четыре элемента И, элемент ИЛИ. 4 ил., 2 табл. (О (Л ю 00 00 о О)

| Микропрограммный процессор | 1977 |

|

SU705452A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммный процессор | 1978 |

|

SU765809A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Коффрон Дж | |||

| Технические средства микропроцессорных систем.-М.: Мир, 1983. | |||

Авторы

Даты

1986-06-15—Публикация

1984-11-19—Подача