с первым входом шестого элемента ИНЕ, вход режима блока управления соединен с третьими входами первого и второго элементов И-НЕ, выход первого триггера соединен с первым управляющим входом первого дешифратора, с управляющим входом второго дешифратора, выход второго триггера соединен с входом третьего элемента И-НЕ, выход которого соединен с управляющими входами элементов И группы, единичный выход третьего триггера соединен с первым входом четвертого элемента , с первым входом третьего дешифратора, с четвертым входом второго элемента И-НЕ, с вторым управляющим входом первого дешифратора с входом пятого элемента И-НЕ и вторым входом шестого элемента И-НЕ, Нулевой выход третьего триггер а соединен с четвертым входом первого элемента И-НЕ, выход которого соединен с единичными входами второго и

третьего триггеров,,- с вторым входом элемента ИЛИ-НЕ и является первым выходом блока, выход четвертого триггера соединен с вторым входом третьего дешифратора, с входом синхронизации третьего триггера и вторым входом четвертого элемента И-НЕ, выход которого является вторым выходом блока, выход пятого триггера соединен с третьим входом третьего дешифратора, первый и второй выходы которого являются соответственно третьим и четвертым выходами блока, выходы пятого и шестого элементов И-НЕ соединены соответственно с входами синхронизации четвертого и пятого триггеров, выход второго элемента И-НЕ соединен с третьим входом элемента ИЛИ-НЕ и единичным вьпсодом пятого триггера, выход регистра команды перехода соединен с информационными входами элементов И группы, выходы которых соединены с выходом да:нных блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1282139A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для отладки программно-аппаратных блоков | 1983 |

|

SU1242965A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1348839A1 |

| Устройство для отладки микропроцессорной системы | 1987 |

|

SU1453408A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

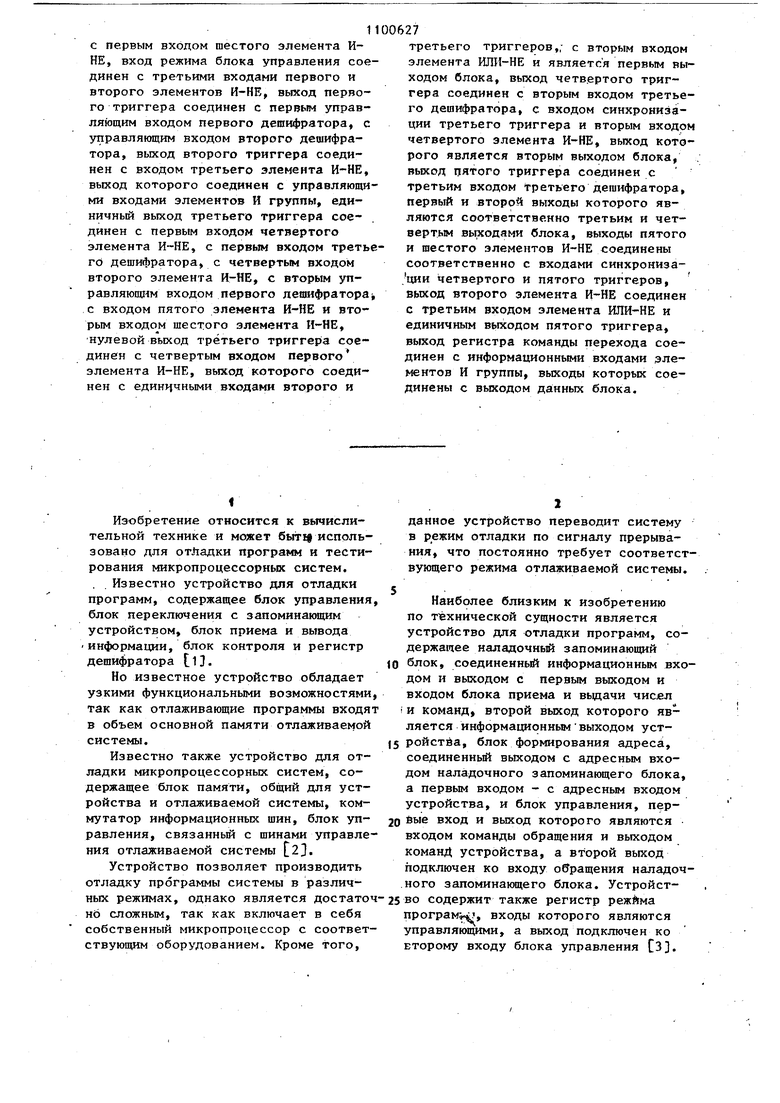

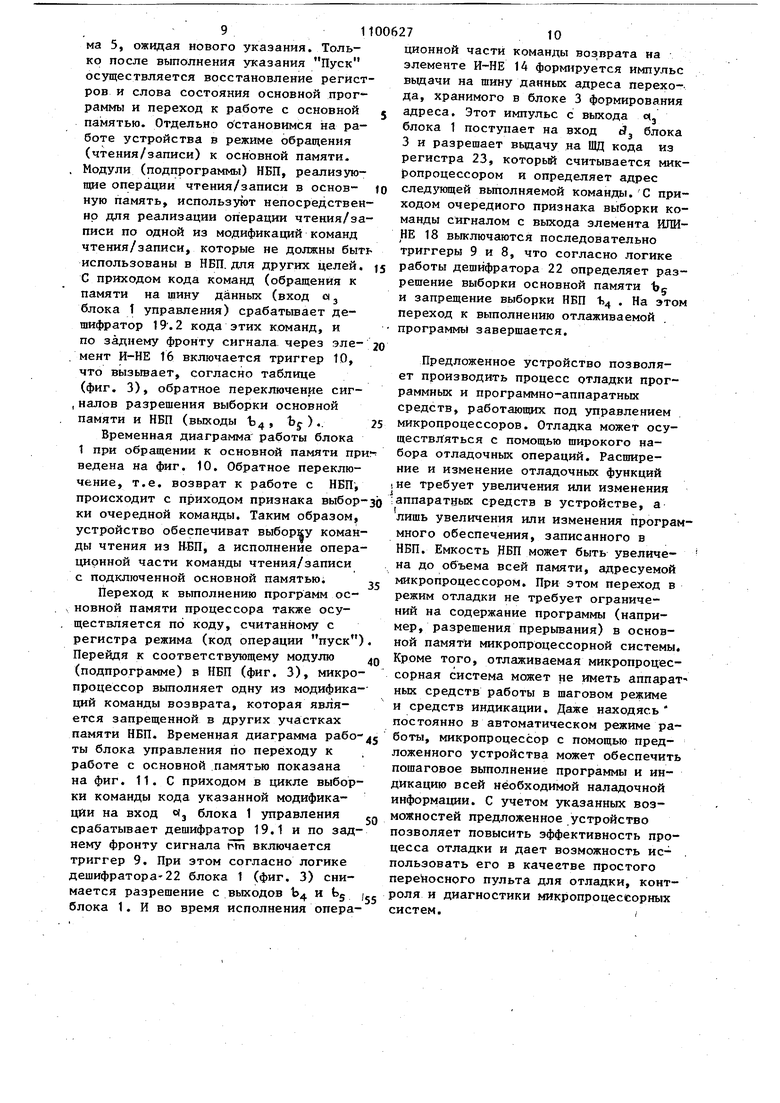

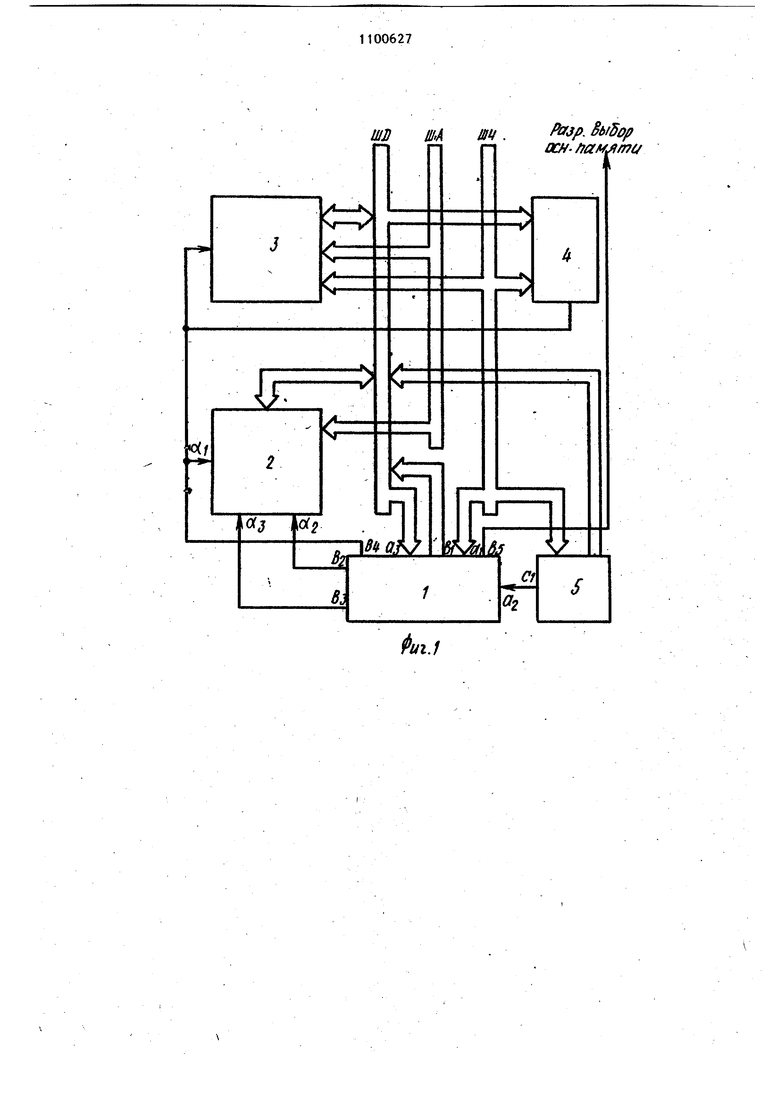

УСТРОЙСТВО ДЛЯ ОТЛАДКИ ПРОГРАММ, содержащее наладёчный блок памяти, блок управления, блок формирования адреса и регистр режима, причем информационные вход и выход устройства через шину данных соединены соответственно с входом и выходами данных наладочного блока памяти и блока управления, адресные входы наладочного блока памяти и блока формирования адреса образуют входную адресную шину устройства, управляющие, входы наладочного блока памяти, блока управления и регистра режима образуют управляющую шину устройства,выход регистра режима соединен с входом режима блока управления, отличиющ е е с я тем, что, с целью расширения функциональных возможностей устройства за счет наращивания сервисных операций, в устройство введен блок отображения Kn optjiaiifm причем первый, второй. Третий и четверть1|й выходы блока правления соединены соответственно с первым, вторым, третьим входами блока Формирования адреса и упрЪ яющим выходом разрешения выборки основной памяти устройства, третий выход блока управления соединен с управляющими входами наладочного блока памяти и блока отображения информации, шина данных устройства соединена с входом и выходом данных блока формирования адреса и с первыми входами блока отображения информации, управляющая шина устройства соединена с вторым входом блока отображения информации, причем блок управления содержит пять триггеров, команды перехода, группу элементов И, шесть элементов И-НЕ, первый, второй и третий дешифраторы, О) элемент ИЖ-НЕ и элемент НЕ, причем первый разряд управляющего входа блока соединен с D-входом первого триггера, с первыми входами первого и второго элементов И-НЕ, второй разряд управляющего входа блока соединен с вторыми входами первого и второго элементов И-НЕ и с входом синхронизации первого триггера, третий разряд управлякицего входа блока соединен с входом синхронизации второго тригге- , ра и через элемент НЕ с управляющими входами третьего, четвертого, пятого и шестого элементов И-НЕ, четвертый разряд управляющего входа блока соединен с входами установки нуля второго и третьего триггеров и с первым входом элемента ИЛИ-НЕ, выход которого соединен с входом установки нуля четвертого триггера, вход данных блока соединен с информационными входами первогои второго дешифраторов, вы, ходы которых соединены соответственно сГ -входами четвертого триггера и

Иэобретение относится к вычислительной технике и может бьтп использовано для отладки программ и тестирования микропроцессорных систем. . . Известно устройство для отладки программ, содержащее блок управления, блок переключения с запоминающим устройством, блок приема и вывода информации, блок контроля и регистр дешифратора t1.

Но известное устройство обладает узкими функциональными возможностями, так как отлаживающие программы входят в объем основной памяти oтлaживae oй системы.

Известно также устройство для отладки микропроцессорных систем, содержащее блок памяти, общий для устройства и отлаживаемой системы, коммутатор информационных шин, блок управления, связанный с шинами управления отлаживаемой системы L23.

Устройство позволяет производить отладку программы системы в различных режимах, однако является достаточно сложным, так как включает в себя собственный микропроцессор с соответствующим оборудованием. Кроме того.

данное уст зойство переводит систему в отладки по сигналу прерывания, что постоянно требует соответствующего режима отлаживаемой системы.

Наиболее близким к изобретению по технической сущности является устройство для отладки программ, содержащее наладочный запоминающий

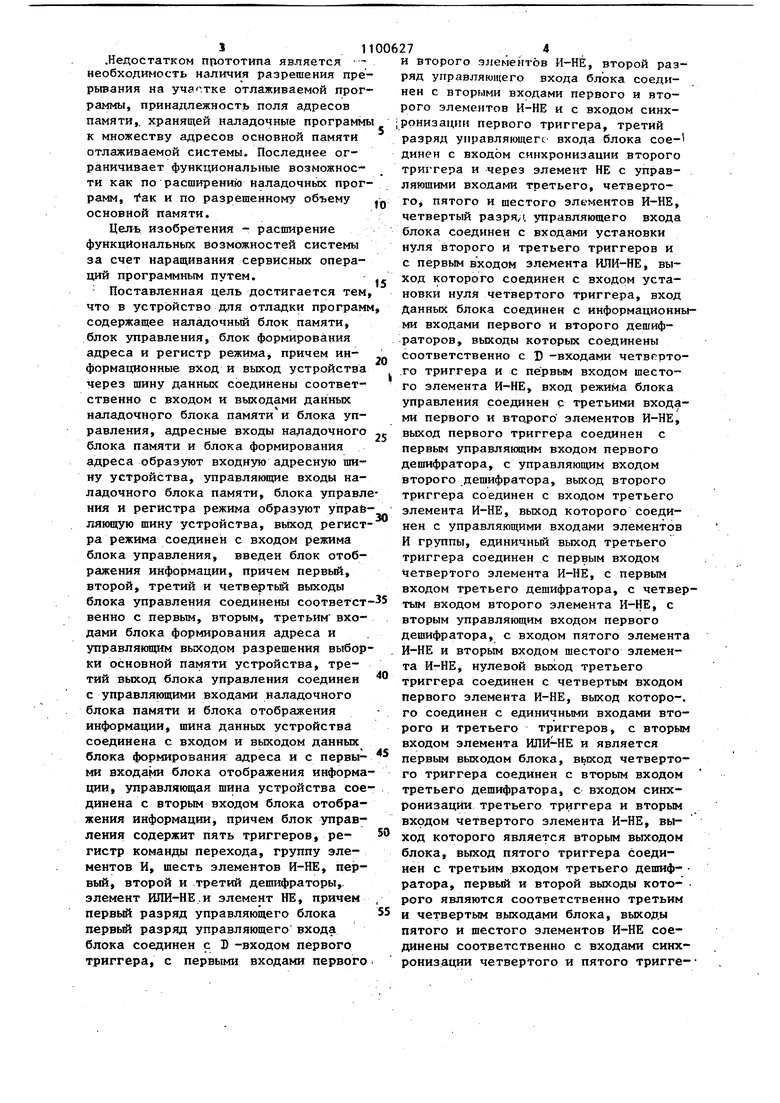

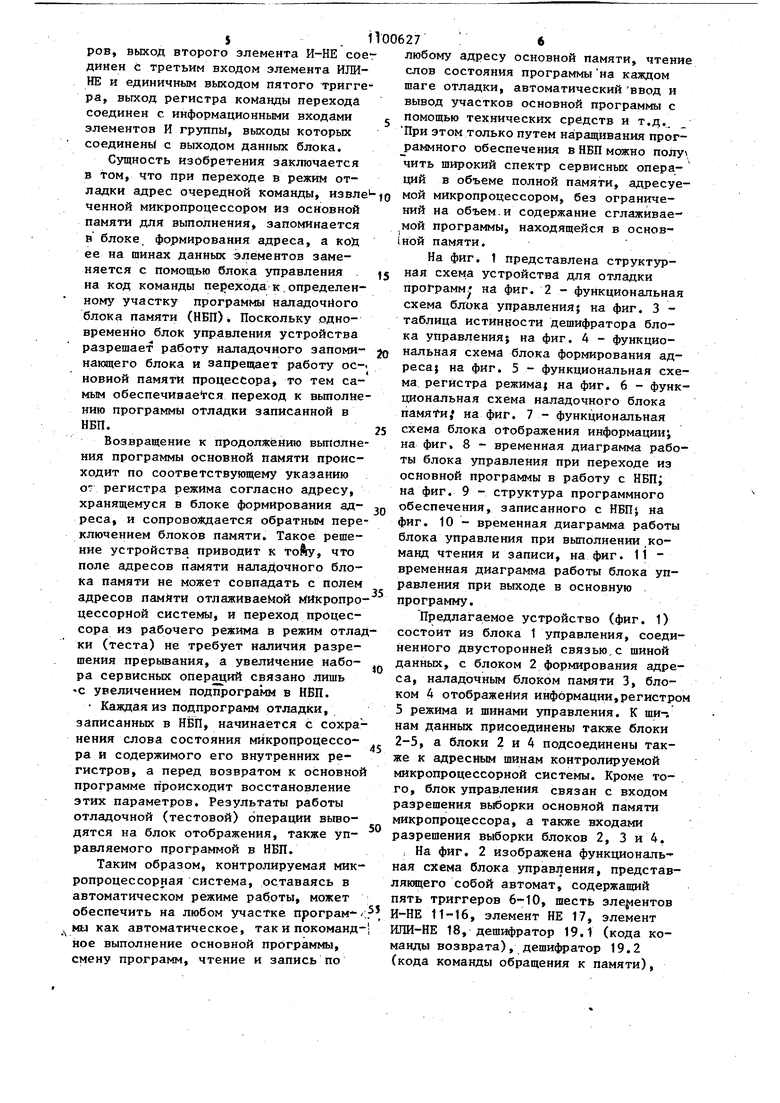

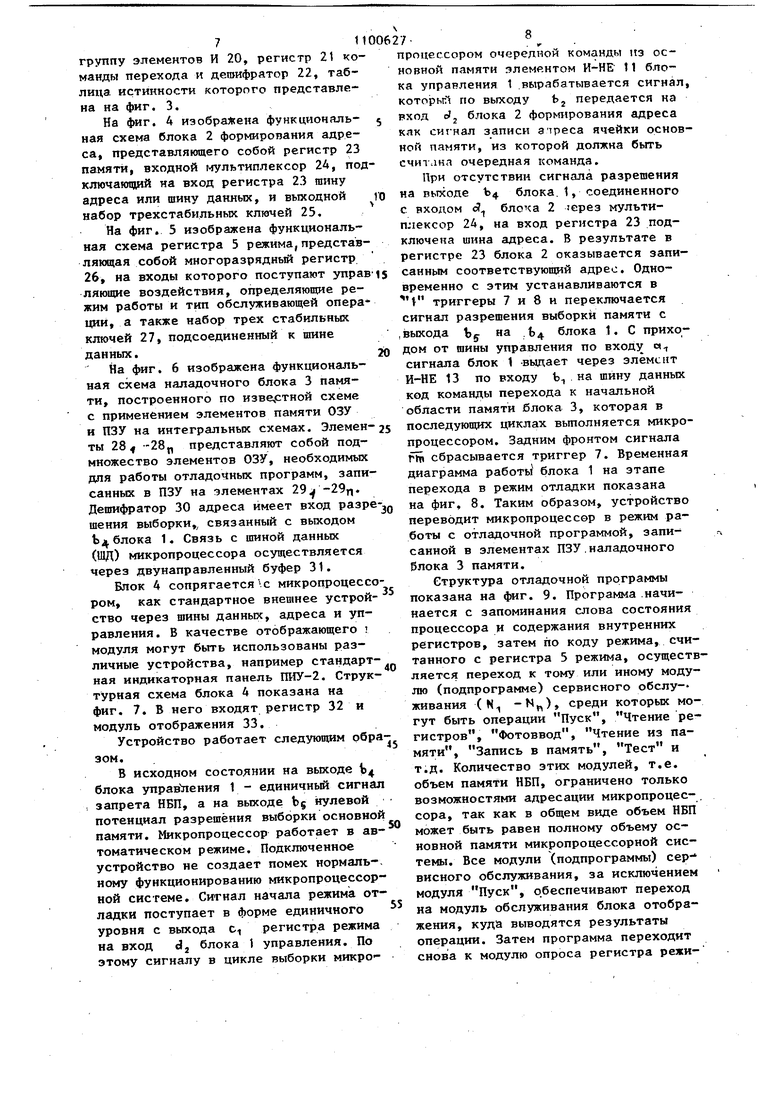

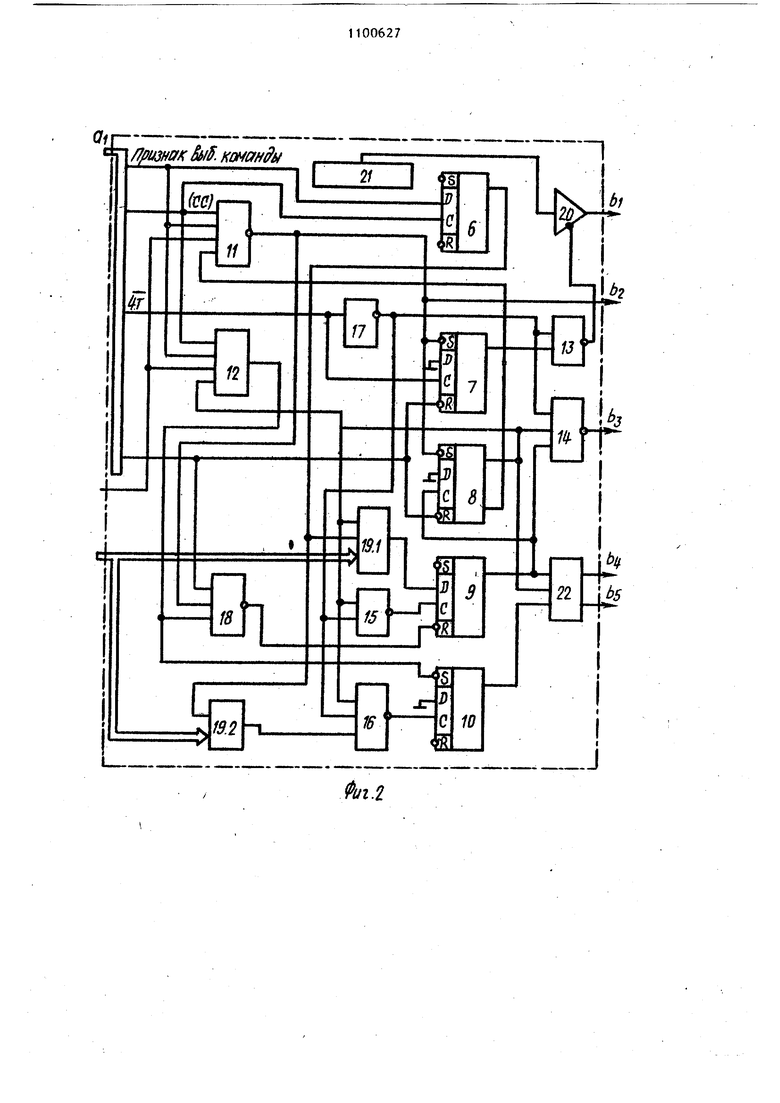

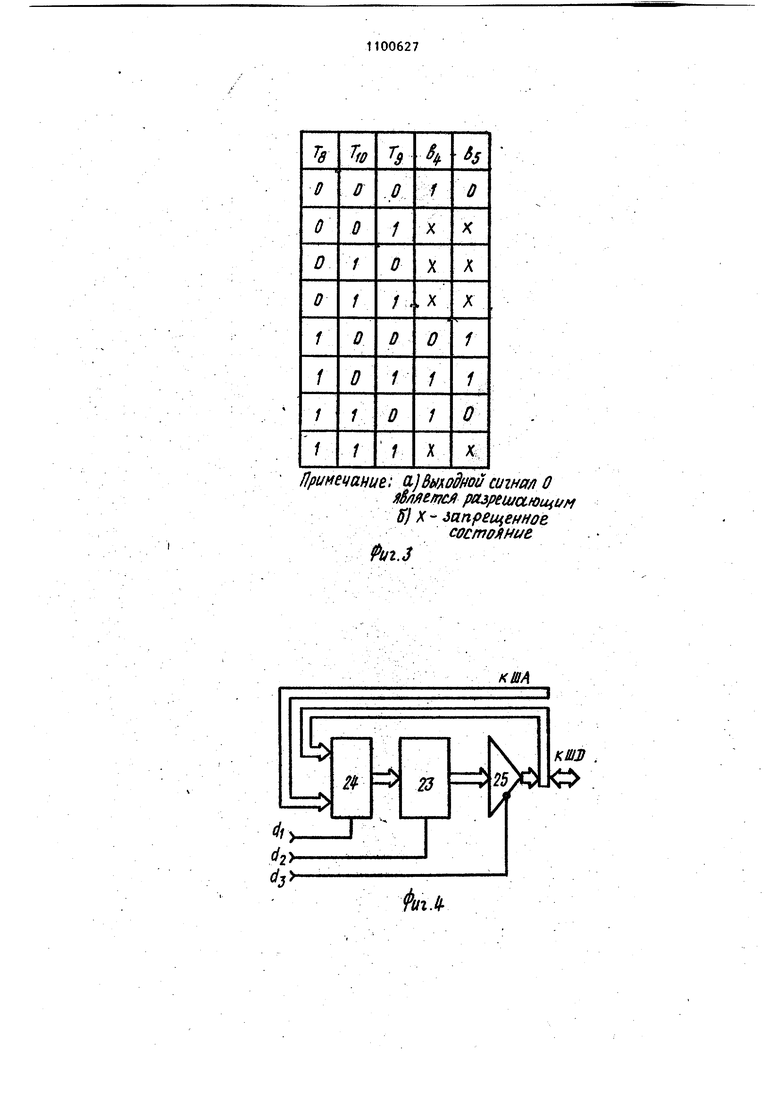

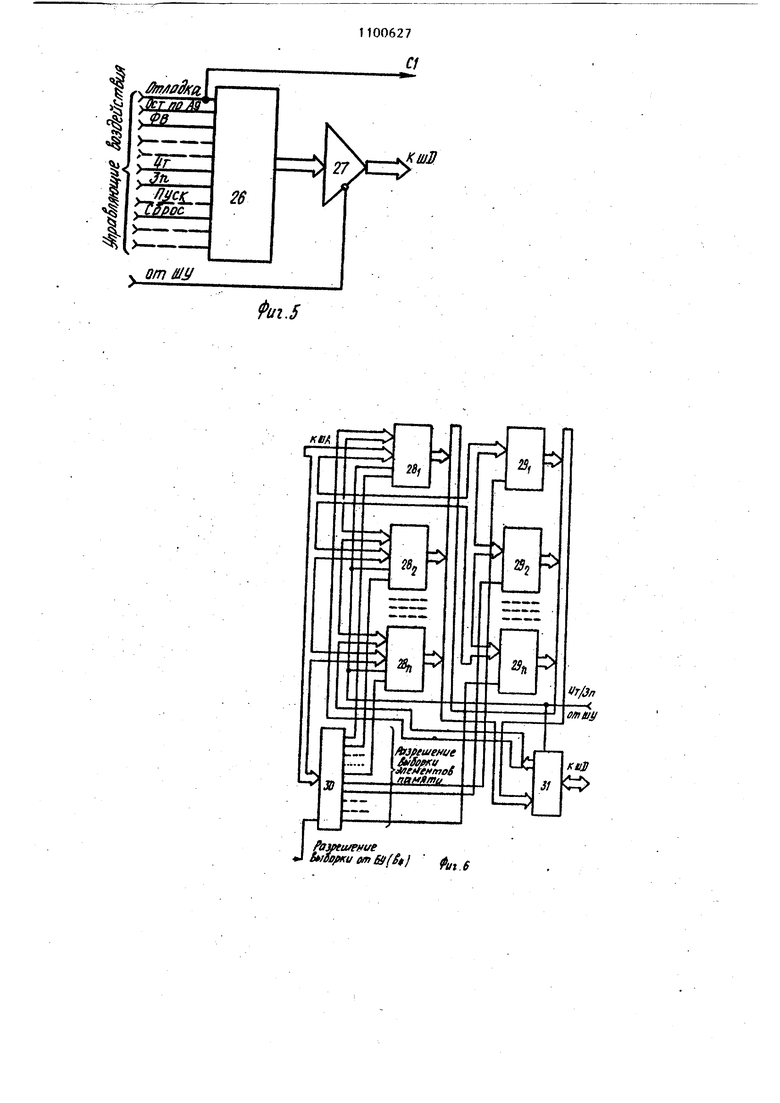

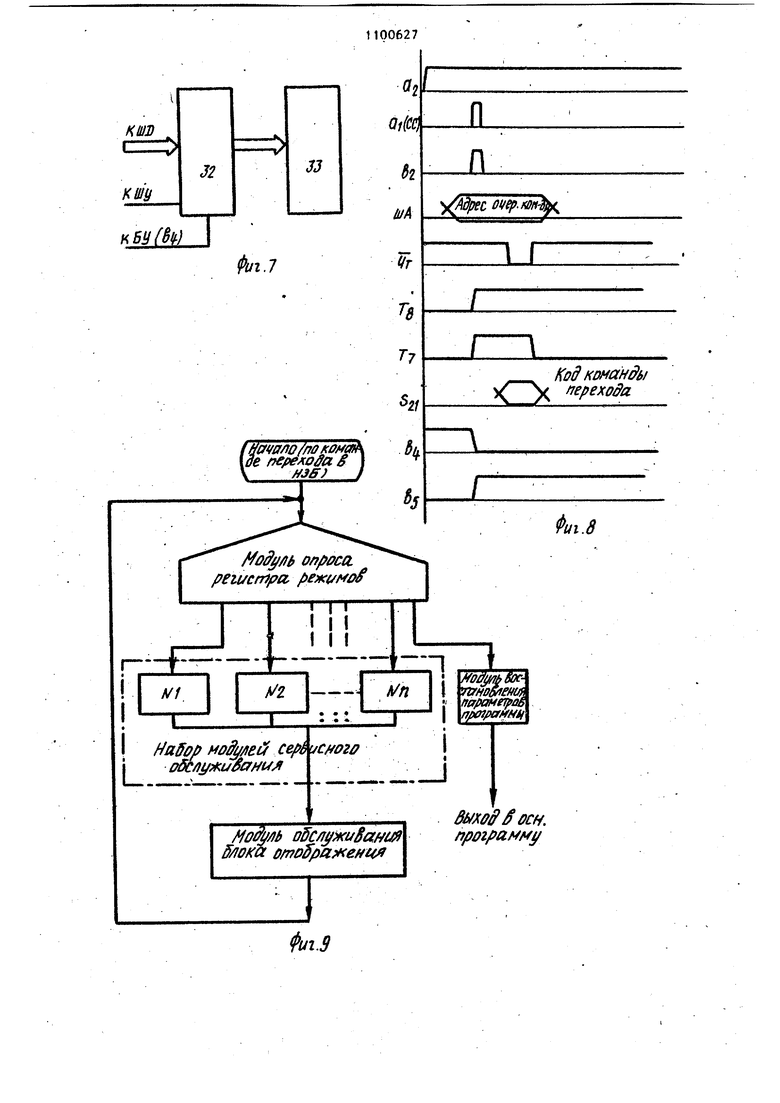

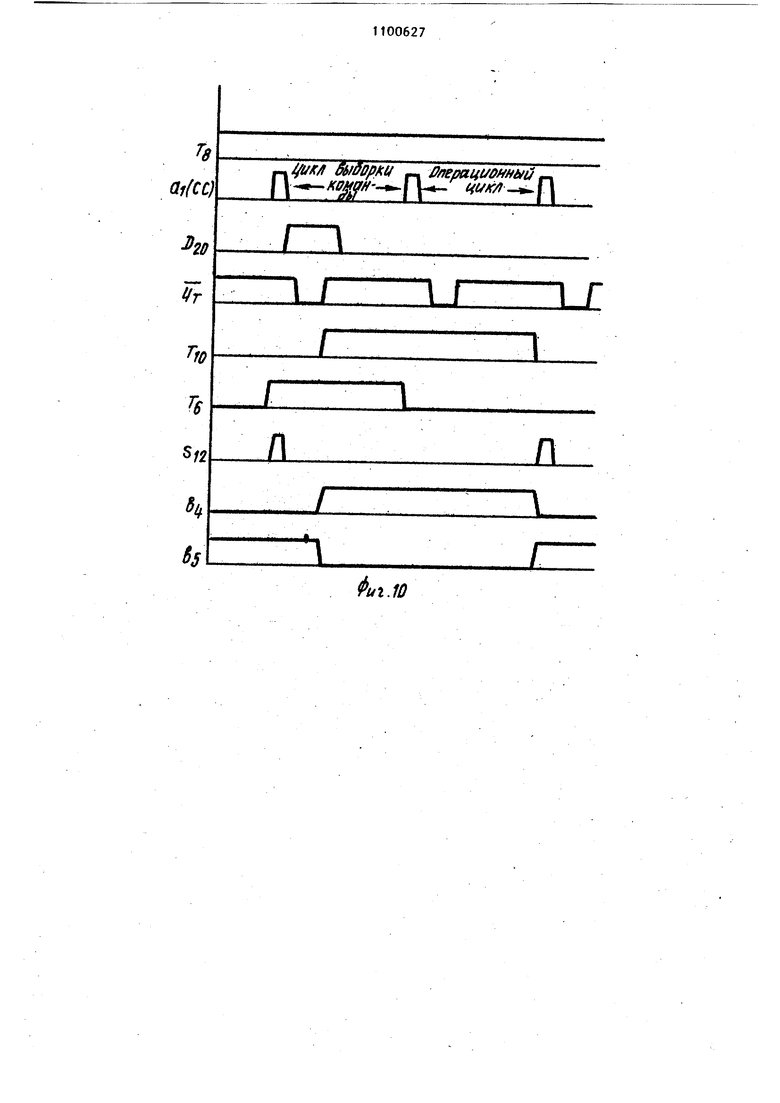

блок, соединенный информационным входом и выходом с первым выходом и входом блока приема и вьщачи чисел и команд второй выход которого является информационнымвыходом устройства, блок формирования адреса, соединенньй выходом с адресным входом наладочного запоминающего блока, а первым входом - с адресным входом устройства, и блок управления, перfibie вход и выход которого являются входом команды обращения и выходом команд устройства, а второй выход подключен ко входу обращения наладочного запоминающего блока. Устроиство содержит также регистр режима програм, входы которого являются управляющими, а выход подключен ко второму входу блока управления СЗ. .Недостатком прототипа является необходимость наличия разрешения пре рывания на участке отлаживаемой прог раммы, принадлежность поля адресов памяти,, хранящей наладочные программ к множеству адресов основной памяти отлаживаемой системы. Последнее ограничивает функциональные возможности как по расширению наладочных прог рамм, faK и по разрешенному объему основной памяти. изобретения - расширение функциональных возможностей системы за счет наращивания сервисных операций программным путем. Поставленная цель достигается тем что в устройство для отладки програм содержащее наладочный блок памяти, блок управления, блок формирования адреса и регистр режима, причем информационные вход и выход устройства через шину данных соединены соответственно с входом и выходами данных наладочного блока памяти и блока управления, адресные входы наладочного блока памяти и блока формирования адреса образуют входную адресную шину устройства, управляющие входы наладочного блока памяти, блока управл ния и регистра режима образуют управ ляющую шину устройства, выход регист ра режима соединен с входом режима блока управления, введен блок отображения информации, причем первый, второй, третий и четввртьй выходы блока управления соединены соответст венно с первым, вторым, третьим входами блока формирования адреса и управляющим вькодом разрешения выбор ки основной памяти устройства, третий выход блока управления соединен с управляющими входами наладочного блока памяти и блока отображения информации, шина данных устройства соединена с входом и выходом данных блока формирования адреса и с первыми входами блока отображения информа ции, управляющая шина устройства сое динена с вторым входом блока отображения информации, причем блок управления содержит пять триггеров, регистр команды перехода, группу элементов И, шесть элементов И-НЕ, первый, второй и третий дешифраторы,, элемент ИЛИ-НЕ.и элемент НЕ, причем первый разряд управляющего блока первый разряд управляющего входа блока соединен с D -входом первого триггера, с первыми входами первого 1 274 и второго элементов И-НЁ, второй разряд управляющего входа блока соединен с вторыми входами первого и второго элементов И-НЕ и с входом синхронизации первого триггера, третий разряд управляющегс- входа блока соединен с входом синхронизации второго три1тера и через элемент НЕ с управляющими входами третьего, четвертого, пятого и шестого элементов И-НЕ, четвертый разряд, управляющего входа блока соединен с входами установки нуля второго и третьего триггеров и с первым входом элемента ИЛИ-НЕ, выход которого соединен с входом установки нуля четвертого триггера, вход данньк блока соединен с информационными входами первого и второго дешифраторов, вькоды которых соединены соответственно с Б -входами четврртото триггера и с первым входом шестого элемента И-НЕ, вход режима блока управления соединен с третьими входами первого и второго элементов И-НЕ, выход первого триггера соединен с первым управляющим входом первого дешифратора, с управляющим входом второго дешифратора, выход второго триггера соединен с входом третьего элемента И-НЕ, выход которого соединен с управляющими входами элементов И группы, единичньй выход третьего триггера соединен с первым входом четвертого элемента И-НЕ, с первым входом третьего дешифратора, с четвертым входом второго элемента И-НЕ, с вторым управляющим входом первого дешифратора, с входом пятого элемента И-НЕ и вторым входом шестого элемента И-НЕ, нулевой выход третьего триггера соединен с четвертым входом первого элемента И-НЕ, выход которо-. го соединен с единичными входами второго и третьего триггеров, с вторым входом элемента ИПИ-НЕ и является первым выходом блока, вькод четвертого триггера соединен с вторым входом третьего дешифратора, с входом синхронизации третьего триггера и вторым входом четвертого элемента И-НЕ, выход которого является вторым выходом блока, выход пятого триггера соединен с третьим входом третьего дешиф- ратора, первый и второй выходы кото- . рого являются соответственно третьим и четвертым выходами блока, выходы пятого и шестого элементов И-НЕ соединены соответственно с входами синхронизации четвертого и пятого тригге- ров, выход второго элемента И-НЕ сое динен с третьим входом элемента ИЛИНЕ и единичным выходом пятого тригге ра, выход регистра команды переходи соединен с информационными входами элементов И группы, выходы которых соединеньГ с выходом данных блока. Сущность изЬбретения заключается в том, что при переходе в режим отладки адрес очередной команды, извле ченной микропроцессором из основной памяти для выполнения, запоминается в блоке формирования адреса, а код ее на шинах данных элементов заменяется с помощью блока управления на код команды перехода к. определенному участку программы наладочйого блока памяти (НБП). Поскольку одновременно блок управления устройства разрешает работу наладочного запоминающего блока и запрещает работу основной памяти процессора то тем самым обеспечиваемся переход к вьтолне нию программы отладки записанной в НБП. Возвращение к продолжению выполне ния программы основной памяти происходит по соответствующему указанию О7 регистра режима согласно адресу, хранящемуся в блоке формирования адреса, и сопровождается обратным пере ключением блоков памяти. Такое решение устройства приводит к Tofty, что поле адресов памяти наладочного блока памяти не может совпадать с полем адресов памйти отлаживае1 ой Микропро цессорной системы, и переход процессора из рабочего режима в режим отла ки (теста) не требует наличия разрешения прерьшания, а увеличение набора сервисных операций связано лишь с увеличением подпрограмм в НБП. Каждая из подпрограмм отладки, записанных в НЁП, начинается с сохра нения слова состояния микропроцессора и содержимого его внутренних регистров, а перед возвратом к основно программе происходит восстановление этих параметров. Результаты работы отладочной (тестовой) операции вьгоодятся на блок отображения, также управляемого программой в НБП. Таким образом, контролируемая мик ропроцессорная система, оставаясь в автоматическом режиме работы, может обеспечить на любом участке програм мы как автоматическое, так и покоманд ное выполнение основной программы, смену программ, чтение и запись по любому адресу основной памяти, чтение слов состояния программы на каждом шаге отладки, автоматический ввод и вывод участков основной программы с помощью технических средств и т.д. При этом только путем наращивания прогjpaMMHoro обеспечения в НБП можно полу чить широкий спектр сервисных операций в объеме полной памяти, адресуе ой микропроцессором, без ограничений на объем.и содержание сглаживаемой программы, находящейся в основнЬй памяти. На фиг. 1 представлена структурная схема устройства для отладки про раммг на фиг. 2 - функциональная схема блока управления; на фиг. 3 таблица истинности дешифратора блока управления} на фиг. 4 - функциональная схема блока формирования адреса; на фиг. 5 - функциональная схема регистра режима| на фиг. 6 - функциональная схема наладочного блока памяти, на фиг. 7 - функциональная схема блока отображения информации; на фиг, 8 - временная диаграмма работы блока управления при переходе из основной программы в работу с НБП; на фиг. 9 - структура программного обеспечения, записанного с НБП; на фиг. 10 - временная диаграмма работы блока управления при вьтолнении ,ко манд чтения и записи, на фиг. 11 временная диаграмма работы блока управления при выходе в основную программу. Предлагаемое устройство (фиг. 1) состоит из блока 1 управления, соединенного двусторонней связью,с шиной данных, с блоком 2 формирования адреса, наладочным блоком памяти 3, блоком 4 отображения информации,регистром 5 режима и щинами управления. К щи-, нам данных присоединены также блоки 2-5, а блоки 2 и 4 подсоединены также к адресным шинам контролируемой микропроцессорной системы. Кроме того, блок управления связан с входом разрешения выборки основной памяти микропроцессора, а также входами разрешения выборки блоков 2, 3 и 4. , На фиг. 2 изображена функциональная схема блока управления, представяющего собой автомат, содержащий пять триггеров 6-10, шесть элементов И-НЕ 11-16, элемент НЕ 17, элемент ИЛИ-НЕ 18, дешифратор 19.1 (кода команды возврата), дешифратор 19.2 (кода команды обращения к памяти), группу элементов И 20, регистр 21 команды перехода и дешифратор 22, таблица истинности которого представлена на фиг. 3. На фиг. 4 изображена функциочальная схема блока 2 формирования адреса, представляющего собой регистр 23 памяти, входной г-гультиплексор 24, под ключающий на вход регистра 23 шину адреса или шину данных, и выходной набор трехстабильных ключей 25. На фиг. 5 изображена функциональная схема регистра 5 режима,представляющая собой многоразрядный регистр 26, на входы которого поступают управ ляющие воздействия, определяющие режим работы и тип обслуживающей опера ции, а также набор трех стабильных ключей 27, подсоединенный к шине данных. На фиг. 6 изображена функциональная схема наладочного блока 3 памяти, построенного по изве,стной схеме с применением элементов памяти ОЗУ и ПЗУ на интегральных схемах. Элементы 28 28 представляют собой подмножество элементов ОЗУ, необходимых для работы отладочных программ, записанных в ПЗУ на элементах 29 -29 Дешифратор 30 адреса имеет вход разре шения выборки, связанный с выходом Ъ; блока 1. Связь с шиной данных (ШД) микропроцессора осуществляется через двунаправленный буфер 31. Блок А сопрягается с микропроцессо ром, как стандартное внешнее устройство через шины данных, адреса и управления. В качестве отображающего г модуля могут быть использованы различные устройства, например стандартная индикаторная панель ПИУ-2. Струк турная схема блока 4 показана на фиг, 7. В него входят регистр 32 и модуль отображения 33. Устройство работает следующим обр зом. В исходном состоянии на выходе Ъ блока управления 1 единичный сигнал запрета НБП, а на выходе bg нулевой потенциал разрешения выборки основно памяти. Микропроцессор работает в ав томатическом режиме. Подключенное устройство не создает помех нормальному функционированию микропроцессор ной системе. Сигнал начала режима от ладки поступает в форме единичного уровня с выхода с регистра режима на вход dj блока 1 управления. По этому сигналу в цикле выборки микророцессором очередной команды из основной памяти элементом И-НЕ 11 блока управления 1 вырабатывается сигнал, KOTojJhrt по Ъ, ,j, передается на eJj блока 2 форьшрования адреса вход как сигнал записи ачреса ячейки основной памяти, из которой должна быть счшана очередная команда. При отсутствии сигнала разрешения на выходе Ъ блока.1, соединенного с входом 3 блоха 2 зерез мультиплексор 24, на вход регистра 23 подключена шина адреса. В результате в регистре 23 блока 2 оказывается записанным соответствующий адрес. Одновременно с этим устанавливаются в t триггеры 7 и 8 и переключается сигнал разрешения выборки памяти с 15ыхода Ъу на .Ь4 блока 1. С приходом от шины управления по входу « сигнала блок 1 -выдает через элемент И-НЕ 13 по входу Ъ на шину данных код команды перехода к начальной области памяти блока 3, которая в последующего циклах вьтолняется микропроцессором. Задним фронтом сигнала fhi сбрасывается триггер 7. Временная диаграмма работы блока 1 на этапе перехода в режим отладки показана на фиг, 8. Таким образом, устройство переводит микропроцессор в режим работы с отладочной программой, записанной в элементах ПЗУ.наладочного блока 3 памяти. Структура отладочной программы показана на фиг. 9. Программа .начинается с запоминания слова состояния процессора и содержания внутренних регистров, затем по коду режима, считанного с регистра 5 режима, осуществляется переход к тому или иному модулю (подпрограмме) сервисного обслу- живания (N -N), среди которых могут быть операции Пуск, Чтение регистров, Фотоввод, Чтение из памяти, Запись в память, Тест и т.д. Количество этих модулей, т.е. объем памяти НБП, ограничено только возможностями адресации микропроцес-, сора, так как в общем виде объем НБП может быть равен полному объему основной памяти микропроцессорной системы. Все модули (подпрограммы) сервисного обслуживания, за исключением модуля Пуск, о.беспечивают переход на модуль обслуживания блока отображения, куда выводятся результаты операции. Затем программа переходит снова к модулю опроса регистра режима 5, ожидая нового указания. Только после выполнения указания Пуск осуществляется восстановление регистров и слова состояния основной программы и переход к работе с основной j памятью. Отдельно остановимся на работе устройства в режиме обращения (чтения/записи) к основной памяти. Модули (подпрограммы) НБП, реализующие операции чтения/записи в основ- fo ную память, используют непосредственно для реализации операции чтения/записи по одной из модификаций команд чтения/записи, которые не должны быть использованы в НБП. для других целей, tf С приходом кода команд (обращения к памяти на шину данных (вход а,, блока Т управления) срабатывает дешифратор 19. 2 кода этих команд, и по заднему фронту сигнала через эле- 20 мент И-НЕ 16 включается триггер 10, что вызьгоает, согласно таблице (фиг. 3), обратное переключение сигналов разрешения выборки основной памяти и НБП (выходы Ъ, у « 25

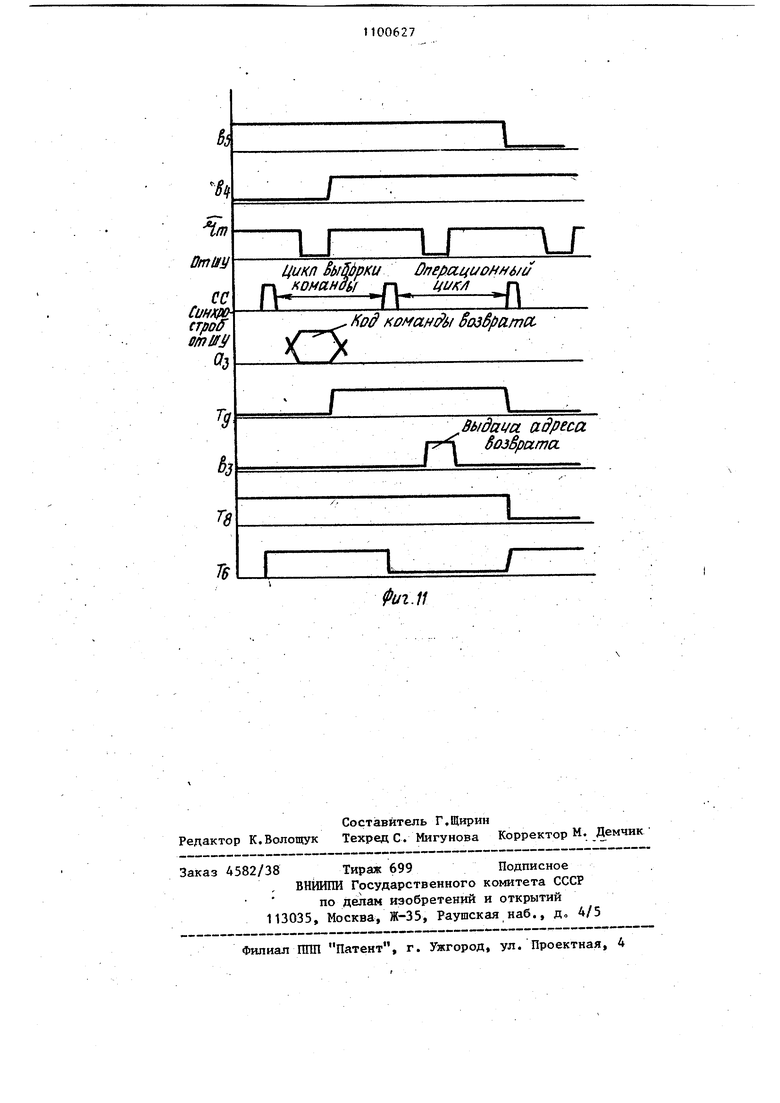

Временная диаграмма работы блока 1 при обращении к основной памяти при; ведена на фиг. 10. Обратное переключение, т.е. возврат к работе с НБП, происходит с приходом признака выбор-зо ки очередной команды. Таким образом, устройство обеспечиват выборку команды чтения из Н-БП, а исполнение операционной части команды чтения/записи с подключенной основной памятью.

Переход к вьтолнению программ основной памяти процессора также осуществляется по коду, считанному с регистра режима (код операции пуск). Перейдя к соответствующему модулю о (подпрограмме) в НБП (фиг. 3), микропроцессор выполняет одну из модификаций команды возврата, которая является запрещенной в других участках памяти НБП. Временная диаграмма рабо-45 ты блока управления по переходу к работе с основной памятью показана на фиг. 11. С приходом в цикле выборки команды кода указанной модификации на вход «3 блока 1 управления срабатывает дешифратор 19.1 и по заднему фронту сигнала rtri включается триггер 9. При этом согласно логике дешифратора-22 блока 1 (фиг. 3) снимается разрешение с выходов Ь4 Ц 45 блока 1. И во время исполнения операционной части команды возврата на элементе 14 форштруется импульс вьщачи на шину данных адреса перехода, хранимого в блоке 3 формирования адреса. Этот импульс с выхода ч блока 1 поступает на вход cfj блока 3 и разрешает вьвдачу на ШД кода из регистра 23, которьй считывается микропроцессором и определяет адрес следующей выполняемой команды.С приходом очередного признака выборки команды сигналом с выхода элемента ИЛИНЕ 18 выключаются последовательно триггеры 9 и 8, что согласно логике работы дешифратора 22 определяет разрешение выборки основной памяти ) и запрещение выборки НБП l . На этом переход к выполнению отлаживаемой программы завершается.

Предложенное устройство позволяет производить процесс отладки программных и программно-аппаратных средств, работающих под управлением микропроцессоров. Отладка может осуществляться с помощью широкого набора отладочных операций. Расширение и изменение отладочных функций .не требует увеличения или изменения ;аппаратных средств в устройстве, а лишь увеличения или изменения программного обеспечения, записанного в НБП. Емкость НБП может быть увеличена до объема всей памяти, адресуемой микропроцессором. При этом переход в режим отладки не требует ограничений на содержание программы (например, разрешения прерьгоания) в основной памяти микропроцессорной системы. Кроме того, отлаживаемая микропроцессорная система может не иметь аппаратных средств работы в шаговом режиме и средств индикации. Даже находясь постоянно в автоматическом режиме работы, микропроцессор с помощью предложенного устройства может обеспечить пошаговое выполнение программы и индикацию всей необходимой наладочной информации. С учетом указанных возможностей предложенное устройство позволяет повысить эффективность процесса отладки и дает возможность испольэовать его в качестве простого переносного пульта для отладки, контроля и диагностики микропроцессорных систем.

/Lм-V

(г

ofj , o

М ej

WS Д4 ШЧ. /

оу/-/ afMff7e/

Ч RfUL.

gA/ /

Г/

2

/ ринечание: а, Выгодной сигнал О

Vr

(

fiS/i inc разрешающим 57 х- anpeutef/ffoe состав Hue

hi.S

KllID

о

ФигЛ

KttA

/ ytu/pffue

MofKuom6 l{St} ф

Фиг.9

4/2. Л

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО ДЛЯ ОТЛАДКИ ПРОГРАММ | 0 |

|

SU277410A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-06-30—Публикация

1982-07-12—Подача