(54) НАКАПЛИВАКЯЦИЙ СУММАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый арифметический модуль | 1979 |

|

SU855654A1 |

| Арифметико-логическое устройство со встроенной диагностикой | 1984 |

|

SU1275426A1 |

| Устройство для возведения в квадрат | 1988 |

|

SU1534458A2 |

| Двоично-десятичное арифметико-логическое устройство накапливающего типа | 1981 |

|

SU1024904A1 |

| Процессор параллельной обработки | 1990 |

|

SU1797126A1 |

| Арифметико-логическое устройство | 1987 |

|

SU1495782A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Число-импульсное арифметическое устройство | 1980 |

|

SU951303A1 |

| Дифференцирующее устройство | 1983 |

|

SU1117657A1 |

| УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 1997 |

|

RU2119717C1 |

I

Изобретение относится к вычислительной технике и может использоваться для построения устройств арифметической и логической обработки двоичных чисел.

Известен накапливакяций сумматор, содержащий в каждом разряде триггер, пять элементов И, два элемента задержки, выход переноса и выход результата, информационный вход и две управлякщие шины для сдвига вправо и сдвига влево 1

Недостатком такого сумматора является ограниченный набор математических операций (не реализует логических операций) .

Наиболее близким к предлагаемому является накапливакщий сумматор, содержащий триггерный накапливакщий регистр, триггерный приемный регистр; элементы И и ИЛИ, причем в каждом разряде единичный вход приемного регистра подключен к первым входам первого и второго элементов И, ко

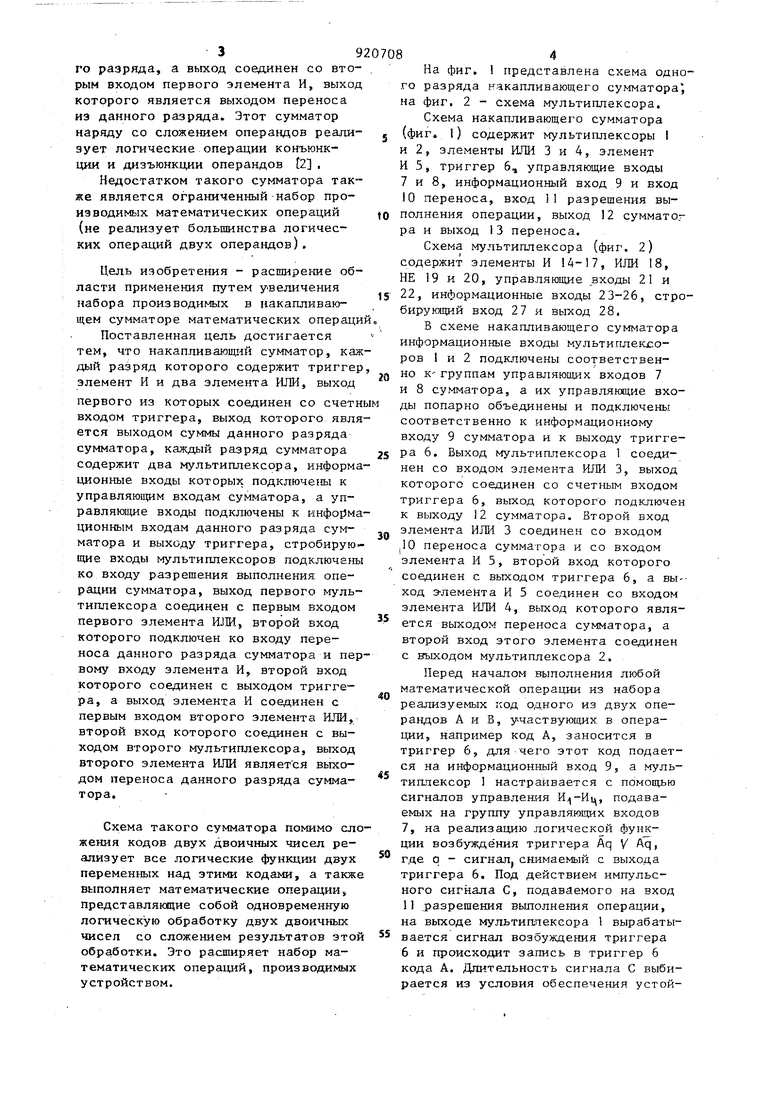

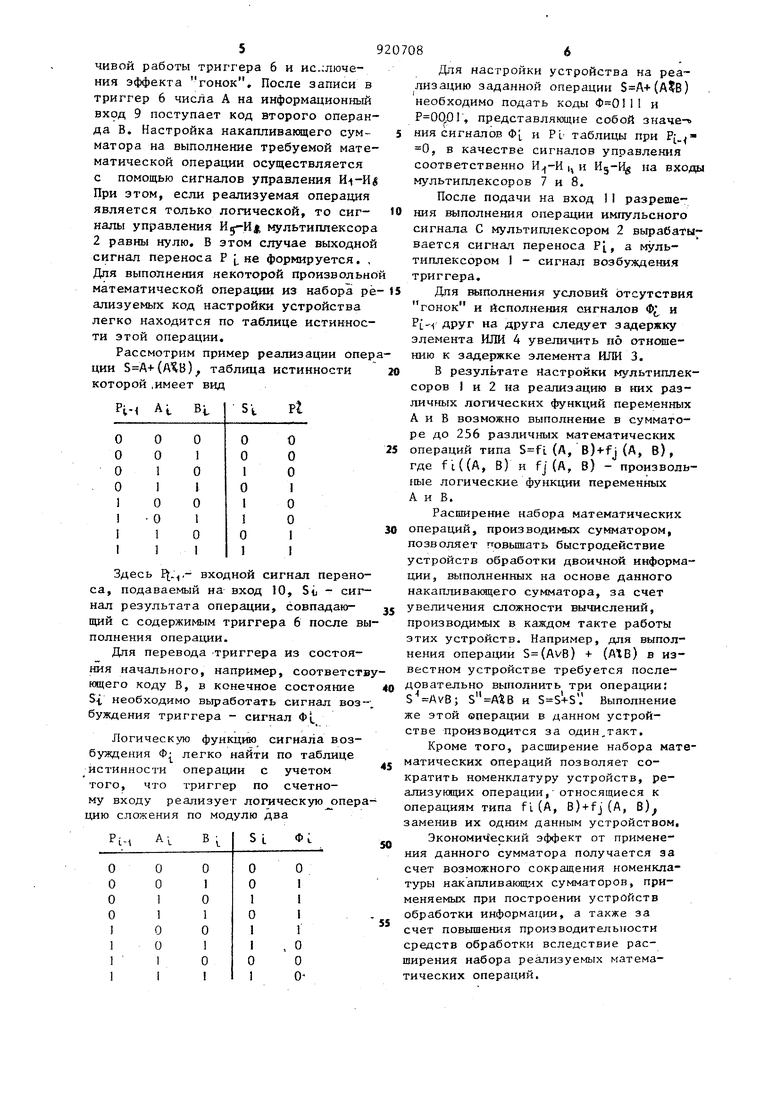

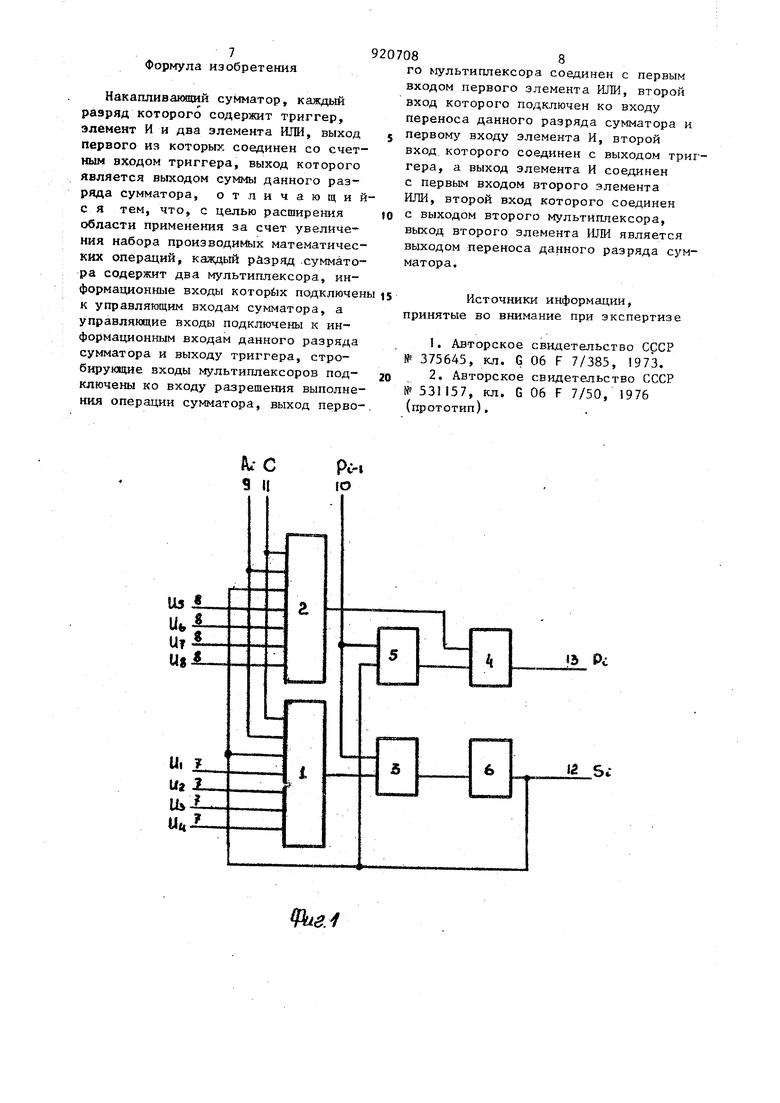

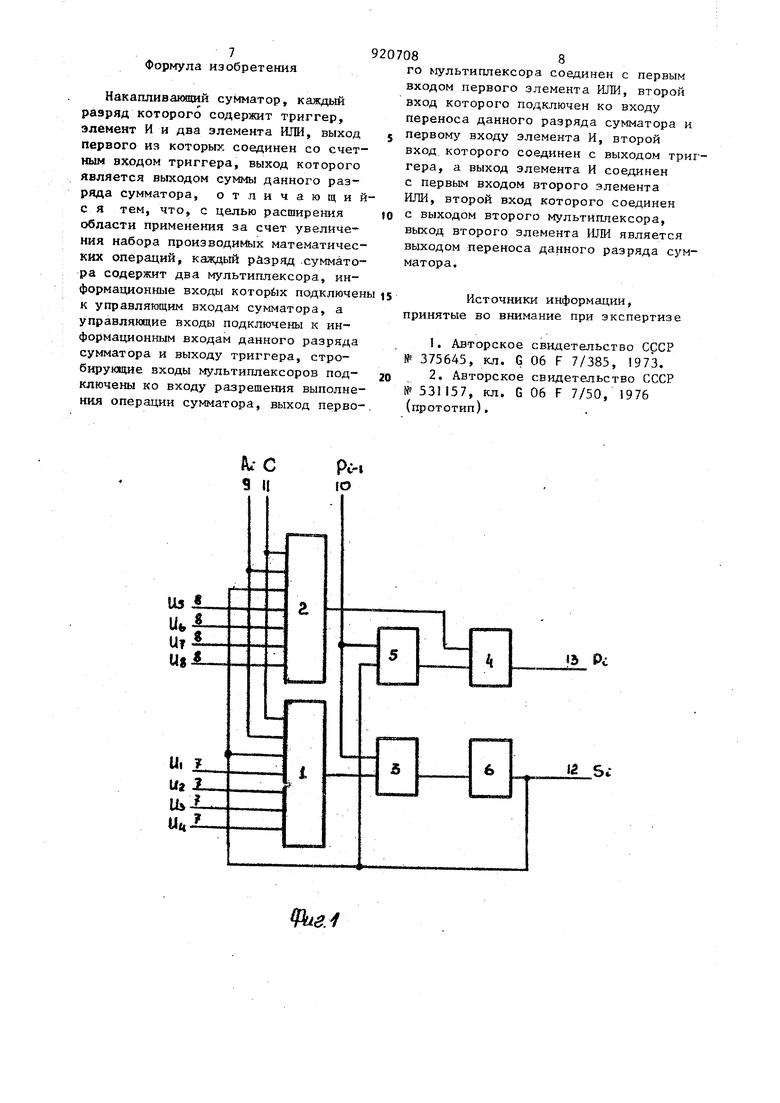

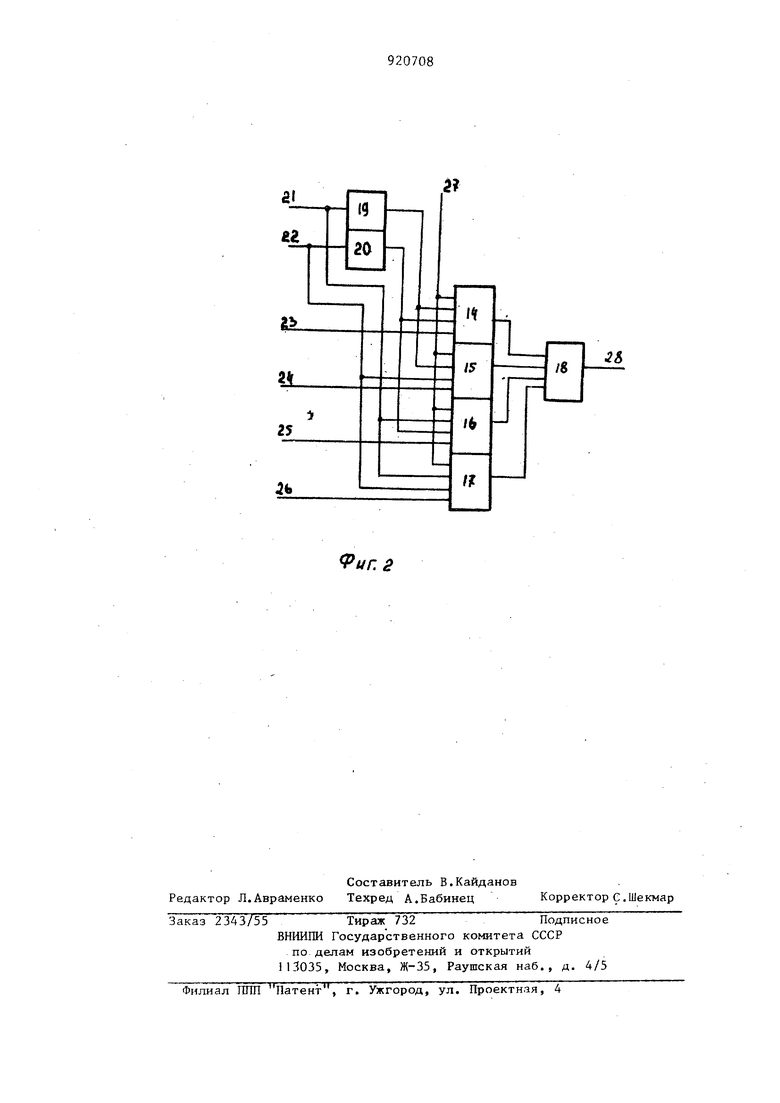

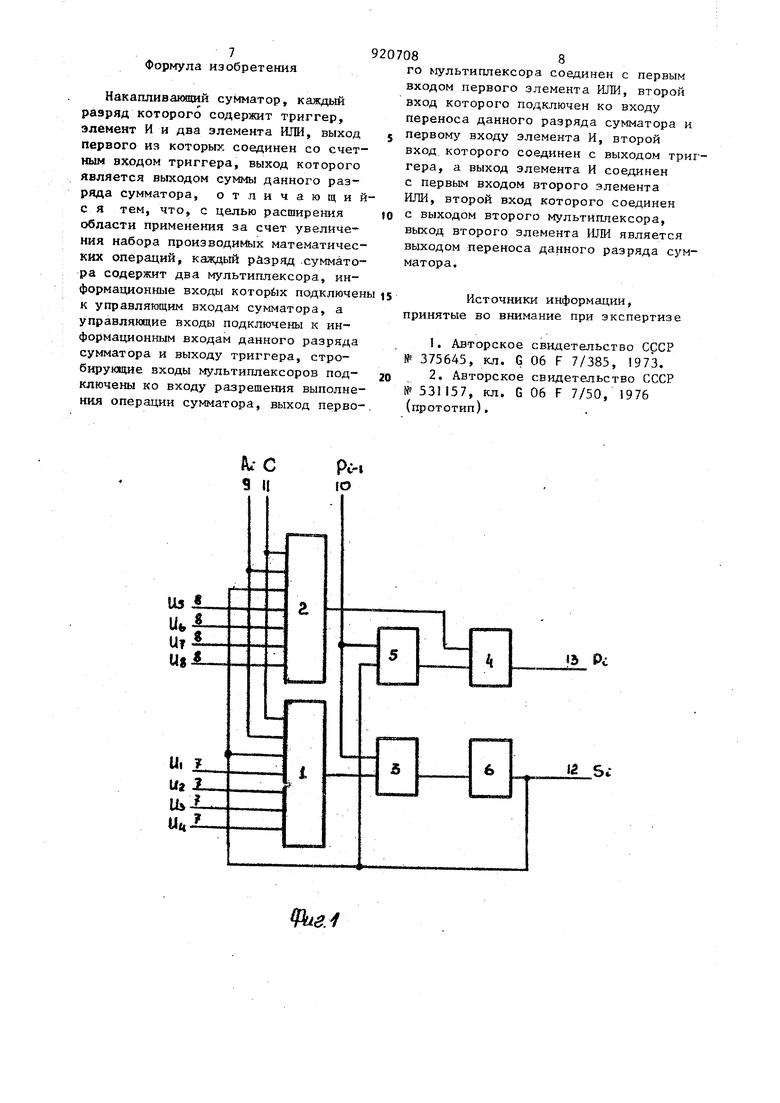

второму входу второго элемента И подключена шина разрешения вьщачи кода из приемного регистра, а выход его соединен с первым входом первого элемента ИЛИ, второй вход которбго соединен с выходом третьего элемента И, первый- вход которого подключен к выходу переноса из младшего разряда, а второй вход - к шине разрешения сложения, выход первого элемента ИЛИ подключен к счетному входу триггера накапливающего регистра, единичный выход которого подключен к первому выходу четвертого элемента И, ко второму входу которого подключена шина разрешения приема кода в приемный регистр из накапливающечг го регистра, а выход его подключен к единичному входу триггера приемного регистра, а нулевой выход триггера накапливающего регистра подключен к первому входу второго элемента ИЛИ, ко второму входу которого подключен выход переноса из младшего разряда, а выход соединен со рым входом первого элемента И, выход которого является выходом переноса из данного разряда. Этот сумматор наряду со сложением операндов реали зует логические операции конъюнкции и дизъюнкции операндов t2 , Недостатком такого сумматора также является ограниченный набор производимых математических операций (не реализует большинства логических операций двух операндов). Цель изобретения - расширерме области применения путем увеличения набора производимых в накапливающем сумматоре математических операци Поставленная цель достигается тем, что накапливающий сумматор, каж дый разряд которого содержит триггер элемент И и два элемента ИЛИ, выход первого из которых соединен со счетн входом триггера, выход которого явля ется выходом суммы данного разряда сумматора, каждый разряд сумматора содержит два мультиплексора, информа ционные входы которых подключены к управляющим входам сумматора, а управляклцие входы подключены к инфо13ма ционным входам данного разряда сумматора и выходу триггера, стробирую щие входы мультиплексоров подключега ко входу разрешения выполнения операции сумматора, выход первого мультиплексора соединен с первым входом первого элемента ИЛИ, второй вход которого подключен ко входу переноса данного разряда сумматора и пер вому входу элемента И, второй вход которого соединен с выходом триггера, а выход элемента И соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом второго мультиплексора, выход второго элемента ИЛИ является выходом переноса данного разряда сумматора. Схема такого сумматора помимо сл жения кодов двух двоичных чисел реализует все логические функции двух переменных над этими кодами, а такж выполняет математические операции, представляющие собой одновременную логическую обработку двух двоичных чисел со сложением результатов это обработки. Это расширяет набор математических операций, производимых устройством. 9 На фиг, представлена схема одного разряда накапливающего сумматора , на фиг. 2 - схема мультиплексора. Схема накапливающего сумматора (фиг. 1) содержит мультиплексоры I и 2f элементы ИЛИ 3 и 4, элемент И 5, триггер 6, управляющие входы 7 и 8, информационньш вход 9 и вход 10 переноса, вход П разрешения выполнения операции, выход 2 суммато,ра и выход 13 переноса. Схема мультиплексора (фиг. 2) содержит элементы И 14-17, ИЛИ 18, НЕ 19 и 20, управляющие входы 21 и 22, информационные входы 23-26, стробиругаций вход 27 и выход 28, В схеме накапливающего сумматора информационные входы мультигшексоров 1 и 2 подключены соответственно К группам управляюшлх входов 7 и 8 сумматора, а их управляющие входы попарно объединены и подключены соответственно к информационному входу 9 сумматора и к выходу триггера 6. Выход мультиплексора 1 соединен со входом элемента ИЛИ 3, выход которого соединен со счетным входом триггера 6, выход которого подключен к выходу 12 сумматора. Второй вход элемента ИЛИ 3 соединен со входом |10 переноса сумматора и со входом элемента И 5, второй вход которого сое,цинен с выходом триггера 6, а вы-ход элемента И 5 сое.яинен со входом элемента ИЛИ 4, выход которого является выходом переноса сумматора, а второй вход этого элемента соединен с выходом мультиплексора 2. Перед началом выполнения любой математической операции из набора реахшзуемых код одного из двух операндов А и В, участвующих, в операции, например код А, заносится в триггер 6, для.чего этот код подается на информационный вход 9, а мультиплексор 1 настраивается с помощью сигналов управления И;(-Иц, подаваемых на группу управляющих входов 7, на реализацию логической возбуждения триггера Aq У Aq, где о - сигнал снимаемый с выхода триггера 6. Под действием импульсного сигнала С, подаваемого на вход 11 .разрешения выполнения операции, на выходе мультиплексора I вырабатывается сигнал возбуждения триггера 6 и происходит запись в триггер 6 кода А. Длительность сигнала С выбирается из условия обеспечения устойчивой работы триггера 6 и ис.;лючения эффекта гонок. После записи триггер 6 числа А на информационны вход 9 поступает код второго опера да В. Настройка накапливаклцего сум матора на выполнение требуемой мат матической операции осуществляется с помощью сигналов управления этом, если реализуемая операци является только логической, то сиг налы управления Ид-И мультиплексор 2 равны нулю. В этом случае выходно сигнал переноса Р , не формируется. Для выполнения некоторой произволь математической операции из набора р ализуемых код настройки устройства легко находится по таблице истиннос ти этой операции. Рассмотрим пример реализации опе ции (АЧВ) таблица истинности которой .имеет вид Здесь входной сигнал перено са, подаваемый на вход 10, Si, - сиг нал результата операции, совпадающий с содержимым триггера 6 после вы полнения операции. Для перевода триггера из состояния начального, например, соответств кщего коду в, в конечное состояние Si необходимо выработать сигнал возбуждения триггера - сигнал Ф( Логическую функцию сигнала возбуждения Ф| легко найти по таблице истинности операции с учетом того, что триггер по счетному входу реализует логическую опера цию сложения по модулю два 708 Для настройки устройства на реа .лизацию заданной операции () необходимо подать коды и ,01, представляющие собой значе- ния сигналов Ф и Р1 таблицы при Р., в качестве сигналов управления соответственно ц и Ид-И на входы мультиплексоров 7 и 8. После подачи на вход )I разрешения выполнения операции импульсного сигнала С мультиплексором 2 вьфабатывается сигнал переноса PJ, а мультиплексором 1 - сигнал возбуждения триггера, Для выполнения условий отсутствия гонок и исполнения сигналов Ф; PL-I друг на друга следует задержку элемента ИЛИ 4 увеличить по отнсчаению к задержке элемента ИЛИ 3. В результате Настройки мультиплексоров I и 2 на реализацию в них различнь х логических функций переменных А и В возможно выполнение в сумматоре до 256 различных математических операций типа (А, B)+fj(А, В), где fi((A, В) и fj(А, В) - произвольные логические функции переменных А и В. Расширение набора математических операций, производимых сумматором, позволяет повьппать быстродействие устройств обработки двоичной информации, и 1полненных на основе данного накапливакяцего сумматора, за счет увеличения сложности вычислений, производимых в каждом такте работы этих устройств. Например, для выполнения операции S(AvB) + (AtO) в известном устройстве требуется последовательно выполнить три операции; и Выполнение же этой ©перации в данном устройстве производится за один,такт, Кроме того, расширение набора математических операций позволяет сократить номенклатуру устройств, реализующих операции, относящиеся к операциям типа fl(А, B)+fj(А, B) заменив их одним данным устройством. Экономичнее кий эффект от применения данного сумматора получается за счет возможного сокращения номенклатуры накапливающих сумматоров, применяемых при построении устройств обработки информации, а также за счет повьпаения производительности средств обработки вследствие расширения набора реализуемых математических операций.

Формула изобретения

Накапливакхций сумматор, каждый разряд которого содержит триггер, элемент И и два элемента ИЛИ, выход первого из которых соединен со счетшом входом триггера, выход которого является выходом суммы данного разряда сумматора, отличающийс я тем, что, с целью расширения области применения за счет увеличе ния набора производимых математических операций, каждый разряд .сумматора содержит два мультиплексора, информационные входы KOToptix подключен к управляющим входам сумматора, а управляющие входы подключены к информационным входам данного разряда сумматора и выходу триггера, стробирующие входы мультиплексоров подключены ко входу разрешения выполнения операции сумматора, выход первоfPue l

го :yльтиплeкcopa соединен с первым входом первого злемента ИЛИ, второй вход которого подключен ко входу переноса данного разряда сумматора и первому входу элемента И, второй вход которого соединен с выходом тригера, а выход элемента И соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом второго мультиплексора, выход второго элемента ИЛИ является выходом переноса данного разряда сумматора.

Источники информации, принятые во внимание при экспертизе

21

иг.2

Авторы

Даты

1982-04-15—Публикация

1979-12-17—Подача