1

(21)4341043/24-24

(22)10.12.87

(46) 30.07.89. Бюл. № 28 (72) В.В. Кацман

(53)681.325(088.8)

(56) Brandes М. Ubertragung vol PCM Signalen auf simmetrichen Kabeln mit binaren Letungsignalen. Fernemelde- technik, 198J, № 6, S. 214-218.

Авторское свидетельство СССР № 1339894, кл. И 03 М 5/14, 1985.

(54)ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО

( 57) Изобретение относится к вычислительной технике и технике связи. Его использование в волоконно-оптических системах передачи информации, а также измерителях коэффициента ошибок позволяет повысить достоверность

декодирования. Это достигается благодаря снижению частоты синхронизации с 0,6 до 0,5F и увеличению минимального интервала при перезаписи информации. Устройство обеспечивает декодирование кода 5ВбВ и измерение коэффициента ошибок в этом коде. Устройство содержит входной блок I, селекторы 2,3 импульсов, регистр 4 сдвига, первый - третий буферные регистры 5-7, блок 8 памяти, делитель 9 частоты на три, делитель 10 частоты на .. два, блок II управления, блок 12 мультиплексирования, селектор 13 тактовой частоты, элемент 14 задержки, блок 15 анализа ошибок, вход 16, информационный 17 и тактовый 18 выходы. 4 3.п. ф-лы, II ил.

§

сл

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодирующее устройство | 1985 |

|

SU1339894A1 |

| Анализатор кодовых последовательностей импульсов (его варианты) | 1984 |

|

SU1238243A1 |

| Кодирующее устройство | 1987 |

|

SU1510093A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1476533A1 |

| Декодирующее устройство | 1984 |

|

SU1290532A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2043660C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Анализатор кодовых последовательностей импульсов | 1985 |

|

SU1305868A2 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Генератор кодовых последовательностей импульсов | 1987 |

|

SU1531080A1 |

Изобретение относится к вычислительной технике и технике связи. Его использование в волоконно-оптических системах передачи информации, а также измерителях коэффициента ошибок позволяет повысить достоверность декодирования. Это достигается благодаря снижению частоты синхронизации с 0,6 до 0,5 F и увеличению минимального интервала при перезаписи информации. Устройство обеспечивает декодирование кода 5В6В и измерение коэффициента ошибок в этом коде. Устройство содержит входной блок 1, селекторы 2,3 импульсов, регистр 4 сдвига, первый-третий буферные регистры 5-7, блок 8 памяти, делитель 9 частоты на три, делитель 10 частоты на два, блок 11 управления, блок 12 мультиплексирования, селектор 13 тактовой частоты, элемент 14 задержки, блок 15 анализа ошибок, вход 16, информационный 17 и тактовый 18 выходы. 4 з.п.ф-лы, 11 ил.

со -vi

4

СП

31497

MnoftpfjTt HHr t)TnncnTCH к иычиспи- тельноГ технике и технике снячи и может быть использовано п яолоконно-оп- тических системах передачи ииформа- ции, а также в измерителях коэ(х))и- циента ошибок.

Цель изобретения - повышение достоверности декодирования.

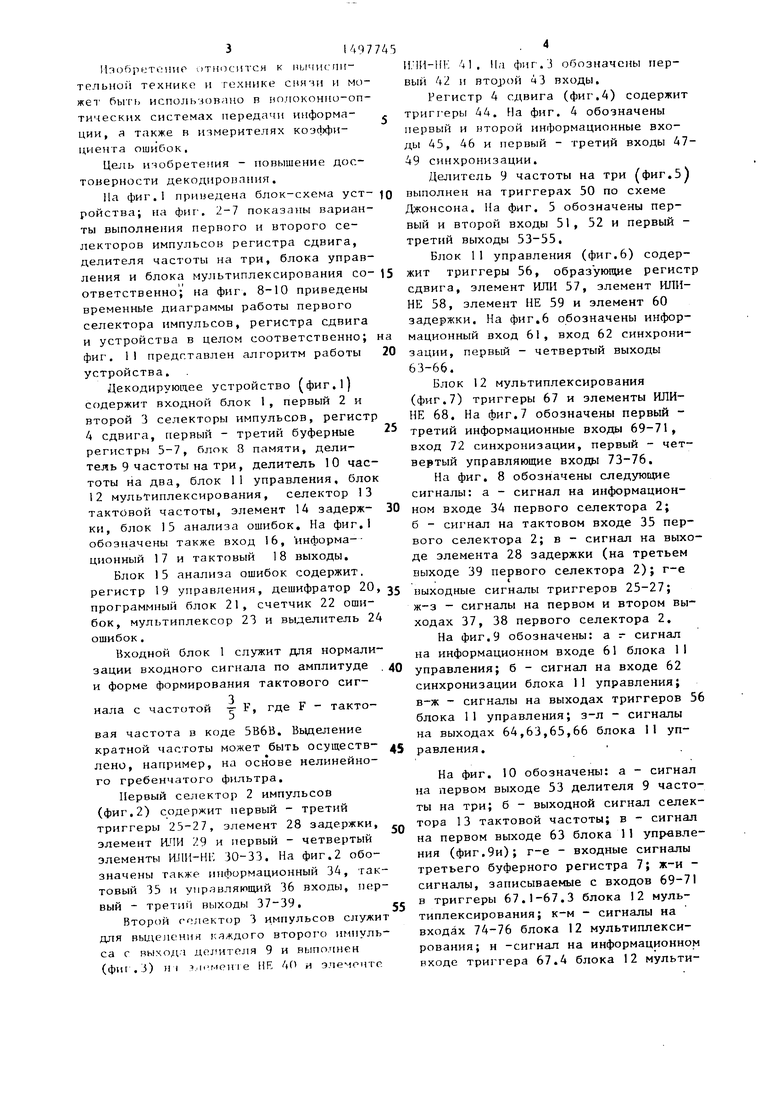

На фиг.1 приведена блок-схема уст- ройства; на фиг, 2-7 показаны варианты выполнения первого и второго селекторов импульсов регистра сдвига, делителя частоты на три, блока управления и блока мультиплексирования со- ответственно; на фиг. 8-10 приведены временнь1е диаграммы работы первого селектора импульсов, регистра сдвига и устройства в целом соответственно; фиг. 11 представлен алгоритм работы устройства.

Декодирующее устройство (фиг.1) содержит входной блок 1, первый 2 и второй 3 селекторы импульсов, регистр 4 сдвига, первый - третий буферные регистры 5-7, блок 8 памяти, делитель 9 частоты на три , делитель 10 частоты на два, блок 11 управления, блок 12 мультиплексирования, селектор 13 тактовой частоты, элемент 14 задерж- ки, блок 15 анализа ошибок. На фиг,1 обозначены также вход 16, информа- ционный 17 и тактовый 18 выходы.

Блок 15 анализа ошибок содержит, регистр 19 управления, дешифратор 20 программный блок 21, счетчик 22 ошибок, мультиплексор 23 и выделитель 24 ошибок.

Входной блок 1 служит для нормализации входного сигнала по амплитуде и форме формирования тактового сигнала с частотой -г F, где F - тактовая частота в коде 5ВбВ, Выделение кратной частоты может быть осуществ- лоно, например, на основе нелинейного гребенчатого фильтра.

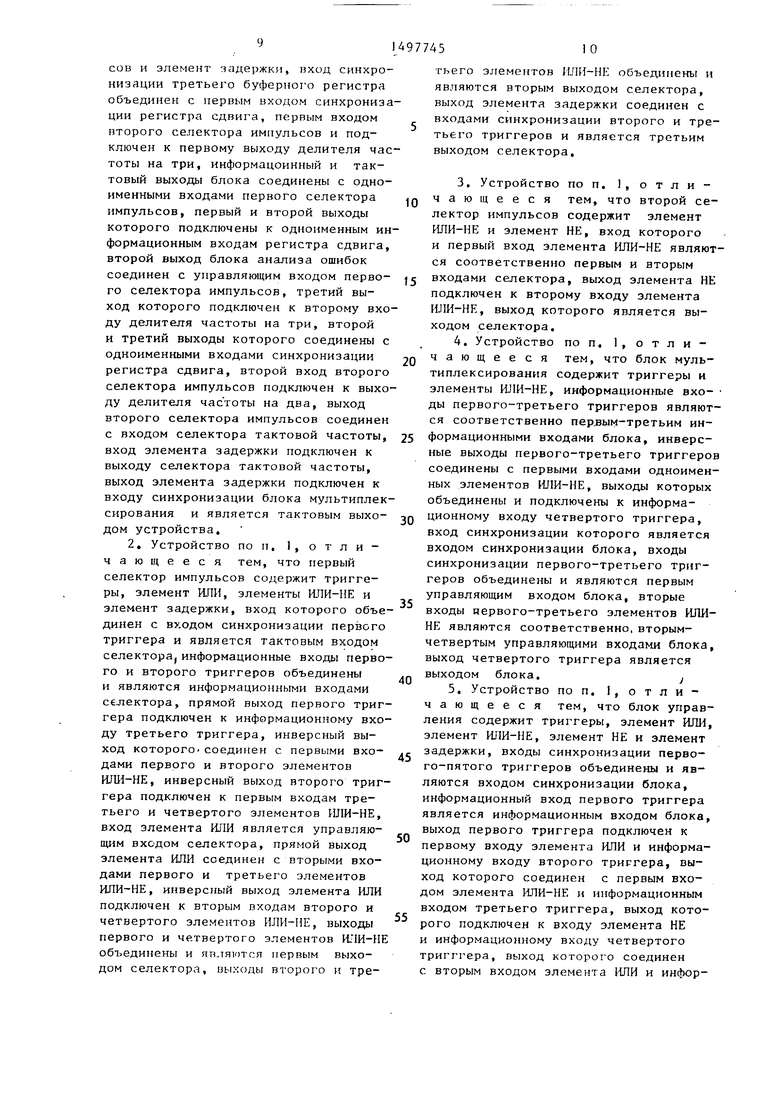

Первый селектор 2 импульсов (фиг.2) содержит первый - третий триггеры 25-27, элемент 28 задержки, элемент ИЛИ 29 и первый - четвертый элементы И.ПИ-НГ, 30-33. На фиг.2 обозначены также информационный 34, тактовый 33 и управляющий 36 входы, первый - третий выходы 37-39.

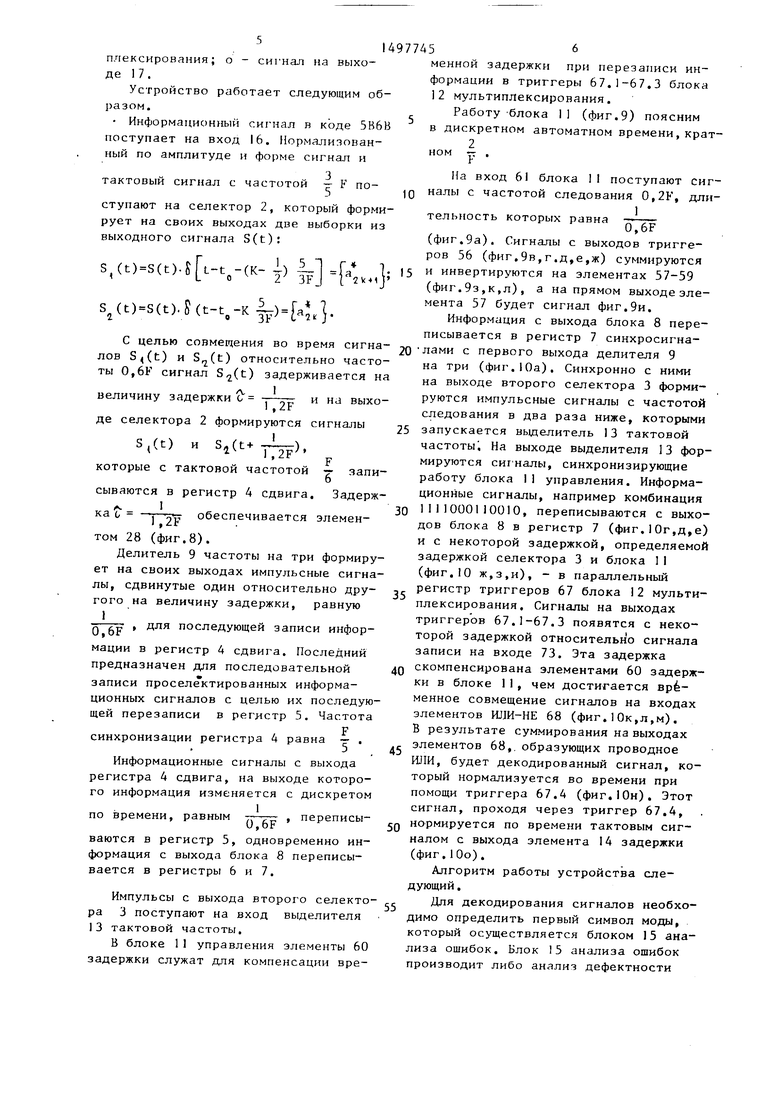

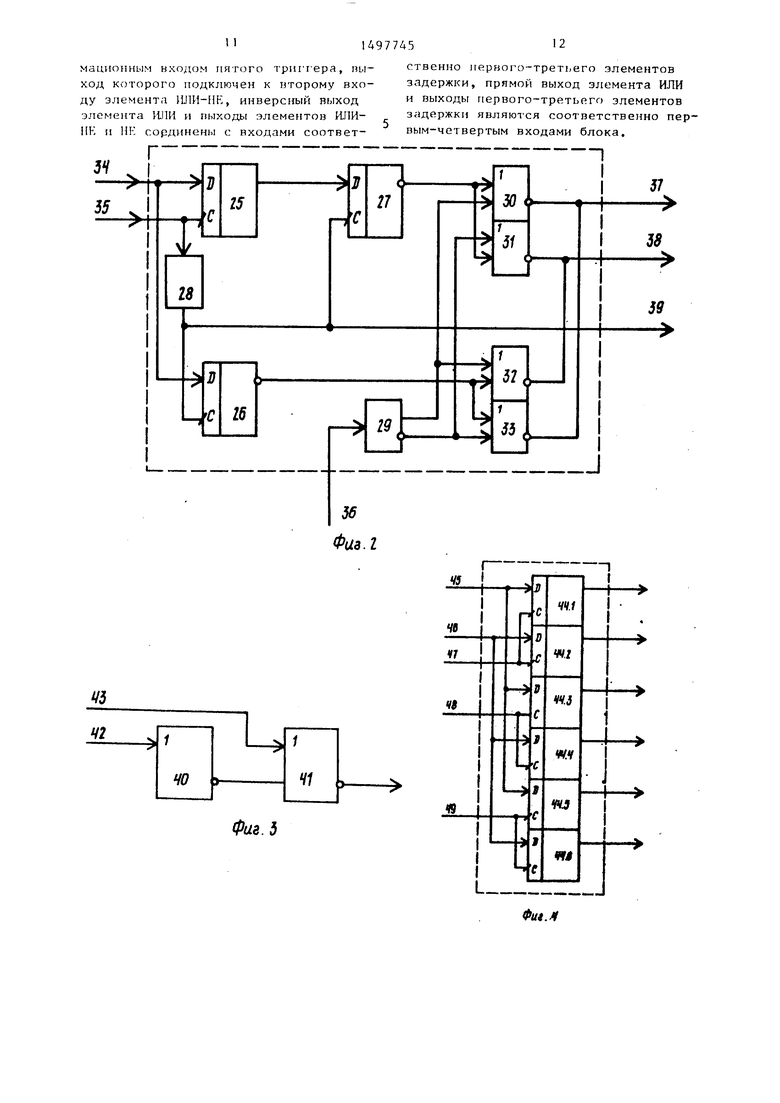

Второй с-олектор 3 импульсов служи для выделения каждого второго имнуль са с выхода делителя 9 и выполнен (фиг .3) HI з. И меше НЕ 40 и элемочте

ИЛИ-И 41, На фиг.З обозначены первый 42 и втор(п1 43 входы.

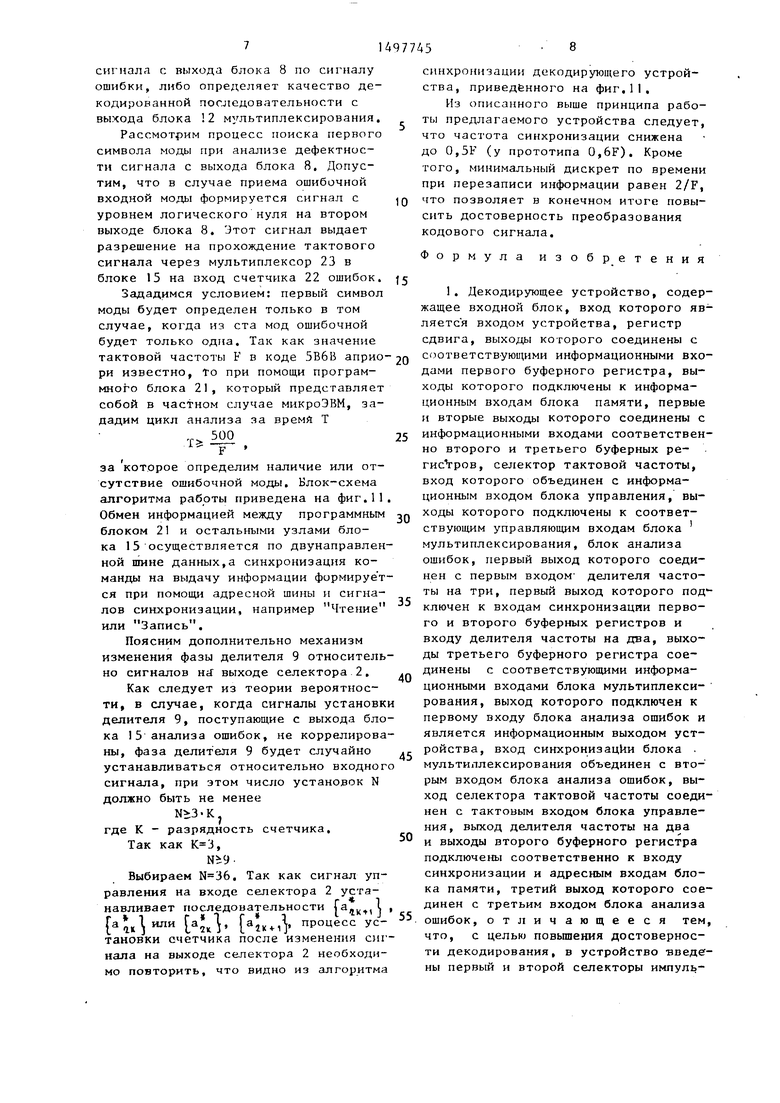

Регистр 4 сдвига (фиг.4) содержит триггеры 44. На фиг. 4 обозначены первый и второй информационные входы 45, 46 и первый - третий входы 47- 49 синхронизации.

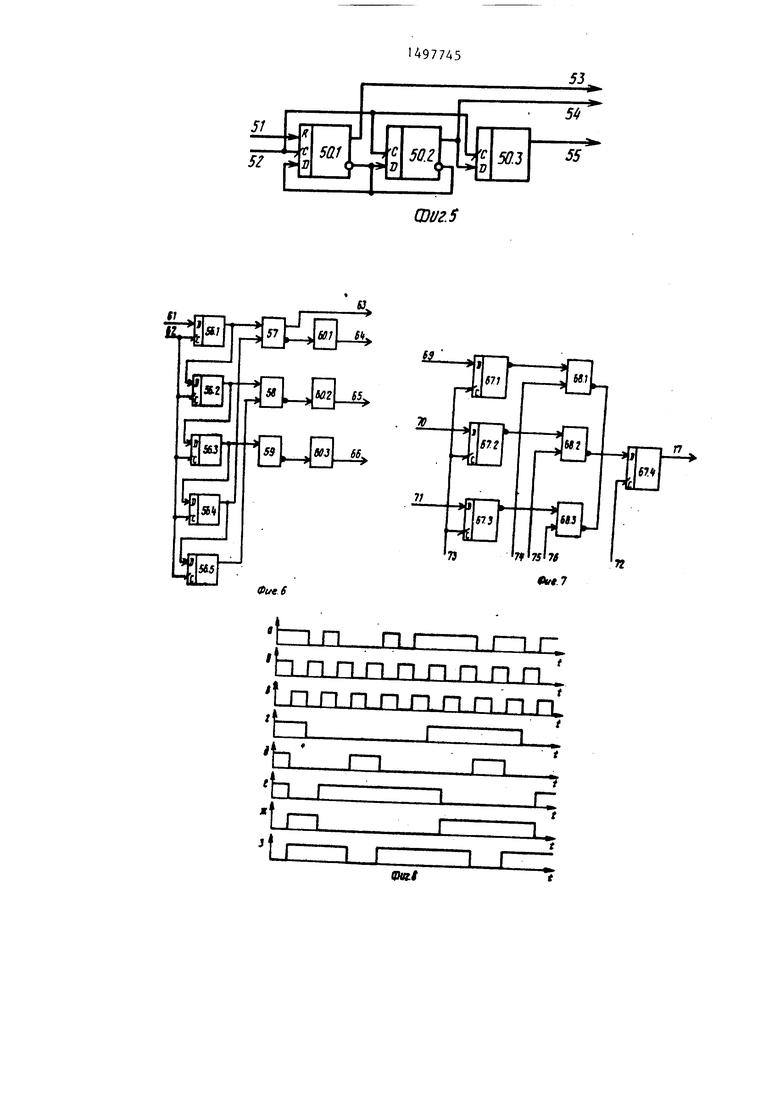

Делитель 9 частоты на три (фиг,5) выполнен на триггерах 50 по схеме Джонсона. На фиг. 5 обозначены первый и второй входы 51, 52 и первый - третий выходы 53-55.

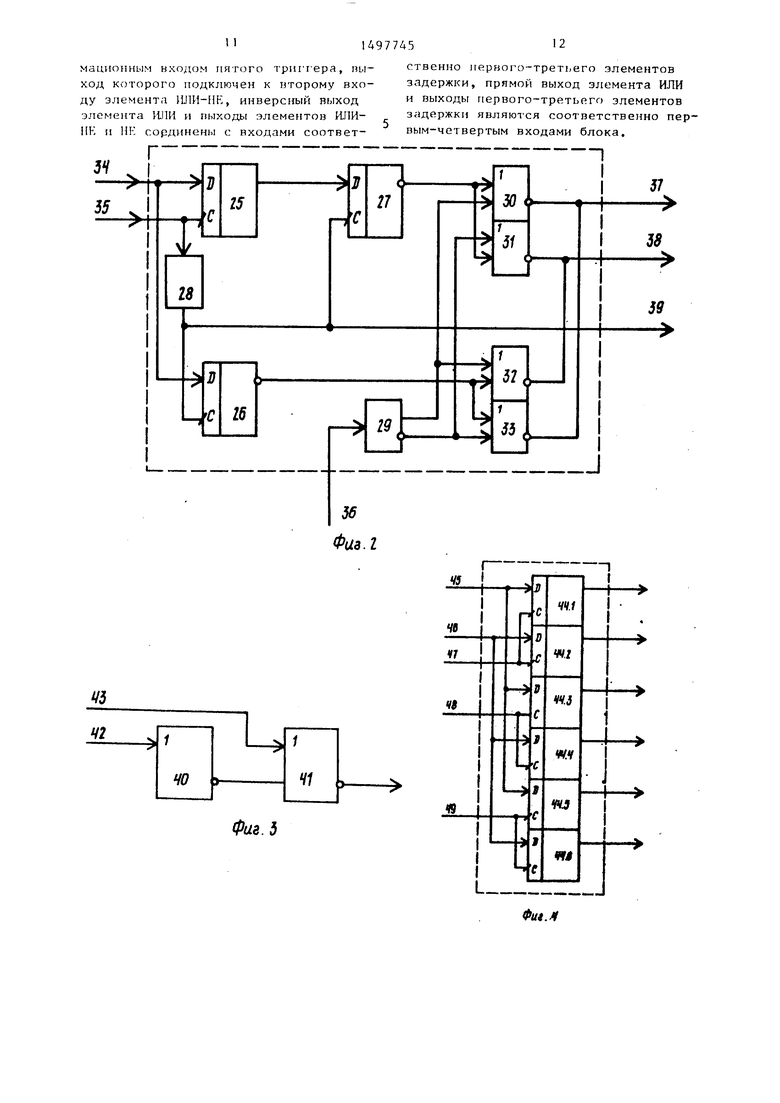

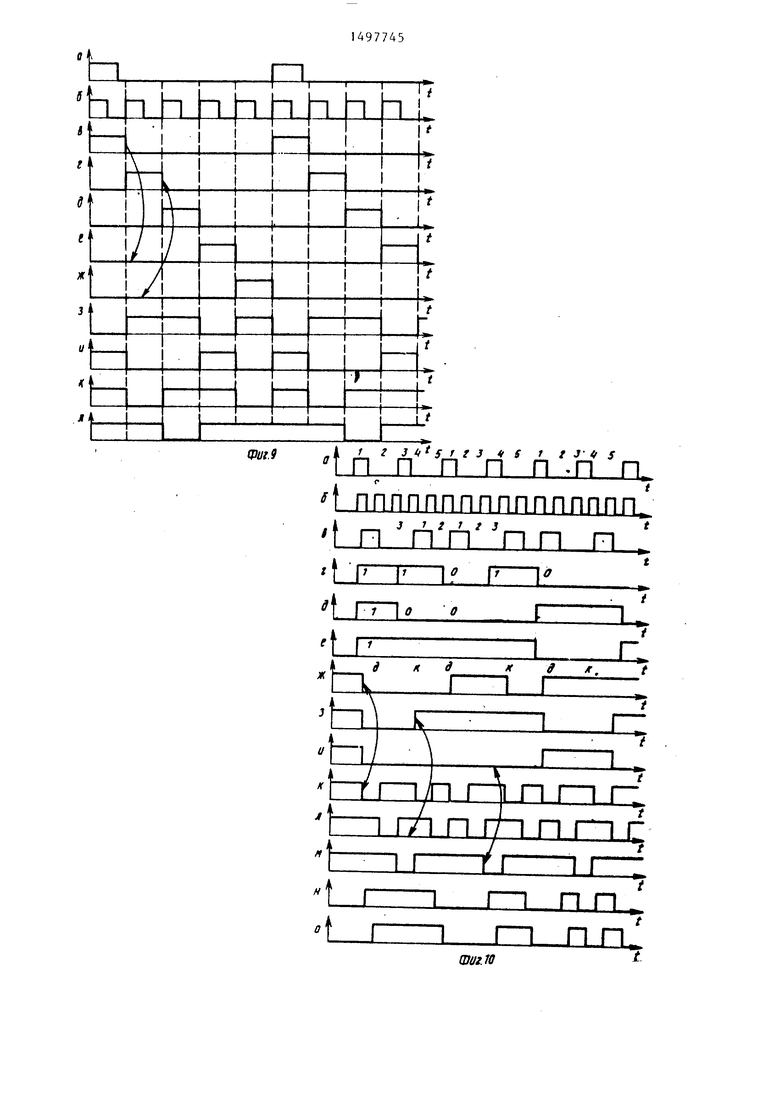

Блок 11 управления (фиг.6) содержит триггеры 56, образующие регистр сдвига, элемент ИЛИ 57, элемент ИЛИ- НЕ 58, элемент НЕ 59 и элемент 60 задержки. На фиг,6 обозначены информационный вход 61, вход 62 синхронизации, первый - четвертый выходы 63-66.

Блок 12 мультиплексирования (фиг.7) триггеры 67 и элементы ИЛИ- НЕ 68. На фиг.7 обозначены первый - третий информационные входы 69-71, вход 72 синхронизации, первый - четвертый управляющие входы 73-76.

На фиг, 8 обозначены следующие сигналы: а - сигнал на информационном входе 34 первого селектора 2; б - сигнал на тактовом входе 35 первого селектора 2; в - сигнал на выходе элемента 28 задержки (на третьем выходе 39 первого селектора 2); г-е выходные сигналы триггеров 25-27; ж-з - сигналы на первом и втором выходах 37, 38 первого селектора 2,

На фиг.9 обозначены; а г сигнал на информационном входе 61 блока II управления; б - сигнал на входе 62 синхронизации блока 11 управления; в-ж - сигналы на выходах триггеров 56 блока 11 управления; з-л - сигналы на выходах 64,63,65,66 блока 11 управления.

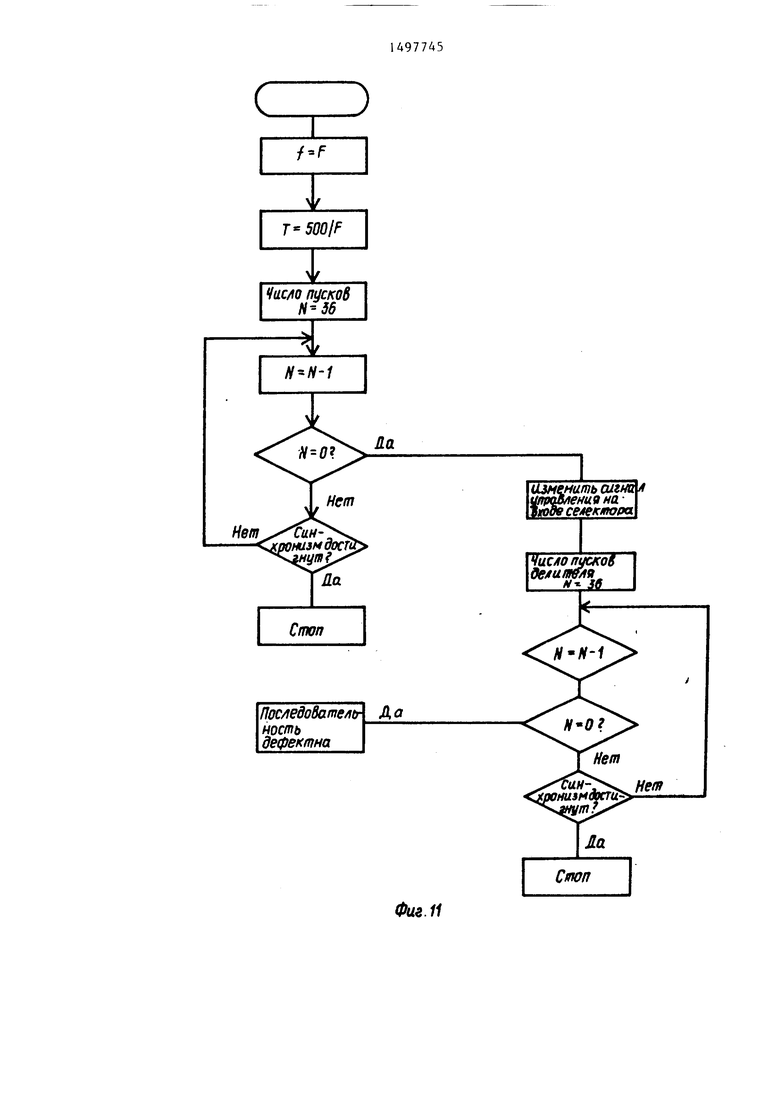

На фиг. 10 обозначены: а - сигнал на первом выходе 53 делителя 9 частоты на три; б - выходной сигнал селектора 13 тактовой частоты; в - сигнал на первом выходе 63 блока П управления (фиг.9и); г-е - входные сигналы третьего буферного регистра 7; ж-и - сигналы, записываемые с входов 69-71 в триггеры 67,1-67,3 блока 12 мультиплексирования; к-м - сигналы на входах 74-76 блока 12 мультиплексирования; н -сигнал на информационном входе триггера 67,4 блока 12 мультиплексирования; о - сигнал на выхо- де 17.

Устройство работает следующим образом.

Информационный сигнал в коде 5В6В поступает на вход 16. Нормализованный по амплитуде и форме сигнал и

тактовый сигнал с частотой

- F поступают на селектор 2, который формирует на своих выходах две выборки из выходного сигнала S(t):

S,(t)S(t).(K-i) у a;,j; 15 SJt)S(t).S(t-t,-K|5,) fa;,.

cQ

С целью совмещения во время сигналов S(t) и S(t) относительно частоты 0,6F сигнал ) задерживается на

величину задержки о

1

1,2F

и на выходе селектора 2 формируются сигналы

I .

которые с тактовой частотой

7- запи- о

ка (

обеспечивается элеменсываются в регистр 4 сдвига, ЗадержI

1,2F том 28 (фиг.8).

Делитель 9 частоты на три формирует на своих выходах импульсные сигналы, сдвинутые один относительно другого на величину задержки, равную

л ,р, , для последующей записи информации в регистр 4 сдвига. Последний предназначен для последовательной записи проселё ктированных информационных сигналов с целью их последующей перезаписи в регистр 5. Частота

F синхронизации регистра 4 равна - .

Информационные сигналы с выхода регистра 4 сдвига, на выходе которого информация изменяется с дискретом

JI

0,6F

ваются в регистр 5, одновременно информация с выхода блока 8 переписывается в регистры 6 и 7.

по времени, равным

переписыИмпульсы с выхода второго селекто- ра 3 поступают на вход выделителя 13 тактовой частоты.

В блоке 11 управления элементы 60 задержки служат для компенсации вре5

0

5

-

менной задержки при перезаписи информации в триггеры 67.1-67.3 блока 12 мультиплексирования.

Работу блока И (фиг.9) поясним в дискретном автоматном времени,крат2ном .

На вход 61 блока 11 поступают сиг- 0 налы с частотой следования 0,2F, дли1

тельность которых равна -

и, or

(фиг.9а). Сигналы с выходов триггеров 56 (фиг.9в,г.д,е,ж) суммируются и инвертируются на элементах 57-59 (фиг.9з,к,л), а на прямом выходе элемента 57 будет сигнал фиг.9и.

Информация с выхода блока 8 переписывается в регистр 7 синхросигна- лами с первого выхода делителя 9 на три (фиг.Юа). Синхронно с ними на выходе второго селектора 3 формируются импульсные сигналы с частотой следования в два раза ниже, которыми запускается вьщелитель 13 тактовой частоты . На выходе выделителя 13 формируются сигналы, синхронизирующие работу блока II управления. Информационные сигналы, например комбинация 1II1000110010, переписываются с выходов блока 8 в регистр 7 (фиг.1Ог,д,е) и с некоторой задержкой, определяемой задержкой селектора 3 и блока II (фиг,10 ж,з,и), - в параллельный регистр триггеров 67 блока 12 мультиплексирования. Сигналы на выходах триггеров 67.1-67.3 появятся с некоторой задержкой относительн о сигнала записи на входе 73. Эта задержка скомпенсирована элементами 60 задержки в блоке 11, чем достигается временное совмещение сигналов на входах элементов ШШ-НЕ 68 (фиг. 10к,л ,м) . В результате суммирования на выходах элементов 68,, образующих проводное ИЛИ, будет декодированный сигнал, который нормализуется во времени при помощи триггера 67.4 (фиг.Юн). Этот сигнал, проходя через триггер 67,4, Q нормируется по времени тактовым сигналом с выхода элемента 14 задержки (фиг.1Оо).

Алгоритм работы устройства следующий .

Для декодирования сигналов необходимо определить первый символ моды, который осуществляется блоком 15 Анализа ошибок. Блок 15 анализа ошибок производит либо анализ дефектности

0

5

0

5

сигнала с выхода блока 8 по сигналу ошибки, либо определяет качество декодированной последовательности с выхода блока 2 мультиплексирования.

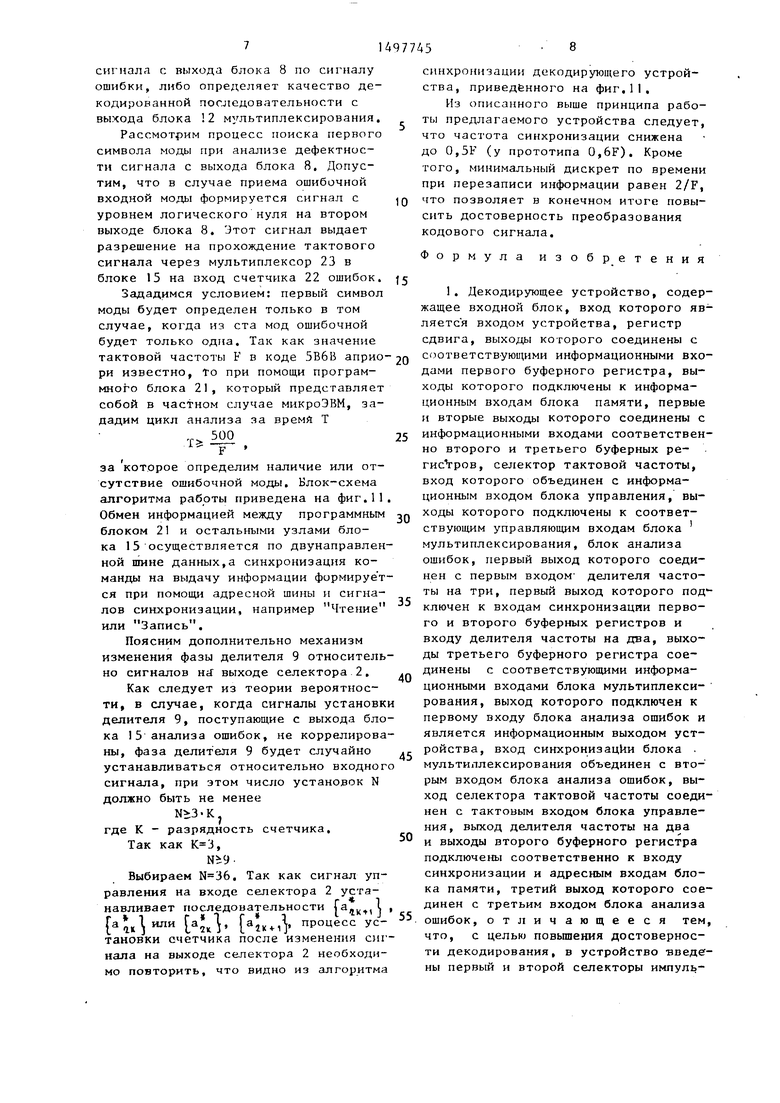

Рассмотрим процесс поиска первого символа моды при анализе дефектности сигнала с выхода блока 8, Допустим, что в случае приема ошибочной входной моды формируется сигнал с уровнем логического нуля на втором выходе блока 8. Этот сигнал выдает разрешение на прохождение тактового сигнала через мультиплексор 23 в блоке 15 на вход счетчика 22 ошибок.

Зададимся условием: первый символ моды будет определен только в том случае, когда из ста мод ошибочной будет только одна. Так как значение

тактовой частоты F в коде 5В6В априо-2о соответствующими информационными входами первого буферного регистра, выходы которого подключены к информационным входам блока памяти, первые и вторые выходы которого соединены с информационными входами соответственно второго и третьего буферных регистров, селектор тактовой частоты, вход которого объединен с информационным входом блока управления, выходы которого подключены к соответствующим управляющим входам блока мультиплексирования, блок анализа ошибок, первый выход которого соединен с первым ВХОДОМ делителя частоты на три, первый выход которого под25

30

например Чтение ключен к входам синхронизации первори известно, то при помощи программного блока 21, который представляет собой в частном случае микроЭВМ, зададим цикл анализа за времй Т

т 500

J. F .

за которое определим наличие или отсутствие ошибочной моды. Блок-схема алгоритма работы приведена на фиг. П. Обмен информацией между программным блоком 21 и остальными узлами блока 15 осуществляется по двунаправленной шине данных,а синхронизация команды на выдачу информации формируе т- ся при помощи адресной шины и сигналов синхронизации, или Запись.

Поясним дополнительно механизм изменения фазы делителя 9 относительно сигналов Htf выходе селектора 2.

Как следует из теории вероятности, в случае, когда сигналы установки делителя 9, поступающие с выхода блока 15 анализа ошибок, не коррелирова- ны, фаза делителя 9 будет случайно .с устанавливаться относительно входного сигнала, при этом число установок N должно быть не менее

Ni3-Kj где К - разрядность счетчика.

Так как ,

Nb9.

Выбираем . Так как сигнал управления на входе селектора 2 устанавливает последовательности , а, aj,,. процесс установки счетчика после изменения сигнала на выходе селектора 2 необходимо повторить, что видно из алгоритма

дами первого буферного регистра, выходы которого подключены к информационным входам блока памяти, первые и вторые выходы которого соединены с информационными входами соответственно второго и третьего буферных регистров, селектор тактовой частоты, вход которого объединен с информационным входом блока управления, выходы которого подключены к соответствующим управляющим входам блока мультиплексирования, блок анализа ошибок, первый выход которого соединен с первым ВХОДОМ делителя частоты на три, первый выход которого под40

50

го и второго буферных регистров и входу делителя частоты на два, выходы третьего буферного регистра соединены с соответствующими информационными входами блока мультиплексирования, выход которого подключен к первому входу блока анализа ошибок и является информационным выходом устройства, вход синхронизации блока . мультиплексирования объединен с вто- рым входом блока анализа ошибок, выход селектора тактовой частоты соединен с тактовым входом блока управления, выход делителя частоты на два и выходы второго буферного регистра подключены соответственно к входу синхронизации и адресным входам блока памяти, третий выход которого соединен с третьим входом блока анализа ошибок, отличающееся тем, что, с целью повьппения достоверности декодирования, в устройство -введены первый и второй селекторы импуль

синхронизации декодирующего устройства, приведённого на фиг.1I.

Из описанного выше принципа работы предлагаемого устройства следует, что частота синхронизации снижена до 0,5F (у прототипа 0,6F). Кроме того, минимальный дискрет по времени при перезаписи информации равен 2/F, что позволяет в конечном итоге повысить достоверность преобразования кодового сигнала.

Формула изобретения

соответствующими информационными вхо

дами первого буферного регистра, выходы которого подключены к информационным входам блока памяти, первые и вторые выходы которого соединены с информационными входами соответственно второго и третьего буферных регистров, селектор тактовой частоты, вход которого объединен с информационным входом блока управления, выходы которого подключены к соответствующим управляющим входам блока мультиплексирования, блок анализа ошибок, первый выход которого соединен с первым ВХОДОМ делителя частоты на три, первый выход которого подс

0

0

го и второго буферных регистров и входу делителя частоты на два, выходы третьего буферного регистра соединены с соответствующими информационными входами блока мультиплексирования, выход которого подключен к первому входу блока анализа ошибок и является информационным выходом устройства, вход синхронизации блока . мультиплексирования объединен с вто- рым входом блока анализа ошибок, выход селектора тактовой частоты соединен с тактовым входом блока управления, выход делителя частоты на два и выходы второго буферного регистра подключены соответственно к входу синхронизации и адресным входам блока памяти, третий выход которого соединен с третьим входом блока анализа ошибок, отличающееся тем, что, с целью повьппения достоверности декодирования, в устройство -введены первый и второй селекторы импульсов и элемент задержки, вход синхронизации третьего буфериого регистра объединен с первым входом синхронизации регистра сдвига, первым входом второго селектора имнульсов и подключен к первому выходу делителя частоты на три, информацоинный и тактовый выходы блока соединены с одноименными входами первого селектора импульсов, первый и второй выходы которого подключены к одноименным информационным входам регистра сдвига, второй выход блока анализа ошибок соединен с управляющим входом первого селектора импульсов, третий выход которого подключен к второму входу делителя частоты на три, второй и третий выходы которого соединены с одноименными входами синхронизации регистра сдвига, второй вход второго селектора импульсов подключен к выходу делителя час тоты на два, выход второго селектора импульсов соединен с входом селектора тактовой частоты, вход элемента задержки подключен к выходу селектора тактовой частоты, выход элемента задержки подключен к входу синхронизации блока мультиплексирования и является тактовым выходом устройства.

2, Устройство по п. I, о т л и - чающееся тем, что первый селектор импульсов содержит триггеры, элемент ИЛИ, элементы ИЛИ-НЕ и элемент задержки, вход которого объединен с входом синхронизации nepijoro триггера и является тактовым входом селектора информационные входы первого и второго триггеров объединены и являются информационными входами селектора, прямой выход первого триггера подключен к информационному входу третьего триггера, инверсный выход которого-соединен с первыми входами первого и второго элементов ИЛИ-НЕ, инверсный выход второго триггера подключен к первым входам третьего и четвертого элементов ИЛИ-НЕ, вход элемента ИЛИ является управляющим входом селектора, прямой выход элемента ИЛИ соединен с вторыми входами первого и третьего элементов ИЛИ-НЕ, инверсный выход элемента ИЛИ подключен к вторым входам второго и четвертого элементов ИЛИ-НЕ, выходы первого и четвертого элементов ИЛИ-FIE объединены и япляются первым выходом селектора, ццходы второго и тре0

5

0

5

0

5

0

5

0

5

тьего элементов ЛЛИ-НЕ объединены и являются вторым выходом селектора, выход элемента задержки соединен с входами синхронизации второго и третьего триггеров и является третьим выходом селектора.

и первый вход элемента ИЛИ-НЕ являются соответственно первым и вторым входами селектора, выход элемента НЕ подключен к второму входу элемента ИЛИ-НК, выход которого является выходом селектора.

и информационному входу четвертого тригггера, выход которо1-о соединен с вторым входом элемента ИЛИ и информационным входом пятого тршт ера, пы ход которого подключен к нторому входу элемента HJIH-HE, инверсный выход элемента Ш1И и пыходы элементов ИЛИ- ПК II ПК сординены с входами соответ- вым-четвертым входами блока.

ственно первого-третьего эле задержки, прямой выход элеме и выходы первого-третьего эл задержки являются соответств

56

Фаз. г

Фав.Ь

вым-четвертым входами блока.

ственно первого-третьего элементов задержки, прямой выход элемента ИЛИ и выходы первого-третьего элементов задержки являются соответственно пер1

51

Фие.в

Шиг.5

lA f

73

«W«7

ФйЕ/

;

e

ж

/r л

t

1 г 3 iif 5 f f 3 5 1 t J if S

П П П П П .П П

П n

С )

Т 500 IF

ЧасАО пусков Н-56

изменить о/г/дг дтсЛления на У(Юв селектора

Число т/сков

.

ЧНк.11

Авторы

Даты

1989-07-30—Публикация

1987-12-10—Подача