g

(Л

i Изобре гение относится к автомати- |се, вычислительной технике и технике |:вязи и может быть .использовано в {цифровых системах передачи (напри- мер, волоконно-оптических)о

Цель изобретения - повьшение быстродействия и упрощение устройства

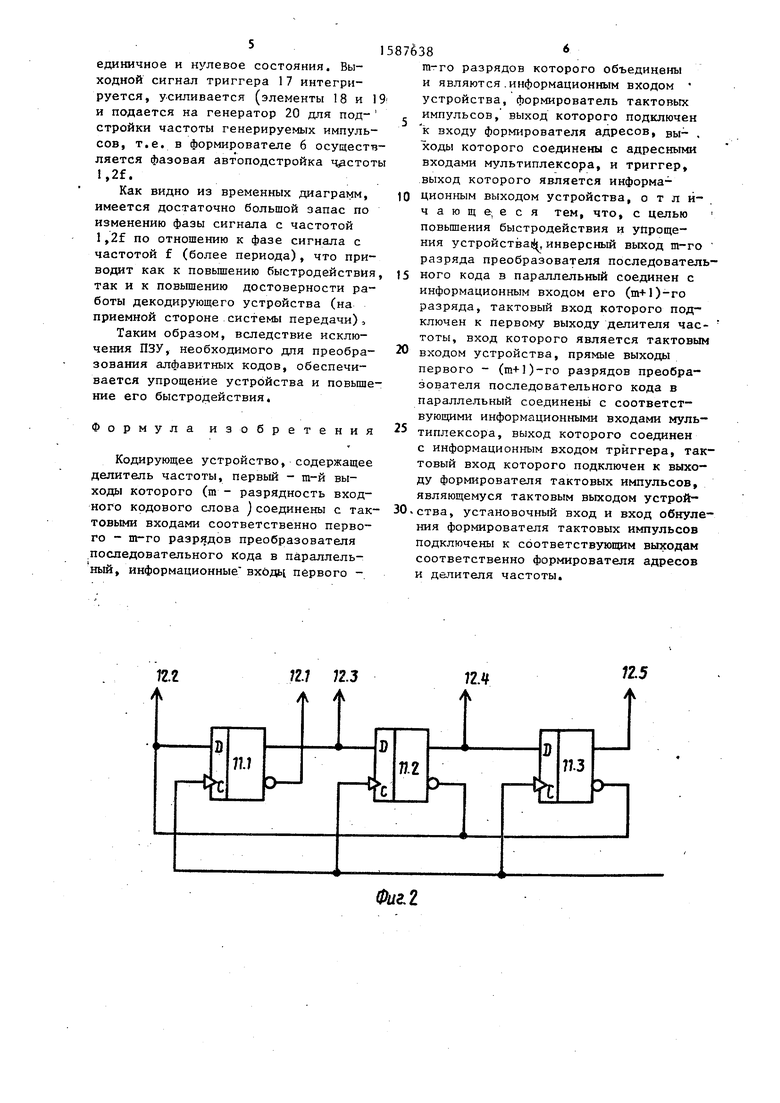

На фиг,1 приведена функциональная схема кодирующего .устройства; на фиг.2-4 - примеры выполнения соот- зетственно, делителя частоты, формирователя адресов и формирователя так- : овых импульсовJ на фиг«5 - временные диаграммы работы,

Кодирующее устройство содержит 1|1реобразователь 1 последовательного кода в параллельный, делитель -2 час оты, мультиплексор 3$ формирователь ч адресов, триггер 5, формирователь

0тактовых импульсов, информахщонный и тактовый входы 7 и 8 и информацион- йьц и тактовьй выходы 9 и 10,

1Преобразователь 1 последовательно- о кода в параллельный представляет фобой (й1+1)-разрядный регистр (т - разрядность входного кодового слова), Информационные входы первых m разрядов которого объединены, а инфор- 1|1ационный вход последнего разряда под Ллючен к инверсному выходу предыдуще- ifo разряда в соответствии с алгорит- йом формирования кода mBlC С

Рассмотрим пример выполнения устройства для случая m 5о

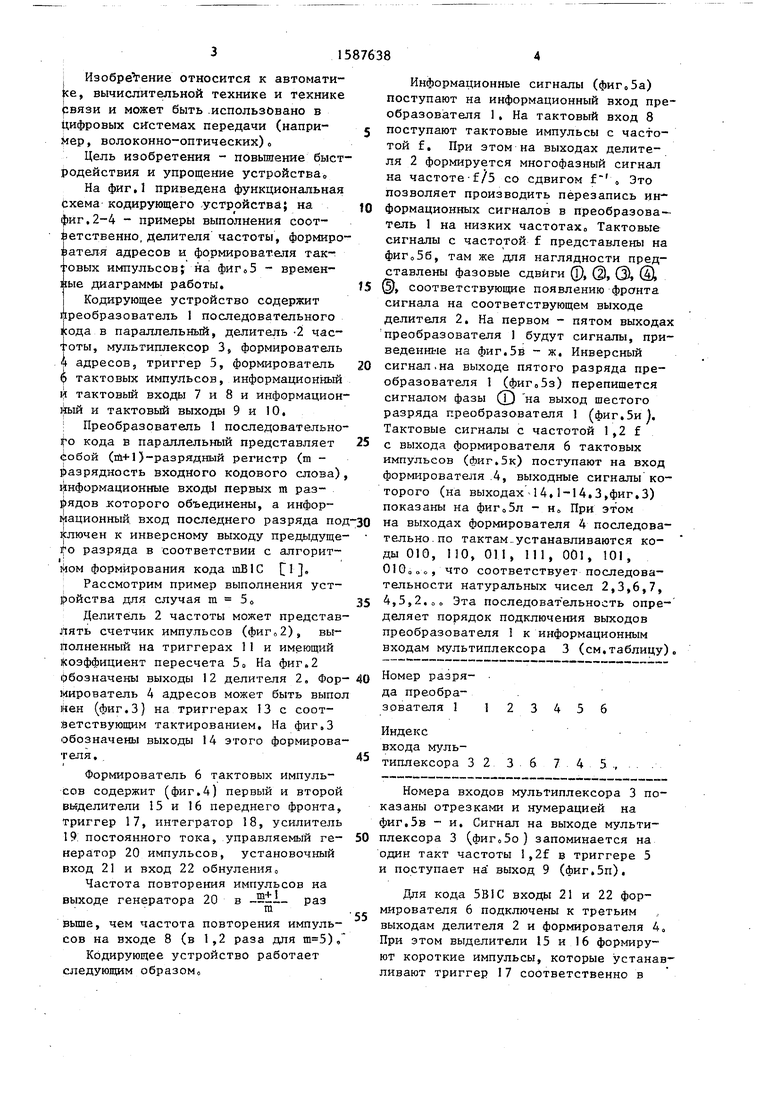

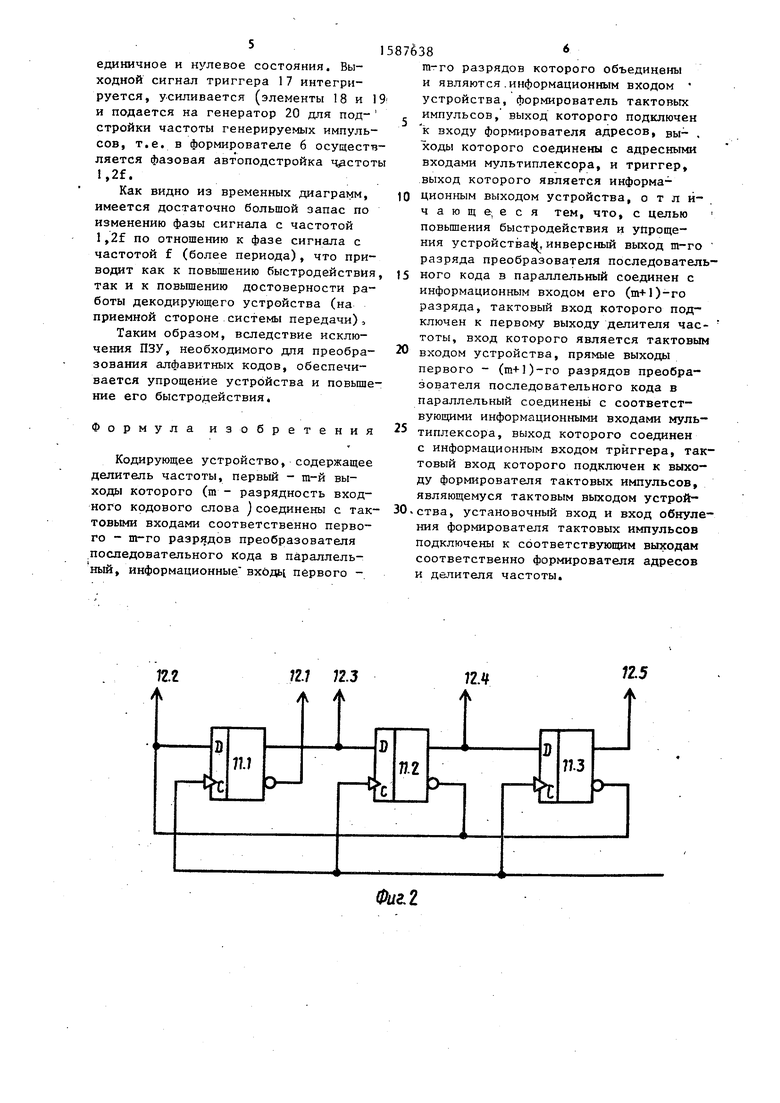

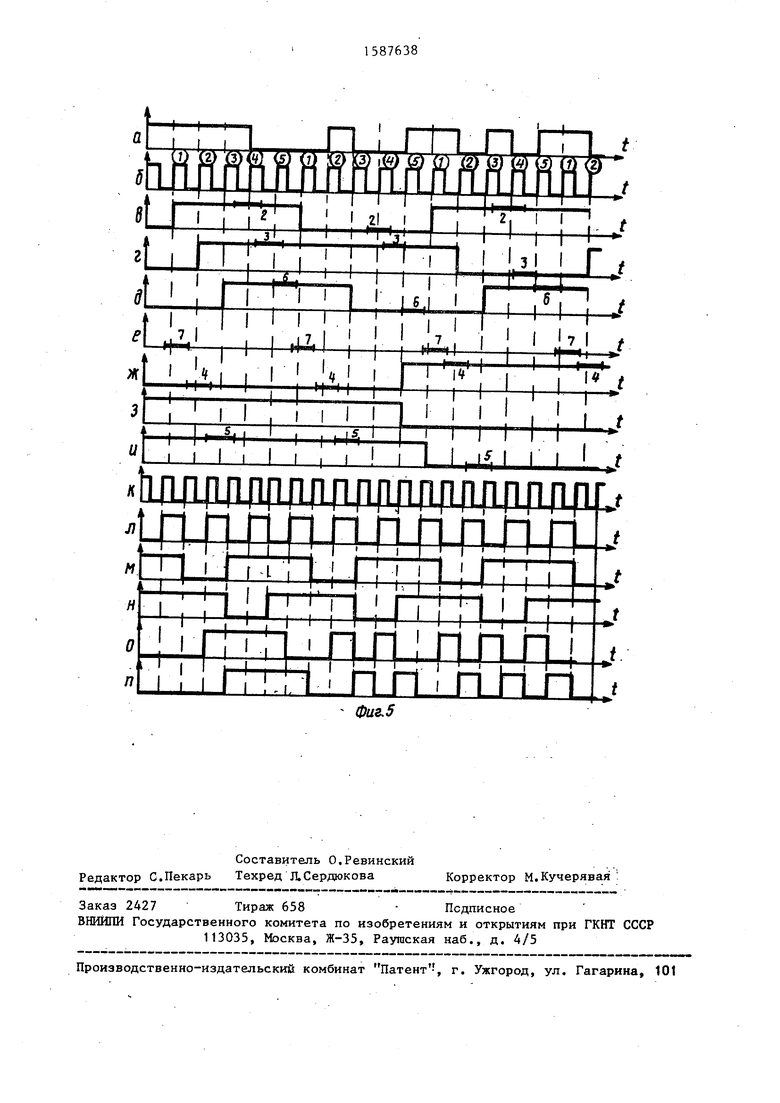

Делитель 2 частоты может представлять счетчик импульсов (), выполненный на триггерах 11 и имеющий Коэффициент пересчета 5 На фиг,2 Обозначены выходы 12 делителя 2, Фор- мирователь 4 адресов может быть выпол йен (фиг.З) на триггерах 13 с соответствующим тактированием. На фиг.З обозначены выходы 14 этого формирователя. .

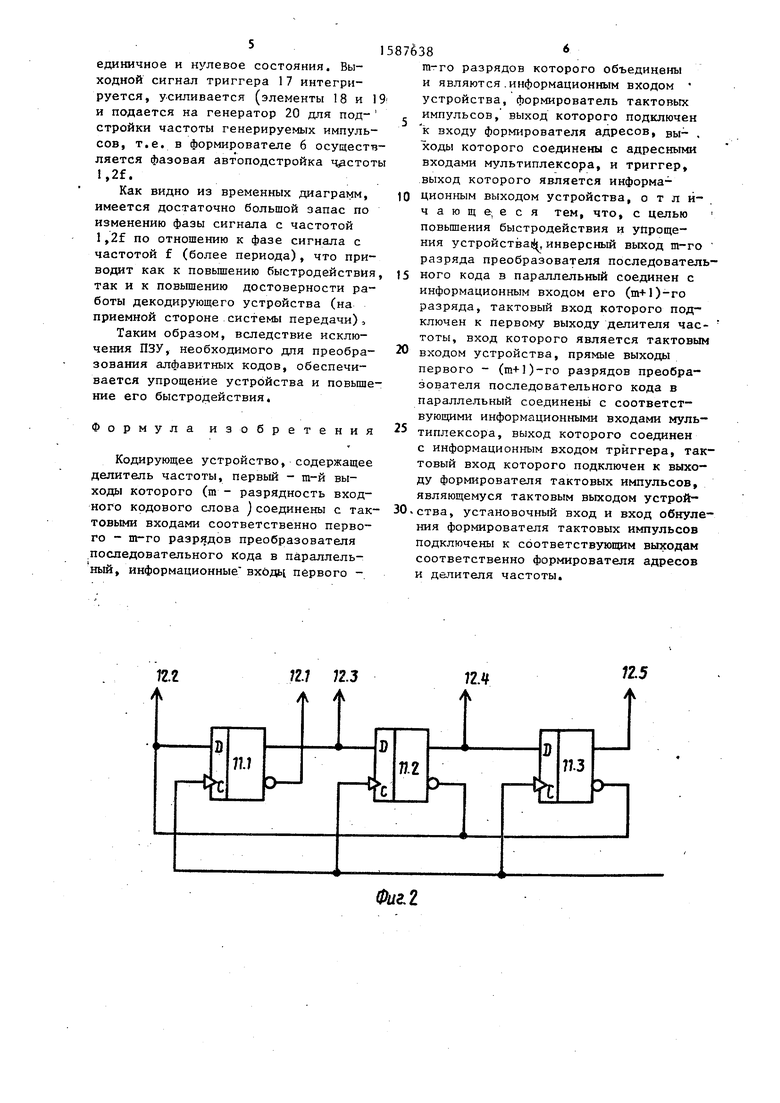

Формирователь 6 тактовых импульсов содержит (фиг.4) первый и второй выделители 15 и 16 переднего фронта, триггер 17, интегратор 18, усилитель 19. постоянного тока, управляемый ге- кератор 20 импульсов, установочный вход 21 и вход 22 обнуления о

Частота повторения импульсов на выходе генератора 20 в -Sii раз

выше, чем частота повторения импульсов на входе 8 (в 1,2 раза для )/

Кодирующее устройство работает следующим образомо

Информационные сигналы (фиго5а) поступают на информационный вход преобразователя 1. На тактовый вход 8 поступают тактовые импульсы с частотой f. При этом на выходах делителя 2 формируется многофазный сигнал на частотеf/5 со сдвигом f , Это позволяет производить перезапись ин- формационных сигналов в преобразователь 1 на низких частотах Тактовые сигналы с частотой f представлены на фиГо5б, там же для наглядности представлены фазовые сдвиги (р, Q, (3 (2i щ), соответствующие появлению франта сигнала на соответствующем выходе делителя 2, На первом - пятом выхода преобразователя 1 будут сигналы, приведенные на фиг,5в - ж. Инверсный сигнал.на выходе пятого разряда преобразователя 1 (фиго5з) перепишется сигналом фазы (Г) на выход шестого разряда преобразователя ( фиг,5и). Тактовые сигналы с частотой 1,2 f с выхода формирователя 6 тактовых импульсов (фиг.Зк) поступают на вход формирователя .4, выходные сигналы которого (на выходах 14,1-14,3,фиг,3) показаны на фиго5л - н„ При этом на выходах формирователя 4 последовательно, по тактам ..устанавливаются коды 010, 110, 011, 111, 001, 101, 01Оо о о, что соответствует последовательности натуральных чисел 2,3,6,7, 4,5,2,„, Эта последовательность определяет порядок подключения выходов преобразователя 1 к информационным входам мультиплексора 3 (см,таблицу)

Номер разря- . да преобразователя 1 1

23456

Индекс входа мультиплексора 323

6 745.,

Номера входов мультиплексора 3 показаны отрезками и нумерацией на фиг,5в - и. Сигнал на выходе мультиплексора 3 (фиго5о} запоминается на один такт частоты l,2f в триггере 5 и поступает на выход 9 (фиг,5п),

Для кода 5В1C входы 21 и 22 формирователя 6 подключены к третьим выходам делителя 2 и формирователя 4 При этом выделители 15 и 16 формируют короткие импульсы, которые устанавливают триггер I7 соответственно в

единичное и нулевое состояния. Выходной сигнал триггера 17 интегрируется, усиливается (элементы 18 и 19 и подается на генератор 20 для под- стройки частоты генерируемых импульсов, т.е. в формирователе 6 осуществляется фазовая автоподстройка частоты l,2f.

Как видно из временных диаграмм, имеется достаточно большой запас по изменению фазы сигнала с частотой l,2f по отношению к фазе сигнала с частотой f (более периода), что приводит как к повьшению быстродействия, так и к повышению достоверности работы декодирующего устройства (на приемной стороне системы передачи).

Таким образом, вследствие исключения ПЗУ, необходимого дпя преобразования алфавитных кодов, обеспечивается упрощение устройства и повышение его быстродействия.

Формула изобретения

Кодирующее устройство, содержащее делитель частоты, первый - т-й выходы которого (т - разрядность входного кодового слова j соединены с так- товыми входами соответственно первого - т-го разрядов преобразователя .последовательного кода в параллельный, информационные вхбдь1 первого 10

25

30,

587638

га-го разрядов которого объединены и являются.информационным входом устройства, формирователь тактовых импульсов, выход которого подключен к входу формирователя адресов, вы- . ходы которого соединены с адресными входами мультиплексора, и триггер, выход которого является информационным выходом устройства, о т л й- ч а ю щ е, е с я тем, что, с целью повышения быстродействия и упрощения устройства, инверсный выход т-го разряда преобразователя последовательного кода в параллельный соединен с информационным входом его (т+1)-го разряда, тактовый вход которого подключен к первому выходу делителя час- тоты, вход которого является тактовым входом устройства, прямые выходы первого - (т+1)-го разрядов преобразователя последовательного кода в параллельный соединены с соответствующими информационными входами мультиплексора, выход которого соединен с информационным входом триггера, тактовый вход которого подключен к выходу формирователя тактовых импульсов, являющемуся тактовым выходом устройства, установочный вход и вход обнуления формирователя тактовых импульсов подключены к соответствующим выходам соответственно формирователя адресов и делителя частоты.

t5

20

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодирующее устройство | 1987 |

|

SU1510093A1 |

| Декодирующее устройство | 1985 |

|

SU1339894A1 |

| Генератор кодовых последовательностей импульсов | 1987 |

|

SU1531080A1 |

| Анализатор кодовых последовательностей импульсов | 1985 |

|

SU1305868A2 |

| Анализатор кодовых последовательностей импульсов (его варианты) | 1984 |

|

SU1238243A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| СИНХРОННЫЙ АДАПТИВНЫЙ МУЛЬТИПЛЕКСОР | 1993 |

|

RU2078401C1 |

| Система для передачи и приема цифровой информации с согласованием скорости | 1989 |

|

SU1755385A1 |

| Устройство для преобразования телеграфного кода в видеокод | 1985 |

|

SU1314461A1 |

| Устройство для регулирования скорости электродвигателя | 1984 |

|

SU1267375A1 |

Изобретение относится к автоматике, вычислительной технике и технике связи. Его использование в цифровых (например, волоконно-оптических) системах передачи позволяет повысить быстродействие и упростить кодирующее устройство. Последнее содержит преобразователь 1 последовательного кода в параллельный, делитель 2 частоты, мультиплексор 3, формирователь 4 адресов, триггер 5 и формирователь 6 тактовых импульсов. Положительный эффект достигается при кодировании кодом МВ1С за счет отказа от ПЗУ, необходимого для преобразования алфавитных кодов. 5 ил., 1 табл.

Фиг, 2

Фи.г.Ъ

27,

5

17

22,

16

Фиг

;а

75

W

Фиг. 5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Кодирующее устройство | 1987 |

|

SU1510093A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| V | |||

Авторы

Даты

1990-08-23—Публикация

1988-02-29—Подача