f

Изобретение относится К вычислительной технике и может быть использовано в арифметических устройствах непозиционного типа для выполнения операции деления чисел, представленных в интервально-модулярной системе счисления,

Цель изобретения - сокращение количества о борудо1ания.

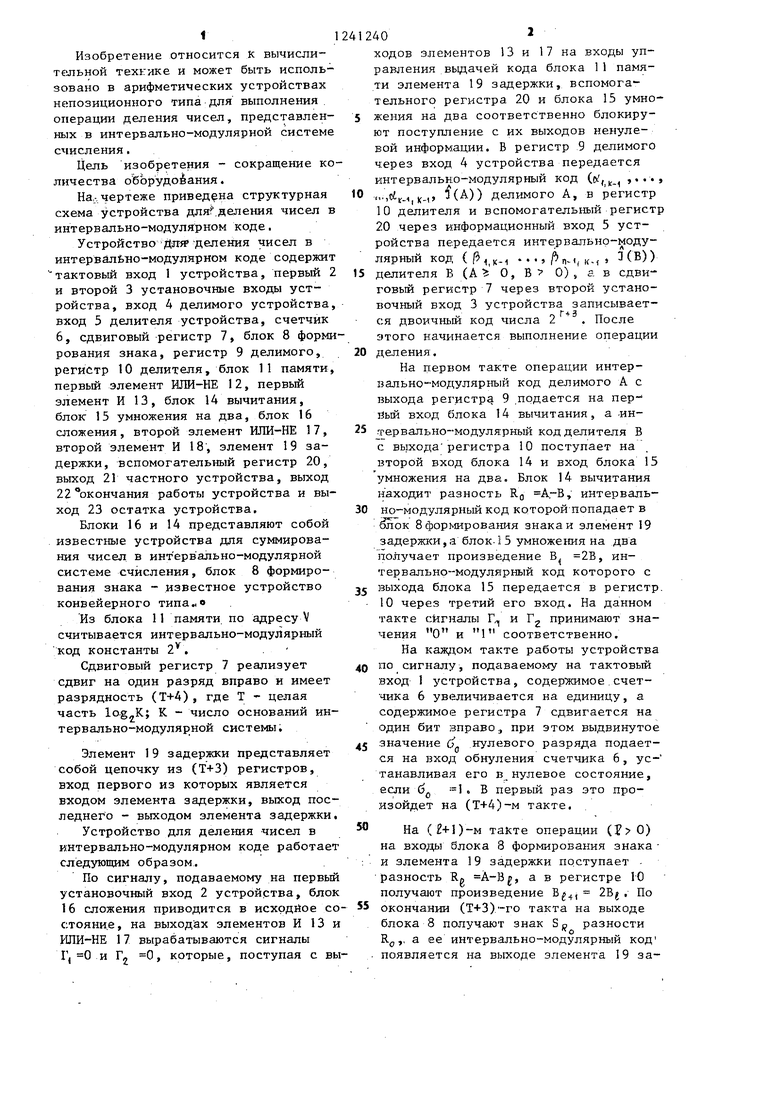

На,-, чертеже приведена структурная схема устройства для,деления чисел в интервально-модулярном коде.

Устройство Для деления чисел в ИНТервалЬно-МОдулярном коде содержит тактовый вход 1 устройства, первый 2 и второй 3 установочные входы устройства, вход 4 делимого устройства, вход 5 делителя устройства, счетчик 6, сдвиговый регистр 7, блок 8 формирования знака, регистр 9 делимого, регистр 10 делителя, блок 11 памяти, первый элемент ИЛИ-НЕ 12, первый элемент И 13, блок 14 вычитания, блок 15 умножения на два, блок 16 сложения, второй элемент ИЛИ-НЕ 17, второй элемент И 18, элемент 19 задержки, вспомогательный регистр 20, выход 21 частного устройства, выход 22 окончания работы устройства и выход 23 остатка устройства.

Блоки 16 и 14 представляют собой известные устройства для суммирования чисел в инт ервально-модулярной системе счисления, блок В формирования знака - известное устройство конвейерного типа«в

Из блока 11 памяти по адресу V считывается иитервально-модулярный код константы 2. . Сдвиговый регистр 7 реализует сдвиг на один разряд вправо и имеет разрядность (Т+4), где Т - целая часть lo. К - число оснований интервально-модулярной системы.

Элемент 19 задержки представляет собой цепочку из (Т+3) регистров, вход первого из которых является входом элемента задержки, выход последнего - выходом элемента задержки.

Устройство для деления чисел в интервально-модулярном коде работает следующим образом.

По сигналу, подаваемому на первый установочный вход 2 устройства, блок 16 сложения приводится в исхрдйое со с;тояни.е, на выходах элементов И 13 и ИЛИ-НЕ 17 вырабатываются сигналы Г, 0 и Г 0, которые, поступая с вы412402

ходов элементов 13 и 17 на входы управления выдачей кода блока 11 памяти элемента 19 задержки, вспомога- тельногсэ регистра 20 и блока 15 умно5 женин на два соответственно блокируют поступление с их выходов ненулевой информации. В регистр 9 делимого через вход 4 устройства передается интервально-модулярный код (&,,.,

0 м. к, (А)) делимого А, в регистр 10 делителя и вспомогательный регистр 20 через информационный вход 5 устройства передается интервально-модулярный код, ,. .. .,,j ,(., , 3(В))

15 делителя В (А% О, В 0) , а в сдвиговый регистр 7 через второй установочный вход 3 устройства записывается двоичный код числа 2 . После этого начинается выполнение операции

20 деления.

На цервом такте операции интервально-модулярный код делимого А с выхода регистру 9 .подается на пер- йый вход )лока 14 вычитания, а -ин25 тервально-модулярный код делителя В с выхода регистра 10 поступает на второй вход блока 14 и вход блока 15 умножения на два. Блок 14 вычитания находит разность Кд А-В, интерваль30 Hoj-модулярный код которой попадает в ёлок 8 формирования знака и элемент 19 задержки, а блок-1 5 умноже шя на два получает произведение В 2В, ин- тервально-модулярный код которого с

35 выхода блока 15 передается в регистр. 10 через третий его вход. На данном такте сигналы Г и Г принимают значения О и 1 соответственно.

На каж;з,ом такте работы устройства

40 по сигналу, подаваемому на тактовый вход I устройства, содержимое счет- чика 6 увеличивается на единицу, а содержимое регистра 7 сдвигается на один бит вправо., при этом выдвинутое

45 .значение ( кулевого разряда подается на вход обнуления счетчика 6, ус- танавливая его в нулевое состояние, если 6jj . В первый раз это произойдет на (Т+4)-м такте.

На (+1)-м такте операции () на входы блока 8 формирования знака

: и элемента 19 задержки поступает - разность Rg А-В, а в регистре 10 получают произведение В, 2В. По

55 окончании (Т+3)-го такта на выходе

, блока 8 получают знак S р разности . о

К.,,, а ее интерв/ально-модулярный код

. появляется на выходе элемента 19 за3

держки. Если S 1(А В), то на выходе элемента И 18 и соответственно на выходе 22 устройства по входным величинам б, 1 и S, 1, поступающим соответственно на первый и второй входы с выходов первого разряда сдвигового регистра 7 и формирователя 8 знака числа соответственно, формируется единичный сигнал, указывающий на то, что процесс деления чисел Аи В завершен. Частное и остаток снимаются с выходов 21 и 23 устройства и на этом работа устройства заканчивается. Если S 0(А В), то описанные вьше действия повторяют ся. На (Т+4)-м такте содержимое dp 1 нулевого разряда сдвигового регистра 7 поступает на вход обнуления счет- чика 6, устанавливая его в нулевое состояние, а на (Т+В+3)-м такте на выходе блока 8 и элемента 19 задержки появляются соответственно знак Sg и интервально-модулярный код числа Rg. Предположим, что при некотором 8 V+1 (V -у 1) на выходе блока 8 появится единичный S 1, соответствующий разности Rv4t Тогда, в силу того, что d, z ..4 0, на выходе элемента И 13 формируется единичный сигнал Г, 1, который поступает в старщий (Т+3)-й разряд сдвигового регистра 7 на второй вход элемента ИЛИ-НЕ 17 и входы упр-авления выдачей кода блока 11 памяти, элемента 19 задержки и вспомогательного регистра 20. Из блока 11 памяти по адресу V, полученному к этому времени в счетчике 6, считывается интервально-модулярный код

V

константы 2 , который подается на вход блока 16 сложения, осуществляющего накопление частного Q. На выходе элемента ИЛИ-НЕ 17 вырабатывается сигнал , который, поступая на вход управления выдачей кода блока 15 умножения на два, блокирует поступление с его выхода ненулевой информации, в регистр 10 из вспомогательного регистра 20.передается интервально-модулярный код делителя В, а в регистр 9 делимого с выхода элемента 19 задержки поступает интер- вапьно-модулярный код разности Ry .. На STOM заканчивается первая итерация реализуемого .алгоритма деления.

В дальнейшем описанный процесс функционирования устройства повторяется до тех пор, пока на выходе эле2404

мента И 18 не появится единичный-сигнал. Это случится после добавления в блоке 16 сложения к накапливаемой сумме младшего члена двоичного представления частного Q. Интервально- модулярные коды частного Q и остатка R от деления снимаются соответственно с выходов 21 и 23 устройства, на этом работа устройства заканчивается

Формул а изобретения

Устройство для деления чисел в интервально-модулярном коде, содержащее регистры делимого и делителя, блок сложения, блок вычитания, блок умножения на два и два элемента ИЛИ- НЕ , причем входы делимого и делителя устройства соединены с первыми информационными входами регистров делимого и делителя соответственно, выход регистра делителя соединен с информационным входом блока умножения на два, выход блока сложения являет- .ся выходом частного устройства, о т- личающееся тем, что, с целью сокращения количества оборудования, оно содержит счетчик, сдвиговый регистр, блок памяти, блок формирования знака, два элемента И, элемент задержки и вспомогательный регистр, причем счетный вход счетчика и вход сдвига сдвигового регистра объединены и подключены к тактовому входу устройства, вход обнуления блока сложения, первые входы первого и второго элементов ИЛИ-НЕ и вход приема кода вспомогательного регистра объединены и подключены к первому установочному входу устройства, информационный вход сдвигового регистра является вторым установочным входом устройства, вход старшего разряда сдвигового регистра, второй вход второго элемента ИЛИ-НЕ, входы выдачи кода блока памяти, элемента задержки и вспомогательного регистра объединены и подключены к выходу первого элемента И, первые входы первого и второго элементов И объединены и подключены к выходу блока формирования знака, вход которого объединен с входом элемента задержки и подключен к выходу блока вычитания, второй информационный вход регистра делимого подключен к выходу элемента задержки, а выход регистра делимого подключен к входу уменьшаемого блока

вычитания, вход вычитаемого которого подключен к выходу регистра делителя, второй и третий информационные входы регистра делителя подключены соответственно к выходам вспомогательного регистра и блока умножения на два, адресный вход блока памяти подключен к выходу счетчика, выход блока памяти соединен с информационным входом блока сложения, выходы разрядов, кроме младшего, сдвигового регистра сое- дине1Е1ы с соответствующими входами первого элементаИЛИ-НЕ,выход мпадше- rd разряда сдвигового регистра соединен с входом обнуления счетчика,

второй вход первого элемента ИЛИ-НЕ соединен с вторым входом второго элемента И, выход первого элемента ИЛИ- НЕ соединен с вторым входом первого элемента И, входы приема кода регистра делимого и выдачи кода блока умножения на два объединены и подключены к выходу второго элемента ИЛИ-НЕ, информационный вход вспомогательного регистра объединен с первым входом регистра делителя, выход регистра делимого подключен к выходу остатка устройства, вьгх;од второго элемента И является выходом окончания работь устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для умножения комплексных чисел в модулярной системе счисления | 1985 |

|

SU1280625A1 |

| Устройство для умножения чисел в непозиционной системе счисления | 1981 |

|

SU1015382A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1989 |

|

SU1667065A1 |

| Устройство для вычисления квадратного корня числа в модулярной системе счисления | 1985 |

|

SU1317434A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1986 |

|

SU1411742A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1368878A1 |

| Устройство для умножения комплексных чисел в модулярном коде | 1985 |

|

SU1330631A1 |

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах непозиционного типа для выполнения операции деления чисел, представленных в интервально-модулярной системе счисления.Цель изобретения - уменьшение количества оборудования устройства. Поставленная цель достигается за счет реализации итерационного алгоритма, базирующегося на операциях умножения на два, деления и формирования знака числа в ин- тервально-модулярном коде. Поставленная цель достигается тем, что устройство для деления чисел в интер-- вально-модулярвом коде, содержащее блоки сложения, вычитания и умножения,, два элемента ИЛИ-НЕ, содержит счетчик, сдвиговый регистр, блок памяти, блок формирования знака, два элемента И, элемент задержки и вспомогательный регистр с соответствующими связями. Устройство также может быть использовано специализированных вычислительных устройствах, реализующих вторичную обработку дискретных сигналов в системах различного назначения..1 ил. с со (Л К) 4

21

Редактор Л. Пчелинская

Составитель А.Клюев

Техред О.Гортвай Корректор Л.Патай

Заказ 3490/44Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035 , Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород ,ул.Проект1 ая ,4

| УСТРОЙСТВО ДЛЯ ОКРУГЛЕНИЯ ЧИСЛА В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 0 |

|

SU398949A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Топка с газифицирующим предтопочным устройством | 1925 |

|

SU5796A1 |

Авторы

Даты

1986-06-30—Публикация

1984-12-20—Подача