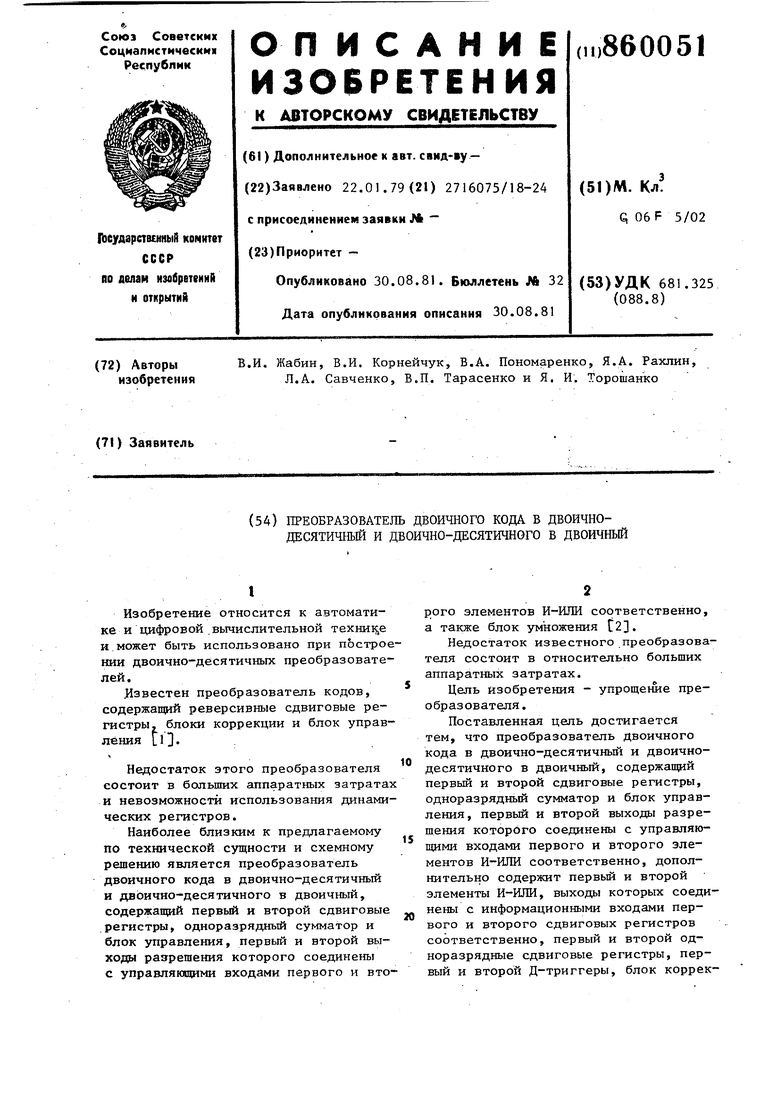

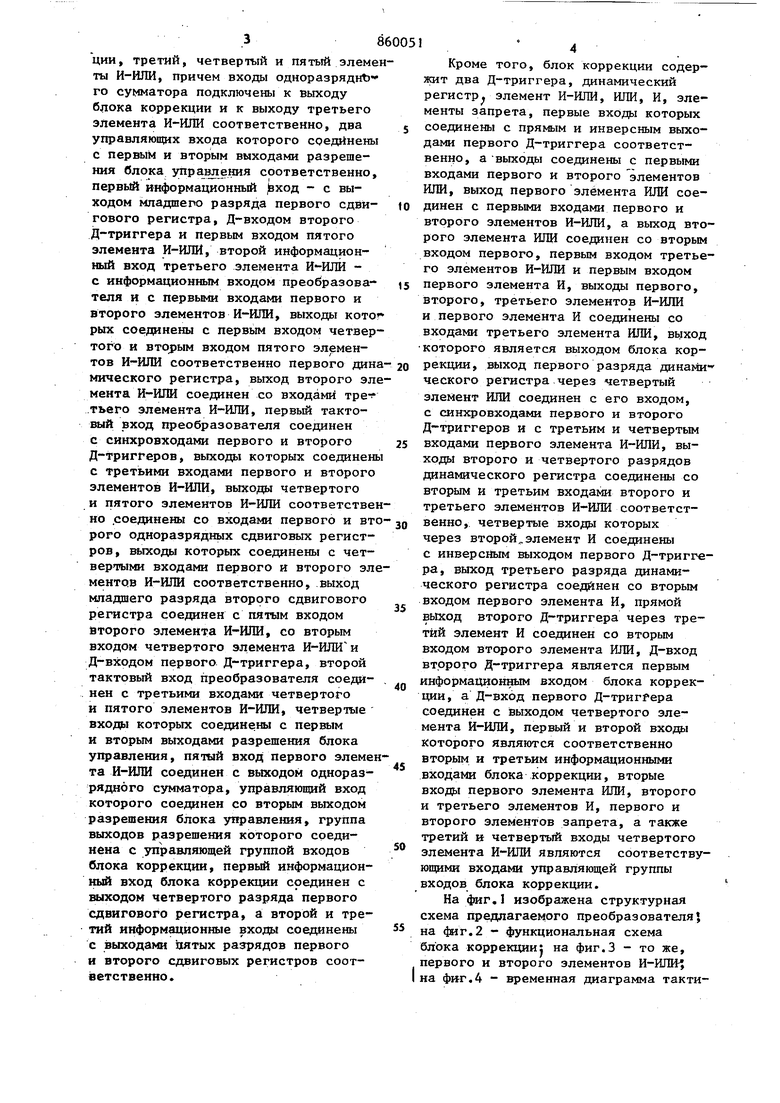

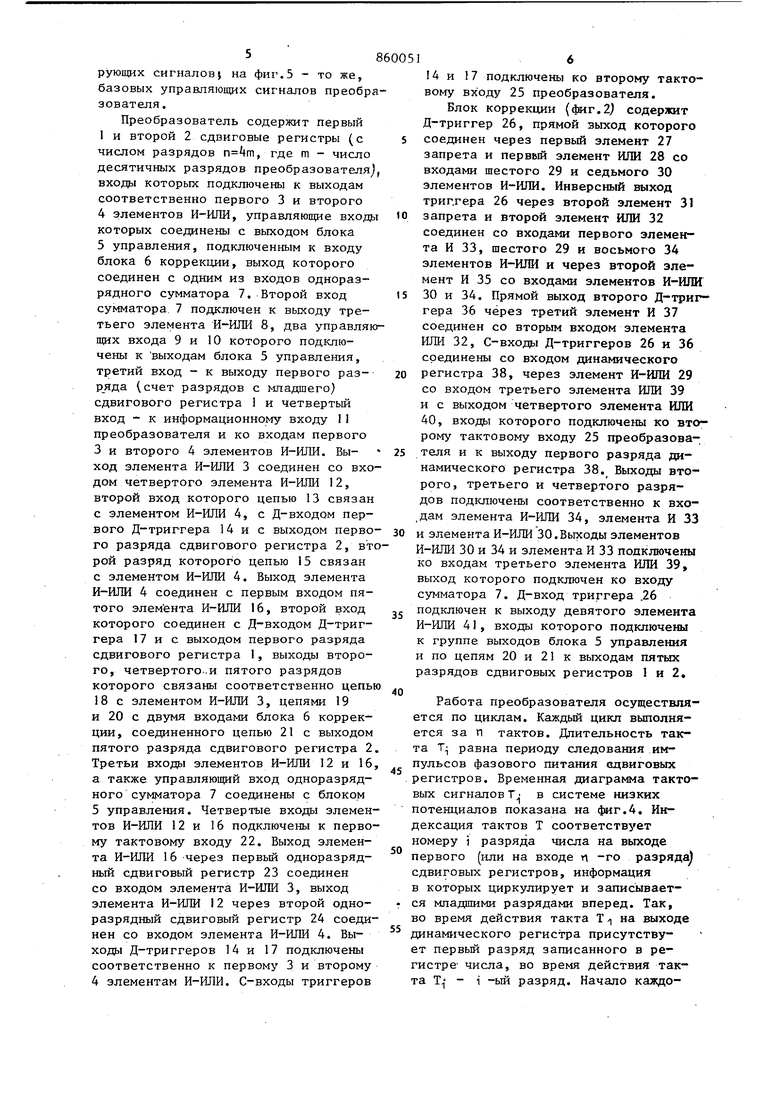

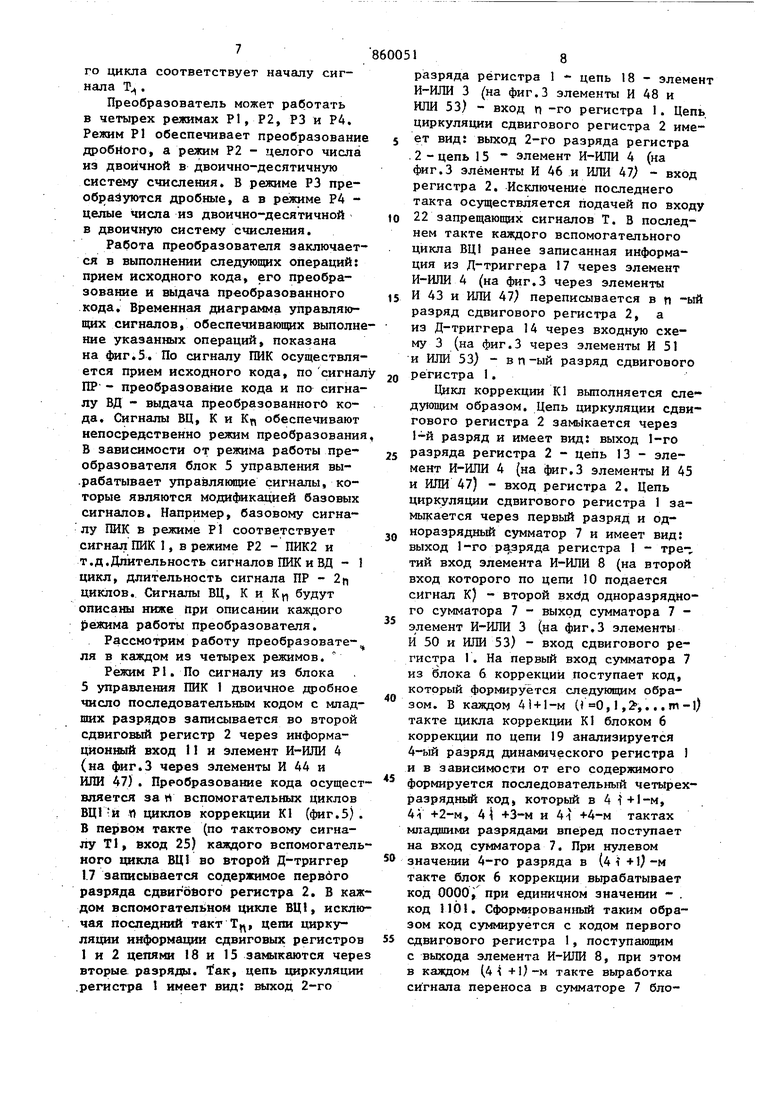

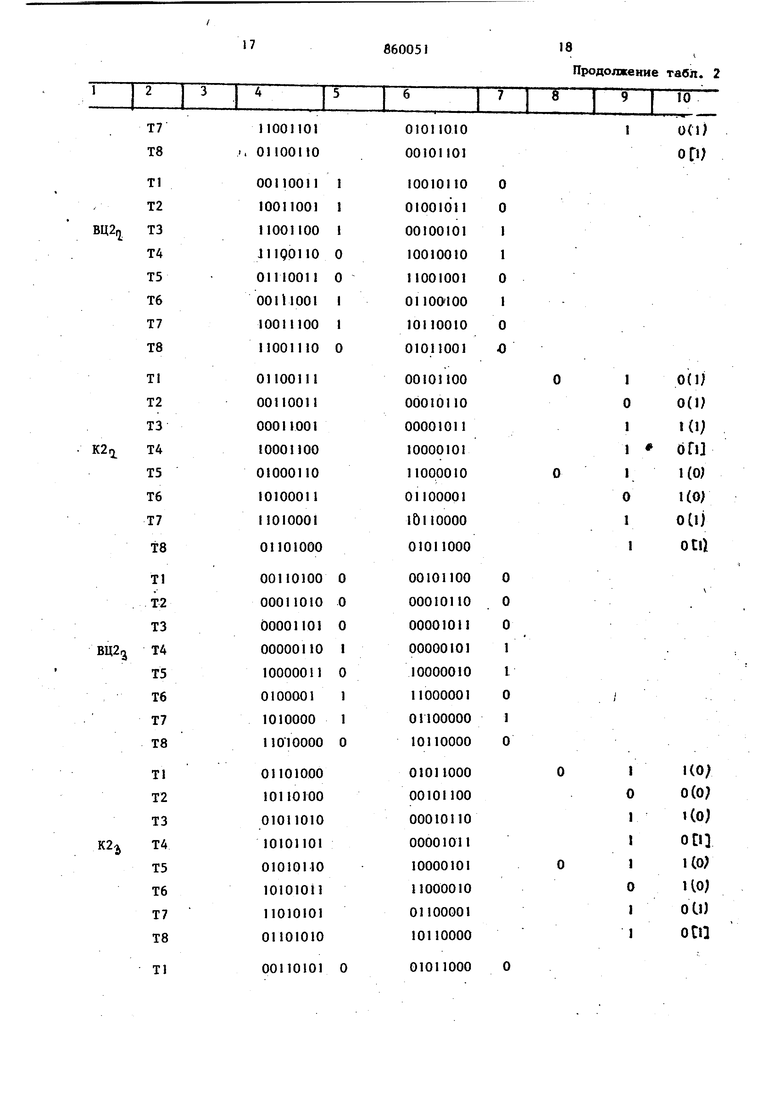

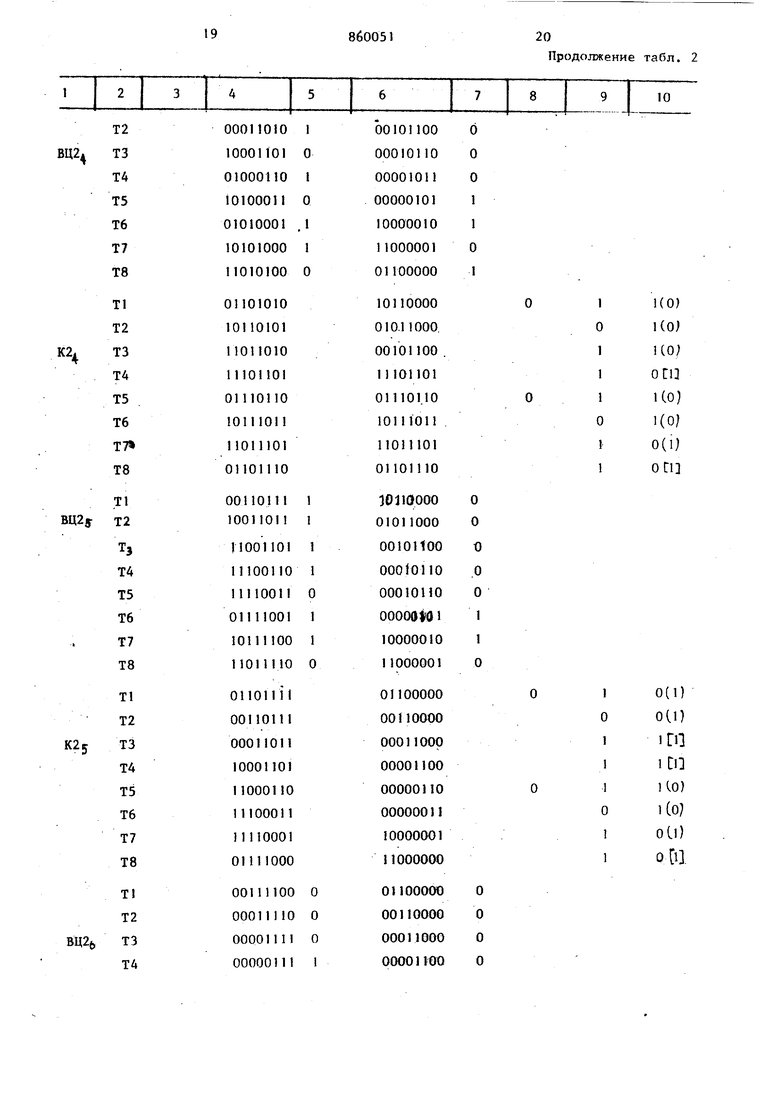

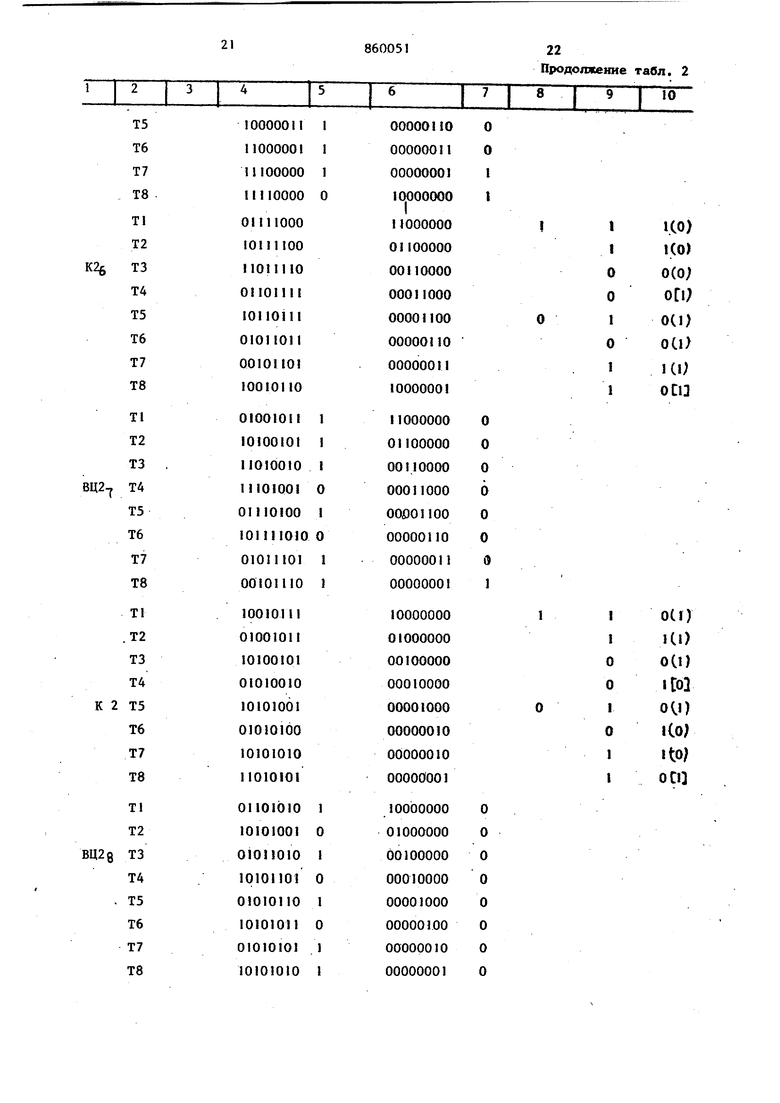

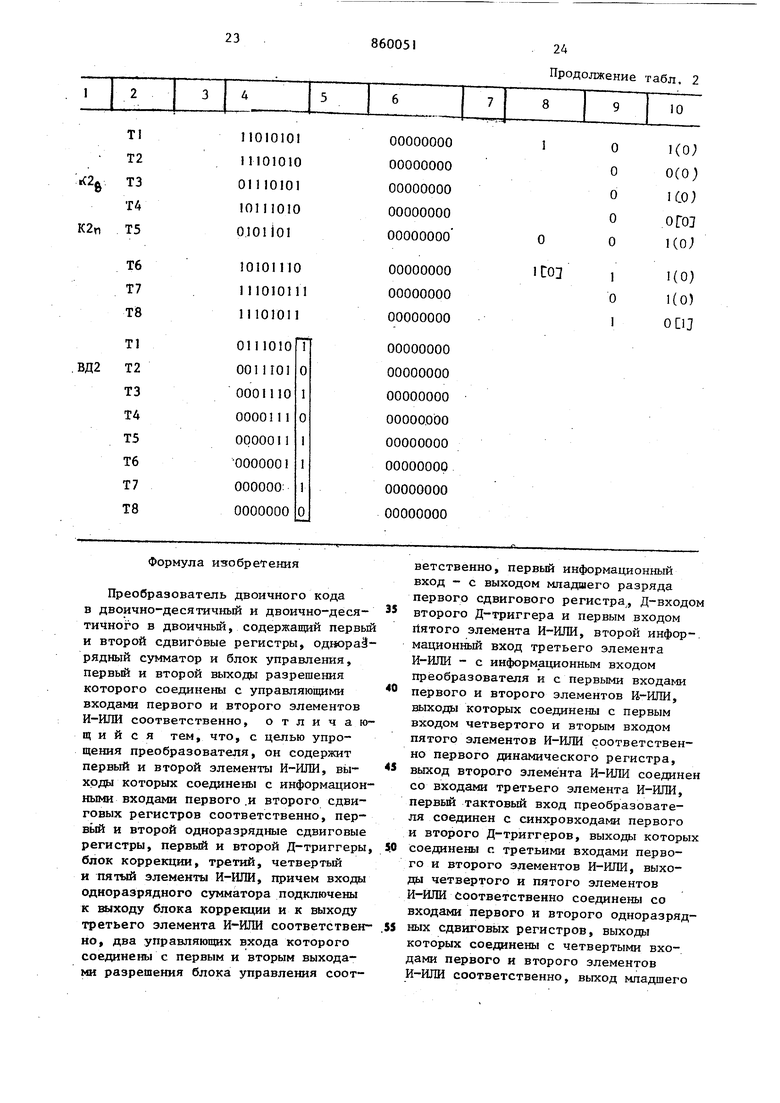

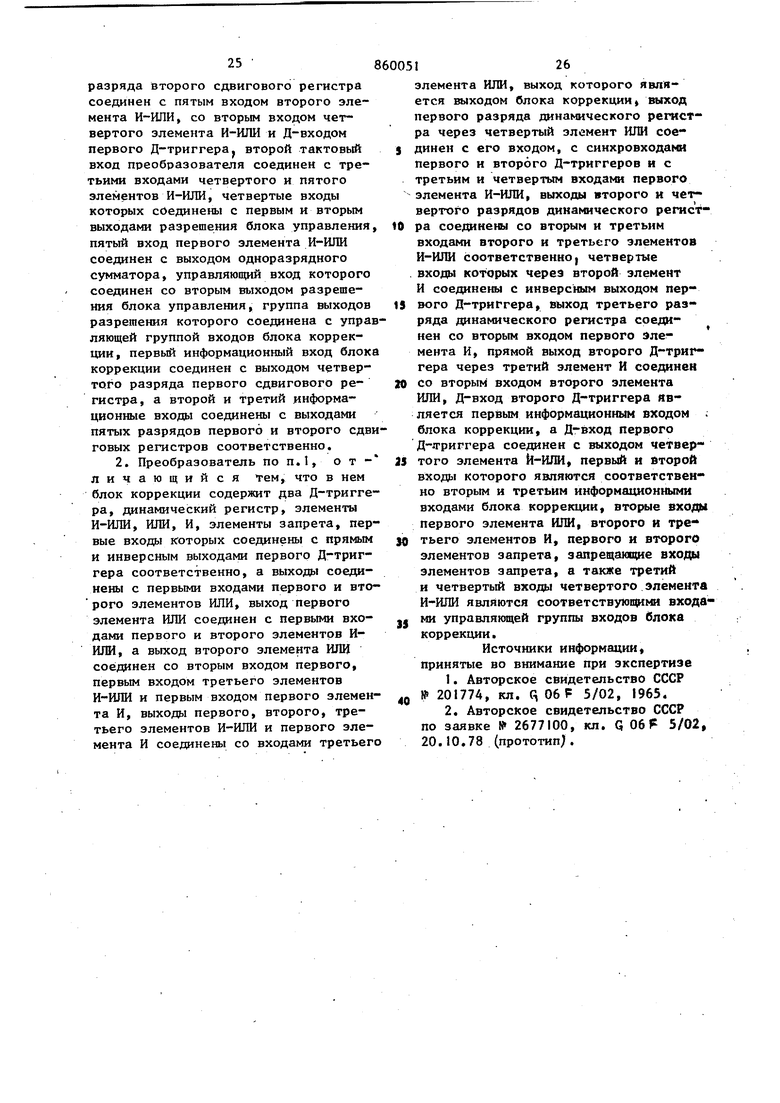

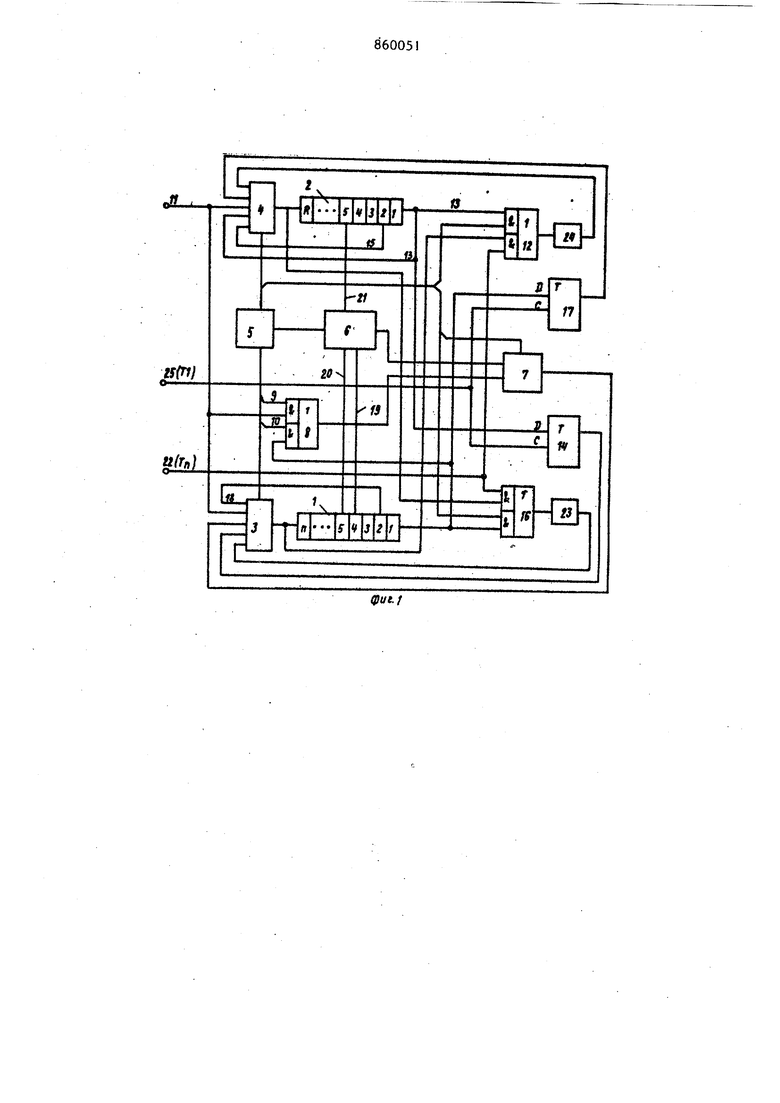

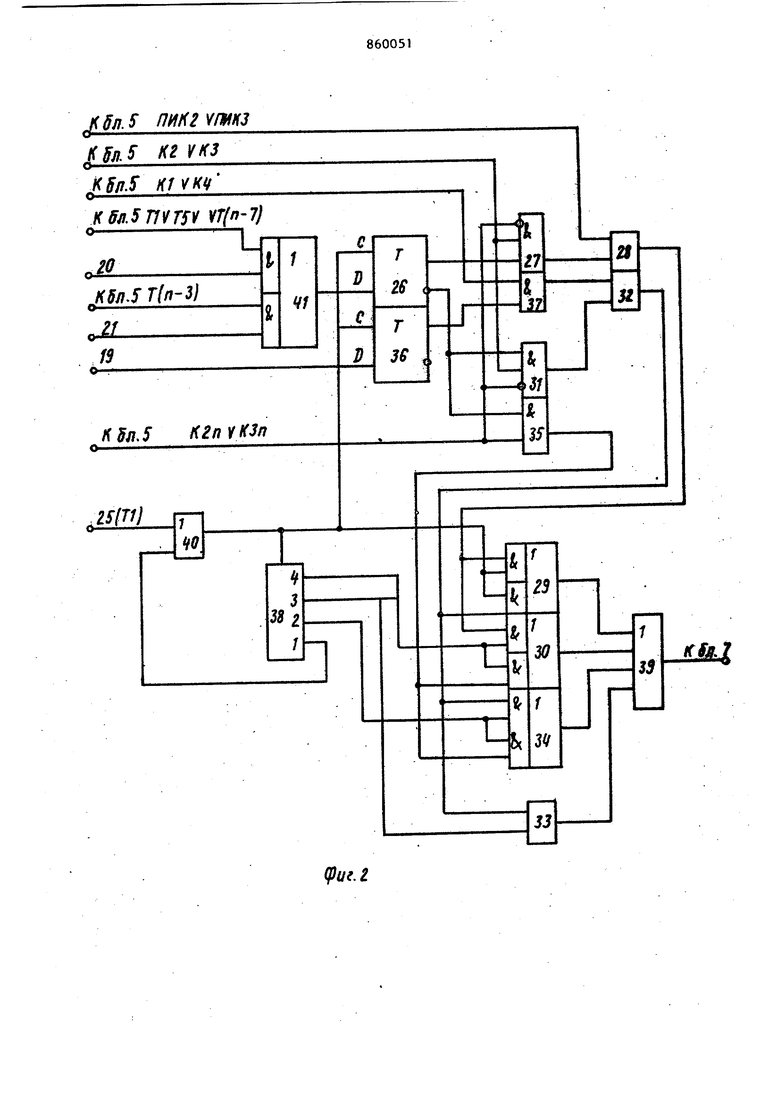

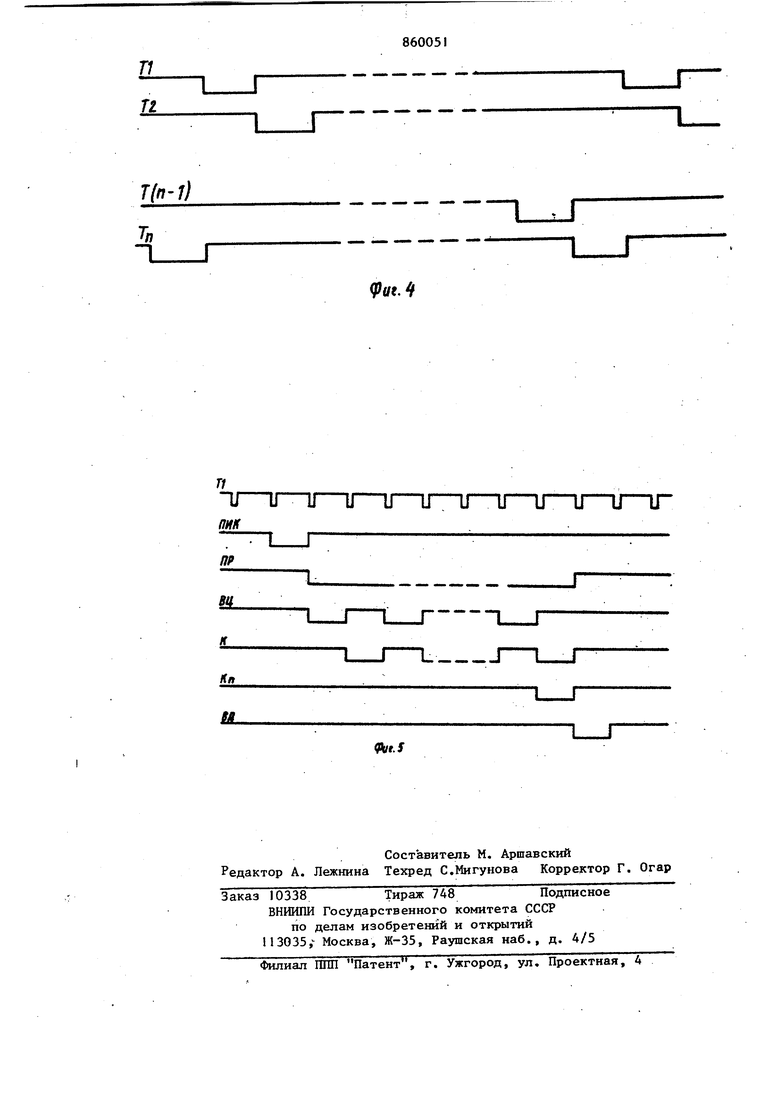

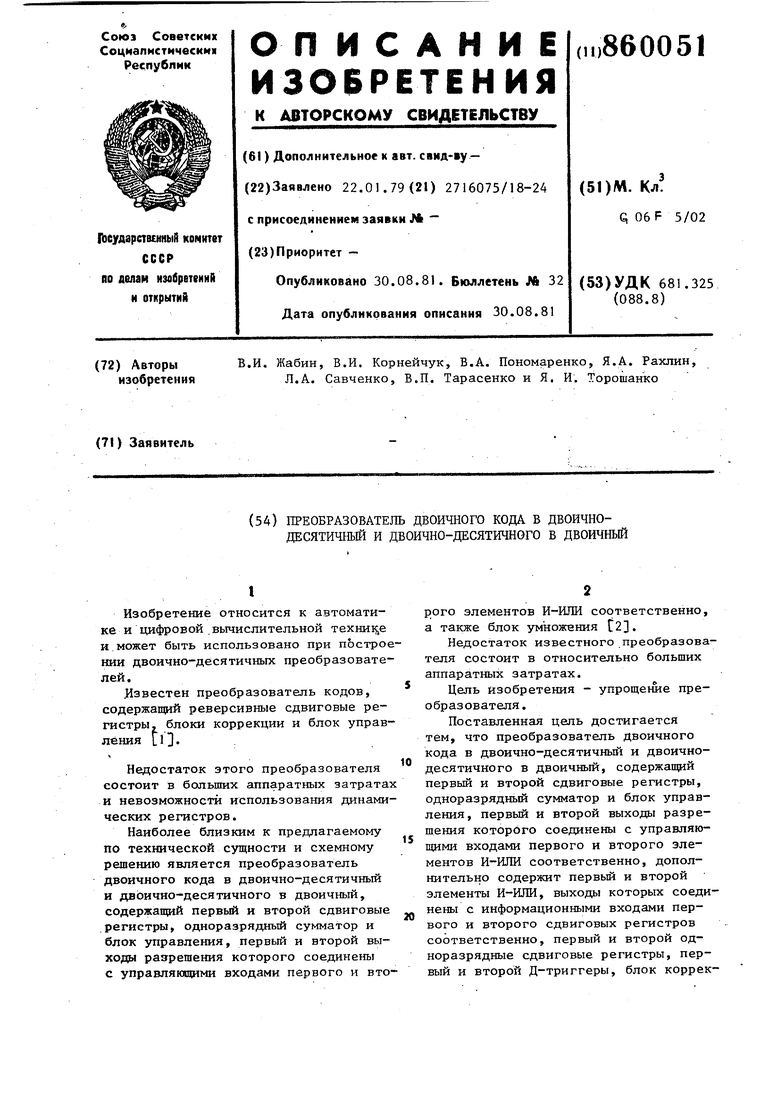

Изобретение относится к автоматике и цифровой . вычислительной техни1 е и.может быть использовано при построе нии двоично-десятичных преобразователей . Язвестен преобразователь кодов, содержащий реверсивные сдвиговые регистры, блоки коррекции и блок управления 1 3 Недостаток этого преобразователя состоит в больших аппаратных затрата и невозможности использования динами ческих регистров. Наиболее близким к предлагаемому по технической сущности и схемному решению является преобразователь двоичного кода в двоично-десятичный и двоично-десятичного в двоичный, содержащий первый и второй сдвиговые регистры, одноразрядный сумматор и блок управления, первый и второй выходы разрешения которого соединены с управляющими входами первого и вто рого элементов И-ИЛИ соответственно, а также блок умножения С2. Недостаток известного преобразователя состоит в относительно больших аппаратных затратах. Цель изобретения - упрощеш1е преобразователя. Поставленная цель достигается тем, что преобразователь двоичного кода в двоично-десятичный и двоичнодесятичного в двоичный, содержащий первый и второй сдвиговые регистры, одноразрядный сумматор и блок управления, первый и второй выходы разрешения которого соединены с управляющими входами первого и второго элементов И-ШШ соответственно, дополнительно содержит первый и второй элементы И-ШШ, выходы которых соединены с информационными входами первого и второго сдвиговых регистров соответственно, первый и второй одноразрядные сдвиговые регистры, первый и второй Д-триггеры, блок коррек3ции, третий, четвертый и пятый элеме ты И-ИПИ, причем входы одноразряднЪ го сумматора подключены к выходу блока коррекции и к выходу третьего элемента И-ИЛИ соответственно, два управляющих входа которого соединены с первым и вторым выходами разрешения блока управления соответственно, первый информационный ход - с выходом младшего разряда первого сдвИгового регистра, Д-входом второго Д-триггера и первым входом пятого элемента И-ИЛИ, второй информационный вход третьего элемента И-ИЛИ с информационным входом преобразователя и с первыми входами первого и второго элементов И-ИЛИ, выходы кото рых соединены с первым входом четвер того и вторым входом пятого элементов И-ИЛИ соответственно первого дин мического регистра, выход второго эл мента И-ИЛИ соединен со входами тре тьего элемента И-ИЛИ, первый тактовый вход преобразователя соединен с синхровходами первого и второго Д-триггеров, выходы которых соединен с третьими входами первого и второго элементов И-ИПИ, выходы четвертого и пятого элементов И-ШШ соответстве но соединены со входами первого и вт рого одноразрядных сдвиговых регистров, иыходы которых соединены с четвертыми входами первого и второго эл ментов И-ИЛИ соответственно, выход младшего разряда второго сдвигового регистра соединен с пятым входом второго элемента И-ШШ, со вторым входом четвертого элемента И-ШШ и Д-входом первого Д-триггера, второй тактовый вход преобразователя соединен с третьими входами четвертого и пятого элементов И-ИЛИ, четвертые входы которых соединены с первым и вторым выходами разрешения блока управления, пятый вход первого элеме та И-ШШ соединен с выходом одноразрядного сумматора, управляющий вход которого соединен со вторым выходом разрешения блока управления, группа выходов разрешения которого соединена с управляющей группой входов блока коррекции, первый информационный вход блока коррекции соединен с выходом четвертого разряда первого сдвигового регистра, а второй и третий информационные входы соединены с выходами цятых разрядов первого и второго сдвиговых регистров соответственно. Кроме того, блок коррекции содер- ясит два Д-триггера, динамический регистр элемент И-ИЛИ, ИЛИ, И, элементы запрета, первые входы которых соединены с прямым и инверсным выходами первого Д-триггера соответственно, а ВЫХОДЫ соединены с первыми входами первого и второго элементов ИЛИ, выход первого элемента ИЛИ соединен с первыми входами первого и второго элементов И-ШШ, а выход второго элемента ИЛИ соединен со вторым входом первого, первым входом третьего элементов И-ИЛИ и первым входом первого элемента И, выходы первого, второго, третьего элементов И-ШШ и первого элемента И соединены со входами третьего элемента ИЛИ, выход которого является выходом блока коррекции, выход первого разряда ческого регистра.через четвертый элемент ИЛИ соединен с его входом, с синхровходами первого и второго Д-триггеров и с третьим и четвертым входами первого элемента И-ИЛИ, выходы второго и четвертого разрядов динамического регистра соединены со вторым и третьим входами второго и третьего элементов И-ИЛИ соответственно, четвертые входы которых через второй элемент И соединены с инверсным выходом первого Д-триггера, выход третьего разряда динамического регистра соединен со вторым входом первого элемента И, прямой выход второго Д-триггера через третий элемент И соединен со вторым входом второго элемента ИЖ, Д-вход второго Д-триггера является первым информационным входом блока коррекции, а Д-вход первого Д-тригрера соединен с выходом четвертого элемента И-ИЛИ, первый и второй входы которого являются соответственно вторым и третьим информационными входами блока коррекции, вторые входы первого элемента ИЛИ, второго и третьего элементов И, первого и второго элементов запрета, а также третий и четвертый входы четвертого элемента И-ШШ являются соответствующими входами управляющей группы входов блока коррекции. На фиг. изображена структурная схема предлагаемого преобразователяJ на 4иг.2 - функциональная схема блока коррекцииJ на фиг.З - то же, первого и второго элементов И-ИЛИ на фиг.4 - временная диаграмма такти5рующих сигналовj на фиг.5 то же, базовых управляющих сигналов преобра зователя. Преобразователь содержит первый 1 и второй 2 сдвиговые регистры (с числом разрядов , где m - число десятичных разрядов преобразователя входы которых подключены к выходам соответственно первого 3 и второго 4элементов И-ИЛИ, управляющие входы которых соединены с выходом блока 5управления, подключенным к входу блока 6 коррекции, выход которого соединен с одним из входов одноразрядного сумматора 7. Второй вход сумматора 7 подключен к выходу третьего элемента И-ИЛИ 8, два управляю щих входа 9 и 10 которого подключены к выходам блока 5 управления, третий вход - к выходу первого разр яда (счет разрядов с младшего) сдвигового регистра 1 и четвертый вход - к информационному входу I1 преобразователя и ко входам первого 3и второго 4 элементов И-ИЛИ. Выход элемента И-ИЛИ 3 соединен со вхо дом четвертого элемента И-ИЛИ 12, второй вход которого цепью 13 связан с элементом И-ИЛИ 4, с Д-входом первого Д-триггера 14 и с выходом перво го разряда сдвигового регистра 2, вт рой разряд которого цепью 15 связан с элементом И-ИЖ 4. Выход элемента И-ИЛИ 4 соединен с первым входом пятого элемента И-ИЛИ 16, второй вход которого соединен с Д-входом Д-триггера 17 и с выходом первого разряда сдвигового регистра 1, выходы второго, четвертого-.и пятого разрядов которого связаны соответственно цепь 18 с элементом И-ИЛИ 3, цепями 19 и 20 с двумя входами блока 6 коррекции, соединенного цепью 21 с выходом пятого разряда сдвигового регистра 2 Третьи входы элементов И-ИЛИ 12 и 16 а также управляющий вход одноразрядного сумматора 7 соединены с блоком 5 управления. Четвертые входы элемен тов И-ИЛИ 12 и 16 подключены к перво му тактовому входу 22. Выход элемента И-ИЛИ 16 через первый одноразрядный сдвиговый регистр 23 соединен со входом элемента И-ШШ 3, выход элемента И-ИЛИ I2 через второй одноразрядный сдвиговый регистр 24 соеди нен со входом элемента И-ИЛИ 4. Выходы Д-триггеров 14 и 17 подключены соответственно к первому 3 и второму 4элементам И-ИЛИ. С-входы триггеров 14 и 17 подключены ко второму тактовому входу 25 преобразователя. Блок коррекции (фиг.2 содержит Д-триггер 26, прямой выход которого соединен через первый элемент 27 запрета и первый элемент ИЛИ 28 со входами шестого 29 и седьмого 30 элементов И-ИЛИ. Инверсный выход триггера 26 через второй элемент 31 запрета и второй элемент ИЛИ 32 соединен со входами первого элемента И 33, шестого 29 и восьмого 34 элементов И-ИЛИ и через второй элемент И 35 со входами элементов И-ИЛИ 30 и 34. Прямой выход второго Д-триггера 36 через третий элемент И 37 соединен со вторым входом элемента ИЛИ 32, С-входы Д-триггеров 26 и 36 соединены со входом динамического регистра 38, через элемент И-ЮШ 29 со входом третьего элемента ИЛИ 39 и с выходом четвертого элемента Ш1И 40, входы которого подключены ко второму тактовому входу 25 преобразова- теля и к выходу первого разряда динамического регистра 38. Выходы второго, третьего и четвертого разрядов подключены соответственно к вхо,дам элемента И-ИЛИ 34, элемента И 33 и элемента И-ИЛИ ЗО.Вьпсоды элементов И-ИЛИ 30 и 34 и элемента И 33 подключены ко входам третьего элемента ИЛИ 39, выход которого подключен ко входу сумматора 7. Д-вход триггера .26 подключен к выходу девятого элемента И-ИПИ 41, входы которого подключены к группе выходов блока 5 управления и по цепям 20 и 21 к выходам пятых разрядов сдвиговых регистров 1 и 2, Работа преобразователя осуществляется по циклам. Каждый цикл выполняется за п тактов. Длительность такта Т равна периоду следования импульсов фазового питания сдвиговых регистров. Временная диаграмма тактовых сигналов в системе низких отенциалов показана на фиг.4. Инексация тактов Т соответствзет номеру i разряда числа на выходе ервого (или на входе п -го разряда сдвиговых регистров, информация в которых циркулирует и записывается младщими разрядами вперед. Так, о время действия такта Т /| на выходе инамического регистра присутствует первый разряд записанного в регистре числа, во время действия такта - i -brii разряд. Начало каждо го цикла соответствует началу сигнала Т . Преобразователь может работать в четырех режимах Р1, Р2, РЗ и Р4. Режим Р1 обеспечивает преобразовани дробйого, а режим Р2 - целого числа из двоичной в двоично-десятичную систему счисления. В режиме РЗ пре образуются дробные, а в реяшме РА целые числа из двоично-десятичной в двоичную систему счисления. Работа преобразователя заключает ся в выполнении следующих операций: прием исходного кода, его преобразование и выдача преобразованного кода. Временная диаграмма управляющих сигналов, обеспечивающих выполн ние указанных операций, показана на фиг.5. По сигналу ПИК осуществля ется прием исходного кода, по сигна ПР - преобразование кода и по сигна лу ВД - выдача преобразованного кода. Сигналы ВЦ, К и К обеспечивают непосредственно режим преобразовани В зависимости от режима работы преобразователя блок 5 управления вы.рабатывает управляницие сигналы, которые являются модификацией базовых сигналов. Например, базовому сигналу ПИК в режиме Р1 соответствует сигнал ПИК 1, в режиме Р2 - ПИК2 и т.д.Длительность сигналов ПИК и ВД цикл, длительность сигнала ПР - 2п циклов. Сигналы ВЦ, К и К будут описаны ниже йри описании каждого режима работы преобразователя. Рассмотрим работу преобразователя в каждом из четырех режимов. Режим PI. По сигналу из блока 5 управления ПИК 1 двоичное дробное число последовательным кодом с млад ших разрядов записывается во второй сдвиговый регистр 2 через информационный вход I и элемент И-ИЛИ 4 (на фиг.З через элементы И 44 и ИЛИ 47). Преобразование кода осущес вляется за вспомогательных циклов ВЦ1и П циклов коррекции К1 (фиг.5} В первом такте (по тактовому сигналу Т1 , вход 25) калдого вспомогател ного цикла ВЦ во второй Д-триггер 17 записывается содержимое первого разряда сдвигойого регистра 2. В ка дом вспомогательном цикле ВЦ1, искл чая последний такт Т, цепи циркуляции информации сдвиговых регистро 1 и 2 цепями 18 и 15 замыкаются чер вторые разряды. taK, цепь циркуляци .регистра 1 имеет вид: выход 2-го 18 разряда регистра 1 - цепь 18 - элемент И-ИЛИ 3 (на фиг.З элементы И 48 и ШШ 53) - вход п -го регистра 1. Цепь циркуляции сдвигового регистра 2 имеет вид: выход 2-го разряда регистра . 2 - цепь 15 элемент И-ИЛИ 4 (на фиг.З элементы И 46 и ИЛИ 47 - вход регистра 2. Исключение последнего такта осуществляется подачей по входу 22 запрещающих сигналов Т. В последнем такте каждого вспомогательного цикла ВЦ1 ранее записанная информация из Д-триггера 17 через элемент И-ИЛИ 4 (на фиг.З через элементы И 43 и ИЛИ 47) переписывается в п -ьА разряд сдвигового регистра 2, а из Д-триггера 14 через входную схему 3 (на фиг.З через элементы И 51 и ШШ 53) - в п-ый разряд сдвигового регистра 1. Цикл коррекции К1 выполняется следу 01цим образом. Цепь циркуляции сдвигового регистра 2 замь кается через 1-й разряд и имеет вид: выход 1-го разряда регистра 2 - цепь 13 - элемент И-ИЛИ 4 (на фиг.З элементы И 45 и ИЛИ 47) - вход регистра 2. Цепь циркуляции сдвигового регистра 1 замыкается через первый разряд и одноразрядный сумматор 7 и имеет вид: выход 1-го разряда регистра 1 - третий вход элемента И-ИЛИ 8 (на второй вход которого по цепи 10 подается сигнал к) - второй вхйд одноразрядного сумматора 7 - выход сумматора 7 элемент И-ИЛИ 3 (на фиг.З элементы И 50 и ИЛИ 53) - вход сдвигового регистра Г. На первый вход сумматора 7 из блока 6 коррекций поступает код, который формируется следующим образом. В каждом 4 +1-м ( 0,1,2-,... m-l) такте цикла коррекции К1 блоком 6 коррекции по цепи 19 анализируется 4-ый разряд динамического регистра 1 и в зависимости от его содержимого формируется последовательный четырехразрядный код, который в 4 1+1-м, 4i +2-М, 4 +3-М и 4i +4-М тактах младшими разрядами вперед поступает на вход сумматора 7. При нулевом значении 4-го разряда в (4i+l)-M такте блок 6 коррекции вырабатывает код OOOOi при единичном значении - . код 1101. Сформированный таким образом код суммируется с кодом первого сдвигового регистра 1, поступающим с выхода элемента И-ИЛИ 8, при этом в каждом (4 { +1)-м такте выработка сигнала переноса в сумматоре 7 блокируется. После выполнения 2 п чередующихся циклов ВЦ1, KI в сдвиговом регистре I образуется соответствующий двоично-десятичный код, который снимается последовательным кодом по сигналу выдачи ВД 1 с выхода 1-го разряда регистра 1 (схемы выдачи кодов с регистров 1 и 2 не показаны) Режим Р2, Прием целого двоичного числа на сдвиговый регистр 2 осуществляется по сигналу ПИК 2 так же, как и в режиме Р1. Одновременно по сигналу ПИК 2 блоком 6 коррекции вырабатывается последовательный п -разрядный код 00110011...0011, который заносится через одноразрядньй сумматор 7 и элемент И-ИЛИ 3 (на фиг.З через элементы И 50 и ИЛИ 53) на сдвиговый регистр 1. На второй вход одноразрядного сумматора 7 при этом с выхода элемента И-ИЛИ 8 поступает нулевой код, В последнем такте цикла ПИК 2 и всех циклов коррекции К2 по сигналу Т п (вход 22) в одноразрядный сдви говьм регистр 23 через элемент И-ИЛИ 16 записывается код последнего п -го разряда числа регистра 2, во второй одноразрядный сдвиговый регистр 24 через элемент И-ИЛИ 12 - код п-го разряда числа регистра 1. Преобразование кода осуществляется также за и вспомогательных циклов и п циклов коррекции, В каждом вспомогательном цикле ВЦ 2 цепи цирку ляции информации в сдвиговых регистр 1 и 2 замыкаются через элементы И-ИЛИ 16 и 12 и одноразрядные сдвиговые регистры 23 и 24, Так, цепь циркуляци сдвигового регистра 1 имеет вид: выход 1-го разряда регистра 1 - второй вход элемента И-ИЛИ 16 (на третий вход которого поступает из блока 5 управления сигнал ВЦ 2) - одноразрядный сдвиговьй регистр 23 - элемент И-ШШ 3 (на фиг,3 элементы И 52 и ИЛИ 53) - вход сдвигового регистра 1 Цепь циркуляции второго сдвигового регистра 2 имеет вид: выход 1-го разряда регистра 2 - цепь 13 - второй вход элемента И-ИЛИ 12 (на третий вход которого поступает сигнал ВЦ 2 из блока 5 управления - одноразрядный сдвиговый регистр 24 - элемент И-ИЖ 4 (на фиг. 3 элементы И 42 и ИЛИ 47) - вход сдвигового регистра 2 При этом, что в первом такте каждого вспомогательного цикла ВЦ2 на вход первого сдвигового регистра .1 поступает содержимое vi -го разряда регистра 2, ранее записанное в одноразрядньгй регистр 23, а на вход второго сдвигового регистра 2 - содержимое Л-го разряда регистра 1, ранее записанное в одноразрядный регистр 24. Цепи циркуляции регистров 1 и 2 в цикле коррекции К2 такие же, как и в режиме Р1, Код, поступакяций на первый вход сумматора 7 в цикле коррекции К2, формируется следупцим образом, В каждом (4j такте и ,,..,w-2) циклов коррекции К2 блоком 6 коррекции по цепи 20 анализируется 5-ft разряд регистра 1 в 4 (т -1) +1 (м -3) -м такте по цепи 21 - 5-н разряд регистра 2, В первых п -I циклах коррекции при нулевом значении 5-го разряда блок 6 коррекции вырабатывает код 1101, при (единичном значении - код ООП, В последнем и -м цикле коррекции К2 f при нулевом значении 5-го разряда блок формирования коррекции вырабатывает код 1010, при единичном 0000, Сформированный код в цикле коррекции сумьшруется с кодом сдвигового регистра 1, при этом выработка сигнала переноса в каждом (4 +4)-м такте блокируется. Результат формируется после описанных ранее 2 п циклов ВЦ2 и К2 на регистре 1, Выдача результата осуществляется также, как и в режиме Р1, Режим РЗ, Б режиме РЗ двоичнодесятичный код дробного хщсла перед преобразованием в двоичный код предварительно преобразуется в двоично-деся- .тичный код с избытком 3, Это .преобразование осуществляется одновременно с приемом на первый регистр 1 следующим образом. По сигналу ПШС 3, поступающему по цепи 9 на вход элемента И-ИЛИ 8, информация со входа 11 через элемент И-ШШ 8 поступает на второй вход сумматора 7, На первьй вход сумматора 7 поступает п -разрядный код 00110011,,,0011, который формируется блоком 6 коррекции по сигналу ПИК 3, Сформированный на выходе сумматора 7 код с избытком 3 через элемент И-ИЛИ 3 (на фиг,3 через элементы И 50 и ИЛИ 53) поступает на вход регистра 1, Во второй динамический регистр заносится нулевой код. Преобразование осуществляется за 2 п циклов ВЦЗ, КЗ и КЗ f, таким же образом, как и в режиме Р2. Результат получается во втором регистре 2 и снимается с выхода -го разряда этого регистра последовательным кодом по сигналу ВДЗ (схема вьщачи тоже не показана)-. Режим Р4. Прием целого десятичног числа осуществляется по сигналу ПИК через элемент И-ИЛИ 3 (на фиг.З чере элемент И 49 и ИЛИ 53} на первый сдв говый регистр 1. На второй регистр 2 заносится нулевой код. Преобразование осуществляется за 2 циклов ВЦ4 и К4 таким же,образом, как и в режиме Р1. Выдача результата со второго регистра 2 такая же, как и в режиме РЗ. I . Блок 6 коррекции работает следующим образом. На Д-триггере 26 в каждом (4 i -«-I) -м такте по сигналам Т1, Т5,...,Т (П -7) и Т (п-3) через элемент И-ИЛИ 41 запоминается содержимое 5-го разряда первого 1 или вто рого 2 сдвиговых регистров. На тригг ре 36 в каждом (4i -Hj -м такте записывается содержимое 4-го разряда первого сдвигового регистра 1. На Свходы триггеров 26 и 36 подаются так тирующие сигналы Т .(4i +U , т.е. сигналы Т1, Т5,...Т (П -3), которые вырабатываются динамическим регистром 38. По сигналу TI через элемент ИЛИ 40 в регистр 38 записывается еди ница, которая циркулирует в нем на протяжении всей работы преобразовате ля. На выходе 4-го разряда регистра 38 образуются таким образом тактирую щие сигналы Т (4 +2), на выходе 3-го разряда - Т (4i +3) , на выходе 2-го разряда - Т (41 +4) и на выходе 1-го разряда - Т (4 +U . Как следует из описания работы преобразователя, в разных режимах логические формулы X условий выработки блоком коррекции соответствующих кодов имеют вид: ООН (f2V/(3J OaTVfU) УПИК 3: Xtfoi - KI ) С„ V//(2VK3J ( -/(2„УКЗн.) С. где Cj и Су - состояния триггеров 36 м 26. ,2 Условие Xjj вырабатывается на выходе элемента ИЛИ. 28, условие выходе элемента ИЛИ 32 и условие Ю10 выходе элемента И 35. На элементах И-ИЛИ 29,30 и 34, элементах И 33 и ИЛИ 39 совместно с динамическим регистром 38 осуществляется преобразование унитарного кода условий X в последовательный код соответствующих чисел ООП, 1101 и iOlO. Работа преобразователя в режиме Р1 при преобразовании числа 0,1010 0,6 из двоичной в двоично-десятичную систему счисления проиллюстрирована в табл.1, в режиме Р2 при преобразовании двоичного числа 01001011 - 75 в табл.2 (см.приложениеj. В графе 10 (выход блока 7} в скобках приведено значение переноса, сформированное в i-ом такте и учитываемое в i+1-ом такте. Квадратными скобками выделены переносы, выработка которых блокируется. Использование предлагаемого преобразователя обеспечивает сокращение аппаратурных затрат при м 40 в два раза. ЗцСр +l, L.. -I-- (2K+6jCp+4CV +Cs (2н +12) Cp 2 раза. При этом предполагается, что устройства вьшолняются из интегральных схем малой степени интеграции. При использовании средних и больших интегральных схем преимущества предлагаемого преобразователя проявляются в большей степени, поскольку известные устройства являются устройствами последовательно-параллельного действия, Б них невозможно использование сдвиговых регистров в интегральном исполнении на основе МДП структур ( серийно выпускаемых промышленностью, Предлагаемое устройство является устройством последовательного действия и применение в нем этих регистров позволяет значительно снизить стоимость, уменьшить габариты устройства и повысить его надежность .

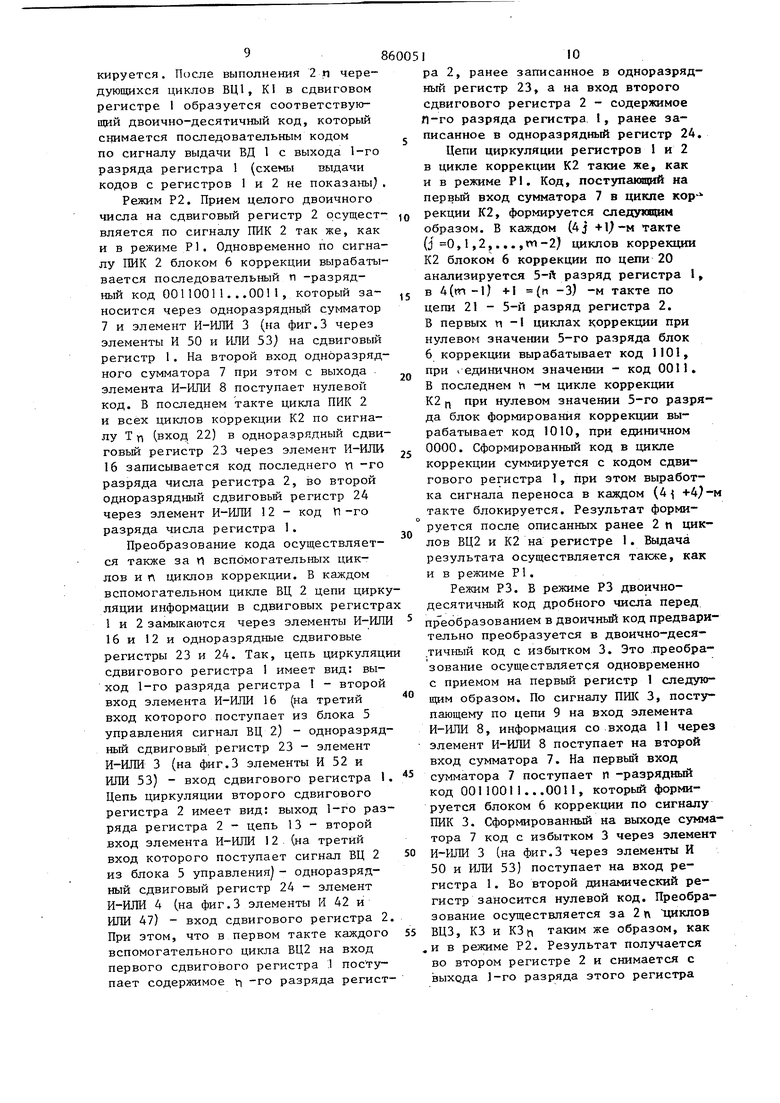

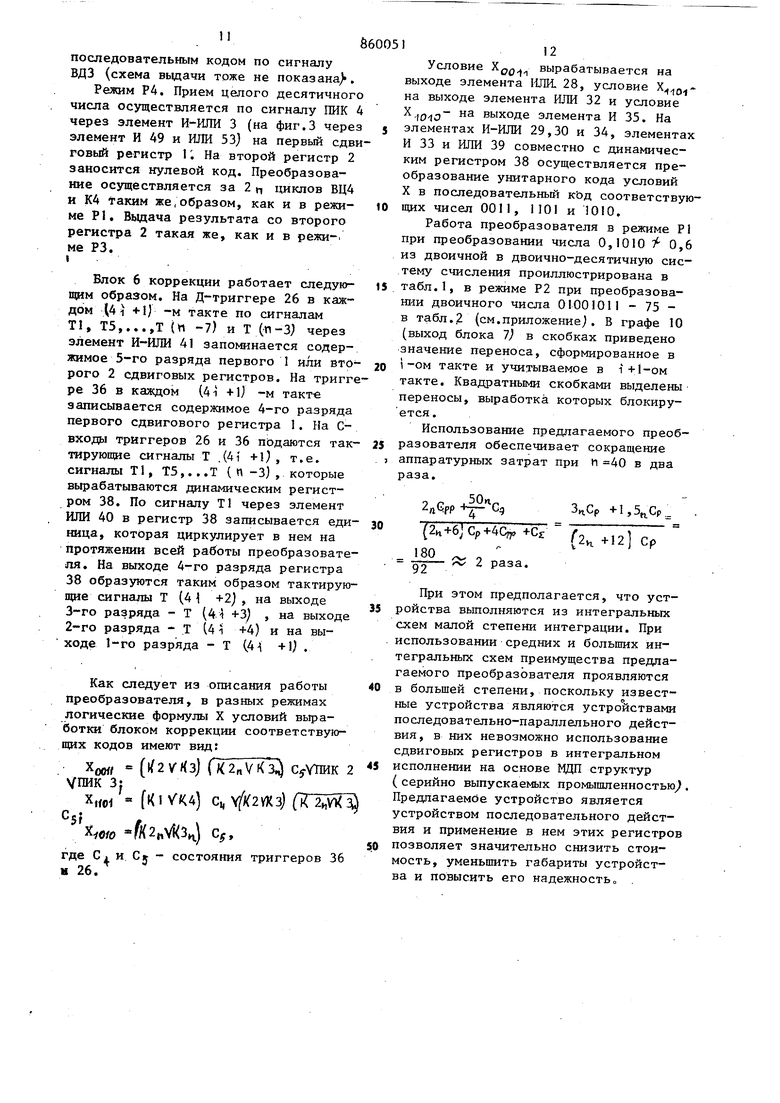

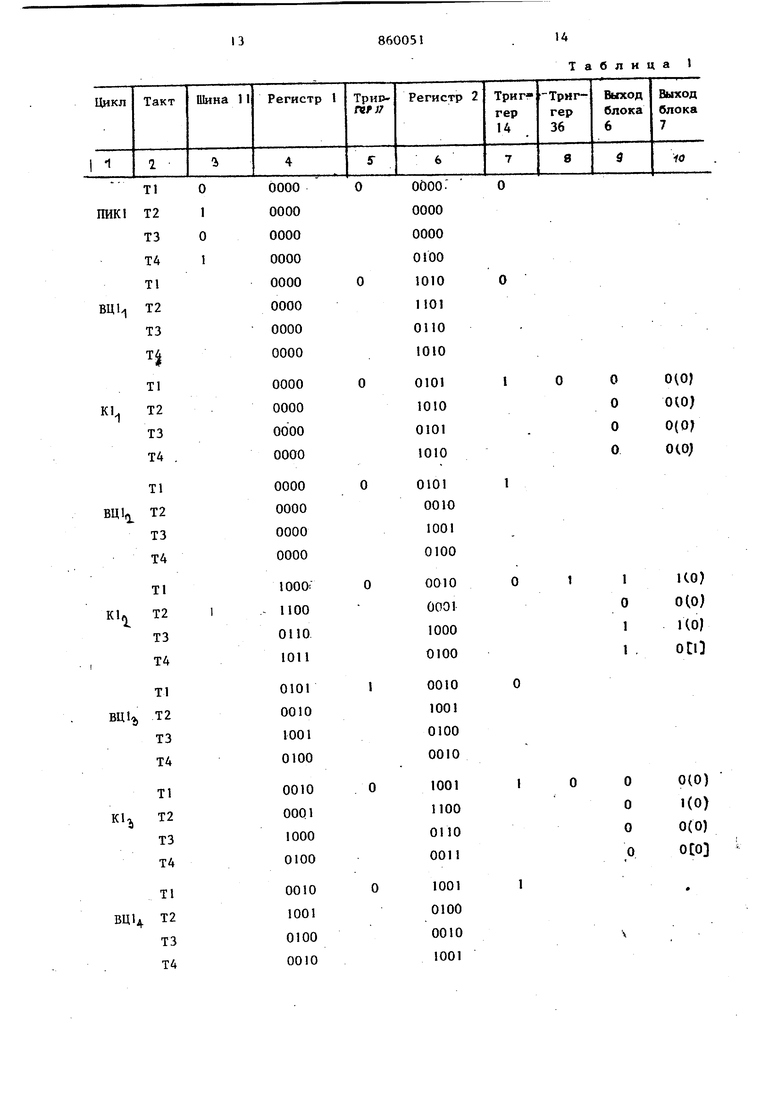

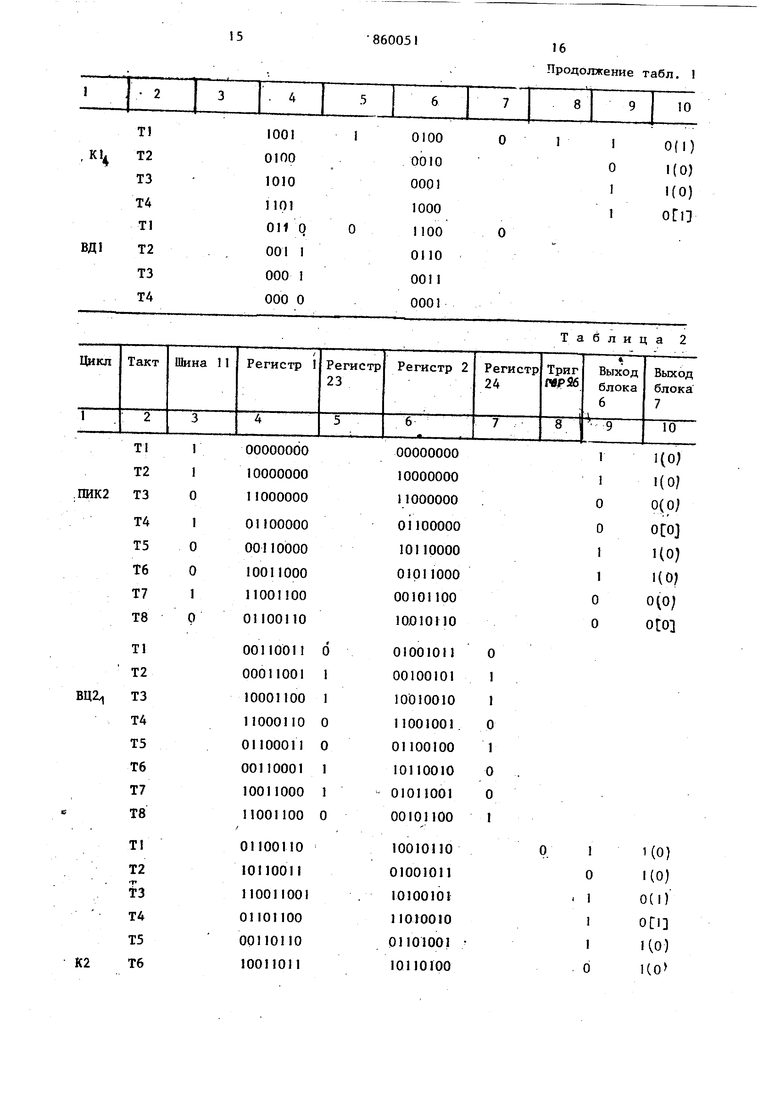

Таблица 1

15

86005 I

6

Продолжение табл. 1

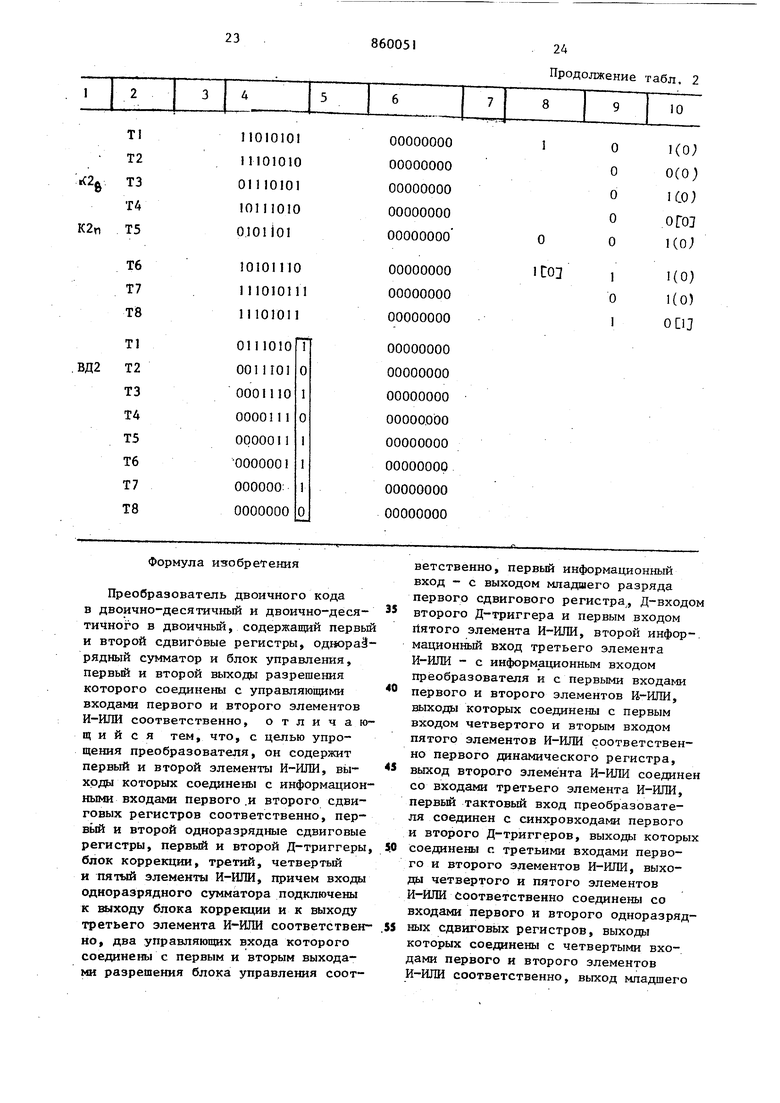

Продолжение табл. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый и дВОичНО-дЕСяТичНОгОВ дВОичНый | 1979 |

|

SU849197A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый и дВОичНО-дЕСя-ТичНОгО B дВОичНый | 1979 |

|

SU809155A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1975 |

|

SU708344A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1978 |

|

SU734669A1 |

| Преобразователь правильной двоично-десятичной дроби в двоичную дробь и целых двоичных чисел в двоично-десятичные | 1978 |

|

SU741260A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1962 |

|

SU717754A1 |

| Преобразователь двоичного кодаВ дВОичНО-дЕСяТичНый | 1978 |

|

SU809150A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

001100111

Т1

100110011 Т2 ТЗ Т4 Т5 Т6 Т7 Т8

11001100I

Ц2,

J11Q0110О

01110011о

OOlMOOlI

100 и 1001

11001 по о

01100111

Т1 00110011 Т2 ТЗ Т4 Т5 Т6 Т7 ТВ 00011001

юоопоо

2г

01000110 10100011 11010001 01101000

00110100о

Т1

00011010о

Т 2

00001101о

ТЗ

000001101

ТА

ВЦ2з

10000011о

Т5

01000011

Т6

10100001

Т7

11010000о

ТВ

01101000

TI 10110100

Т2 01011010

ТЗ 10101101

Т4

К2 01010110

Т5 101010П

Т6 11010101

Т7 01101010

ТВ

00110101 о

Т1

о

о

1

1

о

1 о G

0(1;

I

о

0(1

о 1 1 1

to;

of и

1(0)

о 1(0)

о 1

oti)

Ot)

о

о о

1

г

о

1

о

ко;

1 с

0(0

о I I 1 1(0

oti

1(0

(

Uo

о 1 1 о CD осп

о

Продолжение табл. 2

Т1

ВД2 Т2 ТЗ Т4 Т5 Т6 Т7 Т8 Формула изобретения Преобразователь двоичного кода в двоично-десятичный и двоично-десятичного в двоичный, содержащий первы и второй сдвиговые регистры, однораЗ рядный сумматор и блок управления, первый и второй выходы разрешения которого соединены с управляющими входами первого и второго элементов И-ИЛИ соответственно, отличаю щийся тем, что, с целью упрощения преобразователя, он содержит первый и второй элементы И-ИЛИ, выходы которых соединены с информацион ными входами первого .и второго сдвиговых регистров соответственно, первьй и второй одноразрядные сдвиговые регистры, первый и второй Д-триггеры блок коррекции, третий, четвертый и пятый элементы И-ИЛИ, причем входы одноразрядного сумматора подключены к выходу блока коррекции и к выходу третьего элемента соответствен но, два управляющих входа которого соединены с первым и вторым выходами разрешения блока управления соотПродолжение табл. 2

00000000 00000000 00000000 00000000 00000000

ооооооор

00000000 00000000 ветственно, первьй информационный вход - с выходом младшего разряда первого сдвигового регистра, Д-входом второго Д-триггера и первым входом йятого элемента И-ШШ, второй инфор-. мационный вход третьего элемента И-ИЛИ - с информ адионным входом преобразователя и с первыми входами первого и второго элементов И-ИЛИ, выходы которых соединены с первым входом четвертого и вторым входом пятого элементов И-ИЛИ соответственно первого динамического регистра, выход второго элемента И-ИЛИ соединен со входами третьего элемента И-ИЛИ, первьй тактовый вход преобразователя соединен с синхровходами первого и второго Д-триггеров, выходы которых соединены с третьими входами первого и второго элементов И-ИЛИ, выходы четвертого и пятого элементов И-ИЛИ соответственно соединены со входами первого и второго одноразрядных сдвиговых регистров, выходы которых соединены с четвертыми входами первого и второго элементов И-ИЛИ соответственно, выход младшего разряда второго сдвигового регистра соединен с пятым входом второго элемента И-ИПИ, со вторым входом четвертого элемента И-ИЛИ и Д-входом первого Д-триггера. второй тактовый вход преобразователя соединен с третьими входами четвертого и пятого элементов И-ИЛИ, четвертые входы которых соединены с первым и вторым выходами разрешения блока управления пятый вход первого элемента И-ШШ соединен с выходом одноразрядного сумматора, управляющий вход которого соединен со вторым выходом разрешения блока управления, группа выходов разрешения которого соединена с упра ляющей группой входов блока коррекции, первый информационный вход блок коррекции соединен с выходом четвертого разряда первого сдвигового регистра, а второй и третий информационные входы соединены с выходами пятых разрядов первого и второго сдв говых регистров соответственно. 2. Преобразователь по п.1, отличающийся тем, что в нем блок коррекции содержит два Д-тригге ра, динамический регистр, элементы И-ИЛИ, ИЛИ, И, элементы запрета, пер вые входы которых соединены с прямым и инверсным выходами первого Д-триггера соответственно, а выходы соединены с первыми входами первого и вто рого элементов ИЛИ, выход первого элемента ИЛИ соединен с первыми входами первого и второго элементов И- ИЛИ, а выход второго элемента ИЛИ соединен со вторым входом первого, первым входом третьего элементов И-ИЛИ и первым входом первого элемен та И, выходы первого, второго, третьего элементов И-ИЛИ и первого элемента И соединены со входами третьег 126 элемента ИЛИ, выход которого является выходом блока коррекции, выход первого разряда динамического регистра через четвертый элемент ИЛИ соединен с его входом, с синхровходаки первого и второго Д-триггеров и с третьим и четвертым входами первого элемента И-ИЛИ, выходы второго и четвертого разрядов динамического регистpa соединены со вторым и третьим входами второго и третьего элементов И-ИЛИ соответственноI четвертые входы которых через второй элемент И соединены с инверсным выходом первого Д-триггера, выход третьего разряда динамического регистра соединен со вторым входом первого элемента И, прямой выход второго Д-триггера через третий элемент И соединен со вторым входом второго элемента ИЛИ, Д-вход второго Д-триггера является первым информационШ)1М входом ; блока коррекции, а Д-вход первого Д-л-риггера соединен с выходом четвертого элемента Й-ИЛИ, первый и второй входы которого являются соответственно вторым и третьим информационными входами блока коррекции, вторые входц первого элемента ИЛИ, второго и тре тьего элементов И, первого и второго элементов запрета, эапреца 01цие входы элементов запрета, а также третий и четвертый входы четвертого элемента И-ШШ являются соответствующими входами управляющей группы входов блоха коррекции. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 201774, кл. ЦОбР 5/02, 1965. 2.Авторское свидетельство СССР по заявке № 2677100, кл. Q 06f 5/02, 20.10.78 (прототип/.

J(6n. пик 2 УПНКЗ

п ri

Г(П1}

Тп

nj IT-U-U-и-IT пик

Г

put.

in U r

Авторы

Даты

1981-08-30—Публикация

1979-01-22—Подача