1

ю

00 00

о о

коммутатор 8, (п+2)-разрядную входную-выходную шину 9 данных, двухразрядный кодовый вход 10 двух младших разрядов кода одного из сомножителей операции умножения кодов без знаков, вход 11 управления вводом данных, тактовый вход 12, входы 13 и 14 двухразрядного кода операции, вход 16 выбора устройства, информационные выходы 17-20 и управляющий выход 36. Устройство может быть использовано при

построении функционально ориентированных процессоров (ФОП) с программируемой обработкой информации, алгоритмы которых реализуются с широким использованием модификаций операций умножения и деления, например при построении ФОП группового управления векторными индикаторами комплекса средств отображения ин1- формации метеорадиолокатора. 2 з.п. ф-лы, 5 фиг., 3 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1990 |

|

SU1746378A1 |

| Цифровой генератор функций | 1989 |

|

SU1663607A1 |

| Устройство для деления | 1989 |

|

SU1619256A1 |

| Устройство для деления | 1988 |

|

SU1517026A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

| Устройство для умножения и деления | 1986 |

|

SU1376082A1 |

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Устройство для деления | 1986 |

|

SU1325467A1 |

Изобретение относится к области вычислительной техники и предназначено для выполнения операции умножения кодов без знаков, операции умножения в прямом коде, операции деления в прямом коде с авто9 (at) матическим определением делимого и делителя не меньшего делимого по модулю и операции деления в прямом коде с заданными делимым и делителем. Цель изобретения - расширение функциональных возможностей устройства за счет выполнения операции умножения кодов без знаков, операции умножения в прямом коде и операции деления в прямом коде с автоматическим определением делимого и делителя не меньшего делимого по модулю. Устройство содержит умножитель 1, блок 2 поразрядного кодирования и вход 15 начальной установки. Новым в устройстве является то, что оно содержит блок 3 управления, формирователь 4 информационных сигналов, первый 5 и второй 6 регистры, компаратор 7,

Изобретение относится к области вычислительной техники, предназначено для выполнения операции умножения кодов без знаков, операции умножения в прямом коде, операции деления в прямом коде с определением делимого и делителя не меньшего делимого по модулю делимому и операции деления в прямом коде, с заданными делимым и делителем и может быть использовано при построении функционально ориентированных процессов (ФОП) с программируемой обработкой информации, алгоритмы которых реализуются с широким использованием модификаций операций умножения и деления, например, при построении ФОП группового управления векторными индикаторами комплекса средств отображения информации метеорадиолокатора.

В структуре ФОП для метеорадиолокатора можно выделить шины данных (ШД), адреса (ША), управления (ШУ) и ряд устройств, в их числе устройство ввода-вывода, генератор знаков, генератор напряжений разверток, формирователь видеоимпульсов изображения, устройство синхронизации и временных программ, устройство программного управления, запоминающее устройство оперативной и постоянной информации, микропроцессор для выполнения логических и коротких арифметических операций и данное устройство для быстрого выполнения требуемых модификаций операций умножения и деления, с помощью которых в ФОП выполняются с требуемыми быстродействием и точностью все операции преобразования координат, например, прямоугольных координат в полярные координаты, полярных координат в прямоугольные координаты, прямоугольных координат при повороте осей, вычисление высоты и т.п.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения дополнительных возможностей выполнения операции умножения кодов без знаков, операции умножения в

прямом коде и операции деления в прямом коде с определением делимого и делителя не меньшего делимого по модулю.

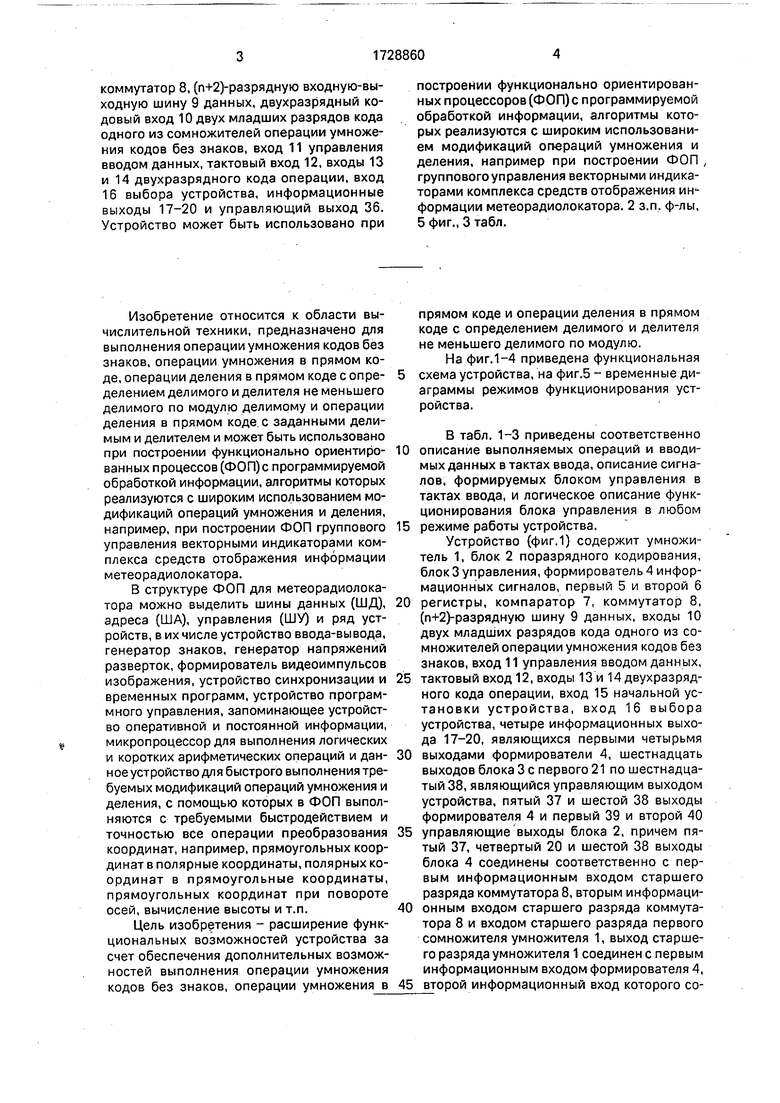

На фиг.1-4 приведена функциональная схема устройства, на фиг.5 - временные диаграммы режимов функционирования устройства.

В табл. 1-3 приведены соответственно

описание выполняемых операций и вводимых данных в тактах ввода, описание сигналов, формируемых блоком управления в тактах ввода, и логическое описание функционирования блока управления в любом

режиме работы устройства.

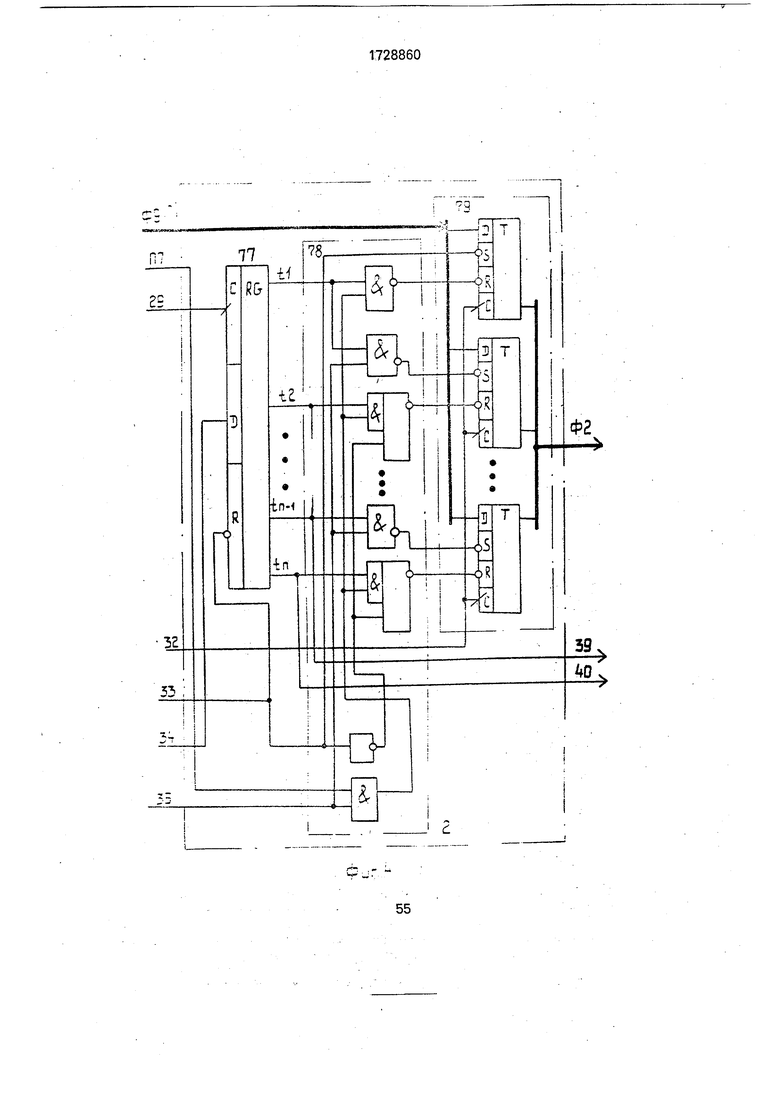

Устройство (фиг.1) содержит умножитель 1, блок 2 поразрядного кодирования, блок3 управления, формирователь 4 информационных сигналов, первый 5 и второй 6

регистры, компаратор 7, коммутатор 8, (п+2)-разрядную шину 9 данных, входы 10 двух младших разрядов кода одного из сомножителей операции умножения кодов без знаков, вход 11 управления вводом данных,

тактовый вход 12, входы 13 и 14 двухразрядного кода операции, вход 15 начальной установки устройства, вход 16 выбора устройства, четыре информационных выхода 17-20, являющихся первыми четырьмя

выходами формирователи 4, шестнадцать выходов блока 3 с первого 21 по шестнадцатый 38, являющийся управляющим выходом устройства, пятый 37 и шестой 38 выходы формирователя 4 и первый 39 и второй 40

управляющие выходы блока 2, причем пятый 37, четвертый 20 и шестой 38 выходы блока 4 соединены соответственно с первым информационным входом старшего разряда коммутатора 8, вторым информационным входом старшего разряда коммутатора 8 и входом старшего разряда первого сомножителя умножителя 1, выход старшего разряда умножителя 1 соединен с первым информационным входом формирователя 4,

второй информационный вход которого соединен с выходом компаратора 7, с первым управляющим входом блока 2 и с первым входом блока 3, остальные входы, с второго по девятый, которого соединены соответственно с входом 11 управления вводом данных, с тактовым входом 12, с входом 13. первого разряда кода операции, с входом 14 второго разряда кода операции, с входом 15 начальной установки устройства, с входом 16 выбора устройства и с первым 39 и вторым 40 управляющими выходами блока 2, выход коммутатора 8 соединен с шиной 9, входы-выходы младших (п+1) разрядов шины 9 соединены с входами младших разрядов первого сомножителя умножителя 1 и с первым информационным входом компаратора 7 и связаны через первый регистр 5 с вторым информационным входом компаратора 7, входы-выходы младших п разрядов шины 9 связаны через блок 2 с входами младших разрядов второго информационного входа коммутатора 8 и с входами стар- ших разрядов второго сомножителя умножителя 1, входы младших разрядов второго сомножителя умножителя 1 связаны через второй регистр 6 с входами 10 двух младших разрядов кода одного из сомножителей операции умножения кодов без знаков, выходы младших разрядов умножителя 1 соединены с входами младших разрядов первого информационного входа коммутатора 8, вход логического О устройства соединен с входом второго старшего разряда второго информационного входа коммутатора 8, первый выход 21 блока 3 соединен с синхровходом первого регистра 5, вход-выход старшего разряда шины 9 соединен с третьим информационным входом формирователя 4, синхровход, первый и второй управляющие входы которого соединены с вторым 22, с третьим 23 и с четвертым 24 выходами блока 3 соответственно, вход установки в О и синхровыход второго регистра 6 соединены соответственно с пятым 25 и шестым 26 выходами блока 3, седьмой 27 и восьмой 28 выходы которого соединены с входом управления округлением и с первым синхровыходом умножителя 1 соответственно, второй синхровход умножителя 1 соединен с первым синхровходом блока 2 и с девятым 29 выходом блока 3, десятый 30 и одиннадцатый 31 выходы которого соединены с первым и вторым управляющими входами коммутатора 8 соответственно, а второй синхровход,- вход начальной установки, второй управляющий вход и третий синхровход блока 2 соединены с двенадцатым 32, тринадцатым 33, четырнадцатым 34 и пятнадцатым 35 выходами блока 3 соответственно.

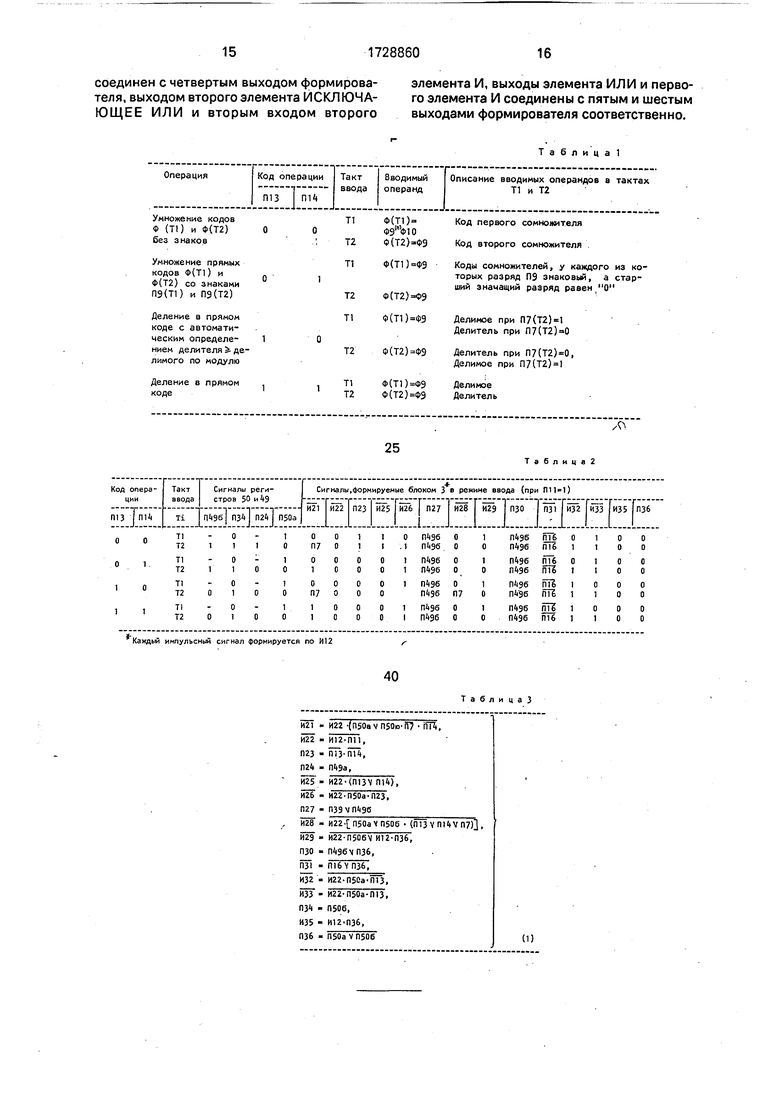

Блок 3 (фиг.2) содержит восемь элементов ИЛ И-НЕ (первый 41, седьмой 42. второй 43, третий 44, четвертый 45, пятый 46, восьмой 47 и шестой 48), буферный регистр 49,

двиговой регистр 50, шесть элементов ИЛИ (первый 51, четвертый 52, шестой 53, третий 54, второй 55 и пятый 56), четыре элемента И (первый 57, второй 58, четвертый 59 и третий 60), пять элементов И-НЕ (первый

0 61. второй 62, пятый 63, четвертый 64 и третий 65) и первый 66, второй 67 и третий 68 элементы НЕ.

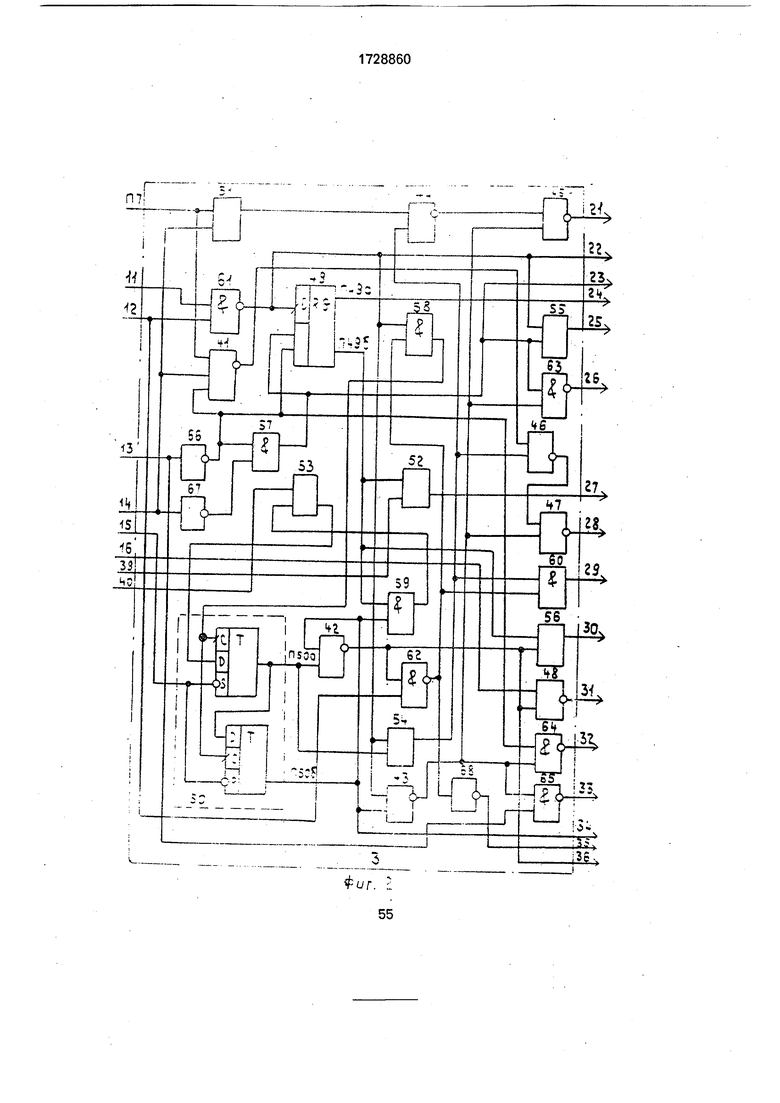

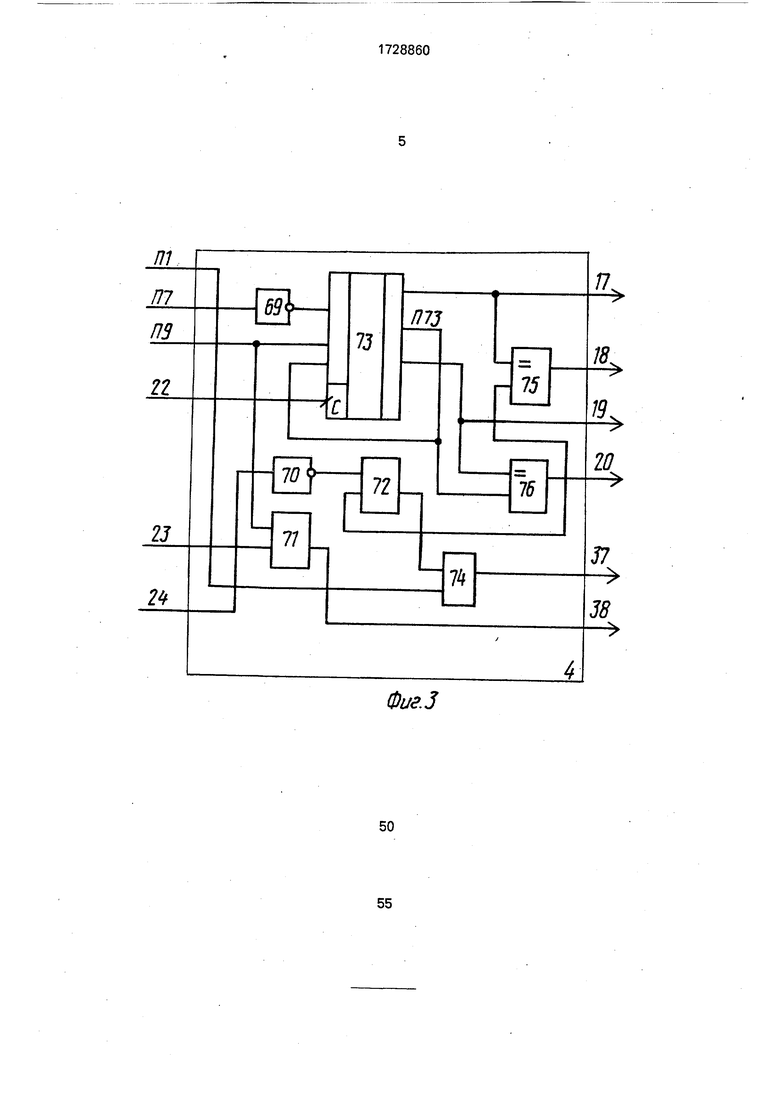

Формирователь 4 (фиг.З) содержит первый 69 и второй 70 элементы НЕ, первый 71

5 и второй 72 элементы И, регистр 73, элемент ИЛИ 74 и первый 75 и второй 76 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ.

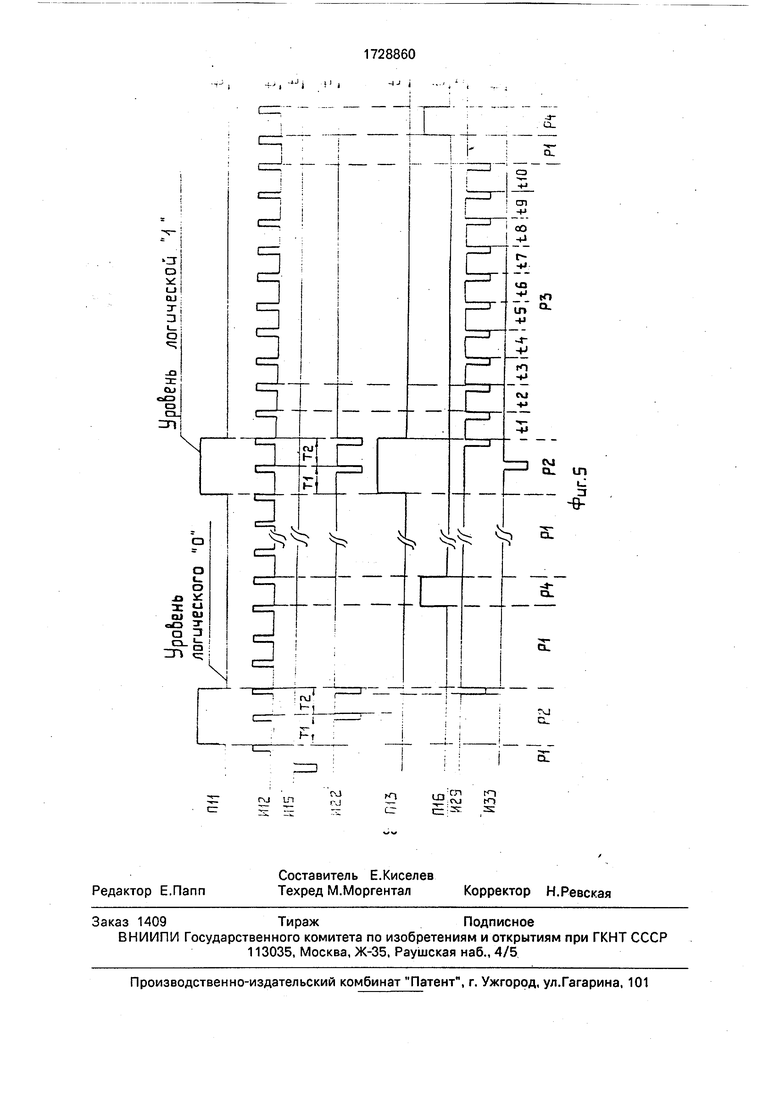

Блок 2 (фиг.4) содержит сдвиговый регистр 77, управляющий дешифратор 78 и

0 регистр 79 кода модуля частного.

Предлагаемое устройство реализовано для п 10 на ИС серий 530, 533 и 1802 так, что умножитель 1 представляет собой ИС 1802 В Р4, регистр 5 содержит две И С 533

5 ТМ9, регистр 6 выполнен на ИС 533 ТМ2, компаратор 7 содержит три ИС 533СП1, коммутатор 6 содержит три ИС 530КП11, каждый из регистров 49 и 50 выполнен на ИС 533 ТМ2, регистр 73 выполнен на ИС 533

0 ТМ9, регистр 77 содержит две ИС 533ИР8, регистр 79 содержит пять ИС 533 ТМ2, а остальные составные части устройства являются комбинационными элементами, выполненными на соответствующих ИС серий

5 530 и 533.

Умножитель 1 (ИС 1802ВР4) содержит первый и второй регистры сомножителей, триггер округления, блок умножения, сдви- гатель, регистры старшей и младшей частей

0 произведения, выходные буферные усилители, вход управления округлением, синх- ровходы записи информации в регистры и управляющие входы (на фиг.1 один не показаны), на которые поданы сигналы, обеспе5 чивающие функционирование умножителя 1 по модулям 12-разрядных сомножителей (они содержатся в первом и втором регистрах сомножителей умножителя 1) и комбинационную выдачу 12-разрядного произведения без

0 округления или с округлением от блока умножения через регистр старшей части произведения и выходные буферные усилители,. Обозначим на входах и выходах устройства и его узлов через Ф, П, П; И и И соот5 ветственно коды, прямые потенциальные сигналы, прямые импульсы и инверсные импульсы так, что после каждой из этих букв стоит, номер входа или выхода устройства или его узла или номер самого узла. например, Ф9, П11, П31, J/I12 и И15 означают

соответственно код Ф9 на шине 9, прямой потенциальный сигнал на входе 11, инверсный потенциальный сигнал на выходе 31 блока 3, прямые импульсы на входе 12 и инверсные импульсы начальной установки устройства на,входе 15, или, например, Ф2, П52 П27, П48 П31, И68 ИЗБ и И45 И21 означают код Ф2 на выходе блока 2, прямой потенциальный сигнал на выходе элемента 52, являющийся сигналом на выходе 27 блока 2, инверсный потенциальный сигнал на выходе элемента 48, являющийся сигналом на выходе 31 блока 3, прямые импульсы на выходе элемента 68, являющиеся импульсами на выходе 35 блока 3 и инверсные импульсы на выходе элемента 45, являющиеся импульсами на выходе 21 блока 3 соответственно.

Кроме того, обозначим через П9 разрядную цифру О или 1 старшего разряда кода Ф9, а через и Ф9 коды, образованные (п+1) и п младшими разрядами кода Ф9 соответственно, причем над наклонной чертой, пересекающей шины данных, в круглых скобках проставлена разрядность этих шин (фиг.1).

В процессе функционирования устройства загрузка регистров первого (Рг1) и второго (Рг2) сомножителей умножителя 1 (где через Рг1 и Рг2) обозначено содержимое регистров первого и второго сомножителей умножителя 1 соответственно), загрузка регистров 5, 6, 49, 73 и 79 и изменение содержимого сдвиговых регистров 50 и 77 производится по положите л ьнь1м ф р рнтам инвер с нь1х 11мпульсдв И28 и И29, И21, И26, И22,1/I22, И32 и И58 и И29 соответственно.

Временные программы поступления на устройство сигналов П11, П12, П13, П14, П15 и П16 и кодов Ф9 и Ф10 (при П11 1, П16 0) и съема с устройства кода Ф9 Ф8 (при П11 ОиП16 1) определяют функционирование устройства во времени так, что в его работе можно выделить следующие четыре режима (фиг.5): режим хранения (Р1) при П11 П16 0 и Ф50 10 П50аП50б; режим ввода (Р2) при П11 1 и Ф50 f 00, содержащий два временных такта Т1 и Т2, длительность каждого из которых равна длительности периода частоты следования тактовых импульсов И12, которую обозначим через Т™; режим (РЗ) выполнения операции деления при П11 О, Ф50 00 длительностью Тд п Т™; режим (Р4) вывода результата при П11 0, П16 1, Ф50 10.

Чередование режимов работы устройства (т.е. взаимосинхронизация его входных и выходных сигналов и кодов)обеспечивается устройством программного управления ФОП, например, на фиг.5 показано следующее чередование режимов работы устройства: Р1, Р2 при П13 0, Р1, Р4, Р1, Р2 при

П13 1,РЗ, Р1.Р4

С учетом изложенного работу предлагаемого устройства можно описать следующим образом, начиная с режима Р1.

При описании работы устройства необходимо иметь в,виду, что шина 9 является в ФОП мультиплексной ШД, т.е. в режиме

0 разделения времени любые устройства ФОП, имеющие входы-выходы на ШД, могут обмениваться между собой кодовой информацией.

В режим Р1 устройство первоначально

5 устанавливается по И15 0, фиксирующем регистр 50 в состоянии Ф50 10. В течение режима Р1 регистр 50 находится в состоянии Ф50 10, кодовый выход коммутатор 8 находится в третьем (высокоимпедансном)

0 состоянии по сигналу П31 1, а в памяти остальных узлов устройства содержится информация, обусловленная предысторией его функционирования.

В режиме Р2 ввода от соответствующих

5 устройств ФОП на данное устройство поступают сигнал П11 1, код П13П14 операции и коды ФЭиФЮ. В течение Т1 иТ2 режима Р2 код П13П14 неизменен и производится ввод в устройство с шин 9 и 10 двух операн0 дов в режиме разделения времени так, что первый Ф(Т1) и второй Ф(Т2) из них вводятся в тактах Т1 (при Ф50 10) и Т2 (при Ф50 01) соответственно. Описание вводимых операндов в тактах Т1 и Т2 в зависимости от

5 кода операции приведено в табл. 1, а в табл. 2 описано формирование сигналов, вырабатываемых блоком 3 в режиме Р2 ввода.

На основании фиг.2 и табл. 1 и 2 функционирование блока 3 в любом из режимов

0 описано выражениями (1), приведенными в табл. 3.

Согласно фиг.1-4 и табл.1-3 в такте Т1 код Ф9 1 заносится в регистр 5 по 1/121 О, код П38Ф9Л 1)() (где П38 ГНН123) зано5 сится в Рг1 умножителя 1 по Й28 0, при П23 1 код Ф10 заносится в регистр 6 по И26 0 (при П23 0 формируется Й25 О, устанавливающий регистр 6 в состояние Ф6 00), при код Ф9(Т1)(П) заносится в

0 регистр 79 по И32 0(при П13 1 формируется ИЗЗ 0, устанавливающий регистры 77 и 79 в состояния Ф77 0...0, Ф79 ICLJLB регистр 73 заносятся сигналы П69 П7(Т1), П9(Т1), П73(Т1) (где П/3 - сигнал с выхода

5 второго разряда регистра 73) по И22 0, в ре гистр 49 заносятся сигналы П57 П13-П14д 49б П66 П13 по И22 0, по первому И58 0 регистр 50 переключается в состояние Ф50 01 такта Т2, а в такте Т2 содержимое регистров 6 и 49 не изменяется,

при П7 П14 0 (в противном случае содержимое регистра 5 не изменяется регистр 5 заносится код Ф9(Т2)(п+1) по И21 0 (где сигнал П7 вырабатывает компаратор 7 так, что П7 1 при Ф9(п+1) Ф5 или П7 0 при фд(п+1) ф в регистр 73 заносятся сигналы П69 - П7(Т2), П9(Т2), П73 П9(Т1) по И22 0, при П13 1 и П14 П7 О содержимое Рг1 умножителя 1 не изменяется в противном случае в РН заносится код П38Ф9(Т2Г+1) по И28 0, в Рг2 и триггер округления умножителя 1 заносятся код Ф2Ф6 и сигнал Тр П27(Т2) П52 П39 V П496 соответственно, где Тр - сигнал О или 1, определяющий состояние триггера округления умножителя 1.

После окончания Р2 на устройство поступает сигнал П11 0, регистр 50 находится в состоянии Ф50 П53(Т2)0, формирователь 4 вырабатывает сигналы

(/П17 П7(Т2),

П18-П17а-;П20,

ч т9 П73(Т2) П9(Т1), П20 П9СГ1)©П9(Т2),

П20-П24, (2) в регистре 5 содержится код согласно выражению

Ф5 П14 П7(Т2) Ф9(Т1)(п+1) V П7(Т2)х хФ9(Т2)(п+1) V П14 Ф9(Т1Г+1),(3)

в Рг1 и Рг2 умножителям додержатся коды (Рг1) П13 П14 (Т2)

П38СГ2)Ф9(Т2)()У П13 П14 П7(Т2) П38(Т1)Ф9(Т1)(П+1)3,

(Рг2) Ф2(Т2)Ф6(Т2), .(4)

Ґ умножитель 1 вырабатывает код

Ф1 П1Ф1(п+1) Тр YoKP(PH)x

х (Рг2) (РП) (Рг2), (5) где Y YOKP - оператор операции умножения с округлением;

Y Y0i6 - оператор операции умножения с отбрасыванием.

Таким образом, после окончания Р2 при П496 П13 1 в РН и Рг2 умножителя 1 содержатся коды модулей сомножителей соответствующей операции умножения (табл. 1), регистр 50 находится в состоянии Ф50 10 и устройство может быть переведено в режим Р4, а при П496 0 в Рг2 умножителя 1 содержится код(Рг2) 10...О, в регистрах 5 и Рг1 содержатся коды модулей делимого и делителя соответственно, регистр 50 находится в состоянии Ф50 00 и устройство находится в режиме РЗ, поскольку вырабатывает управляющий сигнал П36 1, по которому устройство захватывает шину 9, т.е. выходы всех устройств ФОГ, подключенных к шине 9 по сигналу П36 1, переходят в третье состояние, кроме данно

го устройства, выдающего на шину 9 через коммутатор 8 код произведения

Ф$ Ф8 П37Ф1(п+1),(6)

код модуля которого сравнивается с кодом Ф5 выражение (3) модуля делимого на компараторе 7, вырабатывающего сигнал ( 1 при Ф1(п+1)Ф5

ОприФ1(п+1)4Ф5.(7)

В течение РЗ выполняется операция деления кода Ф5 выражение (3) модуля делимого на код (Рг1) выражение (4) модуля делителя. Эта операция выполняется за п тактов ti,.... tn поразрядного кодирования и

заключается в нахождении такого кода Ф2 (tj), при котором наиболее точно выполняется приближенное равенство при t9 П39. Ф5 -19 YOT6 (РП) (Рг2) - -t9 YOKp(Pr1)-(Pr2) 0(8)

так, что

Ф2 ,(Рг1),(9)

где Д - оператор деления кода Ф5 на код (РП).

В каждом такте tj кодирования блок 3

вырабатывает по импульсу И29 0 и ИЗБ 1, дешифратор 78 по сигналу (7) и непосредственно по И35 1 управляет переключением триггеров j и j+1 регистра 79 так, что триггер J+1 устанавливается в Г, атриггер при П7

(tj) 0 остается в 1, а при П7 (tj) 1 устанавливается в О. По окончании Й29 0 (т.е. по окончании такта tj) в Рг2 умножителя 1 загружается новый код Ф2, а регистр 77 переходит в состояние следующего такта

кодирования.

В течение последнего такта кодирования блок 2 вырабатывает сигнал П40 1, а в блоке 3 формируется сигнал П53 П40 V П59 1, поступающий на информационный вход

сдвигового регистра 50, на тактовом входе которого в каждом такте режимов Р2 и РЗ присутствует импульс И58 0. В этой связи в такте tn в регистре 79 формируется окончательно код Ф2 модуля частного, а после

окончания этого такта регистр 77 переключается в состояние Ф77 0...0, регистр 50 переключается в состояние Ф50 10 и режим РЗ заканчивается.

После окончания режима ввода (при

П496 1) или после окончания режима РЗ (при П496 0) устройство может быть переведено в режим Р4. В этом режиме от устройства на шину 9 выводится код

Ф9 Ф8 П496 П37Ф1(п+1) V

х П20-ОФ2,(10)

где П37 - разрядная цифра старшего значащего (при П24 1) или знакового (при П24 0) разряда кода произведения;

П20 - разрядная цифра знакового разряда кода частного.

Технико-экономическая эффективность предлагаемого устройства заключается в том, что оно по сравнению с известным обладает более широкими функциональными возможностями, поскольку известное устройство выполняет только одну операцию деления, а предлагаемое устройство позволяет выполнить по две модификации операций умножения и деления.

Формула изобретения

0 умножителя, вход младших разрядов второго сомножителя которого соединен с выходом второго регистра, информационные входы которого соединены с входами двух младших разрядов кода одного из сомножи5 телей операции умножения кодов без знаков устройства, вход логического нуля устройства соединен с вторым информационным входом второго старшего разряда коммутатора, первый и второй выходы бло0 ка управления соединены с синхровходами первого регистра и формирователя информационных сигналов соответственно, выход старшего разряда коммутатора через шину данных соединен с третьим информаци5 онным входом формирователя информационных сигналов, первый и второй управляющие входы которого соединены соответственно с третьим и четвертым выходами блока управления, пятый и шестой вы0 ходы которого соединены соответственно с входом установки в О и синхровходом второго регистра, седьмой и восьмой выходы блока управления соединены соответственно с входом управления округлением и с

5 первым синхровходом умножителя, второй синхровход которого соединен с первым синхровходом блока поразрядного кодирования и девятым выходом блока управления, десятый и одиннадцатый выходы

0 которого соединены соответственно с первым и вторым управляющими входами коммутатора, с двенадцатого по пятнадцатый выходы блока управления соединены соответственно с вторым синхровходом, входом

5 начальной установки, вторым управляющим входом и третьим синхровходом блока поразрядного кодирования, шестнадцатый выход блока управления соединен с выходом признака окончания работы устройст0 ва.

5 ИЛИ, четыре элемента И, пять элементов И-НЕ, три элемента НЕ, причем первый вход блока соединен с первыми входами первых элементов ИЛИ-НЕ и ИЛИ, второй вход блока соединен с первым входом пер- вого элемента И-НЕ, второй вход которого

соединен с первым входом второго элемента И-НЕ и с третьим входом блока, четвертый вход которого соединен с входом первого элемента НЕ и первым входом третьего элемента И-НЕ, пятый вход блока соединен с входом второго элемента НЕ и вторыми входами первых элементов ИЛИ- НЕ и ИЛИ, шестой вход блока соединен с входом начальной установки сдвигового регистра, выходы первого и второго элементов НЕ соединены с первым и вторым входами соответственно первого элемента И, первый вход которого соединен с третьим входом первого элемента ИЛИ-НЕ, первым входом четвертого элемента И-НЕ и информационным входом младшего разряда буферного регистра1, информационный вход старшего разряда которого соединен с выходом первого элемента И и первыми входами второго элемента ИЛИ и пятого элемента И-НЕ и.является третьим выходом блока, выход первого элемента И- НЕ соединен с синхровходом буферного регистра, первыми входами второго элемента И, третьего элемента ИЛИ, второго элемента ИЛ И-Н Е, вторым входом второго элемента ИЛИ и является вторым выходом блока, выход первого элемента ИЛИ соединен с первым входом третьего элемента ИЛИ- НЕ, выход которого соединен с первым входом четвертого элемента ИЛИ-НЕ, выход которого соединен с первым выходом блока, выход первого элемента ИЛИ-НЕ соединен с первым входом пятого элемента ИЛИ-НЕ, второй вход которого соединен с выходом третьего элемента ИЛИ, вторым входом третьего элемента ИЛИ-НЕ и первым входом третьего элемента И, второй вход которого соединен с выходом второго элемента И-НЕ, вторым входом второго элемента И и входом третьего элемента НЕ, выход которого соединен с пятнадцатым выходом блока, выход старшего разряда буферного регистра соединен с четвертым выходом блока, пятый выход которого соединен с выходом второго элемента ИЛИ, выход младшего разряда буферного регистра соединен с первыми входами четвертого и пятого элементов ИЛИ и четвертого элемента И, выход которого соединен с первым входом шестого элемента ИЛИ, второй вход которого соединен с девятым входом блока, восьмой вход которого соединен с вторым входом четвертого элемента ИЛИ, выход которого соединен с седьмым выходом блока, седьмой вход которого соединен с первым входом шестого элемента ИЛИ-НЕ, второй вход которого соединен с вторыми входами пятого элемента ИЛИ и второго элемента И-НЕ, выходом седьмого элемента ИЛИНЕ и является шестнадцатым выходом блока, выход второго элемента И соединен с синхровходом сдвигового регистра, выход старшего разряда которого соединен с первым входом седьмого элемента ИЛИ-НЕ и вторым входом третьего элемента ИЛИ, выход младшего разряда сдвигового регистра соединен с вторыми входами второго и седьмого элементов ИЛИ-НЕ, четвертого

0 элемента И и является четырнадцатым выходом блока, выход шестого элемента ИЛИ соединен с информационным входом сдвигового регистра, выход второго элемента ИЛИ-НЕ соединен с вторыми входами

5 третьего, четвертого и пятого элементов И- НЕ, четвертого элемента ИЛИ-НЕ, первым входом восьмого элемента ИЛИ-НЕ, второй вход которого соединен с выходом пятого элемента ИЛИ-НЕ, выход пятого элемента

0 И-НЕ соединен с шестым выходом блока, выходы восьмого элемента ИЛИ-НЕ, третьего элемента И, пятого элемента ИЛИ и шестого элемента ИЛИ-НЕ соединены с восьмого по одиннадцатый выходы блока

5 соответственно, выходы четвертого и третьего элементов И-НЕ соединены с двенадцатым и тринадцатым выходами блока соответственно.

0 формирователя соединен с вторым информационным входом регистра и с первым входом первого элемента И, второй вход которого соединен с первым управляющим входом формирователя, второй управляю5 щий вход которого соединен через второй элемент НЕ с первым входом второго элемента И, выход которого соединен с вторым входом элемента ИЛИ, синхровход формирователя соединен с синхровходом регист0 ра, первый выход которого соединен с первым входом первого.элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и первым выходом формирователя, второй выход регистра соединен с третьим информационным входом регистра

5 и первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с третьими выходами регистра и формирователя, второй выход которого соединен с выходом первого элемента ИСКЛ Ю- ЧАЮЩЕЕ ИЛИ, второй вход которого

соединен с четвертым выходом формирователя, выходом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и вторым входом второго

Делитель при П7(Т2)0

Т2 Ф(Т2)Ф9 Делитель при П(Т2)0, Делимое при П7(Т2)1

Т1 Ф(Т1)Ф9 Делимое Т2 Ф(Т2)Ф9 Делитель

Каждый импульсный сигнал формируется по И12

элемента И, выходы элемента ИЛИ и первого элемента И соединены с пятым и шестым выходами формирователя соответственно.

Т а б л и ц а 1

Тэблица2

ТаблицаЗ

Фиг. :

55

Фие.З

| Арифметическое устройство | 1986 |

|

SU1363186A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления | 1987 |

|

SU1441389A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-04-23—Публикация

1990-01-29—Подача