1

Изобретение относится к а.втома - тике и вычислительной технике и может быть использовано при разработке технических средств автоматики и ЭВМ для сравнения двух чисел, синхронно поступающих в прямом последовательном двоичном коде.

ЦЕЛЬ изобретения - расширение области применения устройства за счет возможности сравнения чисел, поступающих старшими разрядами вперед.

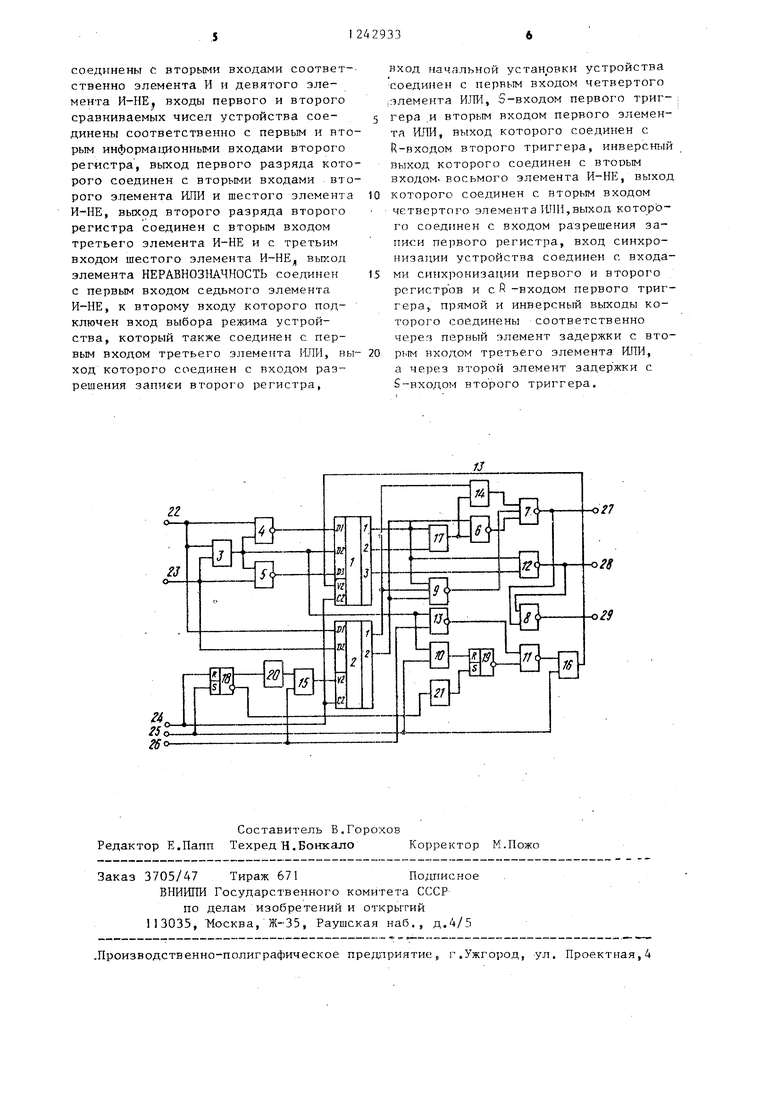

На чертеже приведена схема устройства.

Устройство содержит регистры 1 и элемент НЕРАВНОЗНАЧНОСТЬ 3, элементы И-НЕ 4-12, элементы ИЛИ 13 - 16, элемент И 17, триггеры 18 и 19, элементы 20 и 21 задержки, входы 22 и 23 первого и второго сравниваемых чисел, вход 24 синхронизации, вход

25 начальной установки, вход 26 выбор режима, выходь1 Меньше 27, Равно 28 и Больше 2У.

Устройство, работает следующим образом.

В исходное состояние устройство Приводится импульсом по входу начальной установки, при этом триггер 18 устанавливается в единичное, а триггер 19 - в нулевое состояния. Поскольку на- входах 22 и 23 - логические нули, то в регистры I и 2 записываются-соответственно числа 101 и 00, Если на входе 26 выбора режима логический нуль, это означа- ет, что числа поступают старшими разрядами вперед, а если единица - то младшими. В обоих случаях числа представлены в прямом последовательном двоичном коде со знаком, располо- женным в старшем разряде, причем каждый разряд стробируется импульсом по входу 24 синхронизации.

Если на входе 26 выбора режима - логическая единица, то она через эле мент ИЛИ 15 поступает на вход разрешения записи регистра 2, поэтому в этот регистр записьшаются значения последних поступивших разрядов,, т,е. знаковых разрядов.

35 40

2933 2

Поскольку триггер 19 установлен в нулевое состояние, то на выходе элемента И-НЕ 11 - единица только тогда, когда единица и на выходе

5 элемента НЕРАВНОЗНАЧНОСТЬ 3. Логическая единица через элемент ИЛИ 16 iпоступает на вход разрешения записи регистра I, поэтому в регистре 1 находится код ПО, если в последнем

0 из неравных разрядов а ; Ь , код ОП , если 01 Ь , и 101, если числа А и В равны (число А поступает по входу 22, число В - по входу 23).

Если же на входе 26 выбора режи 5 ма - лог5игческий нуль, то в регистр 2 записываются первые, т.е. знаковые разряды, а затем задним фронтом импульса синхро низации триггер 18 устанавливается в нулевое состояние

20 (а за ним и триггер 19 устанавливается в единичное состояние, и на входе разрешения записи регистра 2 имеется лог ический нуль. Нулевой сигнал с инверсного выхода триггера

2- 19 обеспечивает запись в регистр 1 первых же несовпавших разрезов чисел А и В (в приведенном выше коде), а затем сигналом с выхода элемента НЕРАВНОЗНАЧНОСТЬ 3 через элемент

30 ИЛИ 10 триггер 19 устанавливается в нулевое состояние. Это состояние триггера запрещает дальнейшую запись в регистр 1.

Таким образом, при поступлении чисел как младшими, так и старшими разрядами вперед, в регистре 2 находятся значения знаковых ра.зрядов чисел, а в регистре 1 - код, соответствующий соотношению самых старши (возможно, знаковых, при их неравенстве) неравных разрядов. При этом код 110 соответствует случаю, когда в самом старшем из неравных разрядов

, 101 - нет.

Возможные случаи соотношения сравниваемых чисел указаны в таблице. Точка отделяет знаковый разряд, X - безразличное состояние разряда.

1.Ь

С1 : ь код 011 - когда сл если несовпавших разрядов

1) Несовпавших разрядов нет. .2) Самые старшие несовпавшие разряТаким образом, устройство обеспечивает сравнение двух чисел в прямом последовательном двоичном коде, поступаю1 (йх как старшими, так и младшими разрядами .вперед.

Формула изобре. тения

Устройство для сравнения двоичных чисел, содержащее элемент неравнозначности, первый, второй, третий четвертый, пятый, шестой, седьмой и восьмой элементы И-НЕ, первый и второй элементы ИЛИ и элемент И, причем вход первого сравниваемого числа устройства соединен с первым и входами элемента НЕРАВНОЗНАЧНОСТЬ и перво го элемента И-НЕ, вход второго сравнваемого числа устройства соединен с первым входом второго элемента И-НЕ и вторым входом элемента НЕРАВНОЗНАЧНОСТЬ, выход которого соединен с первым входом первого элемента ИЛИ, выход элемента И соединен с пер . выми входами второго элемента ИЛИ и третьего элемента . выход которого соединен с первым входом четвертого элемента И-НЕ, выход которого является выходом Меньше устройства и соединен с перйым вхо

знаковые.

дом пятого элемента И-НЕ, выход которого является выходом Больше устройства, второй и третий входы четвертого элемента И-НЕ подключены соответственно к выходам шестого элемента И-НЕ и второго элемента ИЛИ, выход седьмого элемента И-НЕ соединен с первым входом восьмого элемента И-НЕ, отличающеес я тем, что, с целью расширения области его применения за счет возможности сравнения чисел, поступающих старшими разрядами вперед, в него введены первый и второй регистры, третий и четвертый элементы ИЛИ, первый и второй триггеры и первый и второй элементы задержки, причем выходы первого элемента И-НЕ, элемента НЕРАВНОЗНАЧНОСТЬ и второго элемента И-НЕ соединены соответственно с первым, вторым и третьим информационными входами первого регистра, выход перво- го разряда которого соединен с первым входом элемента И и первыми входами шестого и девятого элементов И-НЕ, выход девятого элемента И-НЕ является выходом Равно устройства и соединен с вторым входом пятого элемента И-НЕ, выходы второго и третьего разрядов первого регистра

соединены с вторыми входами соответ-- ственно элемента И н девятого элемента И-НЕ входы первого и второго сравниваемых чисел устройства сое- динены соответственно с первым и вторым информа1дионными входами второго регистра, выход первого разряда которого соединен с вторыми входами второго элемента ИЛИ и шестого элемента И-НЕ, выход второго разряда второго регистра соединен с вторым входом третьего элемента И-НЕ и с третьим входом шестого элемента И-НЕ, выкод элемента НЕРАВНОЗНАЧНОСТЬ соединен с первым входом седьмого элемента И-НЕ, к второму входу которого подключен вход выбора режима устройства, который также соединен с первым входом третьего элемента ИЛИ, вы- ход которого соединен с входом разрешения записи второго регистра,

Составитель В.Горохов Редактор Е.Папп Техред Н.Бонкало Корректор

Заказ 3705/47 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Носква, Ж-35, Раушская наб., д.4/5

.Производственно-полиграфическое пре;щриятие, г.Ужгород, ул. Проектная,4

вход начальной установки устройства соединен с первым входом четвертого .элемента ИЛИ, 5-входом первого триг- гера .и вторым входом первого элемента ИЛИ, выход которого соединен с R-входом: второго триггера, инверст 1й выход которого соединен с ВТОРЫМ входом- восьмого элемента И-НЕ, выход которого соединен с вторым входом четвертого элемента ИПИ,выход которого соединен с входом разрешения записи пе твого регистра, вход синхронизации устройства соединен с входами синх юнизации первого и второго регистров и с R -входом первого триггера,, прямой и инверсный выходы которого соединены соответственно через первый элемент задержки с вторым входом третьего элемента ИЛИ, а через второй элемент задер жки с -входом второго триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для спектрального анализа | 1984 |

|

SU1241256A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ В ТРОИЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ НА НЕЙРОНАХ | 2010 |

|

RU2453900C2 |

| Устройство для определения фазы спектральных составляющих | 1982 |

|

SU1080148A1 |

| Устройство для алгебраического сложения чисел | 1986 |

|

SU1339552A1 |

| Устройство для выполнения векторно-скалярных операций над действительными числами | 1990 |

|

SU1718215A1 |

| Устройство для деления чисел | 1981 |

|

SU1119006A1 |

| Параллельно-последовательный сумматор-вычитатель старшими разрядами вперед на нейронах | 2019 |

|

RU2708501C1 |

| Устройство для вычисления разности двух чисел | 1987 |

|

SU1444753A1 |

| Параллельный сумматор-вычитатель на элементах нейронной логики | 2020 |

|

RU2780299C2 |

| Устройство для выполнения векторно-скалярных операций над действительными числами | 1990 |

|

SU1728861A1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке технических средств автоматики и ЭВМ для сравне- ния двух чисел, синхронно поступаюiщих в прямом последовательном двоичном коде. Цель изобретения - расширение области применения устройства за счет возможности сравнения чисел, поступающих как младшими, так и старшими разрядами вперед. С этой целью в устройство введены два регистра, два триггера, элементы задержки, злементы ИЛИ. Режим поступления чисел (старшими/младшими разрядами вперед) задается сигналом на входе выбора режима. В любом случае в первом регистре по окончании передачи числа находятся значения самых старших (возможно, знаковых) разрядов чисел, а во втором - значения знаковых разрядов. Логическая схема из элементов И, ИЛИ, И-НЕ преобразует коды в сигнал нулевого уровня на одном из трех выходов устройства - Больше, 1 табл. Равно, Меньше. 1 ил. с S (Л 1C 4i QD СО СО

| Устройство для сравнения двоичных чисел | 1974 |

|

SU485445A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Устройство для сравнения двоичных чисел | 1976 |

|

SU635485A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-07—Публикация

1984-09-21—Подача