Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных вычислительных системах для аппаратной реализации векторно-скалярных операций умножения и деления чисел, представленных в прямом коде в форме с фиксированной запятой. Компоненты Х| вектора X (Щ 1,

2L }) и скаляр Y являются (п+1)-разрядными двоичными числами, представленными в прямом коде. В старшем (нулевом) разряде фиксируется знак числа, в разрядах с первого по п-й - модуль числа. ,1Hfe{1.2,..., L}:iyU 1/2.Ц Известно устройство для выполнения операций умножения и деления, содержащее блок приема и выдачи, регистр, блок суммирования, мультиплексор, блок управления, блок формирования признака активности, счетчик циклов, дешифратор, коммутатор, элементы 2И-ИЛИ. И, ИЛИ,

НЕ, ИСКЛЮЧАЮЩЕЕ ИЛИ и триггер с соответствующими связями 1.

Недостатками известного устройства являются низкое быстродействие и ограниченные функциональные возможности, обеспечивающие одновременную обработку только двух операндов.

Наиболее близким по технической сущности к предлагаемому является устройство для параллельного деления чисел, содержащее L+1 операционных блоков (L - количество компонентов векторного операнда), триггер знака, блок управления 2.

Недостатками данного устройства являются ограниченные функциональные возможности, обеспечивающие выполнение только векторно-скалярной операции деления.

Цель изобретения - расширение функциональных возможностей за счет выполне00

го ел

ния операции векторно-скалярного умножения L множимых на один множитель.

Цель достигается тем, что в устройство для выполнения векторно-скалярных операций над действительными числами, со дер- жащее L+1 операционных блоков (L - количество компонентов векторного операнда) и блок управления, причем вход 1-го

компонента векторного операнда (1е{1, 2

L } ) соединен с первым информационным входом 1-го операционного блока, первый и второй выходы которого соединены соответственно с выходами i-ro компонента вектора результата и 1-го признака переполнения устройства, вход запуска и тактовый вход которого соединены соответ- ственно с входом запуска и тактовым входом блока управления, первый выход которого соединен с выходом признака конца операции устройства и входом разрешения счета каждого операционного блока, вход разрешения записи каждого операционного блока соединен с вторым выходом блока управления, третий выход которого соединен с выходом признака деления на нуль устройства, второй информационный вход каждого операционного блока соеди- нен с четвертым выходом блока управления, введен вспомогательный операционный блок, вход разрешения счета которого соединен с первым выходом блока управления, вход промежуточного кода которого соединен с выходом вспомогательного операци- онного блока, первый информационный вход которого соединен с пятым выходом блока управления, второй выход которого соединен с входом разрешения записи вспомогательного операционного блока, второй информационный вход которого соединен с четвертым выходом ()-го операционного блока, входы множителя-делителя и кода операции устройства соединены соответственно с входами множителя-делителя и кода операции блока управления, шестой выход которого соединен с входом формирования знака 1-го операционного блока, вход признака умножения на ноль которого соединен с седьмым выходом блока управления, восьмой выход которого со- единен с первым информационным входом (L+1)-ro операционного блока, входы признака умножения на ноль, формирования знака и тактовый вход которого соединены с входом логического О устройства, вход запуска которого соединен с тактовым входом 1-го операционного блока, третий выход которого соединен с выходом знака 1-го компонента вектора результата устройства.

Цель достигается также тем, что опера- ционный блок содержит элемент НЕРАВНОЗНАЧНОСТЬ, мультиплексор, триггер знака, регистр, элемент И, сдвигатель и сумматор, выход которого соединен с первым информационным входом мультиплексора, второй информационный вход которого соединен с первым информационным входом блока, вход признака умножения на ноль которого соединен с первым входом элемента И, второй вход которого соединен с выходом регистра, входом первого слагаемого сумматора, информационным входом сдвигателя и вторым выходом блока, вход формирования знака которого соединен с первым входом элемента НЕРАВНОЗНАЧНОСТЬ, второй вход которого соединен с входом знакового разряда первого информационного входа блока, вход разрешения Счета которого соединен с управляющим входом мультиплексора, выход которого соединен с информационным входом регистра, вход записи которого соединен с входом разрешения записи блока, тактовый вход которого соединен с тактовым входом триггера знака, информационный вход которого соединен с выходом элемента НЕРАВНОЗНАЧНОСТЬ, а выход - с третьим выходом блока, первый выход которого соединен с выходом элемента И, а четвертый выход - с входом второго слагаемого сумматора и выходом сдвигателя, вход управления сдвигом которого соединен с вторым информационным входом блока.

Цель достигается также тем, что вспомогательный операционный блок содержит мультиплексор, регистр и сумматор, выход которого соединен с первым информационным входом мультиплексора,второй информационный вход которого соединен с первым информационным входом блока, вход разрешения счета которого соединен с управляющим входом мультиплексора, выход которого соединен с информационным входом регистра, выход которого соединен с выходом блока и входом первого слагаемого сумматора, вход второго слагаемого которого соединен с вторым информационным входом блока, вход разрешения записи которого соединен с входом записи регистра.

Сопоставимый анализ заявляемого решения с прототипом показывает, что заявляемое устройство отличается от известного набором блоков и связями между ними, приводящими к получению положительного эффекта, в силу чего предложенное техническое решение соответствует критерию изобретения новизна.

Неизвестно использование указанной выше совокупности отличительных признаков в других объектах аналогичного назначения, которая в сочетании с совокупностью известных признаков обеспечивает возможность получения положительного эффекта, в силу чего предложенное техническое решение соответствует критерию изобретения существенные отличия.

Все элементы заявляемого устройства могут быть выполнены на серийно выпуска- емых микросхемах, в силу чего предложенное решение соответствует критерию изобретения техническое решение задачи.

Работа устройства основана на использовании итерационных алгоритмов умножения и деления, реализующих мультипликативный метод вычислений.

Устройство реализует векторно-скаляр- ные операции умножения и деления чисел, представленных в прямом коде и форме с фиксированной запятой. Компоненты Xi векторного операнда X (1с{1,2L}), скалярного операнда Y и компоненты Zi векторного результата Z являются (п+1)-разрядными двоичными числами, представленными в прямом коде. В старшем (нулевом) разряде фиксируется знак числа, в разрядах с первого по п-й - модуль числа.

utie tfCiiadeLo vfc4U,...,tf,.M:

Тип выполняемой операции определяется кодом операции д&{ 0,1} . При уст-7Х|

роиство производит вычисления Zi -y- ,

при - вычисления -YVit{1,2L}.

Обе операции выполняются с использованием рекуррентных соотношений

,.,Щ

.,-2 lK. ,a2l., .

аьк-ои.лэцк.

о,., Ьк., ; .,.,,.,-,

где k - номер выполняемой итерации, и {1,2,..., т}-количествоитераций, необходимое для получения результатов операции. 45

Значение jk при выполнении k-й итерации выбирается равным номеру старшего нулевого разряда кода Ck-1.

В случае выполнения операции умножения начальные значения переменных опре- ел деляются соотношениями

Vk{1,2L}aio Xi;bo 1/2;Co 1/2+

+ (1-ТО(2)

в случае операции деления - соотношениями

VU{1,2L}aio Xi;bo Y;Co Y (3) 55

Вычисления продолжаются до тех пор, пока в результате реализации очередной t-й итерации не будет выполнено условие

1 m;1-Ct-,2

5

10 15

20 25 30

35

40

45

ел

55

где m - мультипликативная разрядность вычислений, обеспечивающая получение результата с заданной точностью (т п).

Полученные в результате вычислений значения заявляются в зависимости от вида выполняемой операции либо произведением , либо частным .

Окончательный результат вычислений для каждого операнда выдается в виде(п+1)- разрядного кода, в котором старший (нулевой) разряд является знаковым, а разряды с первого по п-й - числовыми разрядами результата.

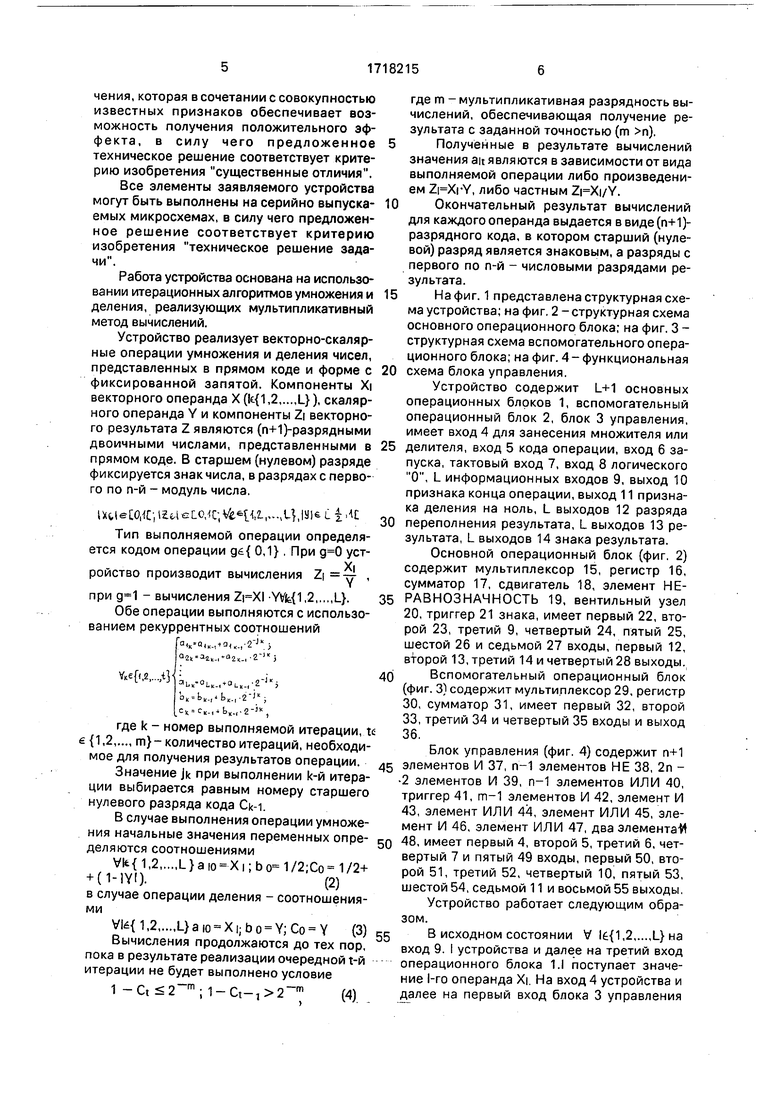

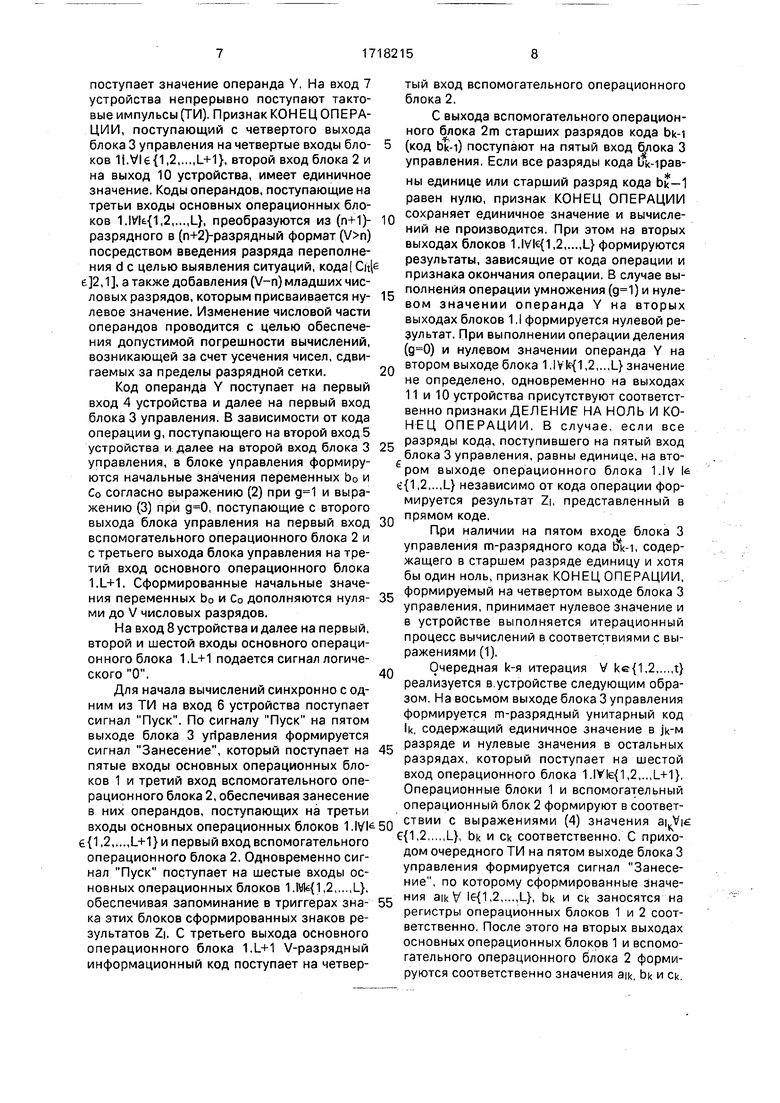

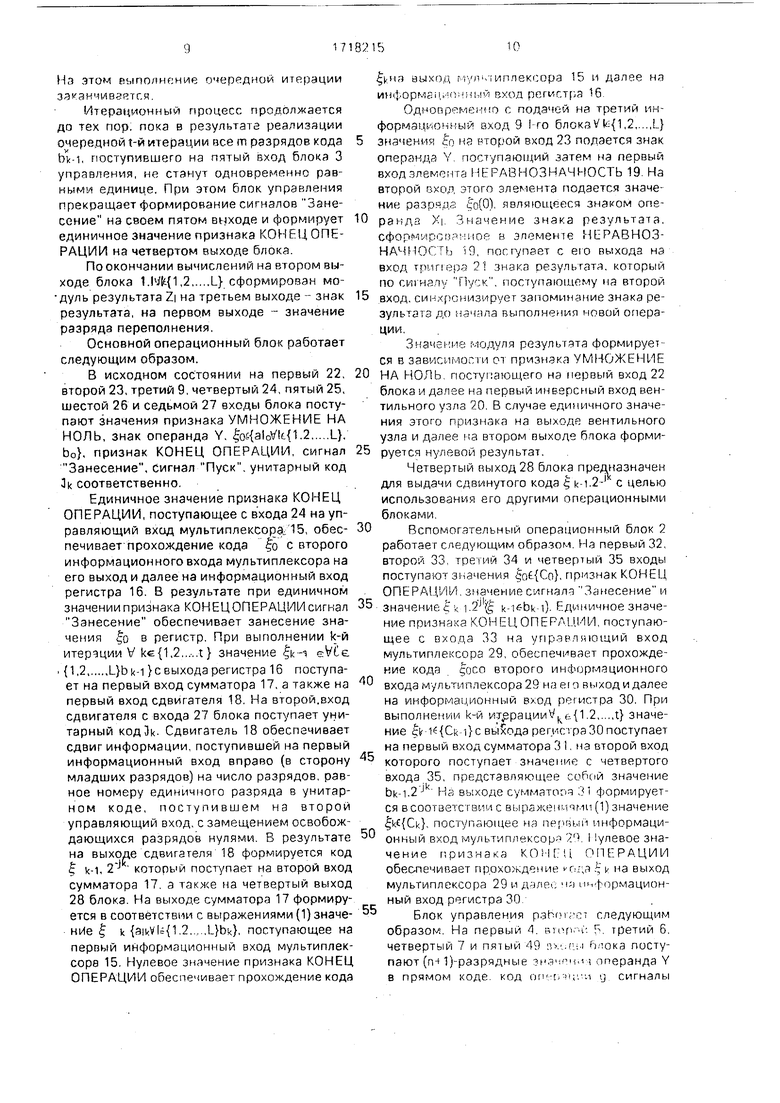

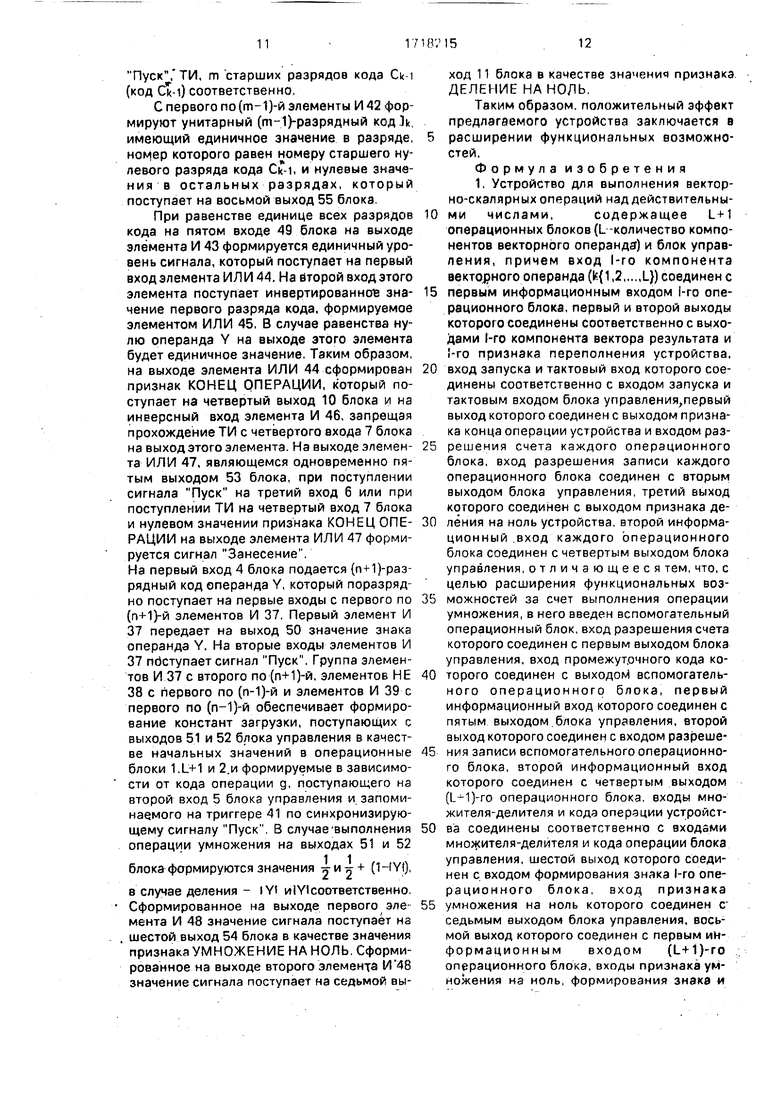

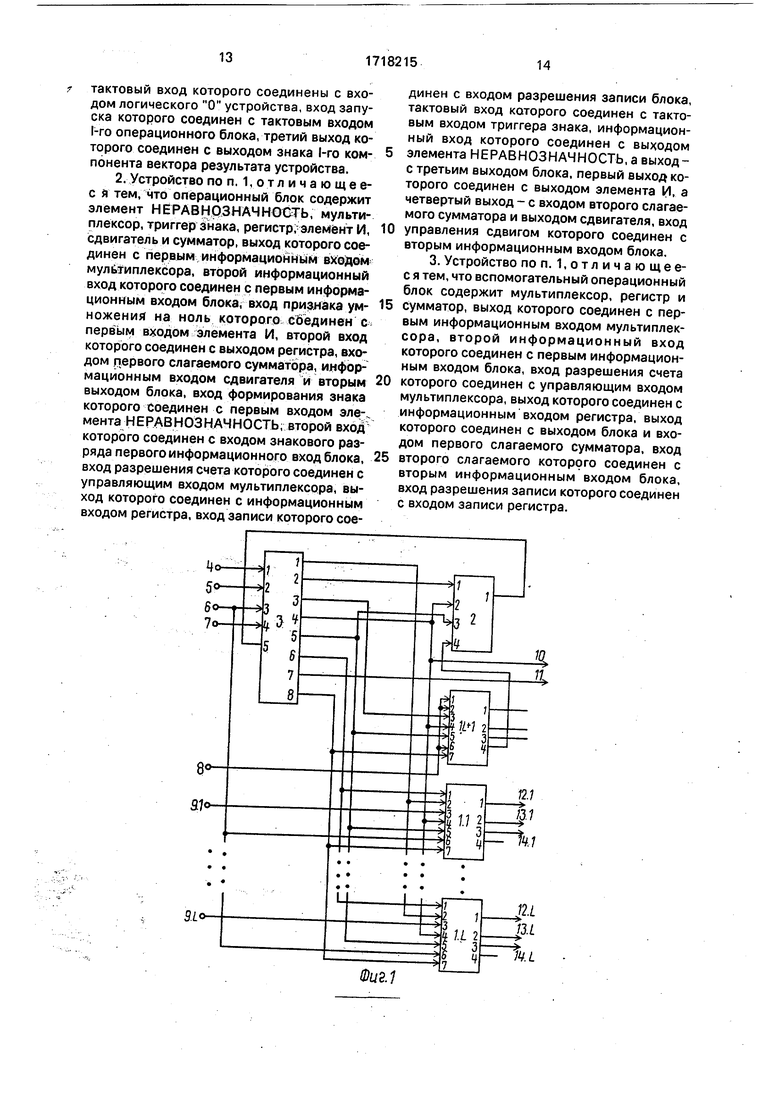

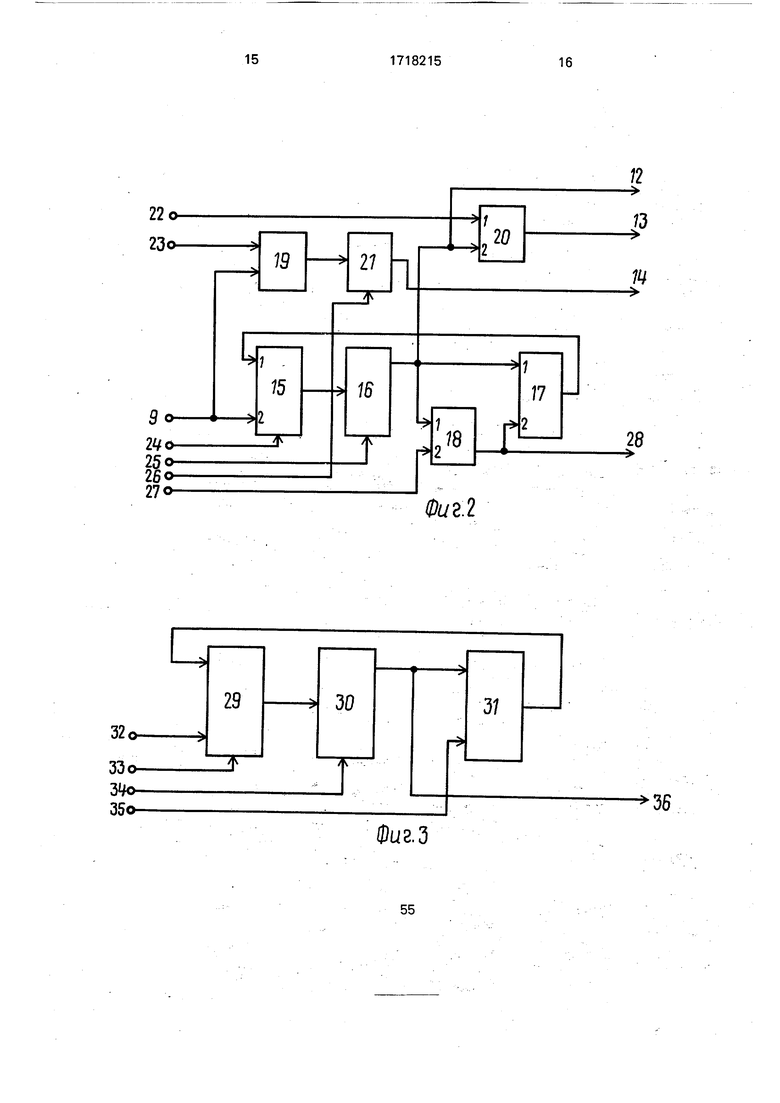

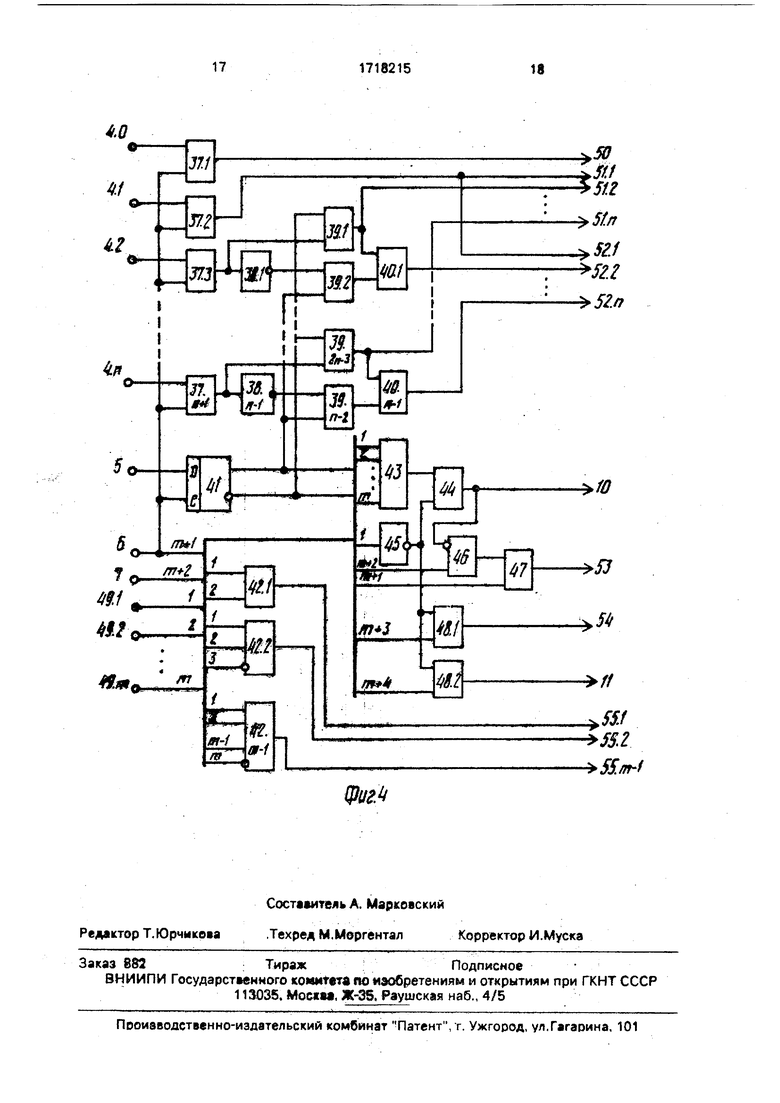

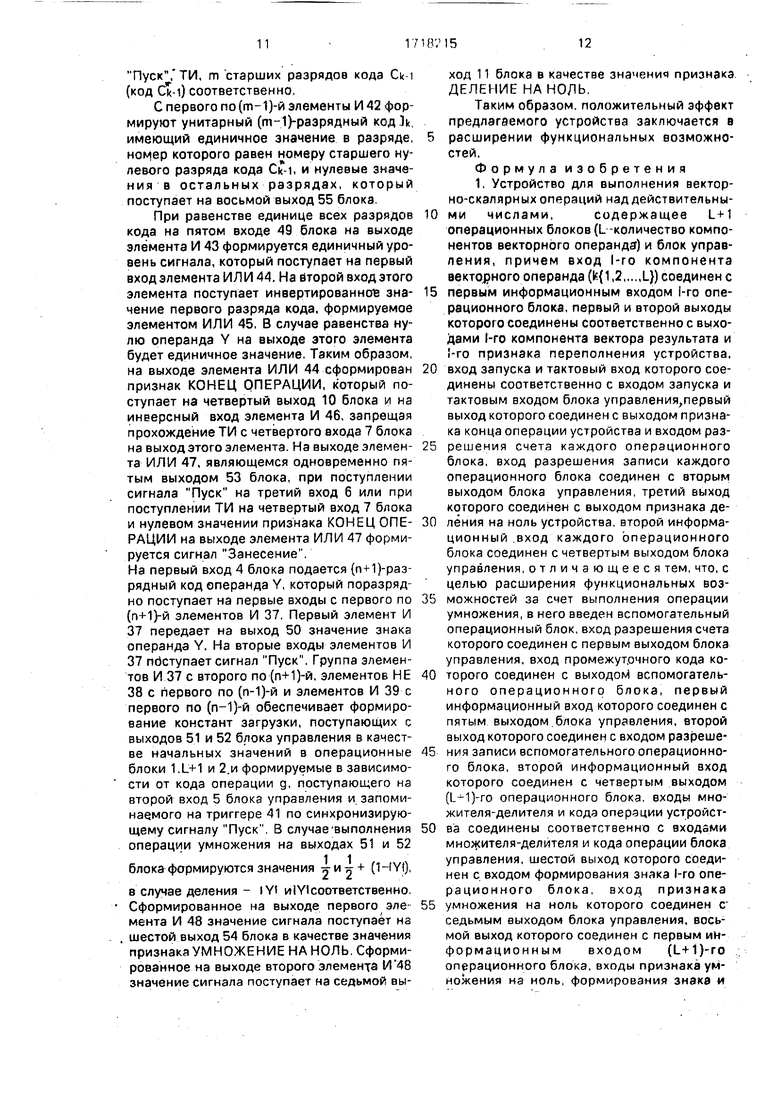

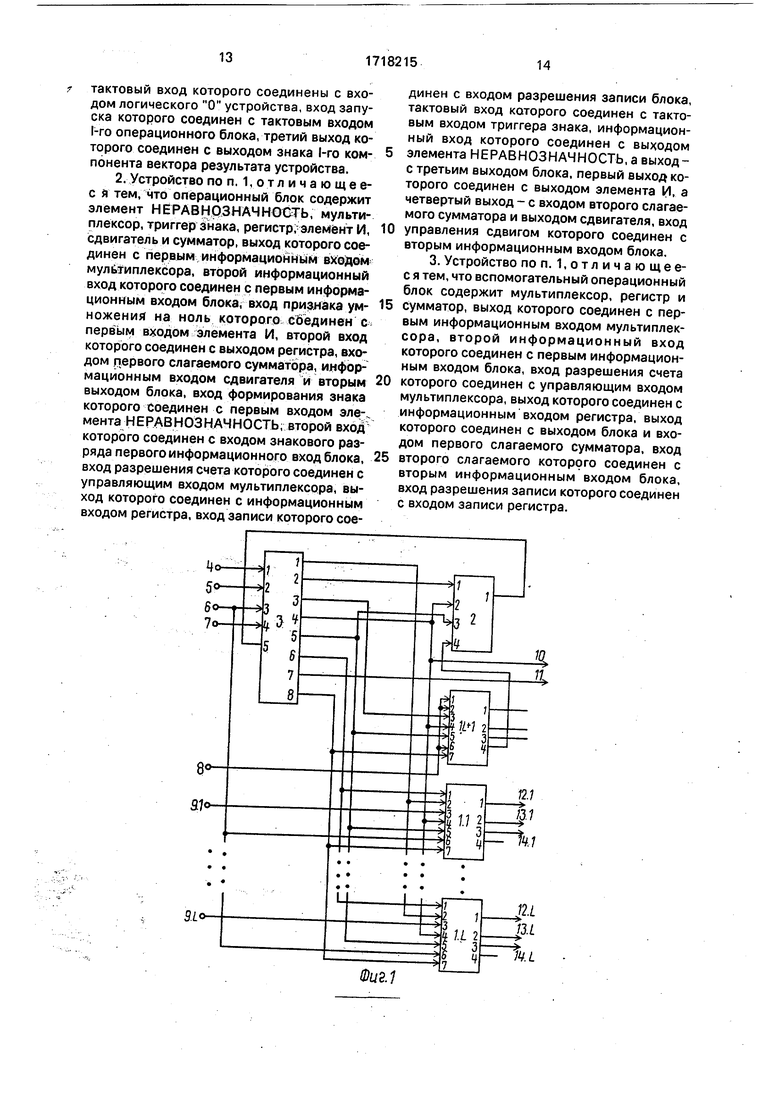

На фиг. 1 представлена структурная схема устройства; на фиг. 2 -структурная схема основного операционного блока; на фиг. 3 - структурная схема вспомогательного операционного блока; на фиг. 4- функциональная схема блока управления.

Устройство содержит L+1 основных операционных блоков 1, вспомогательный операционный блок 2, блок 3 управления, имеет вход 4 для занесения множителя или делителя, вход 5 кода операции, вход 6 запуска, тактовый вход 7, вход 8 логического О, L информационных входов 9, выход 10 признака конца операции, выход 11 признака деления на ноль, L выходов 12 разряда переполнения результата, L выходов 13 результата, L выходов 14 знака результата.

Основной операционный блок (фиг. 2) содержит мультиплексор 15, регистр 16, сумматор 17, сдвигатель 18, элемент НЕРАВНОЗНАЧНОСТЬ 19, вентильный узел 20, триггер 21 знака, имеет первый 22, второй 23, третий 9, четвертый 24, пятый 25, шестой 26 и седьмой 27 входы, первый 12, второй 13, третий 14 и четвертый 28 выходы.

Вспомогательный операционный блок (фиг. 3) содержит мультиплексор 29, регистр 30, сумматор 31, имеет первый 32, второй 33, третий 34 и четвертый 35 входы и выход 36.

Блок управления (фиг. 4) содержит п+1 элементов И 37, п-1 элементов НЕ 38, 2п - 2 элементов И 39, п-1 элементов ИЛИ 40, триггер 41, гл-1 элементов И 42, элемент И 43, элемент ИЛИ 44, элемент ИЛИ 45, элемент И 46, элемент ИЛИ 47, два элемента М 48, имеет первый 4, второй 5, третий 6, четвертый 7 и пятый 49 входы, первый 50, второй 51, третий 52, четвертый 10, пятый 53, шестой 54, седьмой 11 и восьмой 55 выходы.

Устройство работает следующим образом.

В исходном состоянии V lЈ{1,2L} на

вход 9. I устройства и далее на третий вход операционного блока 1.1 поступает значение 1-го операнда Xi. На вход 4 устройства и далее на первый вход блока 3 управления

поступает значение операнда Y. На вход 7 устройства непрерывно поступают тактовые импульсы (ТИ). Признак КОНЕЦ ОПЕРАЦИИ, поступающий с четвертого выхода блока 3 управления на четвертые входы бло- 5 ков 1|.VIe{1,2,...,L+1}, второй вход блока 2 и на выход 10 устройства, имеет единичное значение. Коды операндов, поступающие на третьи входы основных операционных блоков 1.IVk{1,2,...,}, преобразуются из (п+1)- 10 разрядного в (п+2)-разрядный формат () посредством введения разряда переполнения d с целью выявления ситуаций, кода СпИ

2,1, а также добавления (V-n) младших числовых разрядов, которым присваивается ну- 15 левое значение. Изменение числовой части операндов проводится с целью обеспечения допустимой погрешности вычислений, возникающей за счет усечения чисел, сдвигаемых за пределы разрядной сетки.20

Код операнда Y поступает на первый вход 4 устройства и далее на первый вход блока 3 управления. В зависимости от кода операции д, поступающего на второй вход 5 устройства и далее на второй вход блока 3 25 управления, в блоке управления формируются начальные значения переменных bo и Со согласно выражению (2) при и выражению (3) при , поступающие с второго выхода блока управления на первый вход 30 вспомогательного операционного блока 2 и с третьего выхода блока управления на третий вход основного операционного блока 1.L+1. Сформированные начальные значения переменных bo и Со дополняются нуля- 35 ми до V числовых разрядов.

На вход 8 устройства и далее на первый, второй и шестой входы основного операционного блока 1.L+1 подается сигнал логического О.40

Для начала вычислений синхронно с одним из ТИ на вход 6 устройства поступает сигнал Пуск. По сигналу Пуск на пятом выходе блока 3 управления формируется сигнал Занесение, который поступает на 45 пятые входы основных операционных блоков 1 и третий вход вспомогательного операционного блока 2,обеспечивая занесение в них операндов, поступающих на третьи входы основных операционных блоков 1.IVI&50

{1,2L+1} и первый вход вспомогательного

операционного блока 2. Одновременно сигнал Пуск поступает на шестые входы основных операционных блоков 1.1УЦ1,2L},

обеспечивая запоминание в триггерах зна- 55 ка этих блоков сформированных знаков результатов Zi. С третьего выхода основного операционного блока 1.L+1 V-разрядный информационный код поступает на четвертый вход вспомогательного операционного блока 2.

С выхода вспомогательного операционного блока 2т старших разрядов кода Ьм (код bk-i) поступают на пятый вход блока 3 управления. Если все разряды кода bk-фавны единице или старший разряд кода равен нулю, признак КОНЕЦ ОПЕРАЦИИ сохраняет единичное значение и вычислений не производится. При этом на вторых

выходах блоков 1.IVIe{1,2L} формируются

результаты, зависящие от кода операции и признака окончания операции. В случае выполнения операции умножения () и нулевом значении операнда Y на вторых выходах блоков 1.1 формируется нулевой результат. При выполнении операции деления () и нулевом значении операнда Y на втором выходе блока 1,IVk{1,2,..,L} значение не определено, одновременно на выходах 11 и 10 устройства присутствуют соответственно признаки ДЕЛЕНИЕ НА НОЛЬ И КО- НЕЦ ОПЕРАЦИИ. В случае, если все разряды кода, поступившего на пятый вход блока 3 управления, равны единице, на втором выходе операционного блока 1.IV &

С ,2,..,L} независимо от кода операции формируется результат Zi, представленный в прямом коде.

При наличии на пятом входе блока 3 управления m-разрядного кода bVi, содержащего в старшем разряде единицу и хотя бы один ноль, признак КОНЕЦ ОПЕРАЦИИ, формируемый на четвертом выходе блока 3 управления, принимает нулевое значение и в устройстве выполняется итерационный процесс вычислений в соответствиями с выражениями (1).

Очередная k-я итерация V ke{1,2t}

реализуется в.устройстве следующим образом. На восьмом выходе блока 3 управления формируется m-разрядный унитарный код Ik, содержащий единичное значение в jk-м разряде и нулевые значения в остальных разрядах, который поступает на шестой вход операционного блока 1.1У1е{1,2,..,, Операционные блоки 1 и вспомогательный операционный блок 2 формируют в соответствии с выражениями (4) значения ai.Vie

{1,2L}, bk и Ck соответственно. С приходом очередного ТИ на пятом выходе блока 3 управления формируется сигнал Занесение, по которому сформированные значения aikV le{1,2,...,L}, bk и ck заносятся на регистры операционных блоков 1 и 2 соответственно. После этого на вторых выходах основных операционных блоков 1 и вспомогательного операционного блока 2 формируются соответственно значения aik, bk и Ck.

На этом выполнение очередной итерации заканчивается.

Итерационный процесс продолжается до тех пор; пока в результате реализации очередной t-й итерации все m разрядов кода bk-1, поступившего на пятый вход блока 3 управления, не станут одновременно равными единице. При этом блок управления прекращает формирование сигналов Занесение на своем пятом внходе и формирует единичное значение признака КОНЕЦ ОПЕРАЦИИ на четвертом выходе блока.

По окончании вычислений на втором выходе блока 1.№{1,2L} сформирован модуль результата Zi на третьем выходе - знзк результата, на первом выходе - значение разряда переполнения.

Основной операционный блок работает следующим образом.

В исходном состоянии на первый 22, второй 23, третий 9, четвертый 24, пятый 25, шестой 26 и седьмой 27 входы блока поступают значения признака УМНОЖЕНИЕ НА

НОЛЬ, знак операнда Y, ЈoЈ{a 0VM1.2L}.

bo}, признак КОНЕЦ ОПЕРАЦИИ, сигнал Занесение, сигнал Пуск, унитарный код 3k соответственно.

Единичное значение признака КОНЕЦ ОПЕРАЦИИ, поступающее с входа 24 на управляющий вход мультиплексора/, обеспечивает прохождение кода |о с второго информационного входа мультиплексора на его выход и далее на информационный вход регистра 16. В результате при единичном значении признака КОНЕЦ ОПЕРАЦИИ сигнал Занесение обеспечивает занесение значения Јо в регистр. При выполнении k-й итерации V ke{1,2..,..:} значение Јk-i eVCe {1,2L}bk-l} с выхода регистра 16 поступает на первый вход сумматора 17, а также на первый вход сдвигателя 18. На второй.вход сдвигателя с входа 27 блока поступает унитарный кодЗк. Сдвигатель 18 обеспечивает сдвиг информации, поступившей на первый информационный вход вправо (в сторону младших разрядов) на число разрядов, равное номеру единичного разряда в унитарном коде, поступившем на второй управляющий вход, с замещением освобождающихся разрядов нулями. В результате на выходе сдвигателя 18 формируется код Ј k-1, 2- который поступает на второй вход сумматора 17. а также на четвертый выход 28 блока. На выходе сумматора 17 формируется в соответствии с выражениями (1) значение Ј k {aikVU{1.2,.,.,L}bk}. поступающее на первый информационный вход мультиплексора 15. Нулевое значение признака КОНЕЦ ОПЕРАЦИИ обеспечивает прохождение кода

0

выход мультиплексора 15 и далее на информационный вход регистра 16.

Одновременно с подачей на третий информационный вход 9 1-го блока Vte{ 1,2Ц

значения to на второй вход 23 подается знак операнда Y, поступающий затем на первый вход элемента НЕРАВНОЗНАЧНОСТЬ 19. На второй вход этого элемента подается значение разряда Јо(0), являющееся знаком операнда Х|. Значение знака результата, сформированное в элементе НЕРАВНОЗНАЧНОСТЬ i9, поступает с его выхода на

вход триггера

О

знака результата, который

5

0

5

0

5

0

5

0

5

по сигналу Пуск, поступающему на второй вход, синхронизирует запоминание знака результата до начала выполнения новой операции.

Значение модуля результата формируется в зависимости от признака УМНОЖЕНИЕ НА НОЛЬ, поступающего на первый вход 22 блока и далее на первый инверсный вход вентильного узла 20. В случае единичного значения этого признака на выходе вентильного узла и далее на втором выходе блока формируется нулевой результат.

Четвертый выход 28 блока предназначен для выдачи сдвинутого кода Ј ы. с целью использования его другими операционными блоками.

Вспомогательный операционный блок 2 работает следующим образом. На первый 32, второй 33, третий 34 и четвертый 35 входы поступают значения ЈоЈ{Со}, признак КОНЕЦ ОПЕРАЦИИ, значение сигнала Занесение и значение с k 1.2J {Ј ). Единичное значение признака КОНЕЦОПЕРАЦИИ, поступающее с входа 33 на управляющий вход мультиплексора 29, обеспечивает прохождение кода soco второго информационного входа мультиплексора 29 на ею выход и далее на информационный вход регистра 30. При выполнении k-й итерацииУк&{1.2t} значение Јir-iЈ{Ci -i}c выхода регистра 30 поступает на первый вход сумматора 3 t, на второй вход которого поступает значение с четвертого входа 35, представляющее собой значение bk-i.2 J На выходе сумматооч 31 формируется в соответствии с выражениями (1) значение Јkf{Ck}, поступающее на первый информационный вход мультиплексор- 2Г. улевое значение признака КОНЕЦ ОПЕРАЦИИ обеспечивает прохождение ода Ј i/ на выход мультиплексора 29 и далее ня информационный вход регистра 30.

Блок управления рзо ог ет следующим образом. На первый 4. ЙУОП.-Ч-. 5. третий 6. четвертый 7 и пятый 49 :vv,.n.;.i п.чока поступают (ги 1)-разрядные 1 операнда Y в прямом коде, код оп .-п- П .-и g сигналы

Пуск,ТИ, m старших разрядов кода Сы (код Сы) соответственно,

С первого по (т-1)-й элементы И 42 формируют унитарный (т-1)-раэрядный код 3k, имеющий единичное значение в разряде, номер которого равен номеру старшего нулевого разряда кода Сы, и нулевые значения в остальных разрядах, который поступает на восьмой выход 55 блока.

При равенстве единице всех разрядов кода на пятом входе 49 блока на выходе элемента И 43 формируется единичный уровень сигнала, который поступает на первый вход элемента ИЛ И 44. На йторой вход этого элемента поступает инвертированное значение первого разряда кода, формируемое элементом ИЛИ 45, В случае равенства нулю операнда Y на выходе этого элемента будет единичное значение. Таким образом, на выходе элемента ИЛИ 44 сформирован признак КОНЕЦ ОПЕРАЦИИ, который поступает на четвертый выход 10 блока и на инверсный вход элемента И 46, запрещая прохождение ТИ с четвертого входа 7 блока на выход этого элемента. На выходе элемента ИЛИ 47, являющемся одновременно пятым выходом 53 блока, при поступлении сигнала Пуск на третий вход 6 или при поступлении ТИ на четвертый вход 7 блока и нулевом значении признака КОНЕЦ ОПЕРАЦИИ на выходе элемента ИЛИ 47 формируется сигнал Занесение. На первый вход 4 блока подается {п+1)-раз- рядный код операнда Y, который поразрядно поступает на первые входы с первого по (п+1)-й элементов И 37. Первый элемент И 37 передает на выход 50 значение знака операнда Y. На вторые входы элементов И

37поступает сигнал Пуск. Группа элементов И 37 с второго по (п+1)-й, элементов НЕ

38с первого по (п-1)-й и элементов И 39 с первого по (п-1)-й обеспечивает формирование констант загрузки, поступающих с выходов 51 и 52 блока управления в качестве начальных значений в операционные блоки 1.L+1 и 2.и формируемые в зависимости от кода операции д, поступающего на второй вход 5 блока управления и запоминаемого на триггере 41 по синхронизирующему сигналу Пуск. В случае выполнения операции умножения на выходах 51 и 52

блока формируются значения ,

в случае деления - lYt и 1YI соответственно. Сформированное на выходе первого элемента И 48 значение сигнала поступает на шестой выход 54 блока в качестве значения признака УМНОЖЕНИЕ НА НОЛЬ. Сформированное на выходе второго элемента И 48 значение сигнала поступает на седьмой выход 11 блока в качестве значение признака. ДЕЛЕНИЕ НА НОЛЬ.

Таким образом, положительный эффект предлагаемого устройства заключается в 5 расширении функциональных возможностей,

Формула изобретения 1. Устройство для выполнения вектор- но-скалярных операций над действительны0 ми числами, содержащее L+1 операционных блоков (L -количество компонентов векторного операнда) и блок управления, причем вход 1-го компонента векторного операнда (И{1,2L}) соединен с

5 первым информационным входом 1-го операционного блока, первый и второй выходы которого соединены соответственное выходами 1-го компонента вектора результата и 1-го признака переполнения устройства,

0 вход запуска и тактовый вход которого соединены соответственно с входом запуска и тактовым входом блока управления,первый выход которого соединен с выходом признака конца операции устройства и входом раз5 решения счета каждого операционного блока, вход разрешения записи каждого операционного блока соединен с вторым выходом блока управления, третий выход которого соединен с выходом признака де0 лёния на ноль устройства, второй информационный .вход каждого операционного блока соединен с четвертым выходом блока управления, отличающееся тем, что, с целью расширения функциональных воз5 можностей за счет выполнения операции умножения, в него введен вспомогательный операционный блок, вход разрешения счета которого соединен с первым выходом блока управления, вход промежуточного кода ко0 торого соединен с выходом вспомогательного операционного блока, первый информационный вход которого соединен с пятым выходом.блока управления, второй выход которого соединен с входом разреше5 ния записи вспомогательного операционного блока, второй информационный вход которого соединен с четвертым выходом (L-1)-ro операционного блока, входы множителя-делителя и кода операции устройст0 ва соединены соответственно с входами множителя-делителя и кода операции блока управления, шестой выход которого соединен с входом формирования знака 1-го опе- рационного блока, вход признака

5 умножения на ноль которого соединен С седьмым выходом блока управления, восьмой выход которого соединен с первым ин- формационным входом (L-M)-ro операционного блока, входы признака умножения на ноль, формирования знака и

тактовый вход которого соединены с входом логического О устройства, вход запуска которого соединен с тактовым входом 1-го операционного блока, третий выход которого соединен с выходом знака 1-го компонента вектора результата устройства.

2. Устройство по п. отличающее- с я тем, что операционный блок содержит элемент НЕРАВНОЗНАЧНОСТЬ, мультиплексор, триггер знака, регистр,-элемент И, сдвигатель и сумматор, выход которого соединен с первым информационным входом мультиплексора, второй информационный вход которого соединен с первым информационным входом блока, вход признака умножения на ноль которого соединен с первым входом элемента И, второй вход которого соединен с выходом регистра, входом первого слагаемого сумматора, информационным входом сдвигателя и вторым выходом блока, вход формирования знака которого соединен с первым входом элемента НЕРАВНОЗНАЧНОСТЬ; второй вход которого соединен с входом знакового разряда первого информационного вход блока, вход разрешения счета которого соединен с управляющим входом мультиплексора, выход которого соединен с информационным входом регистра, вход записи которого соединен с входом разрешения записи блока, тактовый вход которого соединен с тактовым входом триггера знака, информационный вход которого соединен с выходом

элемента НЕРАВНОЗНАЧНОСТЬ, а выход- с третьим выходом блока, первый выход которого соединен с выходом элемента И, а четвертый выход - с входом второго слагаемого сумматора и выходом сдвигателя, вход

управления сдвигом которого соединен с вторым информационным входом блока.

3. Устройство по п. 1, о т л и ч а ю щ е е- с я тем, что вспомогательный операционный блок содержит мультиплексор, регистр и

сумматор, выход которого соединен с первым информационным входом мультиплексора, второй информационный вход которого соединен с первым информационным входом блока, вход разрешения счета

которого соединен с управляющим входом мультиплексора, выход которого соединен с информационным входом регистра, выход которого соединен с выходом блока и входом первого слагаемого сумматора, вход

второго слагаемого которого соединен с вторым информационным входом блока, вход разрешения записи которого соединен с входом записи регистра.

Фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выполнения векторно-скалярных операций над действительными числами | 1990 |

|

SU1728861A1 |

| Устройство для деления чисел | 1990 |

|

SU1795456A1 |

| УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОГО ДЕЛЕНИЯ ЧИСЕЛ | 1991 |

|

RU2010311C1 |

| Устройство для обработки данных | 1987 |

|

SU1513443A1 |

| МАТРИЧНЫЙ СПЕЦПРОЦЕССОР | 1994 |

|

RU2079879C1 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Операционное устройство | 1985 |

|

SU1367012A1 |

| Устройство для вычисления квадратного корня из суммы квадратов | 1990 |

|

SU1751751A1 |

| Устройство для деления | 1990 |

|

SU1742815A1 |

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных вычислительных системах для аппаратной реализации параллельного деления или умножения чисел, представленных в прямом коде в форме с фиксированной запятой. Цель изобретения - расширение функциональных возможностей устройства за счет выполнения операции умножения, Цель достигается тем, что в устройство, содержащее L+1 операционных блоков (L - количество элементов векторного операнда) и блок управления, введен вспомогательный операционный блок. 2 з. п. ф-лы, 4 ил,

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для выполнения операций умножения и деления | 1986 |

|

SU1403061A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР fsb 1618165, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-03-07—Публикация

1990-04-26—Подача