,, Xi

вида l) -j

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных вычислительных системах для аппаратной реализации векторно-скалярных операций

Y It {1,2 L}(L-число

компонентов векторного операнда) для действительных чисел, представленных в дополнительном коде в форме с фиксированной запятой.

Известно устройство для выполнения операций умножения и деления, содержащее блок приема и выдачи, регистр, блок суммирования, мультиплексор, блок управления, блок формирования признака активности, триггер, счетчик циклов, дешифратор, коммутатор, элементы НЕ, И, ИЛИ, 2И-ИЛИ и НЕРАВНОЗНАЧНОСТЬ с соответствующими связями.

Недостатками известного устройства являются низкое быстродействие и ограниченные функциональные возможности, обеспечивающие одновременную обработку толь ко двух операндов, которые должны быть положительны. Кроме того известное устройство не позволяет выполнять одновременно операции умножения и деления.

Наиболее близким к предлагаемому по технической сущности является устройство для параллельного деления чисел, содержащее (L+1) операционных блоков, блок управления и триггер знака.. Недостатком данного устройства являются ограниченные функциональные возможности, обеспечивающие выполнение только операции деления.

vj КЭ 00 00

О

Цель изобретения - расширение функциональных возможностей за счет выполнения операции вида Ui -j- Y ,

Поставленная цель достигается тем, что устройство для выполнения векторно-ска- лярных операций над действительными чис- лами, содержащее (L+1) операционных блоков (L- количество компонентов векторного операнда) и блок управления, причем вход 1-го компонента векторного операнда устройства (Vlt{1, ) соединен с первым информационным входом 1-го операционного блока, первый выход которого соединен с выходом 1-го компонента векто- ра результата устройства, а второй выход- с выходом 1-го признака переполнения устройства, вход делителя устройства соединен с первым информационным входом ()-го операционного блока, первый вы- ход которого соединен с входом признака делителя блока управления, вход запуска и тактовый вход которого соединены с входом запуска и тактовым входом устройства соответственно, выход признака деления на нуль которого соединен с первым выходом блока управления, второй выход которого соединен с выходом признака конца операции устройства и входом разрешения счета каждого операционного блока, информаци- онной вход каждого операционного блока соединен с третьим выходом блока управления, четвертый выход которого соединен с входами разрешения записи всех операционных блоков, дополнительно введены вспомогательный операционный блок и элемент неравнозначность, выход которого соединен с входом формирования знака 1-го операционного блока, вход формирования знака ()-го операционного блока соеди- нен с входом логического нуля устройства, вход множителя которого соединен с входом признака множителя блока управления и первым информационным входом вспомогательного операционного блока, второй информационный вход которого соединен с входами делителя устройства и блокауправ- ления, вход промежуточного кода которого соединен с выходом вспомогательного операционного блока и третьими информаци- онными входами всех операционных блоков, вход признака умножения на нуль которых соединены с пятым выходом блока управления, второй, третий и четвертый выходы которого соединены соответственно с входом разрешения счета, третьим информационным входом и входом разрешения записи вспомогательного операционного блока, вход делителя которого соединен с

выходом ()-го операционного блока, входы знаковых разрядов множителя и делителя устройства соединены соответственно с первым и вторым входами элемента НЕРАВНОЗНАЧНОСТЬ,

Поставленная цель достигается также тем, что операционный блок содержит два сумматора по модулю 2, мультиплексор, регистр, сдвигатель, два элемента И, элемент ИЛИ, элемент РАВНОЗНАЧНОСТЬ, сумматор и элемент НЕ, выход которого соединен с вторым выходом блока, первый выход которого соединен с выходом первого элемента И, первый инверсный вход которого соединен с входом признака умножения на нуль блока, второй информационный вход которого соединен с входом управления сдвигом сдвигателя, информационный вход которого соединен с выходом регистра, входом первого слагаемого сумматора и вторым входом первого элемента И, выходы знаковых разрядов регистра соединены с первым и вторым входами элемента РАВНОЗНАЧНОСТЬ, выход которого соединен с входом элемента НЕ и первым входом элемента ИЛИ, второй вход которого соединен с третьим информационным входом блока и входом первого слагаемого первого сумматора по модулю 2, вход второго слагаемого которого соединен с выходом сдвигателя, а выход - с входом второго слагаемого сумматора, выход которого соединен с первым информационным входом мультиплексора, второй информационный вход которого соединен с выходом второго сумматора по модулю 2, входы первого и второго слагаемых которого соединены соответственно с входом формирования знака и первым информационным входом блока, вход разрешения счета которого соединен с третьим входом элемента ИЛИ и управляющим входом мультиплексора, выход которого соединен с информационным входом регистра, вход записи которого соединен с выходом второго элемента И, первый и второй входы которого соединены соответственно с входом разрешения записи блока и выходом элемента ИЛИ.

Поставленная цель достигается также тем, что вспомогательный операционный блок содержит три сумматора по модулю 2, два сумматора, мультиплексор, регистр, сдвигатель и элемент НЕ, выход которого соединен с входом первого слагаемого первого сумматора по модулю 2, вход второго слагаемого которого соединен с выходом сдвигателя, вход управления сдвигом и информационный вход которого соединены соответственно с третьим информационным входом делителя блока, первый и второй информационные входы которого соединены соответственно с входами слагаемых второго и третьего сумматоров по модулю 2, выходы которых соединены соответственно с входами первого и второго слагаемых первого сумматора, выход которого соединен с первым информационным входом мультиплексора, второй информационный вход которого соединен с выходом второго сумматора, вход первого слагаемого которого соединен с выходом первого сумматора по модулю 2, а вход второго слагаемого - с входом элемента НЕ, выходом блока и выходом регистра, информационный вход которого соединен с выходом мультиплексора, управляющий вход которого соединен с входом разрешения счета блока, вход разрешения записи которого соединен с входом записи регистра.

Работа устройства основана на использовании итерационного алгоритма, реализующего мультипликативный метод вычислений. Операнды и результат представляются (п+1)-разрядными числами в дополнительном коде в форме с фиксированной запятой. В старшем (нулевом) разряде записывается код знака числа, разряды с первого по n-й являются числовыми.

Xi( |t{1,2L})

Y,,1.

Операция выполняется с использованием рекуррентных соотношений:

f ak ak-1 - Skbk-1 bk bk-1 + Skbk-1 2 Jk;

VKt{ 1,2t} Cik Cik-1 + SkCik-1 .

jCLk CLk +:SkCtK -2 , (1) где k - номер выполняемой итерации,

tЈ{1, 2, ..., n} - количество итераций, необходимое для получения результатов операции.

Значение Sk определяется старшим (нулевым) разрядом операнда aic-1, Sk sgnak-i 1-2 -aic-i(0).

Значения jk при выполнении к-й итерации выбираются на основе соотношений:

jk jjk -jk2 при jk1 jk2I

|jk-l(0) npnjk jk2.(2)

где jki min {Jc N/aic-i(l) ak-i(0)},

Jk2 min{jЈ N/bk-iG) 1}ak-i(0) - значение нулевого (знакового) разряда кода ak-1.

Начальные значения переменных определяются соотношениями:

ао IYi -/Zj; bo /Z/; J lt{1, 2..... L};

sgnZ Xi.(3)

Вычисления продолжаются до тех пор, пока в результате реализации очередной t-й итерации будет выполнено условие

I atl .(4)

где m - мультипликативная разрядность вычислений, обеспечивающая получение результата с заданной точностью (т п). Полученные в результате выполнения t-й итерации значения ait используются в

качестве результатов операции Ui.

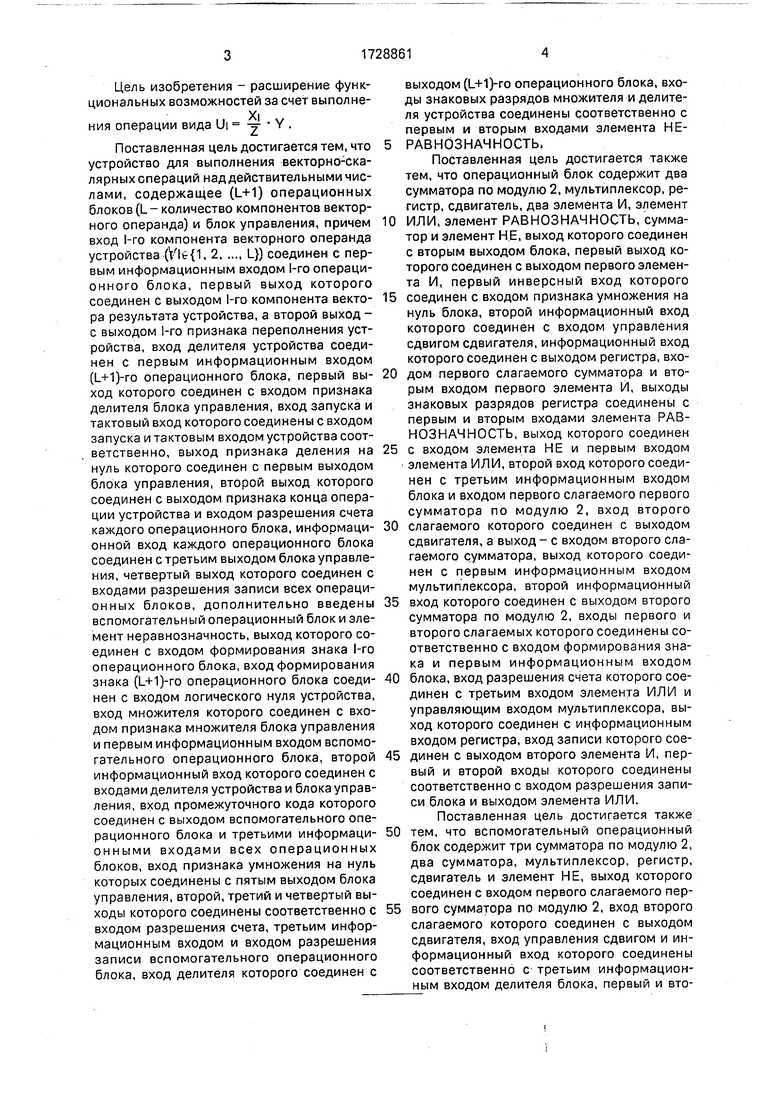

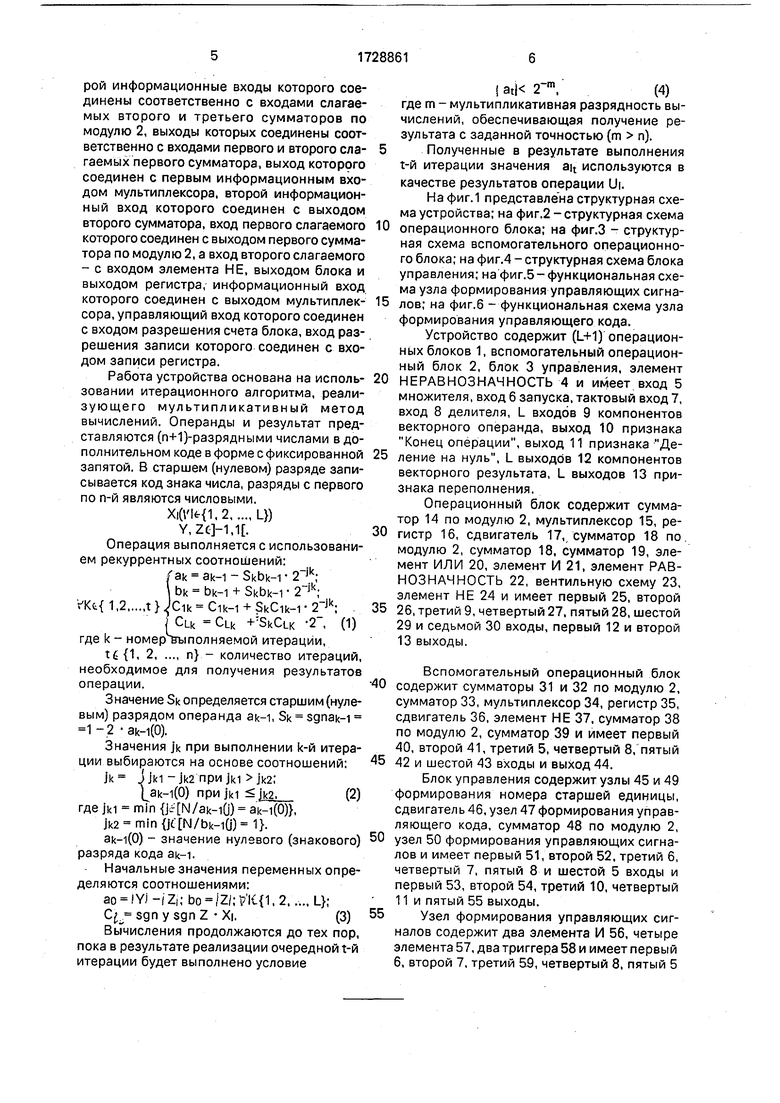

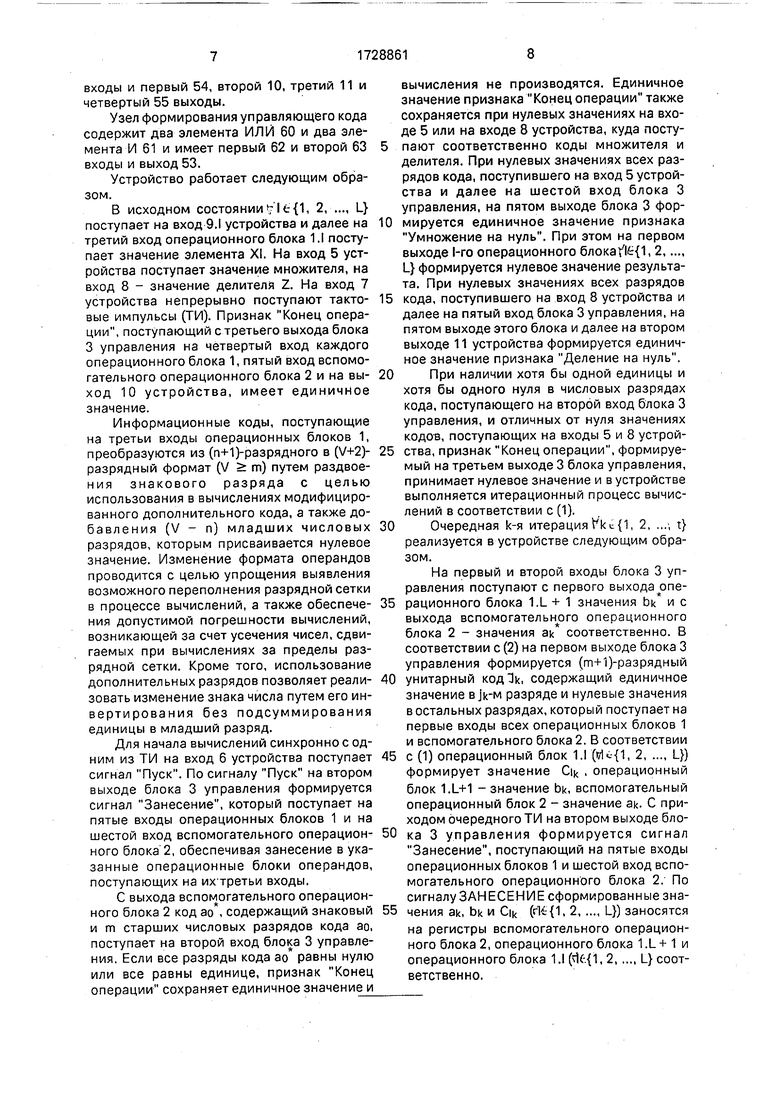

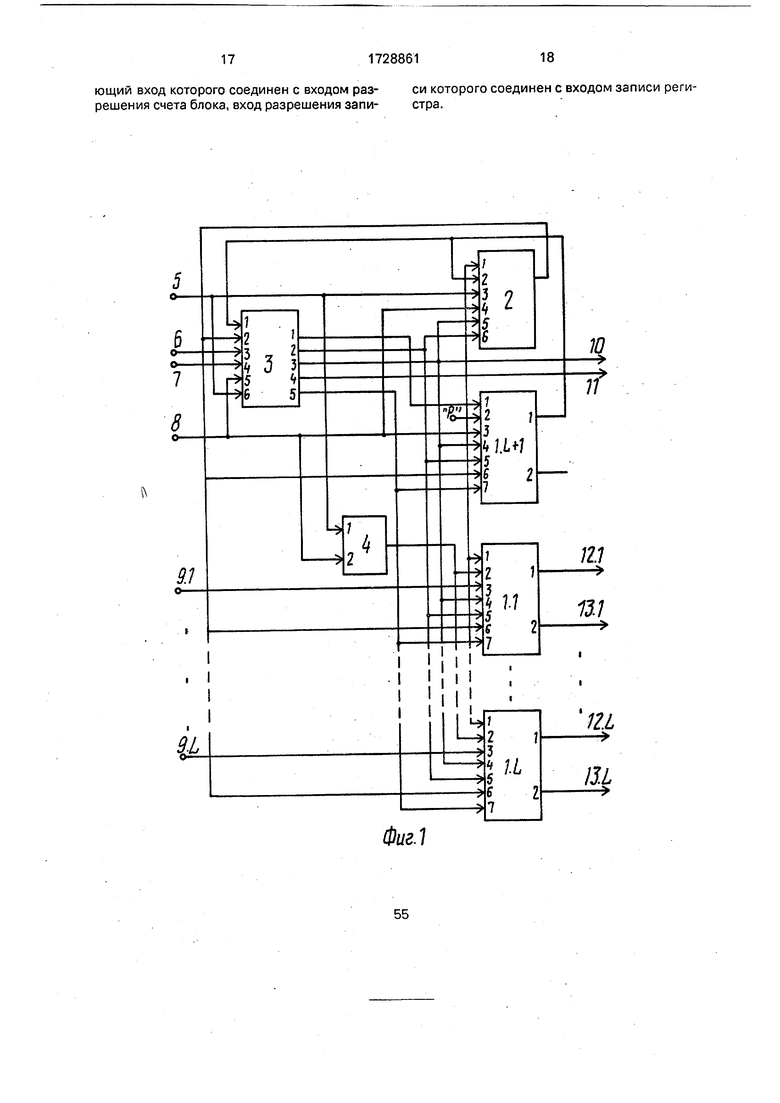

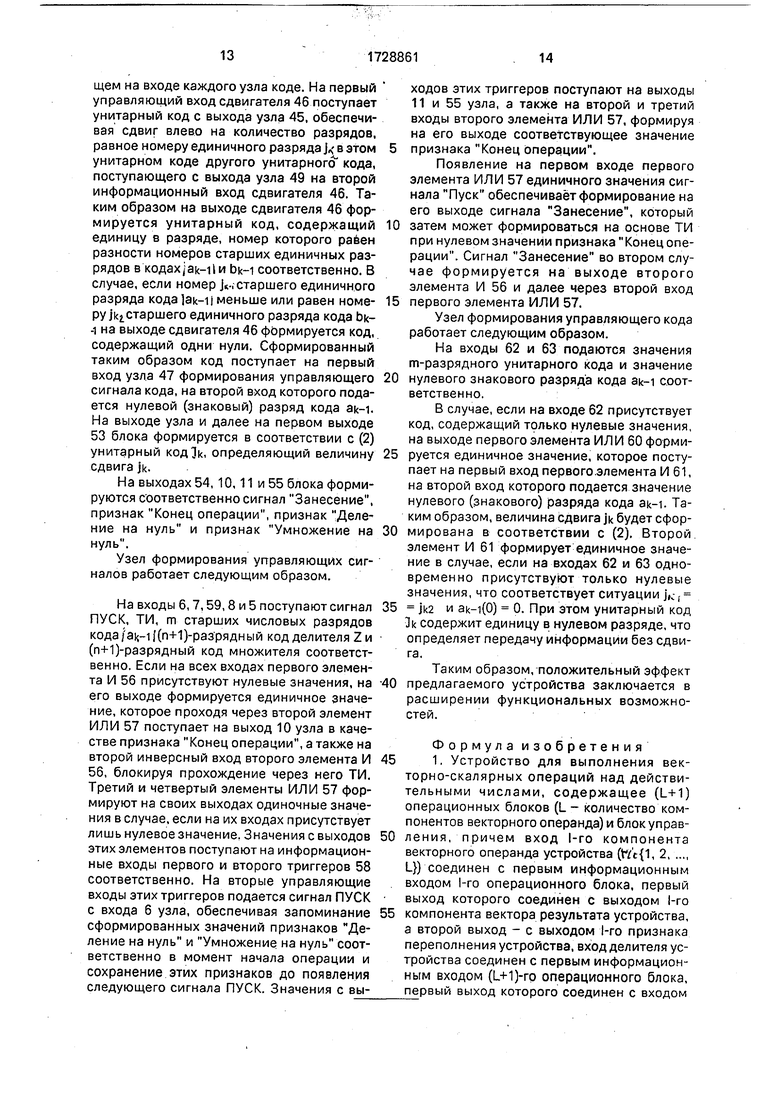

На фиг.1 представлена структурная схема устройства; на фиг.2 -структурная схема

операционного блока; на фиг.З - структурная схема вспомогательного операционного блока; на фиг.4 - структурная схема блока управления; на фиг.5- функциональная схема узла формирования управляющих сигналов; на фиг.6 - функциональная схема узла формирования управляющего кода.

Устройство содержит (L+1) операционных блоков 1, вспомогательный операционный блок 2, блок 3 управления, элемент

НЕРАВНОЗНАЧНОСТЬЮ и имеет вход 5 множителя, вход 6 запуска, тактовый вход 7, вход 8 делителя, L входов 9 компонентов векторного операнда, выход 10 признака Конец операции, выход 11 признака Деление на нуль, L выходов 12 компонентов векторного результата, L выходов 13 признака переполнения.

Операционный блок содержит сумматор 14 по модулю 2, мультиплексор 15, регистр 16, сдвигатель 17, сумматор 18 по. модулю 2, сумматор 18, сумматор 19, элемент ИЛИ 20, элемент И 21, элемент РАВНОЗНАЧНОСТЬ 22, вентильную схему 23, элемент НЕ 24 и имеет первый 25, второй

26, третий 9, четвертый 27, пятый 28, шестой 29 и седьмой 30 входы, первый 12 и второй 13 выходы.

Вспомогательный операционный блок

содержит сумматоры 31 и 32 по модулю 2, сумматор 33, мультиплексор 34, регистр 35, сдвигатель 36, элемент НЕ 37, сумматор 38 по модулю 2, сумматор 39 и имеет первый 40, второй 41, третий 5, четвертый 8, пятый

42 и шестой 43 входы и выход 44.

Блок управления содержит узлы 45 и 49 формирования номера старшей единицы, сдвигатель 46, узел 47 формирования управляющего кода, сумматор 48 по модулю 2,

узел 50 формирования управляющих сигналов и имеет первый 51, второй 52, третий 6, четвертый 7, пятый 8 и шестой 5 входы и первый 53, второй 54, третий 10, четвертый 11 и пятый 55 выходы.

Узел формирования управляющих сигналов содержит два элемента И 56, четыре элемента 57, два триггера 58 и имеет первый 6, второй 7, третий 53, четвертый 8, пятый 5

входы и первый 54, второй 10, третий 11 и четвертый 55 выходы.

Узел формирования управляющего кода содержит два элемента ИЛИ 60 и два мента И 61 и имеет первый 62 и второй 63 входы и выход 53.

Устройство работает следующим образом.

В исходном состоянии v It {I, 2, ..., L} поступает на вход 9.1 устройства и далее на третий вход операционного блока 1.1 поступает значение элемента XI. На вход 5 устройства поступает значение множителя, на вход 8 - значение делителя Z. На вход 7 устройства непрерывно поступают тактовые импульсы (ТИ). Признак Конец операции, поступающий с третьего выхода блока 3 управления на четвертый вход каждого операционного блока 1, пятый вход вспомогательного операционного блока 2 и на выход 10 устройства, имеет единичное значение.

Информационные коды, поступающие на третьи входы операционных блоков 1, преобразуются из (п+1)-разрядного в (V+2)- разрядный формат (V т) путем раздвоения знакового разряда с целью использования в вычислениях модифицированного дополнительного кода, а также до- бавления (V - п) младших числовых разрядов, которым присваивается нулевое значение. Изменение формата операндов проводится с целью упрощения выявления возможного переполнения разрядной сетки в процессе вычислений, а также обеспечения допустимой погрешности вычислений, возникающей за счет усечения чисел, сдвигаемых при вычислениях за пределы разрядной сетки. Кроме того, использование дополнительных разрядов позволяет реализовать изменение знака числа путем его ин- вертирования без подсуммирования единицы в младший разряд.

Для начала вычислений синхронно с одним из ТИ на вход 6 устройства поступает сигнал Пуск. По сигналу Пуск на втором выходе блока 3 управления формируется сигнал Занесение, который поступает на пятые входы операционных блоков 1 и на шестой вход вспомогательного операционного блока 2, обеспечивая занесение в указанные операционные блоки операндов, поступающих на их третьи входы.

С выхода вспомогательного операционного блока 2 код ао , содержащий знаковый и m старших числовых разрядов кода ао, поступает на второй вход блока 3 управления. Если все разряды кода ао равны нулю или все равны единице, признак Конец операции сохраняет единичное значение и

вычисления не производятся. Единичное значение признака Конец операции также сохраняется при нулевых значениях на входе 5 или на входе 8 устройства, куда поступа ют соответственно коды множителя и делителя. При нулевых значениях всех разрядов кода, поступившего на вход 5 устройства и далее на шестой вход блока 3 управления, на пятом выходе блока 3 формируется единичное значение признака Умножение на нуль. При этом на первом

выходе 1-го операционного блокаt lt{1, 2

L} формируется нулевое значение результата. При нулевых значениях всех разрядов

кода, поступившего на вход 8 устройства и далее на пятый вход блока 3 управления, на пятом выходе этого блока и далее на втором выходе 11 устройства формируется единичное значение признака Деление на нуль.

При наличии хотя бы одной единицы и хотя бы одного нуля в числовых разрядах кода, поступающего на второй вход блока 3 управления, и отличных от нуля значениях кодов, поступающих на входы 5 и 8 устройства, признак Конец операции, формируемый на третьем выходе 3 блока управления, принимает нулевое значение и в устройстве выполняется итерационный процесс вычислений в соответствии с (1).

Очередная k-я итерация fkt{1, 2, .,., t} реализуется в устройстве следующим образом.

На первый и второй входы блока 3 управления поступают с первого выхода операционного блока 1.L+ 1 значения bk и с выхода вспомогательного операционного блока 2 - значения ak соответственно. В соответствии с (2) на первом выходе блока 3 управления формируется (т+1)-разрядный

унитарный код 3k, содержащий единичное значение в jk-м разряде и нулевые значения в остальных разрядах, который поступает на первые входы всех операционных блоков 1 и вспомогательного блока 2. В соответствии

с (1) операционный блок 1.1 (i7U-{1, 2L})

формирует значение С|| , операционный блок 1.L+1 - значение bk, вспомогательный операционный блок 2 - значение ak. С приходом очередного ТИ на втором выходе блока 3 управления формируется сигнал Занесение, поступающий на пятые входы операционных блоков 1 и шестой вход вспомогательного операционного блока 2. По сигналу ЗАНЕСЕНИЕ сформированные значения ak, bk и Cik (rlt{1,2L}) заносятся

на регистры вспомогательного операционного блока 2, операционного блока 1 .L + 1 и операционного блока 1.1 (1(-.{1, 2L} соответственно.

Если в процессе вычислений в операционном блоке 1.1 lt{1, 2, .... L} в результате очередной итерации произойдет переполнение разрядной еетки, на втором выходе операционного блока 1.1 по окончании итерации будет сформировано единичное значение признака Переполнение, которое будет сохраняться до начала выполнения следующей операции. На первом выходе операционного блока 1.1 сформируется и будет сохраняться до начала выполнения следующей операции результат выполнения итерации, в процессе реализации которой произошло переполнение.

Итерационный процесс продолжается до тех пор, пока в результате реализации очередной t-й итерации все (т+1) разрядов кода, поступающего на второй вход блока 3 управления, станут одновременно равными нулю или одновременно равными единице. При этом блок 3 управления прекратит формирование на своем втором выходе сигналов Занесение и сформирует единичное значение признака Конец операции на своем третьем выходе.

По окончании вычислений на первом выходе операционного блока 1.1 li-{1, 2,..., L}) будет сформировано значение 1-го элемента вектора результата U.

Операционный блок 1.lV lc{1, 2, .... L} работает следующим образом.

В исходном состоянии на входы 25, 26, 9, 27, 28, 29 и 30 поступают значения унитарного кода Jk, результат сложения по модулю 2 знаков множителя и делителя Cio признак Конец операции, сигнал Занесение, значение (0), признак Умножение на нуль соответственно. Поступающее на вход 9,1 блока значение CIQ складывается по модулю 2 со значением, присутствующим на входе 26, сумматором 14 по модулю 2. Единичное значение признака Конец операции, поступающее с входа 27 блока на управляющий вход мультиплексора 15, обеспечивает прохождение кода, поступающего с выхода сумматора 14 по модулю 2 на второй информационный вход мультиплексора 15, на его выход и далее на информационный вход регистра 16, а также формирует единичный сигнал на выходе элемента ИЛИ 20, обеспечивающий прохождение сигнала Занесение с входа 28 блока через элемент И 21 на управляющий вход регистра 16. В результате при единичном значении признака Конец операции сигнал Занесение осуществляет занесение начального значения переменной, обрабатываемой блоком 1.1.к

При выполнении k-й итерации i/kt{1, 2,

.., t} значение СЈ,-..-.Ј.Ј{1, 2, .., L} с выхода

регистра 16 поступает на второй вход сдвигателя 17, а также на второй вход сумматора

19. На первый вход сдвигателя 17 поступает унитарный KOflJk. Сдвигатель 17 обеспечивает сдвиг информации, поступающей на второй вход, в сторону младших разрядов на число разрядов, равное номеру единичного разряда в унитарном коде, поступившем на первый вход с размножением левого разряда в освобождающихся при сдвиге разрядах. В результате на выходе сдвигателя 17 формируется код Ci| , который

поступает на первый вход сумматора 18 по модулю 2, на каждый разряд второго входа которого подается значение нулевого (знакового) разряда кода ak-1. В результате на выходе сумматора 18 по модулю 2 формируется значение SkCik , которое поступает на первый вход сумматора 19. На выходе сумматора 19 формируется в соответствии с (4) значение Сц , поступающее на первый информационный вход мультиплексора 15. Нулевое значение признака Конец операции обеспечивает прохождение кода Ci| на выход мультиплексора 15 и далее на информационный вход регистра 16.

Знаковые разряды кода Cik-: с выхода регистра 18 поступают на входы элемента Равнозначность 22. При совпадении знаковых разрядов кода Cik , что соответствует отсутствию переполнения в результате выполнения предыдущей итерации, на выходе элемента РАВНОЗНАЧНОСТЬ 22 формируется единичный уровень сигнала, который через элемент ИЛИ 20 проходит на второй вход элемента И 21, обеспечивая прохождение через элемент И 21 сигнала Занесение, поступающего на его первый вход. При несовпадении знаковых разрядов кода С|| - т, что соответствует наличию переполнения в результате выполнения предыдущей итерации, на выходе элемента РАВНОЗНАЧНОСТЬ 22 формируется нулевой уровень сигнала. Если присутствующее при этом на втором входе элемента ИЛ И 20 значение знакового (нулевого) разряда кода

ak-1 также равно нулю, на выходе элемента ИЛИ 20 формируется нулевой сигнал, который блокирует прохождение сигнала Занесение через элемент И 21 при нулевом значении признака Конец операции. В регистре 16 остается информация, зафиксированная в результате реализации итерации, при выполнении которой произошло пере- .полнение разрядной сетки. Сигнал с выхода элемента РАВНОЗНАЧНОСТЬ 22 через элемент НЕ 24 поступает также на выход 13 блока в качестве единичного значения признака Переполнение.

При единичном уровне сигнала на выходе элемента ИЛИ 20 очередной сигнал Занесение, поступающий на вход 28 блока, проходит через элемент И 21 на управляющий вход регистра 16, осуществляя занесение в регистр значения Сц.

По окончании вычислений сформированное в результате выполнения t-й итерации значение С|$ в качестве результата Ui поступает из регистра 16 через вентильную схему 23 на выход 12.1 блока.

При наличии на выходе 30 единичного значения признака Умножение на нуль, поступающего на второй инверсный вход вентильной схемы 23, на ее выходе формируется нулевое значение результата Ui.

При этом выполнение k-й итерации завершается.

Операционный блок 1.L+1 производит обработку переменной bk-1 аналогично описанному. Отличие заключается в формировании начального значения с переменной, обрабатываемой в данном блоке. При этом на вход 26 подается значение логического нуля, а на вход 9 - значение bo.

Вспомогательный операционный блок работает следующим образом.

В исходном состоянии на входы 40, 41, 5, 8, 42 и 43 блока поступают значения унитарного кода Jk, значение bk-1, значение множителя Y, значение делителя Z, признак Конец операции и сигнал Занесение соответственно.

На второй вход сумматора 31 по модулю 2, поступает (У+2)-разрядный код, содержащий в двух старших разрядах код знака множителя Y, n числовых разрядов кода множителя Y и (V-n) нулей в младших разрядах. На первый вход сумматора 31 по модулю 2 поступает код знака множителя. В результате на выходе сумматора 31 по модулю 2 формируется код модуля множителя, представленный с точностью . Аналогичным образом на выходе сумматора 32 по модулю 2 формируется код модуля делителя, представленный как и множитель с точностью . С выхода сумматора 31 по модулю 2 код модуля множителя поступает на первый вход сумматора 33, на второй вход которого с выхода сумматора 32 по модулю 2 поступает инверсный код модуля делителя. Таким образом на выходе сумматора 33 формируется начальное значение ао, поступающее далее на второй информационный вход мультиплексора 34.

Единичное значение признака Конец операции, поступающее с входа 42 на yrt

равляющий вход мультиплексора 34, обеспечивает прохождение кода аос второго информационного входа мультиплексора 34 на его выход и далее на информационный

вход регистра 35. В результате при единичном значении признака КОНЕЦ ОПЕРАЦИИ сигнал Занесение обеспечивает занесение значения ао в регистр 35. При выполнении k-й итерации г{1, 2,..., t} значение ak-1

0 с выхода регистра 35 поступает на второй вход сумматора 39, на первый вход которого поступает значение с выхода сумматора 38 по модулю 2. Сумматор 33 по модулю 2 обеспечивает поразрядное сложение по модулю

.5 2 значения, поступающего на его первый вход с выхода сдвигателя 36 с инверсным значением старшего знакового разряда ak-i(O). Значение ak-i(0) поступает с выхода элемента НЕ 37, значение на вход которого посту0 пает с выхода знакового (нулевого) разряда регистра 35. На первый вход сдвигателя 36 с входа 40 блока подается унитарный- кодЗЪ, на второй вход с входа 41 блока - значение кода bk-1. Сдвигатель 36 обеспечивает сдвиг

5 вправо кода, поступающего на его второй вход, на количество разрядов, равное номеру единице в унитарном коде3k. Старший нулевой разряд сдвигаемого кода при этом размножается. В результате на выходе

0 сдвигателя 36 формируется код bk-1 .

На выходе сумматора 33 формируется в соответствии с выражениями (1) значение ak аы -;Sk bk-1 , поступающее на первый информационный вход мультиплексора

5 34. Нулевое значение признака Конец операции обеспечивает прохождение кода ak на выход мультиплексора 34 и далее на информационный вход регистра. По сигналу ЗАНЕСЕНИЕ этот код записывается в ре0 гистр 35 и выдается на выход 44 блока,

Блок управления работает следующим образом.

На входы 51, 52, 6, 7, 8 и 5.поступают значения bk-1, ak-1, сигнал ПУСК, ТИ, код

5 делителя Z и код множителя Y соответственно. Сумматор 48 по модулю 2 формирует на выходе абсолютную величину кода ak-1, поступающего на его первый вход посредством поразрядного сложения по модулю 2

0 каждого разряда кода со знаковым (нулевым) разрядом этого кода, поступающим на второй вход сумматора 48 по модулю 2. Значение с выхода сумматора 48 по модулю 2 поступает на вход узла 49 формирования

5 номера старшей единицы. На вход узла 45 формирования номера старшей единицы поступает значение bk-1. Узлы 45 и 49 формируют унитарные коды, содержащие единицу в разряде, номер которого равен номеру старшей единицы в присутствующем на входе каждого узла коде. На первый управляющий вход сдвигателя 46 поступает унитарный код с выхода узла 45, обеспечивая сдвиг влево на количество разрядов, равное номеру единичного разряда j, в этом унитарном коде другого унитарного кода, поступающего с выхода узла 49 на второй информационный вход сдвигателя 46. Таким образом на выходе сдвигателя 46 формируется унитарный код, содержащий единицу в разряде, номер которого равен разности номеров старших единичных разрядов в кодах а|с-1 и bk-1 соответственно. В случае, если номер JK-,старшего единичного разряда кода меньше или равен номеру jkiстаршего единичного разряда кода bk- -1 на выходе сдвигателя 46 формируется код, содержащий одни нули. Сформированный таким образом код поступает на первый вход узла 47 формирования управляющего сигнала кода, на второй вход которого подается нулевой (знаковый) разряд кода аы. На выходе узла и далее на первом выходе 53 блока формируется в соответствии с (2) унитарный код 3k, определяющий величину сдвига jk.

На выходах 54,10,11 и 55 блока формируются соответственно сигнал Занесение, признак Конец операции, признак Деление на нуль и признак Умножение на нуль.

Узел формирования управляющих сигналов работает следующим образом.

На входы 6,7,59,8 и 5 поступают сигнал ПУСК, Tl/l, m старших числовых разрядов кода/ак-1(п+1) раз рядный код делителя Zn (п+1)-разрядный код множителя соответственно. Если на всех входах первого элемента И 56 присутствуют нулевые значения, на его выходе формируется единичное значение, которое проходя через второй элемент ИЛИ 57 поступает на выход 10 узла в качестве признака Конец операции, а также на второй инверсный вход второго элемента И 56, блокируя прохождение через него ТИ. Третий и четвертый элементы ИЛИ 57 формируют на своих выходах одиночные значения в случае, если на их входах присутствует лишь нулевое значение, Значения с выходов этих элементов поступают на информационные входы первого и второго триггеров 58 соответственно. На вторые управляющие входы этих триггеров подается сигнал ПУСК с входа 6 узла, обеспечивая запоминание сформированных значений признаков Деление на нуль и Умножение на нуль соответственно в момент начала операции и сохранение этих признаков до появления следующего сигнала ПУСК. Значения с выходов этих триггеров поступают на выходы 11 и 55 узла, а также на второй и третий входы второго элемента ИЛИ 57, формируя на его выходе соответствующее значение

признака Конец операции.

Появление на первом входе первого элемента ИЛИ 57 единичного значения сигнала Пуск обеспечивает формирование на его выходе сигнала Занесение, который

затем может формироваться на основе ТИ при нулевом значении признака Конец операции. Сигнал Занесение во втором случае формируется на выходе второго элемента И 56 и далее через второй вход

первого элемента ИЛИ 57.

Узел формирования управляющего кода работает следующим образом.

На входы 62 и 63 подаются значения m-разрядного унитарного кода и значение

нулевого знакового разряда кода ak-1 соответственно.

В случае, если на входе 62 присутствует код, содержащий только нулевые значения, на выходе первого элемента ИЛИ 60 формируется единичное значение, которое поступает на первый вход первого .элемента И 61, на второй вход которого подается значение нулевого (знакового) разряда кода аы. Таким образом, величина сдвига jk будет сформирована в соответствии с (2). Второй элемент И 61 формирует единичное значение в случае, если на входах 62 и 63 одновременно присутствуют только нулевые значения, что соответствует ситуации jK-,

jk2 и ak-i(O) 0. При этом унитарный код 3k содержит единицу в нулевом разряде, что определяет передачу информации без сдвига.

Таким образом, положительный эффект

предлагаемого устройства заключается в расширении функциональных возможностей.

Ф о р м у л а и з о б р ет е н и я 1. Устройство для выполнения век- торно-скалярных операций над действительными числами, содержащее (L+1) операционных блоков (L - количество компонентов векторного операнда) и блок управ- ления, причем вход 1-го компонента

векторного операнда устройства (Wt{1, 2

L}) соединен с первым информационным входом 1-го операционного блока, первый выход которого соединен с выходом 1-го компонента вектора результата устройства, а второй выход - с выходом 1-го признака переполнения устройства, вход делителя устройства соединен с первым информационным входом (L+1)-rp операционного блока, первый выход которого соединен с входом

признака делителя блока управления, вход запуска и тактовый вход которого соединен с входом запуска и тактовым входом устройства соответственно, выход признака деления на нуль которого соединен с первым выходом блока управления, второй выход которого соединен с выходом признака конца операции устройства и входом разрешения счета каждого операционного блока, второй информационный вход каждого операционного блока соединен с третьим выходом блока управления, четвертый выход которого соединен с входами разрешения записи всех операционных блоков, отличающееся тем, что, с целью расширения функциональных возможностей за счет выполнения операции вида Ui у- Y , в него

введены вспомогательный операционный блок и элемент НЕРАВНОЗНАЧНОСТЬ, выход которого соединен с входом формирователя знака 1-го операционного блока, вход формирования знака (L+1)-ro операционного блока соединен с входом логического нуля устройства, вход множителя которого соединен с входом признака множителя блока управления и первым информационным входом вспомогательного операционного блока, второй информационный вход которого соединен с входами делителя устройства и блока управления, вход промежуточного кода которого соединен с выходом вспомогательного операционного блока и третьими информационными входами всех операционных блоков, вход признака умножения на нуль которых соединены с пятым выходом блока управления, второй, третий и четвертый выходы которого соединены соответственно с входом разрешения счета, третьим информационным входом и входом разрешения записи вспомогательного операционного блока, вход делителя которого соединен с выходом ()-го операционного блока, входы знаковых разрядов множителя и делителя устройства соединены соответственно с первым и вторым входами элемента НЕРАВНОЗНАЧНОСТЬ.

2. Устройство по п.1, о т л и ч а ю щ е е- с я тем, что операционный блок содержит два сумматора по модулю 2, мультиплексор, регистр, сдвигатель, два элемента И, элемент ИЛИ, элемент РАВНОЗНАЧНОСТЬ, сумматор и элемент НЕ, выход которого соединен с вторым выходом блока, первый выход которого соединен с выходом первого элемента И, первый инверсный вход которого соединен с входом признака умножения на нуль блока, второй информационный вход которого соединен с входом управления сдвигом сдвигателя, информационный вход которого соединен с выходом регистра, входом первого слагаемого сумматора и вторым входом первого элемента И, выходы знаковых разрядов регистра соединены с первым и вторым входами элемента РАВНОЗНАЧНОСТЬ, выход которого соединен с входом элемента НЕ и первым

входом элемента ИЛИ, второй вход которого соединен с третьим информационным входом блока и входом первого слагаемого первого сумматора по модулю 2, вход вторс, го слагаемого которого соединен с выходом

сдвигателя, а выход- с входом второго слагаемого сумматора, выход которого соединен с первым информационным входом мультиплексора, второй информационный вход которого соединен с выходом второго

сумматора по модулю 2, входы первого и второго слагаемых которого соединены соответственно с входом формирования знака и первым информационным входом блока, вход разрешения счета которого соединен с

третьим входом элемента ИЛИ и управляющим входом мультиплексора, выход которого соединен с информационным входом . регистра, вход записи которого соединен с выходом второго элемента И, первый и второй входы которого соединены соответственно с входом разрешения записи блока и выходом элемента ИЛИ.

3. Устройство поп.1,отличающеес я тем, что вспомогательный операционный блок содержит три сумматора по модулю 2, два сумматора, мультиплексор, регистр, сдвигатель и элемент НЕ, выход которого соединен с входом первого слагаемого первого сумматора по модулю 2, вход второго слагаемого которого соединен с выходом сдвигателя, вход управления сдвигом и информационный вход которого соединен соответственно с третьим информационным входом и входом делителя блока, первый и второй информационные входы которого соединены соответственно с входами слагаемых второго и третьего сумматоров по модулю 2, выходы которых соединены соответственно с входами первого и второго слагаемых первого сумматора, выход которого соединен с первым информационным входом мультиплексора, второй информационный вход которого соединен с выходом второго

сумматора, вход первого слагаемого которого соединен с выходом первого сумматора по модулю 2, а вход второго слагаемого - с входом элемента НЕ, выходом блока и выходом регистра, информационный вход которого со- единен с выходом мультиплексора, управляющий вход которого соединен с входом разрешения счета блока, вход разрешения записи которого соединен с входом записи регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления квадратного корня из суммы квадратов | 1990 |

|

SU1751751A1 |

| Устройство для выполнения векторно-скалярных операций над действительными числами | 1990 |

|

SU1718215A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ НАТУРАЛЬНОГО ЛОГАРИФМА КОМПЛЕКСНОГО ЧИСЛА | 1991 |

|

RU2010312C1 |

| Устройство для деления чисел | 1990 |

|

SU1795456A1 |

| УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОГО ДЕЛЕНИЯ ЧИСЕЛ | 1991 |

|

RU2010311C1 |

| Устройство для вычисления функций двух аргументов | 1986 |

|

SU1413626A1 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Устройство для вычисления функций @ @ @ @ и @ @ @ @ | 1990 |

|

SU1732342A1 |

| УСТРОЙСТВО ВЫЧИСЛЕНИЯ СУММ ПРОИЗВЕДЕНИЙ | 2006 |

|

RU2306595C1 |

| Устройство для умножения | 1981 |

|

SU1018115A1 |

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных выII xi да Ui - у числительных системах для аппаратной реализации векторно-скалярных операций виY 1б{1, 2L} (L - количество компонентов векторного операнда) для действительных чисел,-представленных в дополнительном коде в форме с фиксированной запятой. Цель изобретения - расширение функциональных возможностей устройства за счет выполнения опера- Xi ции вида Ui Y .Поставленная цель достигается тем, что в устройство, содержащее (L+1) операционных блоков и блок управления, введены вспомогательный операционный блок и элемент НЕРАВНОЗНАЧНОСТЬ. 2 з.п. ф-лы, 6 ил. сл с

Фиг.1

40 о#

оа:

J7

J4

35

42 о-

Фиг. 2

.J5

п

Jtf

1

53

Фие.З

Фиг Л

Фиг. 5

$иг. 6

| Устройство для выполнения операций умножения и деления | 1986 |

|

SU1403061A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1618165, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-04-23—Публикация

1990-04-26—Подача