Изобретение относится к автоматике и вычислительной технике и молчат быть использовано для организации шагового режима работы в устройствах с динамической памятью..

Цель -изобретения - повьшение надежности устройства.

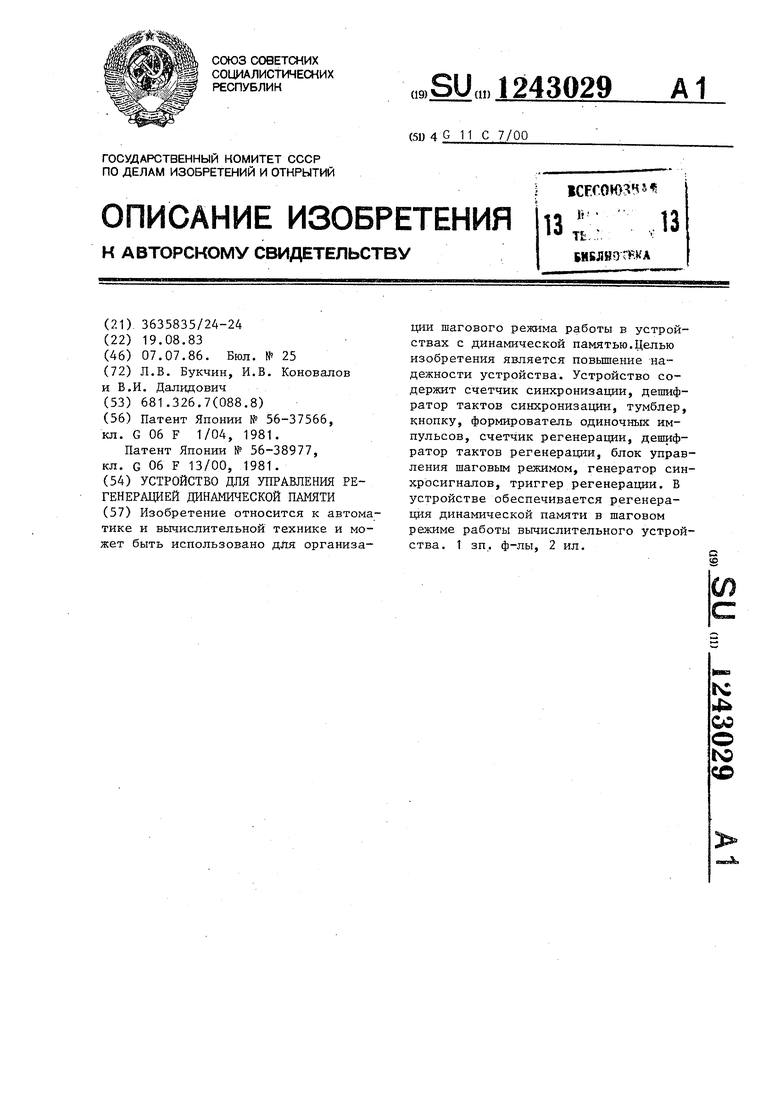

На фиг. 1 представлена схема устройства для управления регенерацией динамической памятиj на фиг. 2 - схема блока управления шаговым режимом .

Устройство содержит первый счетчик

1синхронизации, первый дешифратор

2тактов синхронизации, тумблер 3, ключ 4, формирователь 5 одиночных импульсов, второй счетчик б регенерации, второй дешифратор 7 тактов регенерации, блок 8 управления шаговым редсимом, генератор 9 синхросигналов, триггер 10 регенерации.

Блок 8 управления шаговым режимом содержит первый триггер 11,, первый элемент И-НЕ 12, второй триггер 13, третий триггер 14, второй 15, третий 16 и четвертый 17 элементы И-НЕ.

Устройство работает следуюш;йм образом.

В начальном состоянии триггеры 11 13 и 14 блока В управления шаговым режимом сброшены. Синхросигнал с генератора 9 через элементы И-НЕ 17 и 16 нараш;ивает счетчик 1 синхронизации и стробирует дешифратор 2 тактов синхронизации, работаюш е анало - гично счетчику 6 и дешифратору 7. На выходе дешифратора 2 появляется тактовая последовательность Т,.|, .. , Т-;, цикл которой равен удвоенному циклу регенерации памяти,

В режимах записи и считывания старт памяти производится по такту Т и к моменту появления такта процесс записи или считывания заканчивается.По тактуTN/2устанавливается триг гер 10, выходной сигнал которого подается в память для задания режима регенерации по такту (Т.м/2) + 1„ По такту Т/у сбрасывается триггер 10, и цикл регенерации завершается. Таким обра- зон, в течение одной последовательности тактов If, ,, ,, ,Т|х прО Изводятся как рабочий цикл, так и цикл регенерации.

Для перевода блока в шаговый режлм работы включается тумблер 3. При этом по заднему фронту N-ro такта регенерации (по окончании полного цикла)

устанавливается D-триггер 11, которы блокирует прохождение синхросигнала через элементы И-НЕ-17 и 16 на вход счетчика 1. Счетчик 6 продолжает работать, благодаря чему регенерация памяти не прерывается. Счетчик 1 останавливается в состоянии ожидания 1--ГО такта, и вьшолнение текущей операции устройством прекращается. Сейчас любой такт, появляющийся на выходе дешифратора 2, должен совпадать во времени с 1-м тактом регенерации, поскольку он может быть сигналом старта в рабочем цикле памяти и должен отстоять от начала цикла регенерации на время, достаточное для проведения цикла чтения или записи.

При включении ключа 4 формирователь 5 Бырз.батьтает одиночный импуль который проходит через элемент И-НЕ 12 и устанавливает триггер 14. По задн€;му фронту последнего в цикле N-ro такта регенерации устанавливается триггер 13J что разрешает прохождение 1--ГО такта регенерации через элементы 15 и 16 на вход счетчика 1 и дешифратора 2. На выходе дешифратора 2 появляется синхроимпульс, соответствующий первому такту синхронизации устройства. Счетчик 1 устанавливается в состояние ожидания 2-го такта. По заднему фронту 1-го такта регенерации сбрасывается триггер 14, а по заднему фронту N-ro такта р еген рации - триггер 13, Тем самым схема приводится в исходное состояние,При следующем включении ключа 4 процесс повторяется, на выходе дешифратора 2 появляется 2-й такт синхронизации и т.д.

при вьшяючении тумблера 3 по заднему фронту N-ro такта регенерации (по завершении полного цикла) сбрасывается триггер 11, синхросигнал генератора 9 через элементы 17 и 16 начинает поступать на вход счетчика 1 и дешифратора 2 и блок переходит в непрерывный режим работы,.

Формула изобретения

1 . Устройство для управления реге нерацией динамической памяти, содержащее первый дешифратор, одни входы которого соединены с выходами первого счетчика, а выходы являются выходами синхронизации устройства, формирователь одиночных импульсов, ключ, вход которого является входом режима

регенерации устройства, генератор синхросигналов, отличающее- с я тем, что, с целью повьшения надежности устройства, в него введены второй счетчик, второй дешифратор, триггер и блок управления шаговым режимом, причем один вход второго дешифратора соединен с входом второго счетчика, а другие входы дешифратора подключены к выходам второго счетчика, к первому входу блока управления

шаговым режимом и к выходу генератора синхросигналов, первый выход второго дешифратора является первым управляющим выходом устройства, второй и третий выходы подключены соответственно к второму и третьему входам блока управления шаговым режимом, а четвертый и пятый выходы соединены с соответствующими установочными вкодами триггера, выход которого является вторым управляющим выходом устройства, четвертый и пятый входы блока управления шаговым режимом подключены соответственно к выходу ключа и к выходу формирователя одиночных импульсов , а выход соединен с входом первого счетчика и с другим входом первого дешифратора.

15

а 2о 2430294

2. Устройство по п.1, отличающееся тем, что блок управления шаговым режимом содержит первый триггер, прямой выход которого соеди- 5 вен с вторым входом первого элемента И-НЕ, а инверсный выход подключен к первому входу четвертого элемента И-НЕ, второй триггер, прямой выход которого соединен с вторым входом 10 второго элемента И-НЕ, третий триггер , S-вход которого подключен к выходу первого элемента И-НЕ, D-вход соединен с шиной нулевого потенциала, С-вход подключен к первому входу третьего элемента И-НЕ и к выходу второго элемента И-НЕ, а выход соединен с D-входом второго триггера,. выход четвертого элемента И-НЕ подключен к второму входу третьего элемента И-НЕ, выход которого является выходом блока управления шаговым режимом, а второй вход четвертого элемента И-НЕ, первый вход второго элемента И-НЕ, объединенные С-входы пер- вого и второго триггеров, D-вход первого триггера и первый вход первого элемента И-НЕ являются соответственно первым, вторым, третьим,четвертым и пятым входами блока управления шаговым режимом.

25

У Peze/ epoL i/ фиг.1

Кформироёотелю

НтумдлеруЗ

S

11

12

/4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Устройство для сопряжения модулей процессора | 1982 |

|

SU1056176A2 |

| Устройство для управления оперативной памятью | 1985 |

|

SU1291992A1 |

| Адаптивное устройство для обучения языкам | 1987 |

|

SU1441445A1 |

| Мультимикропрограммное устройство управления | 1983 |

|

SU1161942A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Устройство для синхронизации | 1981 |

|

SU1012228A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для организации шагового режима работы в устройствах с динамической памятью.Целью изобретения является повышение надежности устройства. Устройство содержит счетчик синхронизации, дешифратор тактов синхронизации, тумблер, кнопку, формирователь одиночных импульсов, счетчик регенерации, дешифратор тактов регенерации, блок управления шаговым режимом, генератор синхросигналов, триггер регенерации. Б устройстве обеспечивается регенерация динамической памяти в шаговом режиме работы вычислительного устройства. 1 зп. ф-лы, 2 ил. c со ISD со

Hdeuiu{p/}a- тору 7

Ндеш1/фра- тору -

15

13 о--

/f CVe/77Vl//f f

/i eeHepof/TJopyff

Редактор В. Петраш

Составитель О, Исаев Техред М.Моргентал

Заказ 3711/52 Тираж 543Подписное

ВНИИПИ Гocyдapcтвeннo o комитета СССР

по делам изобретений и открытий 113033, Москва, Ж-35, Раушская наб., i ,д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Л

L:J

фид,1

Корректор А. Тяско

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-07—Публикация

1983-08-19—Подача