1

1

Изобретение-относится к вычислительной технике и может быть использовано для распознавания и синтеза сигналов, в автоматизированных словарях и т.п.

Цель изобретения - повышение надежности устройства.

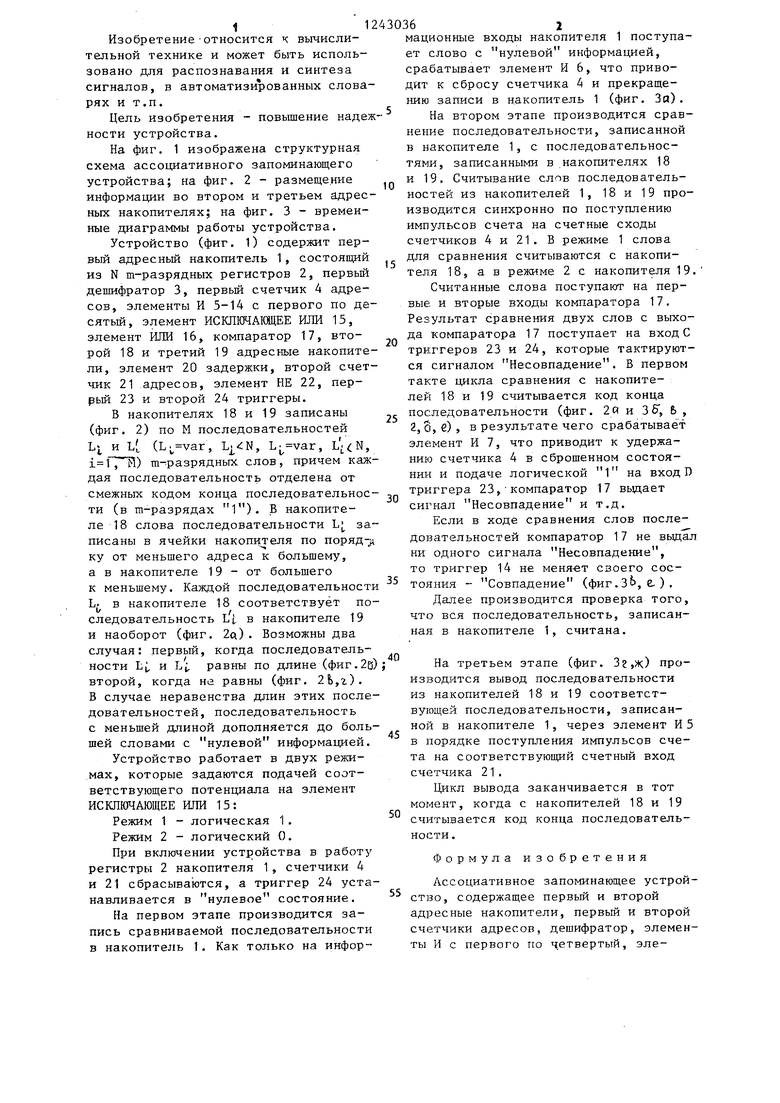

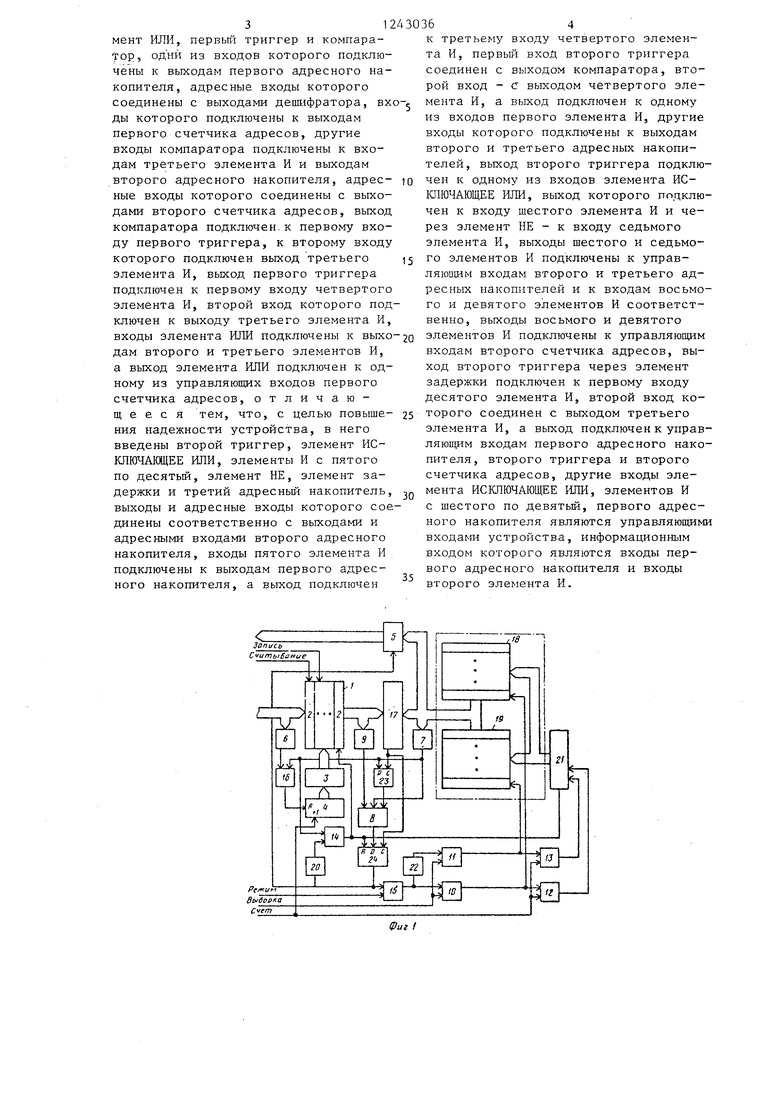

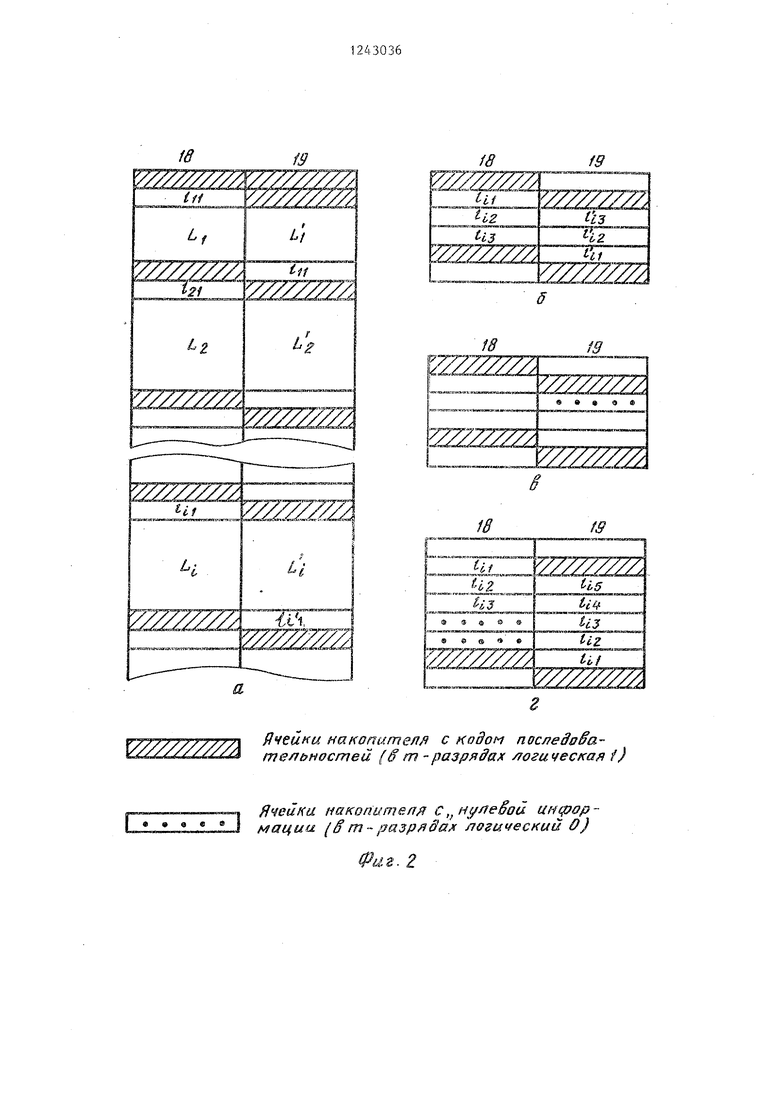

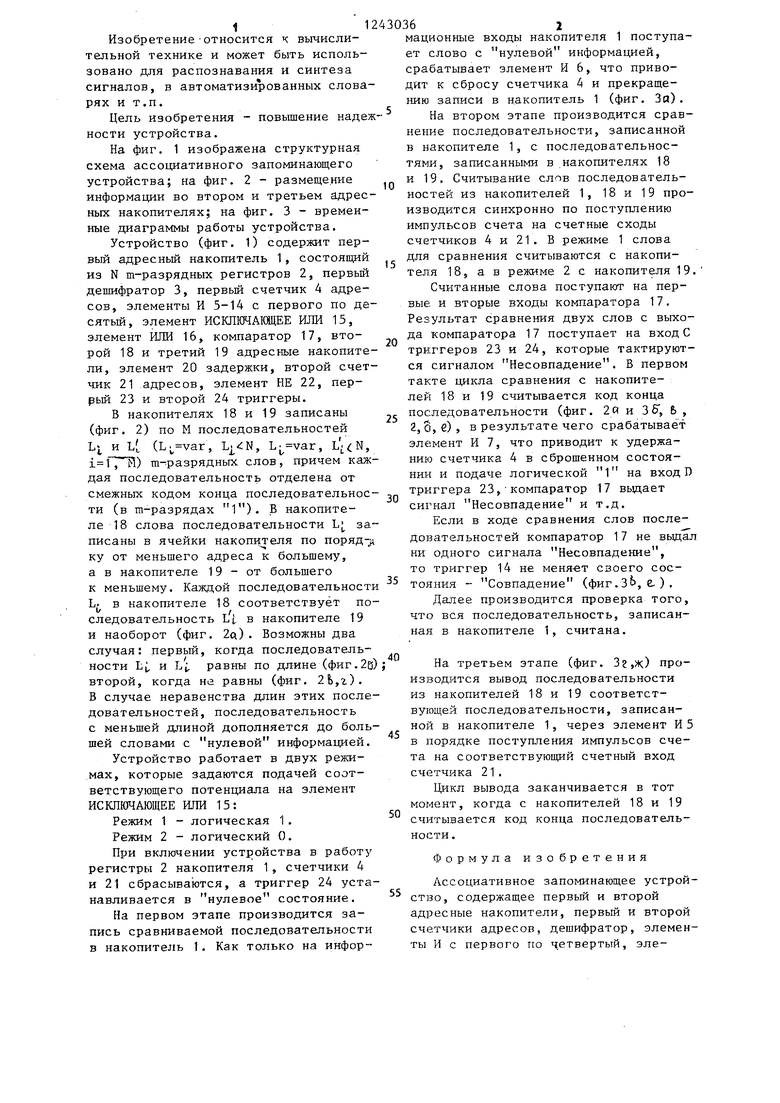

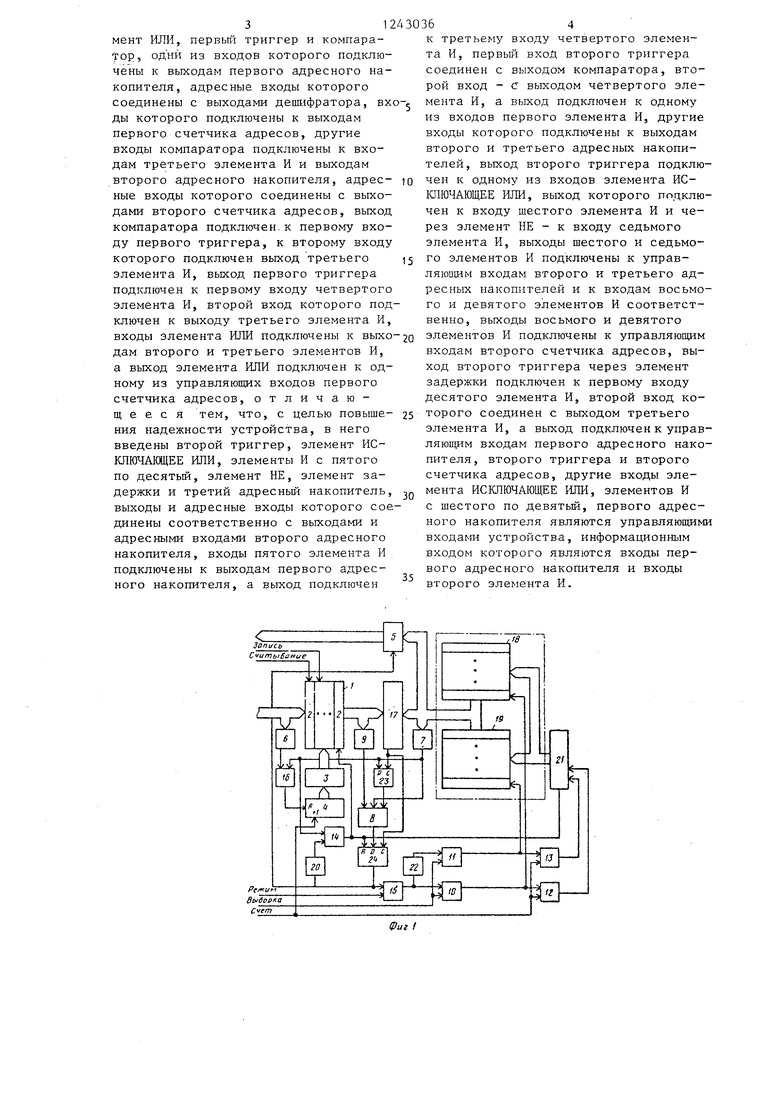

На фиг. 1 изображена структурная схема ассоциативного запоминающего устройства; на фиг. 2 - размещение информации во втором и третьем адресных накопителях; на фиг. 3 - временные диаграммы работы устройства.

Устройство (фиг. 1) содержит первый адресный накопитель 1, состоящий из N т-разрядных регистров 2, первьй дешифратор 3, первый счетчик 4 адресов, элементы И 5-14 с первого по десятый, элемент ИСКПЮЧАЩЕЕ ИЛИ 15, элемент ИЛИ 16, компаратор 17, второй 18 и третий 19 адресные накопители, элемент 20 задержки, второй счетчик 21 адресов, элемент НЕ 22, пер- рьш 23 и второй 24 триггеры.

В накопителях 18 и 19 записаны (фиг. 2) по М последовательностей L HL(. (, , , L .N, ,H) га-разрядных, слов, причем каждая последовательность отделена от смежных кодом конца последовательности (в та-разрядах 1). В накопителе 18 слова последовательности Lj записаны в ячейки накопителя по поряд-д ку от меньшего адреса к большему, а в накопителе 19 - от большего к меньшему. Каждой последовательности

ч

в накопителе 18 соответствует

последовательность L t в накопителе 19 и наоборот (фиг. 2й.) . Возможны два случая: первый, когда последовательности L и Li, равны по длине (фиг. 2s) второй, когда нз равны (фиг. 2),г). В случае неравенства длин этих последовательностей, последовательность с меньшей длиной дополняется до большей словами с нулевой информацией.

Устройство работает в двух режимах, которые задаются подачей соответствующего потенциала на элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 15:

Режим 1 - логическая 1.

Режим 2 - логический О.

При включении устройства в работу регистры 2 накопителя 1, счетчики 4 и 21 сбрасываются, а триггер 24 устанавливается в нулевое состояние.

На первом этапе производится запись сравниваемой последовательности в накопитель 1. Как только на инфор1243036

5

0

5

0

мационные входы накопителя 1 поступает слово с нулевой информацией, срабатывает элемент И 6, что приводит к сбросу счетчика 4 и прекращению записи в накопитель 1 (фиг. За).

На втором этапе производится сравнение последовательности, записанной в накопителе 1, с последовательностями, записанными в накопителях 18 и 19, Считывание слов последовательностей из накопителей 1, 18 и 19 производится синхронно по поступлению импульсов счета на счетные сходы счетчиков 4 и 21. В режиме 1 слова для сравнения считываются с накопителя 18, а в релдаме 2 с накопителя 19.

Считанные слова поступают на первые и вторые входы компаратора 17. Результат сравнения двух слов с выхода компаратора 17 поступает на вход С триггеров 23 и 24, которые тактируются сигналом Несовпадение. В первом такте цикла сравнения с накопителей 18 и 19 считывается код конца последовательности (фиг. 2 и и 3 6, 6 , 2,6, е), в результате чего срабатывает элемент И 7, что приводит к удержанию счетчика 4 в сброшенном состоянии и подаче логической 1 на входD триггера 23,компаратор 17 вьщает сигнал Несовпадение и т.д.

Если в ходе сравнения слов последовательностей компаратор 17 не вьодал ни одного сигнала Несовпадение, то триггер 14 не меня-ет своего сос- 5 тояния - Совпадение (фиг.ЗЬ, е.).

Далее производится проверка того, что вся последовательность, записанная в накопителе 1, считана.

На третьем этапе (фиг. 3,x) производится вывод последовательности из накопителей 18 и 19 соответствующей последовательности, записанной в накопителе 1, через элемент И 5 в порядке поступления импульсов счета на соответствующий счетный вход счетчика 21,

Цикл вывода заканчивается в тот момент, когда с накопителей 18 и 19 считывается код конца последовательности .

Формула изобретения

Ассоциативное запоминающее устройство, содержащее первый и второй адресные накопители, первый и второй счетчики адресов, дешифратор, элементы И с первого по ч.етвертый, элемент ИЛИ, первый триггер и компаратор, од нй из входов которого подключены к выходам первого адресного накопителя, адресные входы которого соединены с выходами дешифратора, вх ды которого подключены к выходам первого счетчика адресов, другие входы компаратора подключены к входам третьего элемента И и выходам второго адресного накопителя, адрес- ные входы которого соединены с выходами второго счетчика адресов, выход компаратора подключен, к первому входу первого триггера, к второму входу которого подключен выход третьего элемента И, выход первого триггера подключен к первому входу четвертого элемента И, второй вход которого подключен к выходу третьего элемента И, входы элемента ИЛИ подключены к выхо дам второго и третьего элементов И, а выход элемента ИЛИ подключен к одному из управляющих входов первого счетчика адресов, отличающееся тем, что, с целью повыше- ния надежности устройства, в него введены второй триггер, элемент ИС- КЛЮЧАЩЕЕ ИЛИ, элементы И с пятого по десятый, элемент НЕ, элемент задержки и третий адресный накопитель, выходы и адресные входы которого соединены соответственно с выходами и адресными входами второго адресного накопителя, входы пятого элемента И подключены к выходам первого адресного накопителя, а выход подключен

к третьему входу четвертого элемента И, первый вход второго триггера соединен с выходом компаратора, второй вход - с выходом четвертого элемента И, а выход подключен к одному из входов первого элемента И, другие входы которого подключены к выходам второго и третьего адресных накопителей, выход второго триггера подключен к одному из входов элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к входу шестого элемента И и через элемент НЕ - к входу седьмого элемента И, выходы шестого и седьмого элементов И подключены к управ- ляюшдм входам второго и третьего адресных накопителей и к входам восьмого и девятого элементов И соответственно, выходы восьмого и девятого элементов И подключены к управляюш 1м входам второго счетчика адресов, выход второго триггера через элемент задержки подключен к первому входу десятого элемента И, второй вход которого соединен с выходом третьего элемента И, а выход подключен к управляющим входам первого адресного накопителя, второго триггера и второго счетчика адресов, другие входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, элементов И с шестого по девятый, первого адресного накопителя являются управляюпщми входаг га устройства, информационным входом которого являются входы первого адресного накопителя и входы второго элемента И.

16

19

18

fff

Составитель В.Рудаков Редактор A.Ворович Техред М.Моргентал Корректоров.

Заказ 3711/52 Тираж 543Подписное

ВШ-ШПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно

-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

I

-i

I I

|N , Oi

11

.s

I

:§ s

I

II l||

1

1 Ч 1 I

Hi

t, «;,|;

III

с c.

i i

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное запоминающее устройство | 1983 |

|

SU1174988A1 |

| Способ записи - воспроизведения цифровой информации и устройство для его осуществления | 1990 |

|

SU1721630A1 |

| Ассоциативное запоминающее устройство | 1987 |

|

SU1432608A1 |

| УСТРОЙСТВО ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ ЦИФРОВОЙ ИНФОРМАЦИИ | 1992 |

|

RU2039382C1 |

| Ассоциативное запоминающее устройство | 1988 |

|

SU1587586A1 |

| Запоминающее устройство | 1983 |

|

SU1115105A1 |

| Устройство для идентификации паролей пользователей | 1988 |

|

SU1661814A1 |

| Устройство для обучения | 1987 |

|

SU1559366A1 |

| Кольцевая пакетная сеть передачи информации | 1987 |

|

SU1555888A1 |

| Устройство для поиска информации в накопителе на магнитных дисках | 1982 |

|

SU1117652A1 |

Изобретение относится к вычислительной технике и может быть использовано для распознавания и синтеза сигналов, в автоматизированных словарях и т.п.. Цель изобретения - повышение надежности устройства. Ассоциативное запоминающее устройство содержит первьй и второй адресные накопители, счетчики адресов, дешифратор, элементы И с первого по четвер- тьй, элемент ИЛИ, первый триггер и компаратор. Цель изобретения достигается введением второго триггера, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, элементов И с пятого по десятьй, третьего адресного накопителя. В процессе ра боты устройства в первьй адресньй накопитель записывается сравниваемая информация, а второй и третий адресные накопители содержат хранимые последовательности слов (во втором накопителе они записаны по порядку рт меньшего адреса к большему, а в третьем - от большего к меньшему). 3 ил. с и

| Кохонен Т | |||

| Ассоциативные запомишющие устройства | |||

| М.: Мир, 1982, с | |||

| Джино-прядильная машина | 1922 |

|

SU173A1 |

| Ассоциативное запоминающее устройство | 1983 |

|

SU1174988A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-07-07—Публикация

1984-10-17—Подача