Изобретение относится к вычислительной технике и предназначено для построения арифметическо-логических устройств.

Цель изобретения - уменьшение количества оборудования.

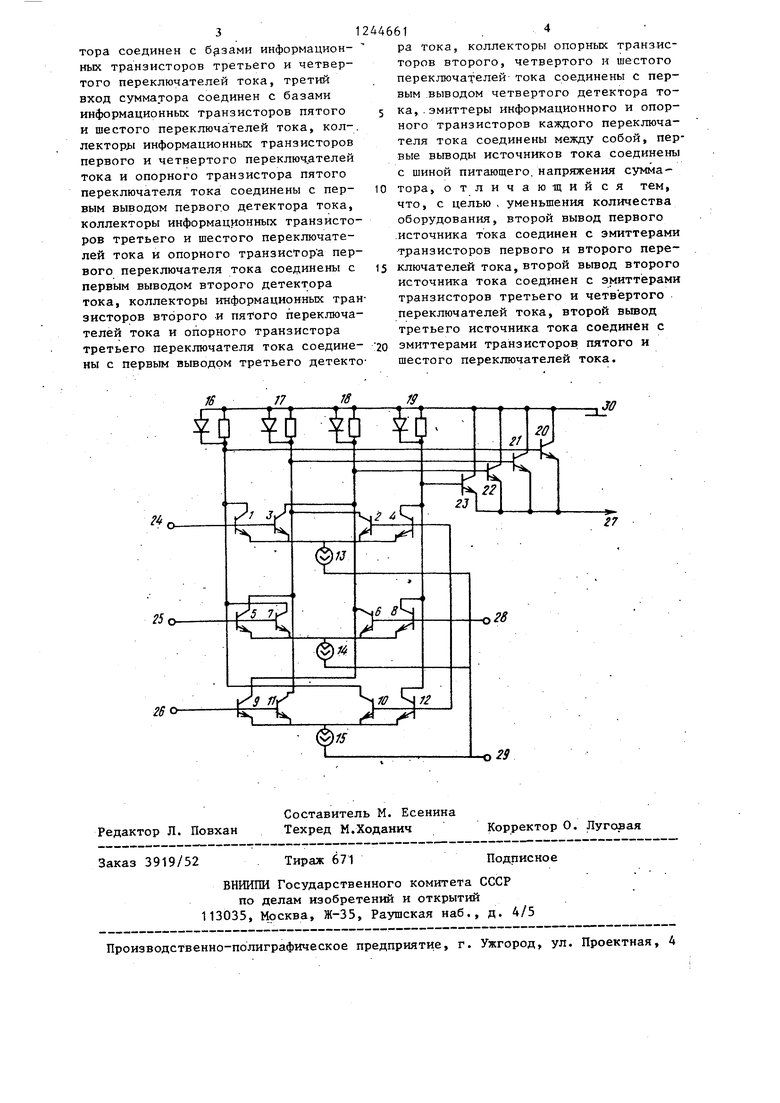

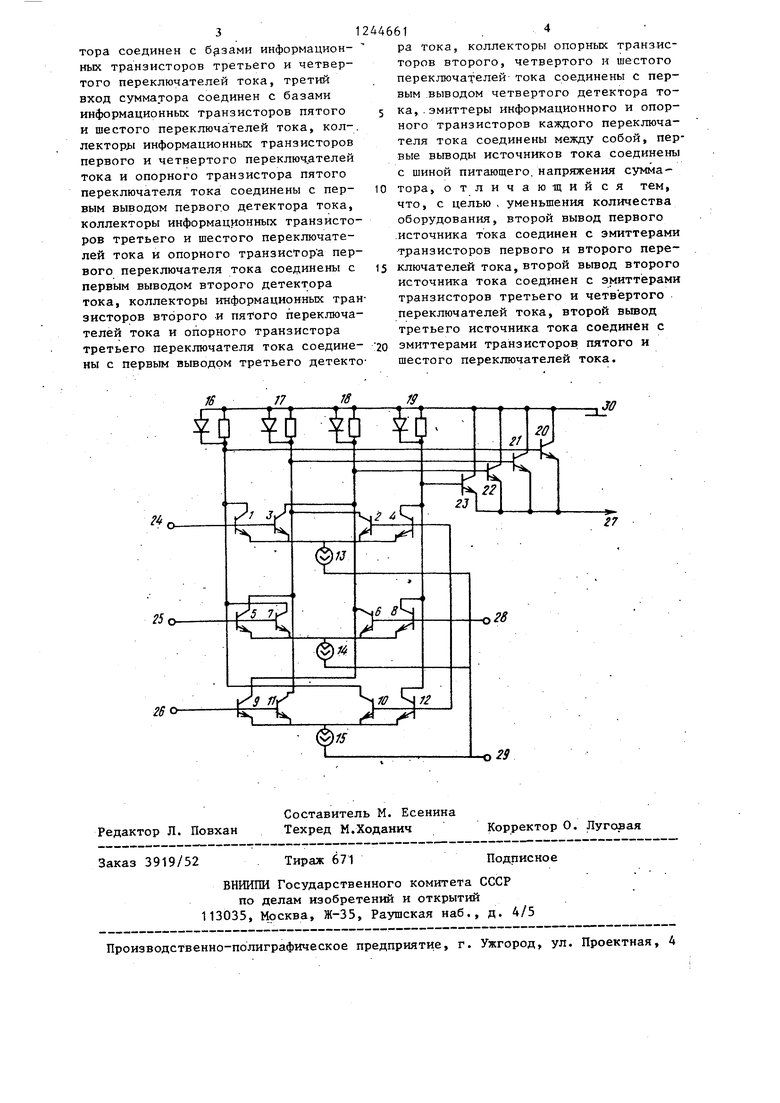

.На чертеже приведена принципиальная схема двоичного сумматора.

Сумматор содержит первый переклю- чатель тока, построенный на информационном и опорном транзисторах 1 и 2; второй, третий, четвертый, пятый, шестой переключатели тока, построенные соответственно на информационных и опорных транзисторах 3 и 4, 5 и 6, 7 и 8,9 и 10, 11 и 12; первый, второй и третий источники тока 13, 14 и 15 соответственно; детекторы 16, 17, 18 и 19 тока; эмиттерные повторители 20, 21, 22, 23 на транзисторах, вход 24, 2, 26, выход 27 суммы, шину 28 опорного напряжения, шину 29 питающеФормула изобре.те ни я Двоичный сумматор, содержащий шесть переключателей тока, состоящих каждый из информационного и опорного транзисторов, четыре эмиттерных повторителя, четыре детектора тока, три источника тока, причем первый вход сумматора соединен с базами информационных транзисторов первого второго пб;реключателей тока, эмитте- ;ры транзисторов эмиттерных повторителей объединены между собой и сое-

го напряжения, шину 30 нулевого потенциала .

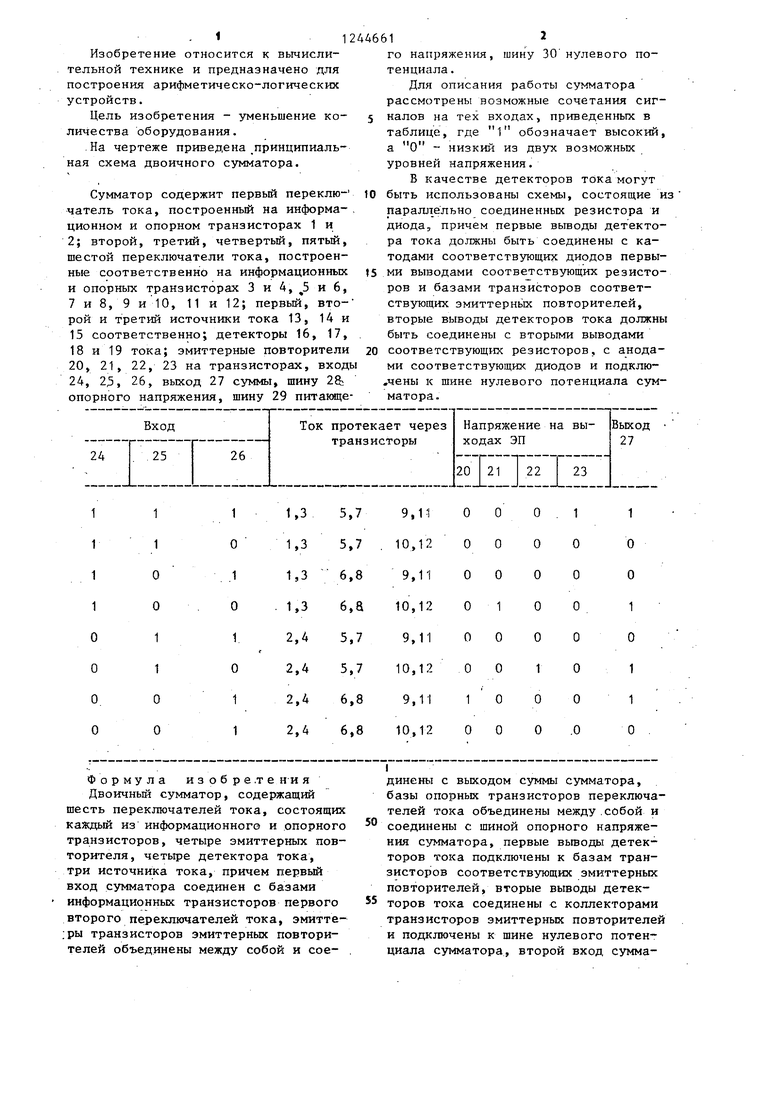

Для описания работы сумматора рассмотрены возможные сочетания сигналов на тех входах, приведенных в таблице, где 1 обозначает высокий, а О - низкий из двух возможных уровней напряжения.

В качестве детекторов тбка могут

быть использованы схемы, состоящие из паралл ельно соединенных резистора и диода., причем первые выводы детектора тока должны быть соединены с катодами соответствующих диодов первыми выводами соответствующих резисторов и базами транзисторов соответствующих эмиттерньпс повторителей, вторые выводы детекторов тока должны быть соединены с вторыми выводами

соответствующ гх резисторов, с анодами соответствующих диодов и подклю- ,чены к щине нулевого потенциала сумматора.

I

динены с выходом суммы сумматора, базы опорных транзисторов переключателей тока объединены между .собой и соединены с шиной опорного напряжения с:,т матора, первые вьгаоды детекторов тока подклю шны к базам транзисторов соответствующих эмиттерных повторителей, вторые выводы детекторов тока соединены с коллекторами транзисторов эмиттерных повторителей и под1слючены к шине нулевого потенциала су1 1матора, второй вход сумма31

тора соединен с базами информационных транзисторов третьего и четвертого переключателей тока, третий вход сумматора соединен с базами информационных транзисторов пятого и шестого переключателей тока, кол-, лектор информационных транзисторов первого и четвертого переключ.ателей тока и опорного транзистора пятого переключателя тока соединены с первым выводом первого детектора тока, коллекторы информационных транзисторов третьего и шестого переключателей тока и опорного транзистор а первого переключателя тока соединены с первым выводом второго детектора тока, коллекторы информационных тран зисторов второго и пятого переключателей тока и опорного транзистора третьего переключателя тока соединены с первым выводом третьего детекто

1В

77

J8

Редактор Л. Повхан

Составитель М. Есенина Техред М.Ходанич

Заказ 3919/52

Тираж 671

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, А

44661 . 4

ра тока, коллекторы опорных транзисторов второго, четвертого и шестого переключателей тока соединены с первым выводом четвертого детектора то- 5 ка,.эмиттеры информационного и опорного транзисторов каждого переключателя тока соединены между собой, первые вьгеоды источников тока соединены с шиной питающего, напряжения сумма -

10 тора, отличающийся тем, что, с целью , уменьшения количества оборудования, второй вывод первого .источника тока соединен с эмиттерами транзисторов первого и второго пере15 ключателей тока, второй вывод второго источника тока соединен с эмиттерами транзисторов третьего и четвертого переключателей тока, второй вывод третьего источника тока соединен с

;2о эмиттерами транзисторов пятого и шестого переключателей тока.

Г9

Корректор О. Луговая

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРЕХВХОДОВЫЙ СУММАТОР | 1972 |

|

SU429422A1 |

| Троичный счетный триггер | 1979 |

|

SU864503A1 |

| Полный троичный сумматор | 1979 |

|

SU826342A1 |

| Усилитель записи - считывания | 1989 |

|

SU1674250A1 |

| Троичный фронтальный Д-триггер | 1980 |

|

SU917307A1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ ТРОИЧНОЙ ЛОГИКИ И УСТРОЙСТВА НА ЕГО ОСНОВЕ | 2009 |

|

RU2394366C1 |

| Д-триггер типа М-S | 1986 |

|

SU1363449A1 |

| Трехвходовой дешифратор | 1974 |

|

SU517155A1 |

| Д-триггер | 1982 |

|

SU1027802A1 |

| Однофазный D-триггер | 1988 |

|

SU1647855A1 |

Изобретение относится к области вычислительной и предназначено для построения арифметикр-логичес- ких устройств. Цель изобретения - уменьшение количества оборудования. Сумматор содержит шесть переключателей тока, каждый из которых построен на информационном и опорном транзисторах, три источника тока, четыре детектора тока и четыре эмиттергалх повторителя. В качестве детекторов тока могут быть использованы схемы, состоящие из параллельно соединенных резистора и диода, t ил,, 1 табл. 1чЭ 4ib ;ik О О)

| Авторское свидетельство СССР № 760094, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ТРЕХВХОДОВЫЙ СУММАТОР | 1972 |

|

SU429422A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-15—Публикация

1984-08-08—Подача