Изобретение относится к вычислительной технике и может быть использовано при построении систем передачи информации, устройств модулярной ариф метики, специализированных многопро- цессорных магистрально-модульных ин- формационно- -управЛяющих систем.

Целью изобретения является расширение функциональных возможностей за счет работы в произвольной системе мо модулей.

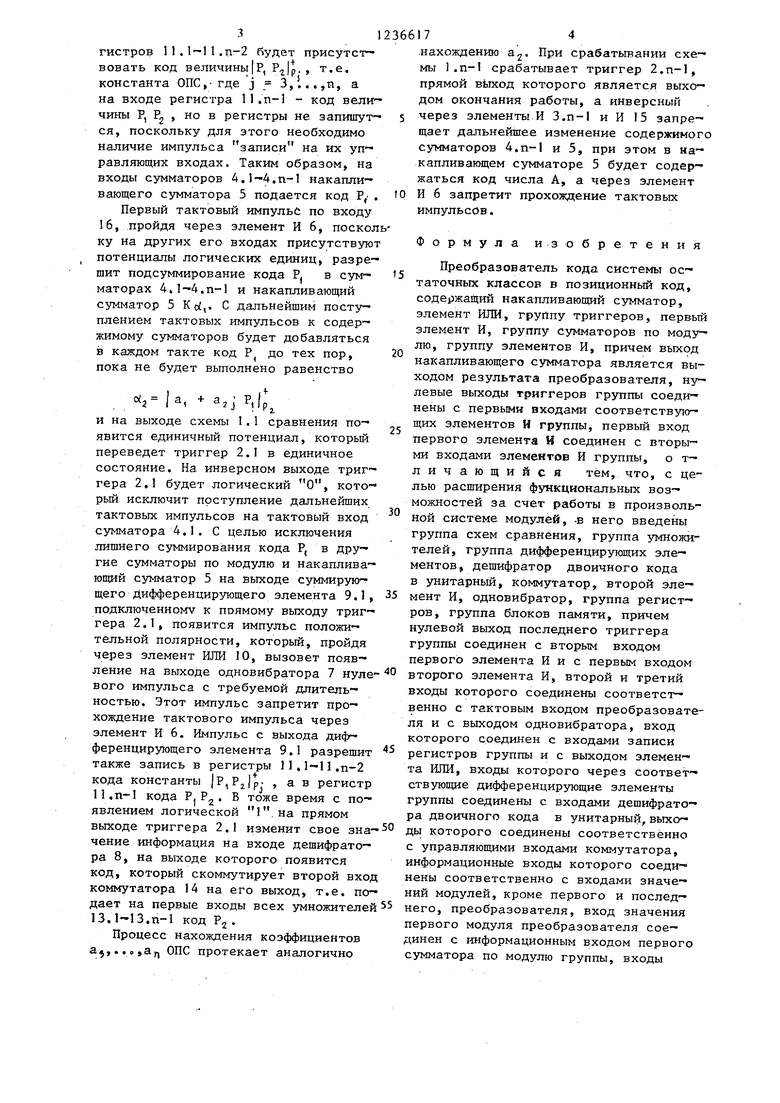

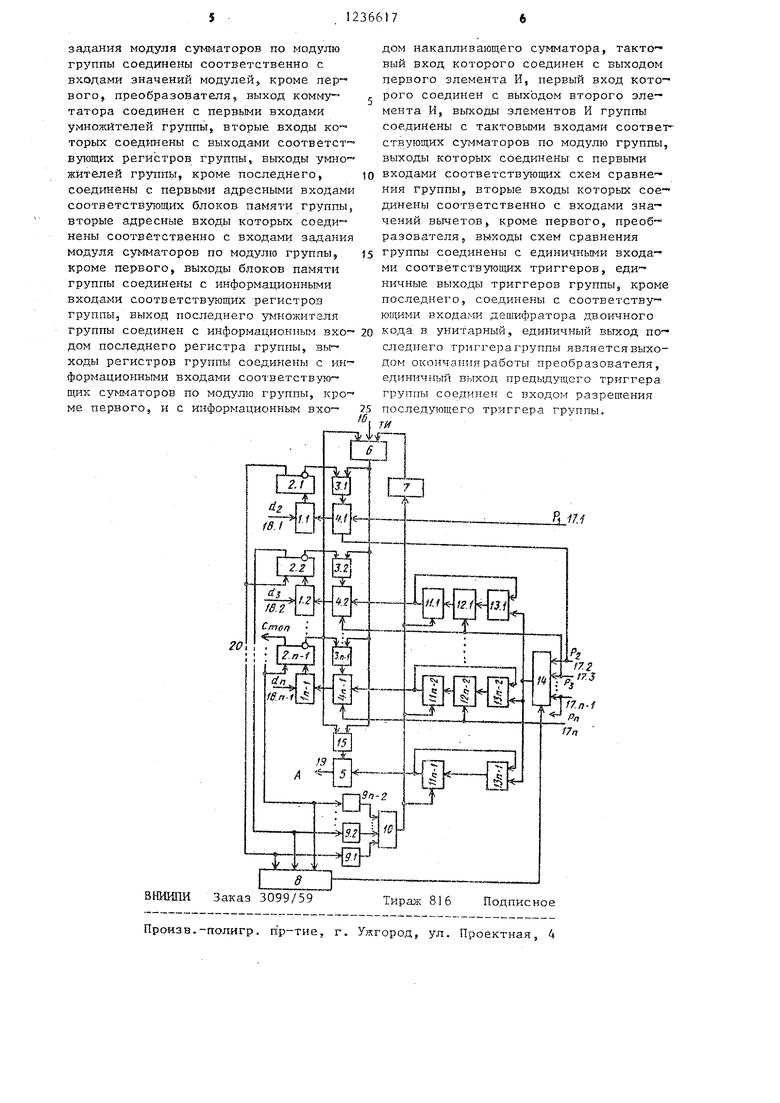

На чертеже представлена схема пре образователя кода системы остаточных классов в позиционный код.

Преобразователь кода системы оста- точных классов в позиционный код содержит группу схем сравнения 1 .1-1 .п- 1 .( п числомодулей), группу триггеров 2,1-2.п-1, группу элементов И S.l-S.n-l; группу сумматоров по модулю 4.1-4.гг1, накаплив ающий сумматор 5, элемент И 6, одновибратор 7, дешифратор 8 двоичного кода в унитарный, группу дифференцирующих элементов 9.1 9.11-2 элемент ИЛИ 10, груп- пу регистров П. -Il.n-lj группу блоков 12,1-12.П-2 памяти, группу умножителей 13. 1-13. п-1, коммутатор 14, элемент И 15, тактовый вход 16 преобразователя , входы 17.1-17. п значений модулей преобразователя, входы 18.1- 18, п-1 значений вычетов преобразователя, выходы 19 и 20 соответственно результата и окончания работы преобразователя.

Дифференциальные элементы 9.1- 9 in-2 дреобразуют скачок напряжения на их входах в одиночный импуЛьс,

Одновибратор 7 с приходом на его вход одиночного импульса формирует нулевой импульс требуемой длительности.

Дешифратор 8 может быть реализован в соответствии с таблицей истинности. ,

Из блока.12,j памяти по величинам В- и Р , поступающим на его первый и второй адресные входы, выбирается величина I В I р. ,,

Б работе преобразователя кода системы остаточных классов в позиционный код используется следующий алгоритм.

Любое число А натурального ряда может быть выражено в обобщенной позиционной системе (ОПС) как

А а, +а.,Р, -... Р;

(О

где aj - коэффициенты ОПС;

Р - основания ОПС, В то же время, число А в системе вычетов с основаниями аналогичными ОПС записывается в виде

А ( (X1 ,, а:

2

.Oip),

(2)

где - вычет от числа по модулю Р- . Если выражение (1) преобразователь по модулям Р; , то мы получим систему уравнений, описьшающую преобразование

ог, а.

i.i;

|Alp oi, ja, +a,,P, jp

(3)

|АГр «in - а,,+а,Р, + ...а,..|;,

Преобразователь кода системы остаточных классов в позиционный код работает следующим образом,

Б исходном состоянии на выходы 18.1-18. п поступают значения ( - на выходы 17.1-17.Л - значения ,, в накапливающий сумматор 5 и сумматоры -4,-4.п-1 по модулю записана величина кода младшего вычета с( , триг геры обнулены, на выходе одновибрато- ра 7 присутствует потенциал логической единицы, в регистры ll.l-ll.n- записан код младшего модуля Р,, первый вход коммутатора 14 скоммутиро- ваи на его выход и величина кода 7 поступит на первые входы умножителей 13.1 -13. п-15 на вторые входы которых с выходов регистров 1 1 , 1-П . п-1 поступает код модуля Р, , в результате на выходах умножителей 13.1-13,п-1 появится код величины , которая поступает на информационный вход регистра 11. п-1 и на первые входы 8 блоков 12.1-12.П-2 памяти, на втором входе j-ro блока памяти будет присутствовать код из входах регистров п. 1 11.11-2 будет присутствовать код величины Р,

т.е.

константа 011С,-где j 3,...,п, а на входе регистра ll.n-1 - код величины Р, „ , но в регистры не запишутся, поскольку для этого необходимо наличие импульса записи на их управляющих входах. Таким образом, на входы сумматоров 4.1-4.П-1 накапливающего сумматора 5 подается код Р, . Первый тактовый импульс по входу 6, пройдя через элемент И 6, поскол ку на других его входах присутствуют потенциалы логических единиц, разре- щит подсуммирование кода Р в сумматорах 4,1-4.п-1 и накапливающий сумматор 5 Кс,. С дальнейшим поступлением тактовых импульсов к содержимому сумматоров будет добавляться в каждом такте код Р до тех пор, пока не будет выполнено равенство

. N, + a,j Pjp

и на выходе схемы 1.1 сравнения появится единичный потенциал, который переведет триггер 2.1 в единичное состояние. На инверсном выходе триггера 2.1 будет логический О, кото рый исключит поступление дальнейщих тактовых импульсов на тактовый вход сумматора 4.1. С целью исключения лищнего суммирования кода Р, в другие сумматоры по модулю и накапливающий сумматор 5 на выходе суммирую щего дифференцирующего элемента 9.1, подключенному к прямому выходу триггера 2.1, появится импульс положительной полярности, который, пройдя через элемент ИЛИ 10, вызовет появление на выходе одновибратора 7 нуле вого импульса с требуемой длительностью. Этот импульс запретит прохождение тактового импульса через элемент И 6. Импульс с выхода дифференцирующего элемента 9.1 разрешит также запись в регистры 11,1-11.п-2 кода константы , а в регистр 11.П-1 кода Р)РЗ В тоже время с появлением логической Г .на прямом выходе триггера 2.1 изменит свое зна чение информация на входе дешифратора 8, на выходе которого появится код, который скоммутирует второй вхо коммутатора 14 на его выход, т.е. подает на первые входы всех умножителе 13.1-13,п-1 код Pj.

Процесс нахождения коэффициентов а,..о,а ОПС протекает аналогично

0

S

0

0

5

.нахождению а. При срабатывании схемы 1.п-1 срабатывает триггер 2.п-1, прямой вЬпсод которого является выходом окончания работы, а инверсный через элементы.И 3,п-1 и И 15 запрещает дальнейшее изменение содержимого сумматоров 4,п-1 и 5, при этом в на- капливакщем сумматоре 5 будет содержаться код числа А, а через элемент И 6 запретит прохождение тактовых импульсов.

Формула изобретения

Преобразователь кода системы остаточных классов в позиционный код, содержащий накапливающий сумматор, элемент ИЛИ, rpyrtny триггеров, первый элемент И, группу сумматоров по модулю, группу элементов И, причем выход накапливающего сумматора является выходом результата преобразователя, нулевые выходы триггеров группы соединены с первыми входами соответствующих элементов И группы, первый вход первого элемента И соединен с вторыми входами элементов И группы, о т- личающийся тем, что, с целью расширения функциональных возможностей за счет работы в произвольной системе модулей, -в него введены группа схем сравнения, группа умножителей, группа дифференцирующих элементов, дешифратор двоичного кода в унитарный, коммутатор, второй элемент И, одновибратор, группа регистров, группа блоков памяти, причем нулевой выход последнего триггера группы соединен с вторым входом первого элемента И и с первым входом второго элемента И, второй и третий входы которого соединены соответственно с тактовым входом преобразователя и с выходом одновибратора, вход которого соединен с входами записи регистров группы и с выходом элемента ШШ, входы которого через соответствующие дифференцирующие элементы группы соединены с входами дешифратора двоичного кода в унитарный, выходы которого соединены соответственно с управляющими входами коммутатора, информационные входы которого соединены соответственно с входами значений модулей, кроме первого и последнего, преобразователя, вход значения первого модуля преобразователя соединен с информационным входом первого сумматора по модулю группы, входы

задания модуля сумматоров по модулю группы соединены соответственно с входами значений модулей,, кроме пер вого, преобразователя, выход коммутатора соед{-шен с первыми входами умножителей группы, вторые входы которых соединены с выходами соответст- вующих регистров группы, выходы умно - жйтелей группы, кроме последнего, соединены с первыми адресными входами соответствующих блоков памяти группы, вторые адресные входы которых соеди- иены соответственно с входами задания модуля сумматоров по модулю группы, кроме первого, выходы блоков памяти группы соединены с информационными входами соответствующих регистров группы, выход последнего умножителя группы соединен с информационным входом последнего регистра группы, выходы регистров группы соединены с информационными входами соответствующих сумматоров по модулю группы, кроме первого, и с информационным вхо-

Т1.

дом накапливающего сумматора, тактовый вход которого соединен с выходом первого элемента И, первый вход которого соединен с выходом второго элемента И, выходы элементов И группы соединены с тактовыми входами соответ ствугощих сумматоров по модулю группы, выходы которых соединены с первыми входами соответствующих схем сравнения группы, вторые входы которых сое динены соответственно с входами зна- чений вычетов, кроме первого, преоб разователя, выходы схем сравнения

группы соединены с единичными входа- ми соответствующих триггеров, единичные выходы триггеров группы, кроме последнего, соединены с соответствующими входами дешифратора двоичного

кода в унитарный, единичный выход по- спеднего триггера группы является выходом окончания работы преобразователя, единичный выход предыдущего триггера группы соединен с входом разрешения последующего тр:яггера группы.

Ш

.-Jj

S

.X

«еf7.2 73

.п-1 Рп

ВНИШШ Заказ 3099/59Тира к816 Подписное

Произв.-полигр. п р-тие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода системы остаточных классов в двоичный код | 1983 |

|

SU1133669A1 |

| Преобразователь непозиционного кода в двоичный код | 1982 |

|

SU1083179A1 |

| Преобразователь непозиционного кода в двоичный код | 1988 |

|

SU1578810A1 |

| Устройство для сравнения чисел в модулярном коде | 1985 |

|

SU1256013A1 |

| Преобразователь непозиционного кода в двоичный код | 1984 |

|

SU1179547A1 |

| Преобразователь кода из системы остаточных классов в позиционный код | 1986 |

|

SU1388996A1 |

| Устройство для определения позиционных характеристик непозиционного кода | 1985 |

|

SU1283948A1 |

| Преобразователь кода | 1989 |

|

SU1619401A1 |

| Обратимый преобразователь двоичных кодов в код системы остаточных классов | 1983 |

|

SU1141398A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1984 |

|

SU1238078A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении систем передачи информации, устройств модулярной арифметики, специализированных многопроце ссорных магистрально-модуль- ных информационно-управляющих систет. Целью изобретения является расширение функциональных возможностей за счет работы в произвольной системе модулей. Поставленная цель достигается тем, что в преобразователь кода системы остаточных классов в позиционный код, содержащий сумматоры по модулю, накапливающий сумматор, триггеры и элементы И, элемент ИЛИ, введены схемы сравнения, регистры, умножители, блоки памяти, дифференцирующие элемеН1Ы дешифратор, коммутатор, одновибратор, 1 ил. с to (Л с го со 05 О)

| Устройство для преобразования чисел из порционной системы счисления в систему остаточных классов | 1981 |

|

SU1008729A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь кода системы остаточных классов в двоичный код | 1983 |

|

SU1133669A1 |

Авторы

Даты

1986-06-07—Публикация

1984-11-11—Подача