12

рицы коммутаторов 2x2, вХоды запроса многоуровневого коммутатора соединены соотв.етственно с входами запроса управляющих коммутаторов 2x2 первой управляющей матрицы коммутаторов, выходы з.апроса управляюпщх коммутаторов 2x2 К-й управляющей матрицы соединены соответственно с в{5гходами сигналов

I

Изобретение относится к автоматике, коммутационной и вычислительной технике и может быть использовано при построении коммутируемых сетей, связывающих, источники и приемники информации.

Цель изобретения -- повьппение быстродействия и упрощение за счет уменьшения числа управляющих входов и реализации асинхронного управления процессом установления связи информационных входов с информационным выходами по заданным адресам и сигналам запросов, что уменьшает время установления требуемой связи.

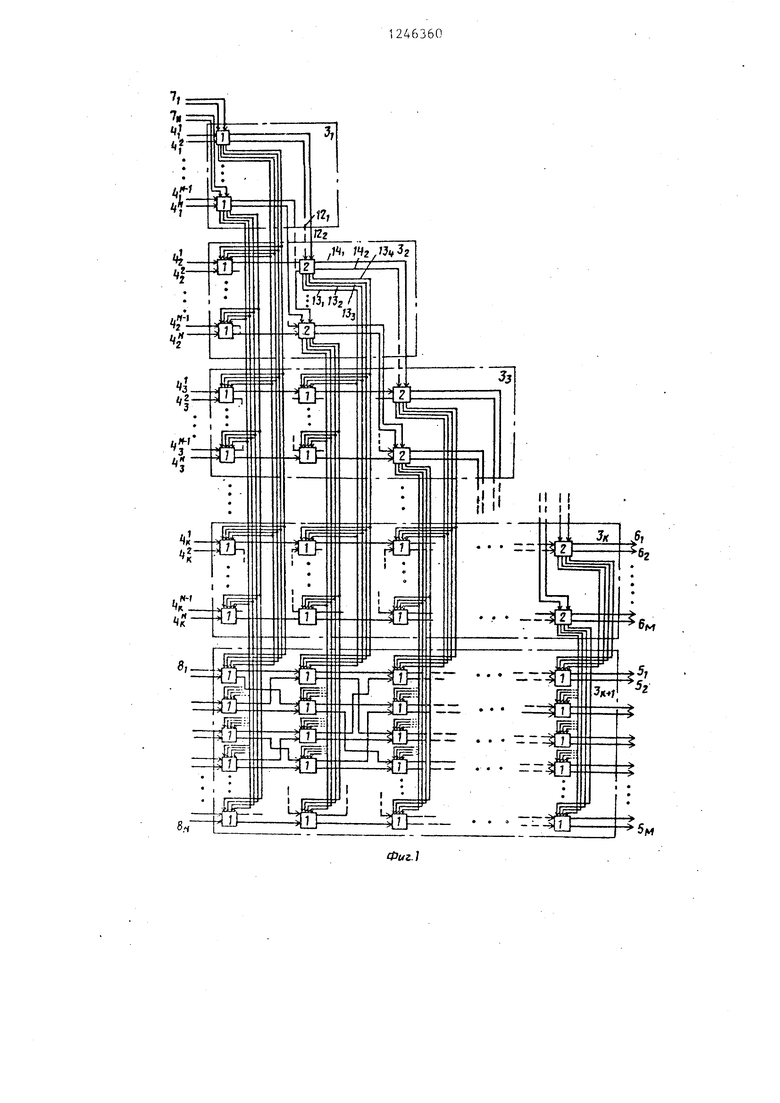

На фиг. 1 представлена структурная схема многоуровневого коммутатора; на фиг. 2 - функциональная схема управляющего коммутатора 2x2.

Многоуровневый коммутатор содер- жит коммутаторы 1 2x2, управляющие коммутаторы 2 2x2, управляющие матрицы 3 , - 3 , коммутации, матрицу 3

коммутации, входы 4- 4

k-n . .

где i 1,...,K, i-ro разряда адреса информационные выходы 5 , 5, ... ,5, выходы 6,1 6j ,.. . ,6 м запроса, входы

7 -7/v запроса, информационные входы

8-f - 8д|.

Упр авляющий коммутатор 2 2x2 соде жит элементы И 9- - 9g элементы ЗАПРЕТ 10 , - lOg , входы 11,, и 11., , /входы 12 и 12 запроса, .управля- ующие выходы 13it - 13, выходы 14 и 14, запроса. .

(к+1) коммутаторов 2x2 содержит К столбцов, где , L max { N, м}; N - число информационных входов; М - число информационных выходов многоуровневого коммута- тора, причем п-й выход коммутатора 1 2x2 d-ro столбца g-й строки, где d 1-(К-1); g 1 ,

запроса- многоуровневого коммутатора, входы коммутаторов 2x2 первого столбца i-й управляющей матрицы коммутации, а для i-1 входы управляющих коммутаторов 2x2 соединены соответственно с входами i-ro разряда адресов информационных выходов многоуровневого коммутатора.

соединен с т-м входом коммутатора 1 2x2 (d+1)-ro столбца S-й строки, где

m

1 + Mod,(|; + 1);

M

S(Mod, (n+ () + gMod (n+ - -H),

3(

3

п-й выход (,2), коммутатора 2x2 g-столбца - g-й строки матрицы коммутаторов 2x2 и управляющих матриц коммутации соединен с т-м входом (га 15 1,2), матричного коммутатора 2x2 S-й строки (d+1)-ro столбца, где

- m 1 + Mod

:s(g-2° (-1) Mod. (n+ ( ) +

I J .

+ g Mod (),

25 Mod ,j (...) означает число в скобках, взятое по модулю два; d 1+(i-1); i - номер управляющей матрицы 3 коммутации. Информационные входы 8; многоуровневого коммутатора соединены

N

соответственно с входами

коммутаторов 1 2x2 первого столбца матрицы 3j,+i коммутаторов 1 2x2, п-й выход коммутатора 1 2x2 d-ro столбца g-й строки, где , d 1- (К-1);

kl о -i

g 1 соединен с га-м входом

(d+1)-ro столбца S-й

),.

)) (g

-С-1) h

(2

+ g Mod (n+ |.),

информационные выходы 5 многоуровне

вого коммутатора соединены соответст венно с выходами коммутаторов 1 2x2 К-го столбца матрицы 3,1, коммутаторов 2x2, п-й выход коммутатора 1 2x г-го столбца g-й строки управляющей матрицы 3; коймутации (, где г 1 (i-1), соединен с т-м входом коммутатора 2x2 (г+1)-го столбца S-й |строки управляющей матрицы 3, , а для г i - 1 - с т-м входом управляющег

коммутатора 2 2x2 i-ro столбца S-й

„о

строки управляющей матрицы j; коммутации, п-й выход запроса управляющего коммутатора 2x2 i-ro столбца g-й строки управляющей матрицы 3, коммутации соединен с т-м входом запроса управляюп;его коммутатора 2 2x2 S-й строки (1+1)-й управляющей матрицы 3,,, коммутации,первый,второй,третий и . четвертый управляющие выходы 13, - 13j, управляющего коммутатора 2 2x2 g-й строки i-ro столбца управлякщей матрицы 3, коммутации 2x2 соединены соответственно с первым, вторьгм, третьим и четвертым управляющими входами коммутаторов 1 2x2 g-й строки i-ro столбца управляющих матриц 3;,, 3 3- ,,..,3j коммутации и матрицы 3| + т коммутации. Входы 7, - 7 запроса многоуровневого коммутатора соединены-соответственно с входами 12 и 122 запроса управляющих комму- таторов 2 2x2 управляющей матрицы

3,коммутаторов. Выходы 6 -6м сигналов запроса многоуровневого коммутатора соединены соответственно с выходами 14 , и 14,j запроса управ- ляющих коммутаторов 2 2x2 управляющей матрицы 3 коммутации. Входы управляющих коммутаторов 2x2 управляющей матрицы 3 коммутации соединены соответственно с входами 4 . ,

214

4 ,..,,4 старшего разряда адресов .информационных выходов многоуровневого коммутатора, а входы 4- ,

4.,...,4; многоуровневого коммутатора i-ro разряда адресов выходов многоуровневого коммутатора соединены соответственно с входами коммутаторов 1 2x2 первого столбца управляющей матрицы 3- коммутации.

Многоуровневый коммутатор работает следующим образом.

Для образования цепи связи между информационными входами 8j и информа

5

5

ционными выходами 5t/ многоуровневого коммутатора, где j 1-N, , в соответствии с принципом двоичного дерева необходимо осуществлять выбор направления связи в К столбцах матрицы коммутации, где К log,, L max IN,ML в которых размещены матричные коммутаторы 1 2x2, дающие возможность установления связи каждого из двух входов с одним из двух выходов путем подачи на четыре его управляющих входа соответствующих управляющих сигналов. Направление установления связи в каждом i-м столбце задается для каждого информационного входа 8j значением i-ro разряда ад- реса, соответствующего этому информационному входу, поступающим на вход 4 управляющей матрицы 3; коммута- дии. В i-й столбец управляющей мат- /рицы 3. коммутации этот разряд адреса поступает с входа 4 | по тому же пути, что и в матрице Зц + -коммутации, что обеспечивается наличием в управляющей матрице 3- коммутации К столбцов,из которых К-1 столбцов содержат коммутаторы 1 2x2, а К-й столбец - управляющие 2 коммутаторы 2x2.

Процесс установления связи между информационным входом 8д и выходом 5/ многоуровневого коммутатора начинается с момента подачи на вход 7j запроса сигнала на установление связи. При этом на входы 41 (), подаются разряды кода адреса информа- . ционного выхода 5 k . В первой управляющей матрице 3| сигнал с входа 7j .запроса поступает на вход запроса управляющего коммутатора 2 2x2, на одноименный вход которого поступает с входа 4 старший разряд кода адреса. Последний определяет, во-первых, на какой из двух запросных выходов управляющего коммутатора 2x2 будет передан входной сигнал запроса, и, во- вторьпс, значение сигналов на первом, втором, третьем и четвертом управляющих выходах 13., - 13 управляющего коммутатора 2x2. Так как управляющие

выходы 13, - 13, связаны с соответI (,

ствующими управляющими входами ком- мутатора 2x2 одноименной строки одноименного столбца управляющих матриц

3...

3;.,, , ...,3к

(-4

коммутации и матрицы 3, коммутации, то подключение входов к выходам в этих коммутаторах 2x2 осуществляется в одинаковом их направлении.

Выбор направления установления связи осуществляется в каждой управляющей матрице 3; коммутации .в управляющих коммутаторах 2x2 i-ro столбца . Если в каком-либо управляющем коммутаторе 2x2 выбираемое направление связи уже занято, то поступивший ранее запрос на установление связи будет блокировать прохождение более позднего запроса и, следовательно, изменения сигналов на управляющих выходах 13 не произойдет. Установленные соединения в многоуровневом ком- мутаторе удерживаются при удержании сигнала на соответствующем входе 7 запроса и освобождаются при снятии этого сигнала, а признак установления связи соответствует сигналу на выходе 6 запроса многоуровневого коммутатора.

Зк+1 комКоммутаторы 1 2x2 матрицы мутации и управляющих матриц 3; коммутации каждого столбца связаны своими выходами с входми коммутаторов 2

12463606

2x2 следующего столбца, так, что обеспечивают полнодоступную связь в первом столбце между каждыми двумя вхо- даьш и двумя выходами каждого комму- 5 татора 2x2 первого столбца, в первом и втором столбце между четверками входов и выходов коммутаторов 2x2 двух строк и двух, столбцов.

Таким образом, в предлагаемом 10 многоуровневом коммутаторе повьщ1ено быстродействие за счет реализации асинхронного управления процессом установления связи информационных входов с выходами по заданным адресам 15 и сигналам запроса, что уменьшает потери времени на установление связи.

Время ожидания разрешения кофлик- тов при запросе несколькими источниками связи с одним выходом не превос- 20 ходит времени использования этого

выхода (N-1) источником, а количество .управляющих входов уменьшено в сравнении с известным устройством в

4 M/log L раз.

4 M/log L раз.

§1 бг

Ф,

Редактор В. Петраш

Составитель С. Куем Техред Л.Олейник

Заказ 4021/55Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

--.- - - -. - - - « - .1.«- «...«. «..

Производственно-полиграфическое предприятие, г Ужгород, ул. Проектная, 4

Фиг,. I

Корректор И, Эрдейи

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для многоуровневой коммутации процессоров и блоков памяти | 1983 |

|

SU1213474A1 |

| Устройство для сопряжения многопроцессорной вычислительной системы | 1983 |

|

SU1160423A1 |

| Генератор волновых функций Мебиуса | 1988 |

|

SU1548778A1 |

| Устройство для сопряжения группы из М вычислительных машин с группой из К абонентов | 1986 |

|

SU1310830A1 |

| Устройство для сопряжения | 1982 |

|

SU1038933A1 |

| Коммутационное устройство | 1988 |

|

SU1539790A1 |

| Устройство для сопряжения | 1981 |

|

SU964622A1 |

| Устройство для сопряжения каналов ввода-вывода с внешними устройствами | 1985 |

|

SU1277128A1 |

| Устройство для сопряжения | 1990 |

|

SU1753478A1 |

| СИСТЕМА КОММУТАЦИИ ПРОЦЕССОРОВ | 1991 |

|

RU2006931C1 |

| Мультипроцессорные системы и параллельные вычисления | |||

| Под ред | |||

| Ф | |||

| Энслоу, М,: Мир, 1976, с, 47, рис | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Processor memory Interconnections for Multiprocessor | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Symp | |||

| on Computer Architecture, 1976, New York, 1979, p | |||

| Аппарат для передачи фотографических изображений на расстояние | 1920 |

|

SU170A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-07-23—Публикация

1985-01-03—Подача