Изобретение относится к вычис лителт.ной технике и иредназначено для объединения процессоров и блоков памяти в системы высокой производительности.

Цель изобретения - повышение быстродействия.

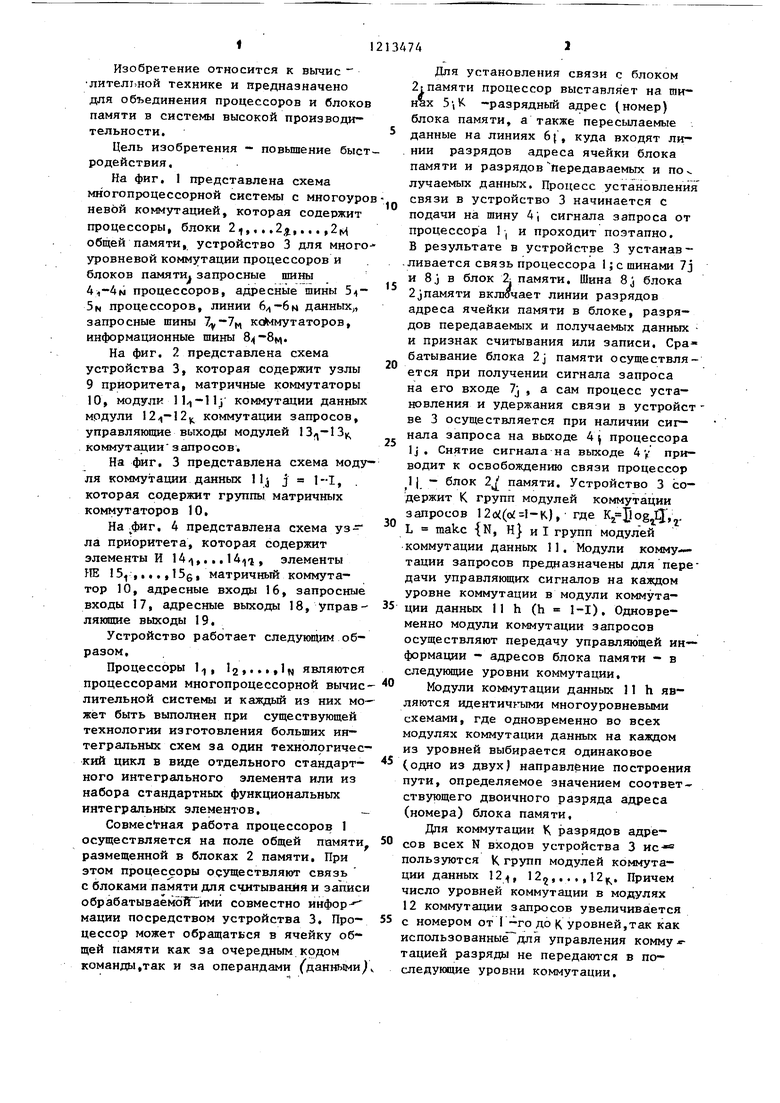

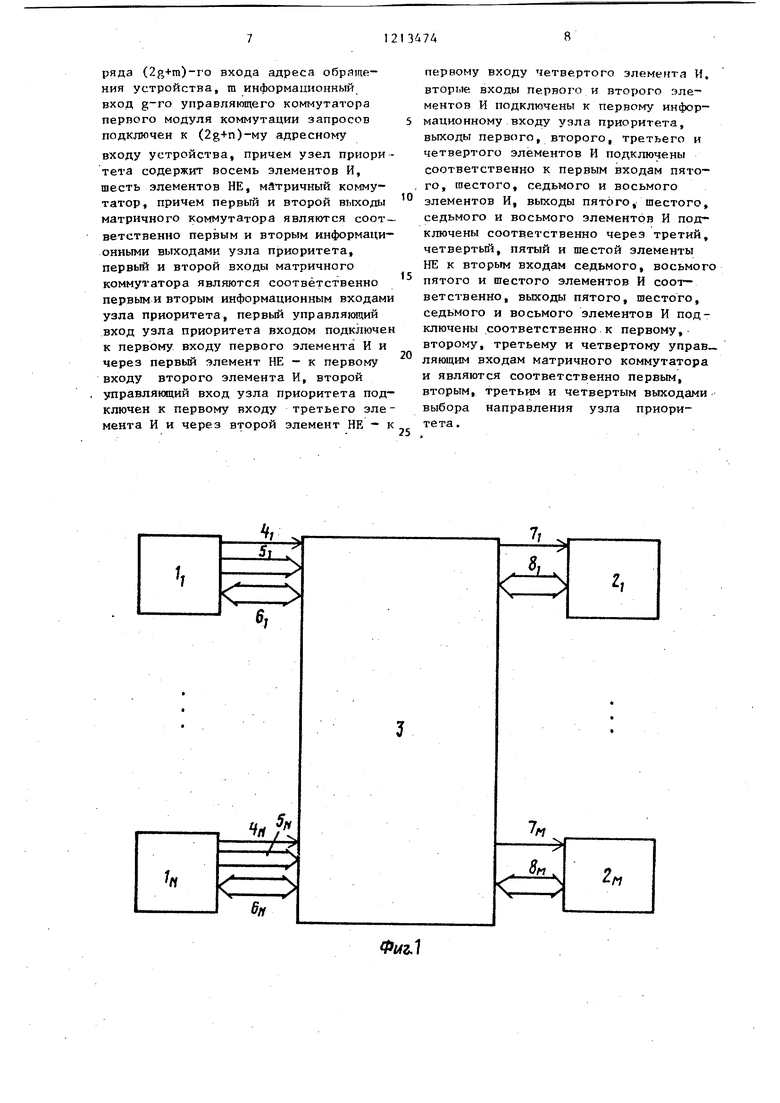

На фиг, 1 представлена схема многопроцессорной системы с многоуров Невой коммутацией, которая содержит процессоры, блоки Zi,,, , ,2д,,,, ,2|v общей памяти, устройство 3 для много-- уровневой коммутации процессоров и блоков памятИс запросные пшны AI-AN процессоров, адресные шины 54 SN процессоров, линии данных,, запросные шины коммутаторов, информационные шины 8/(-8м,

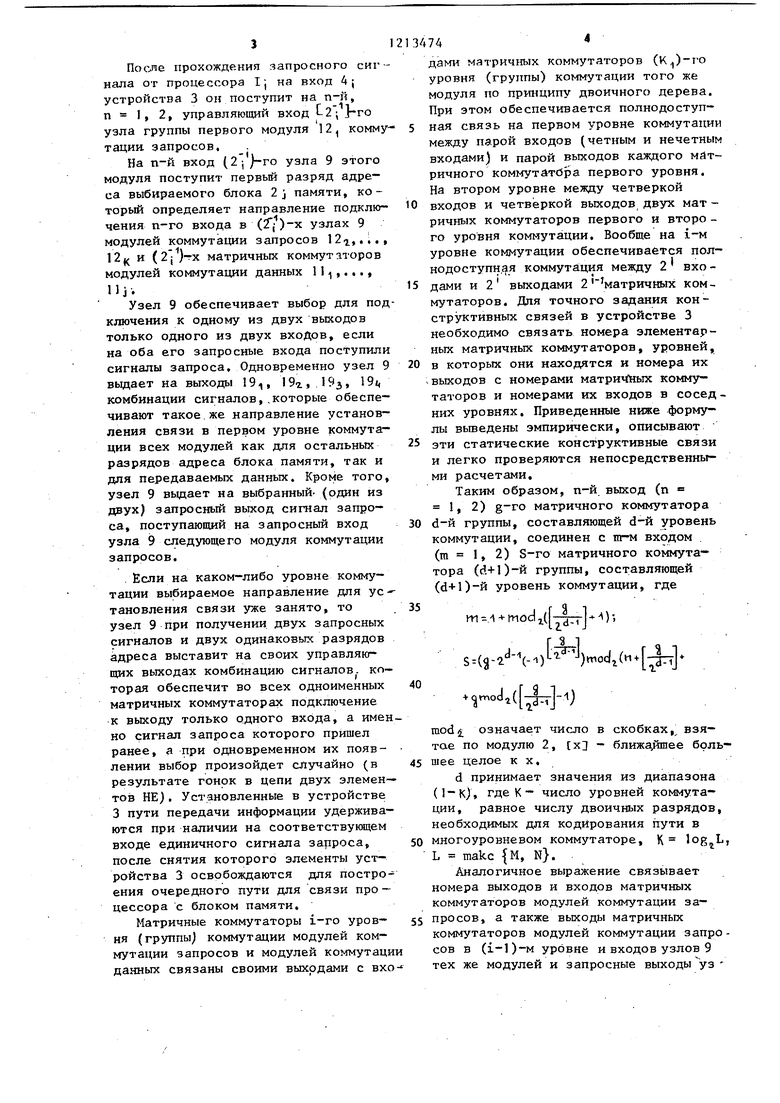

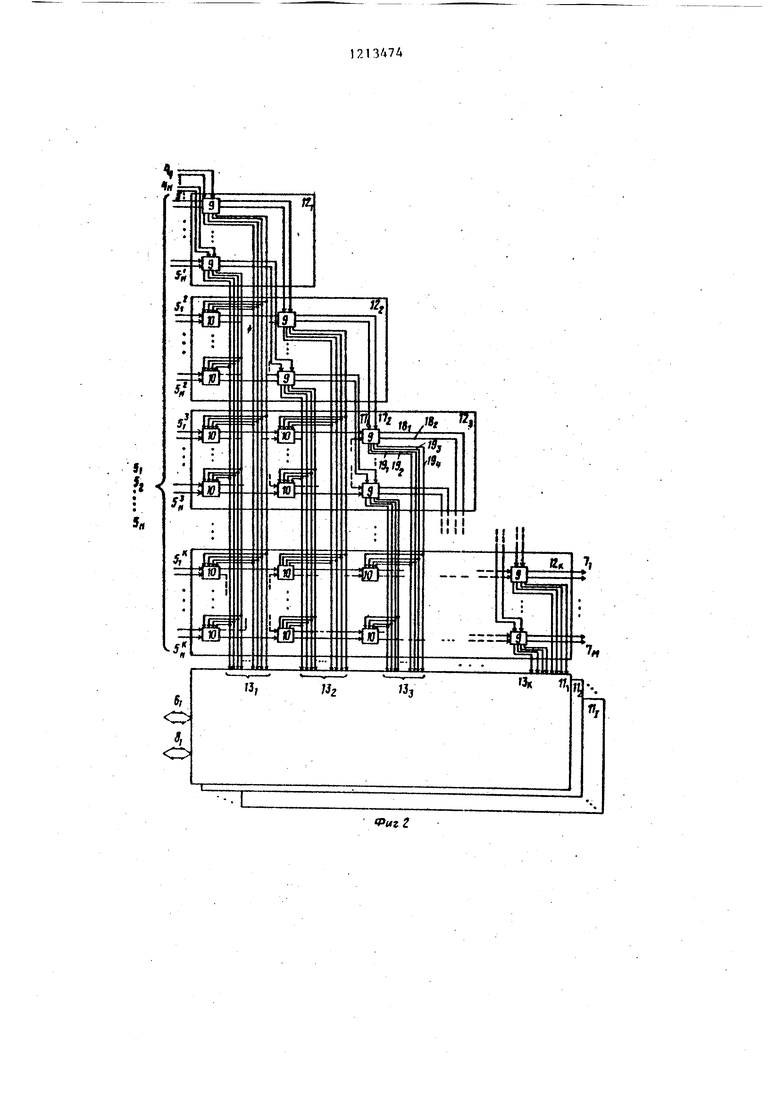

На фиг, 2 представлена схема устройства 3, которая содержит узлы 9 приоритета, матричные коммутаторы 10, МОДУЛИ 11-,-11 j коммутации данных модули ,,, коммутации запросов, управляющие выходы модулей коммутации запросов.

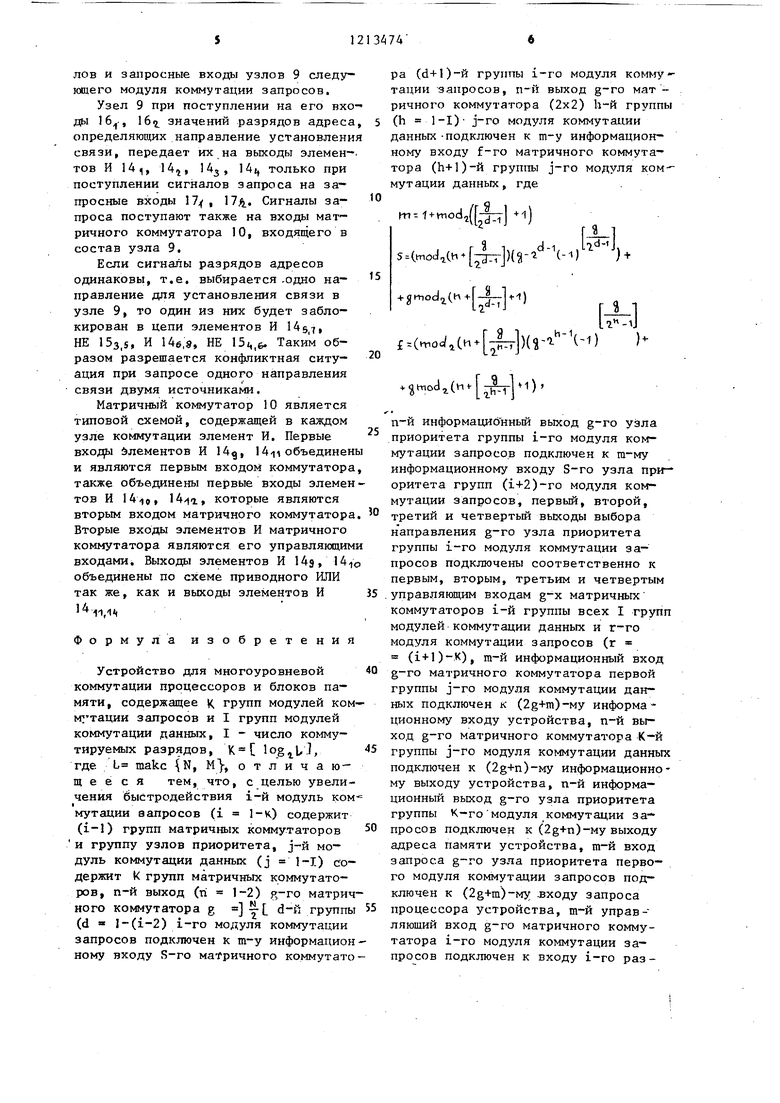

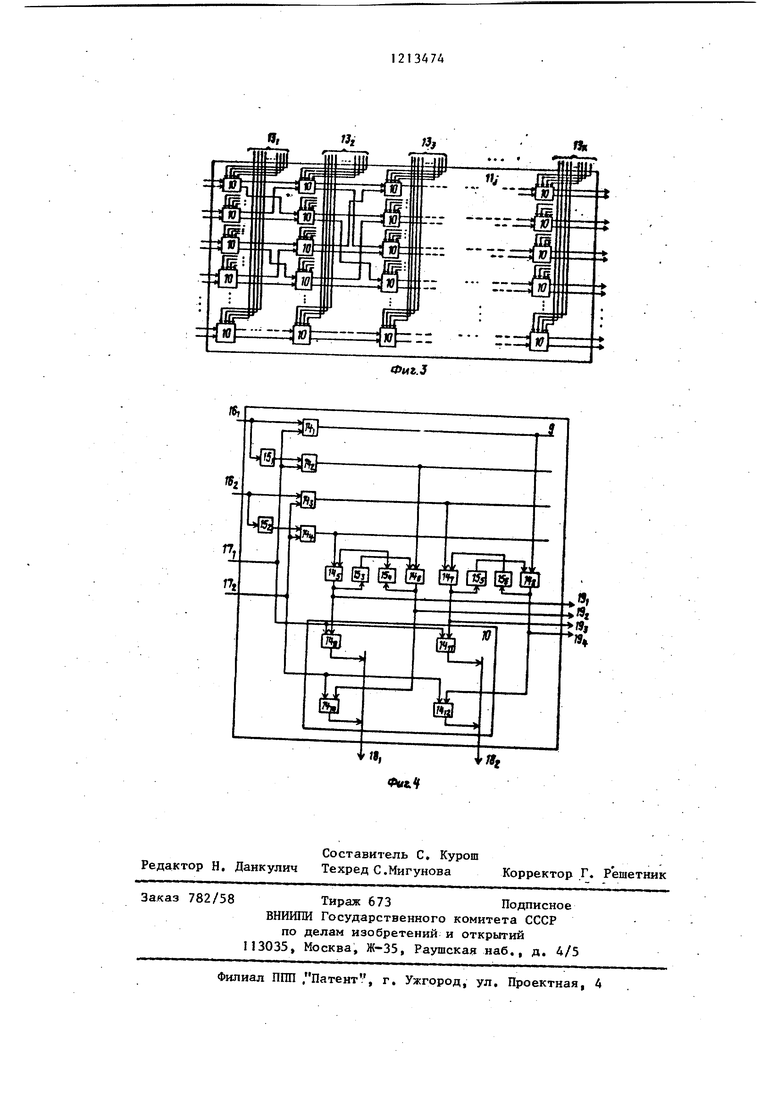

На фиг, 3 представлена схема модзг- ля коммутации даиных 11 j , которая содержит группы матричных коммут аторо в 10,

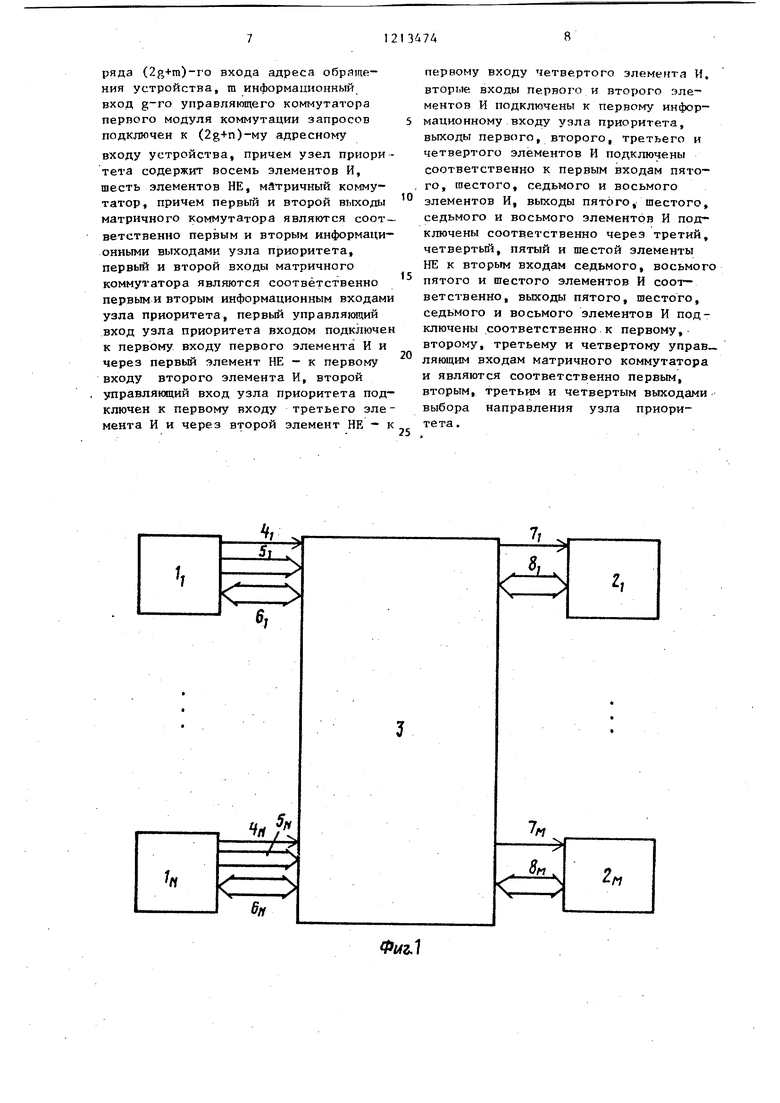

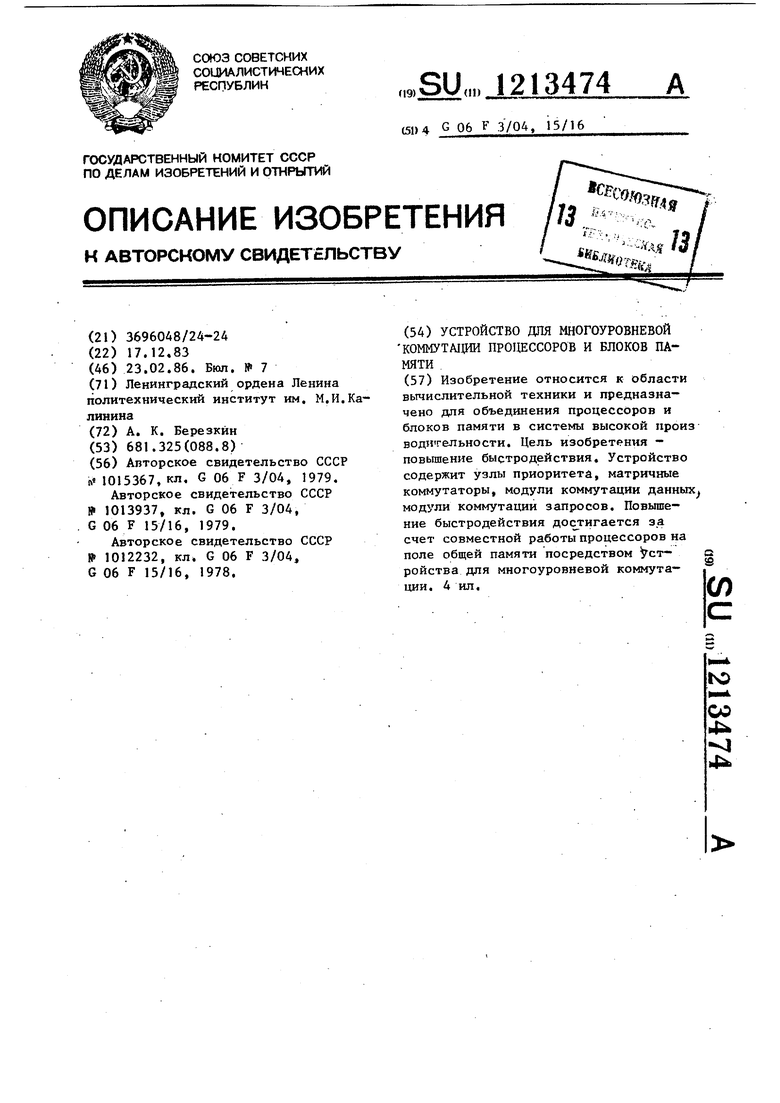

На фиг, 4 представлена схема узла приоритета, которая содержит элементы И 14,,,,4ii, элементы НЕ 15 ,,,,,15g, матричный коммутатор 10, адресные входы 16, запросные входы 17, адресные выходы 18, управляющие выходы 19,

Устройство работает следующим образом.

Процессоры Ц, являются процессорами многопроцессорной вычис- лительной системы и каждый из них может быть выполнен при существующей технологии изготовления больших интегральных схем за один технологический цикл в виде отдельного стандартного интегрального элемента или из набора стандартных функциональных интегральных элементов,-

Совмес гная работа процессоров 1 осуществляется на поле общей памяти размещенной в блоках 2 памяти. При этом процессоры осуществляют связь с блоками памяти для считывания и записи обрабатываемоЙПими совместно инфор- мации посредством устройства 3, Процессор может обращаться в ячейку общей памяти как за очередным кодом команды,так и за операндами (данными)

-

в

в--

г-

с- ос-

и и )

10

15

20

25

30

35

40

45

50

55

Для установления связи с блоком 2 Памяти процессор выставляет на шинах 5,К, -разрядный адрес (номер) блока памяти, а также пересылаемые . данные на линиях 6{, куда входят ли- . НИИ разрядов адреса ячейки блока памяти и разрядов передаваемых и по лучаемых данньпс. Процесс установления связи в устройство 3 начинается с подачи на шину 4) сигнала запроса от процессора Г, и проходит поэтапно, В результате в устройстве 3 устанав - . ливается связь процессора 1; с шинами 7j и 8j в блок 2: памяти. Шина 8j блока 2jпaмяти включает линии разрядов адреса ячейки памяти в блоке, разрядов передаваемых и получаемых данных и признак считывания или записи. Срабатывание блока 2j памяти осуществляется при получении сигнала запроса на его входе 7j , а сам процесс установления и удержания связи в устройст - не 3 осуществляется при наличии сигнала запроса на выходе 4j процессора Ij, Снятие сигнала на выходе 4 у приводит к освобождению связи процессор 1j - блок 2 памяти. Устройство 3 содержит К групп модулей коммутации запросов (.), где о,. L make {N, Н} и I групп модулей коммутации данных 11, Модули коммутации запросов предназначены для передачи управляющих сигналов на каждом уровне коммутации в модули коммутации данных II h (h « l-I), Одновременно модули коммутации запросов осуществляют передачу управляющей информации - адресов блока памяти - в следующие уровни коммутации.

Модули коммутации данных 11 h являются идентич -ыми многоуровневыми схемами, где одновременно во всех модулях коммутации данных на каждом из уровней выбирается одинаковое (одно из двух) направление построения пути, определяемое значением соответствующего двоичного разряда адреса (номера) блока памяти.

Для коммутации К, разрядов адресов всех N входов устройства 3 ис- пользуются К групп модулей коммутации данных 12, 122,...,12, Причем число уровней коммутации в модулях 12 коммутации запросов увеличивается с номером от I -го до К уровней,так как использованныё для управления комму тацией разряды не передаются в последующие уровни коммутации.

3

Посгае прохождения запросного сигнала от процессора Ij на вход 4j устройства 3 он поступит на п-й, п I, 2, управляющий вход С-2; j-ro узла группы первого модуля 12, коммутации, запросов.

На п-й вход (2 )-го узла 9 этого модуля поступит первьй разряд адреса выбираемого блока 2 j памяти, ко - торый определяет направление подключения п-го входа в ( )-х узлах 9 модулей коммутации запросов 127.« 12) и ()тх матричных коммутаторов модулей коммутации данных 11;),..., llj.

Узел 9 обеспечивает выбор для подключения к одному из двух выходов только одного из двух входов, если на оба его запросные входа поступили сигналы запроса. Одновременно узел 9 выдает на выходы 19, 197., 19з 19i, комбинации сигналов,.которые обеспечивают такое.же направление установления связи в первом уровне коммутации всех модулей как для остальных разрядов адреса блока памяти, так и для передаваемых данных. Кроме того, узел 9 выдает на выбранный- (один из двух) запросный вьжод сигнал запроса, поступающий на запросный вход узла 9 следующего модуля коммутации запросов.

.Если на каком-либо уровне коммутации выбираемое направление для установления связи уже занято, то узел 9 при получении двух запросных сигналов и двух одинаковых разрядов адреса выставит на своих управляющих выходах комбинацию сигналов, которая обеспечит во всех одноименных матричных коммутаторах подключение к выходу только одного входа, а именно сигнал запроса которого пришел ранее, а при одновременном их появ- лении выбор произойдет случайно (в результате гонок в цепи двух элементов НЕ)t Установленные в устройстве 3 пути передачи информации удерживаются при наличии на соответствующем входе единичного сигнала зарроса, после снятия которого элементы устройства 3 освобождаются для построения очередного пути для связи процессора с блоком памяти.

Матричные коммутаторы i-ro уровня (группы) коммутации модулей коммутации запросов и модулей коммутаци данных связаны своими выходами с вхо

13474«

дами матричных коммутаторов (К)-го уровня (группы) коммутации того же модуля по npi-шципу двоичного дерева. При этом обеспечивается полнодоступ5 ная связь на первом уровне коммутации между парой входов (четным и нечетным входами) и парой выходов каждого мйт- ричного комнутйтбра первого уровня. На втором уровне между четверкой

О входов и четверкой выходов, двух матричных коммутаторов первого и второ - го уровня коммутации. Вообще на i-м уровне коммутации обеспечивается пол15

20

25

30

35

40

нодоступн.ая коммута;ция между 2 входами и 2 выходами 2 матричных ком мутаторов. Для точного задания кон- стру ктивных связей в устройстве 3 необходимо связать номера элементарных матричных коммутаторов, уровней, в которых они находятся и номера их V выходов с номерами матри йых коммутаторов и номерами их входов в сосед - них уровнях. Приведенные ниже формулы вьшедены эмпирически, описывают эти статические конструктивные связи и легко проверяются непосредственными расчетами.

Таким образом, п-й выход (п 1,2) g-ro матричного коммутатора d-й группы, составляющей d-й уровень коммутации, соединен с га-м входом (та 1, 2) S-ro матричного коммутатора (й+1)-й группы, составляющей (d+l)-й уровень коммутации, где

m.-i mod rlrrl-)-.

Li J

S(.)t)moc|,(H. (- )

mod означает число в скобках, взятое по модулю 2, X - ближа ее большее целое к х.

d принимает значения из диапазона (1-К), где К - число уровней коммутации, равное числу двоичных разрядов, необходимых для кодирования пути в

многоуровневом коммутаторе, К Jog L, L make {М, N}. Аналогичное выражение связывает номера выходов и входов матричных коммутаторов модулей коммутации запросов, а также выходы матричных

коммутаторов модулей коммутации запро - сов в (i-)-M уровне и входов узлов 9 тех же модулей и запросные выходы уз лов и запросные входы узлов 9 следующего модуля коммутации запросов.

Узел 9 при поступлении на его входа 16., 167. значений разрядов адреса, определяющих направление установления связи, передает их на выходы элемен-. тов И 141, 14,j, , 14ц только при поступлении сигналов запроса на запросные входы 17, 17. Сигналы запроса поступают также на входы матричного коммутатора 10, входящего в состав узла 9.

Если сигналы разрядов адресов одинаковы, т.е. выбирается .одно направление для установления связи в узле 9, то один из них будет заблокирован в цепи элементов И 145j, НЕ 15з,5, И 14б,«, НЕ 15ц,6. Таким образом разрешается конфликтная ситуация при запросе одного направления связи двумя источниками.

Матричный коммутатор 10 является типовой схемой, содержащей в каждом узле коммутации элемент И. Первые BXOf Элементов И 14, объединены и являются первым входом коммутатора, также объединены первые входы элементов И 14и, 14-11, которые являются вторым входом матричного коммутатора. Вторые входы элементов И матричного коммутатора являются его управляющими входами. Выходы элементов И 149, объединены по схеме приводного ИЛИ так же, как и выходы элементов И

14

я,-

Формула изобретения

Устройство для многоуровневой коммутации процессоров и блоков памяти, содержащее к групп модулей ком мз тации запросов и I групп модулей коммутации данных, I - число коммутируемых разрядов, К logiU, где L make N, М}-, о т л и ч а ю - щ е е с я тем, что, с целью увеличения быстродействия i-й модуль ком мутации запросов (i 1-к) содержит (i-1) групп матричных коммутаторов и группу узлов приоритета, j-й модуль коммутации данных (j 1-1) содержит k групп матричных коммутаторов, п-й выход (п 1-2) g-ro матричного коммутатора g jL d-й группы (d « I-(i-2) i-го модуля коммутации запросов подключен к т-у информацион ному входу S-ro матричного коммутатора (ё+1)-й группы i-ro модуля коммутации запросов, п-й выход матричного коммутатора (2x2) h-й группы (h 1-1)- j-ro модуля коммутации данных-подключен к т-у информационному входу f-ro матричного коммутатора (Ь+1)-й группы j-ro модуля ком- мут ации данных, где

10

)

f-- 5(mod,)()

+ gmodi() f(n.oc/,CH)) .modjHv -| |M),

информационный выход g-ro узла приоритета группы i-ro модуля коммутации запросов подключен к т-му информационному входу S-ro узла приоритета групп (i+2)-ro модуля коммутации запросов, первьй, второй, третий и четвертый выходы выбора направления g-ro узла приоритета группы i-ro модуля коммутации запросов подключены соответственно к первым, вторым, третьим и четвертым .управляющим входам g-x матричных коммутаторов i-й группы всех I групп модулей коммутации данных и г-го модуля коммутации запросов (г (i+l)-K), га-й информационный вход g-ro матричного коммутатора первой группы j-ro модуля коммутации данных подключен к (2g+m)-My информационному входу устройства, п-й выход g-ro матричного коммутатора К-й группы j-ro модуля коммутации данных подключен к (2g+n)-My информационному выходу устройства, п-й информационный выход g-ro узла приоритета группы К-го модуля коммутации за- про сов подключен к (2g+n)-My выходу адреса памяти устройства, ш-й вход запроса g-ro узла приоритета первого модуля коммутации запросов подключен к (2g+m)-My .входу запроса процессора устройства, т-й управляющий вход g-ro матричного коммутатора i-ro модуля коммутации запросов подключен к входу i-ro разряда (2g+m)-ro входа адреса обряще- ния устройства, га информационный вход g-ro управляющего KObfMyraTOpa первого модуля коммутации запросов подключен к (2g+n)-My адресному входу устройства, причем узел приоритета содержит восемь элементов И, шесть элементов НЕ, матричный коммутатор, причем первый и второй выходы матричного коммутатора являются соответственно первым и вторым информационными выходами узла приоритета, первый и второй входы матричного коммутатора являются соответственно первым и вторым информационным входами узла приоритета, первый управляющий вход узла приоритета входом подключен к первому входу первого элемента И и через первый элемент НЕ - к первому входу второго элемента И, второй управляющий вход узла приоритета подключен к первому входу третьего элемента И и через второй элемент НЕ - к

первому входу четвертого элемента И, вторые входы первого и вто7)ого элементов И подключены к первому информационному входу узла приоритета, выходы первого, второго, третьего и четвертого элементов И подключены соответственно к первым входам пятого, шестого, седьмого и восьмого элементов И, выходы пятого, шестого, седьмого и восьмого элементов И подключены соответственно через третий, четвертьй, пятый и шестой элементы НЕ к вторым входам седьмого, восьмого пятого и Шестого элементов И соот- ветственно, выходы пятого, шестого, седьмого и восьмого элементов И подключены соответственно к первому, второму, третьему и четвертому управляющим входам матричного коммутатора и являются соответственно первым, вторым, третьим и четвертым выходами выбора направления узла приоритета.

r

fPut2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией | 1979 |

|

SU826330A1 |

| Коммутационное устройство | 1988 |

|

SU1539790A1 |

| Устройство управления сегментированной памятью многопроцессорной системы | 1990 |

|

SU1753477A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С ТЕЛЕГРАФНЫМИ КАНАЛАМИ СВЯЗИ | 1979 |

|

SU826332A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1985 |

|

SU1401459A1 |

| Система доступа к памяти | 1983 |

|

SU1151974A1 |

| Устройство для сопряжения каналов ввода-вывода с устройством управления оперативной памятью | 1984 |

|

SU1265788A1 |

| Устройство для обмена информацией | 1980 |

|

SU955014A1 |

Изобретение относится к области вычислительной техники и предназначено для объединения процессоров и блоков памяти в системы высокой произ води гельности. Цель изобретения - повышение быстродействия. Устройство содержит узлы приоритета, матричные коммутаторы, модули коммутации дaнныx модули коммутации запросов. Повышение быстродействия достигается за счет совместной работы процессоров на поле общей памяти посредством Устройства для многоуровневой коммутации. 4 ил. (Л to со 4 J

Я

ш н щ н а

t

а

:5

;

«I

/Vj(

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1979 |

|

SU1015367A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1979 |

|

SU1013937A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1979 |

|

SU1012232A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-02-23—Публикация

1983-12-17—Подача